静电放电保护装置及其操作方法与流程

1.本发明是有关于一种半导体装置,特别是有关于一种静电放电保护装置及其操作方法。

背景技术:

2.静电放电系起因于短时间内(一般在100纳秒nanosecond之内)的高压放电所引进的强大电流脉冲。集成电路及半导体元件对于静电放电相当敏感。尤其是在元件安装时,因为人类或机器碰触接脚,常使强大电流脉冲通过集成电路,而导致元件失效。因此有需要提供集成电路有效的静电放电保护装置。

3.寄生硅控整流器(silicon controlled rectifier,scr)是一种芯片式(on-chip)的半导体静电放电保护装置,可在静电放电发生时,通过骤回崩溃(snapback)开启,将静电放电电流传导至地面,达到静电放电的保护功能。因此,scr是目前业界所广为采用的静电放电保护装置之一。然而,当寄生硅控整流器无法顺利开启,将无法提高电流分路的能力。

4.因此,有需要提供一种先进的静电放电保护装置及其操作方法,以改善已知技术所面临的问题。

技术实现要素:

5.本发明系有关于一种静电放电保护装置及其操作方法,可解决已知寄生硅控整流器无法顺利开启的问题,并可降低静电放电保护装置的有效电阻。

6.根据本发明的一方面,提出一种静电放电保护装置,包括半导体衬底、第一阱区、第二阱区、第三阱区、第一掺杂区、第二掺杂区、第三掺杂区以及第四掺杂区。第一阱区、第二阱区及第三阱区位于半导体衬底之中,且第三阱区直接耦接于第一阱区及第二阱区之间。第一阱区及第二阱区具有第一电性,第三阱区具有第二电性。第一掺杂区具有第一电性,位于第一阱区之中。第二掺杂区具有第二电性,位于第三阱区之中,且第一掺杂区与第二掺杂区彼此隔离。第三掺杂区及第四掺杂区分别具有第一电性及第二电性,且位于第二阱区之中彼此隔离,第二掺杂区与第三掺杂区电性耦接。第一阱区、第二阱区、第三阱区及第四掺杂区形成一寄生硅控整流器。

7.根据本发明的一方面,提出一种静电放电保护装置的操作方法,包括下列步骤。提供一静电放电保护装置,静电放电保护装置与一内部电路电性连接,静电放电保护装置包括一寄生硅控整流器与一二极管串彼此相连。当一静电放电应力施加于内部电路时,通过静电放电保护装置将静电放电电流由一焊垫导入另一焊垫。

8.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

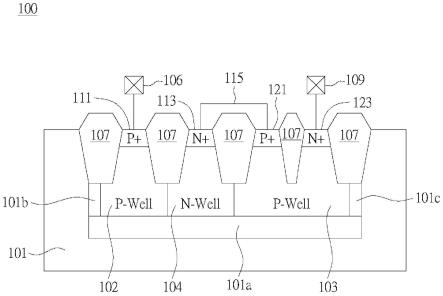

9.图1a绘示依照本发明一实施例的静电放电保护装置的剖面示意图;

10.图1b绘示图1a的静电放电保护装置的等效电路的示意图;

11.图2a绘示依照本发明另一实施例的静电放电保护装置的剖面示意图;

12.图2b绘示图2a的静电放电保护装置的等效电路的示意图;

13.图3a绘示依照本发明另一实施例的静电放电保护装置的剖面示意图;

14.图3b绘示图3a的静电放电保护装置的等效电路的示意图;及

15.图4绘示一比较例的静电放电保护装置的剖面示意图。

16.【符号说明】

17.100,200,300,400:静电放电保护装置

18.101:半导体衬底

19.101a:深n-阱区

20.101b:n-阱区

21.101c:n-阱区

22.102:第一阱区

23.103:第二阱区

24.104:第三阱区

25.106,109:焊垫

26.107:隔离体

27.111,211,311:第一掺杂区

28.113,313:第二掺杂区

29.115:金属导线

30.121,321:第三掺杂区

31.123:第四掺杂区

32.112,116,212,214,312,314:二极管

33.114,414:二极管串

34.118,218,318,418:寄生硅控整流器

35.316:接面

具体实施方式

36.以下系提出实施例进行详细说明,实施例仅用以作为示例说明,并非用以限缩本发明的保护范围。以下是以相同/类似的符号表示相同/类似的元件做说明。

37.第一实施例

38.请参照图1a及图1b,其分别绘示依照本发明一实施例的静电放电保护装置100的剖面示意图及其等效电路的示意图。

39.依照本发明的一实施例,静电放电保护装置100包括一半导体衬底101、第一阱区102、第二阱区103、第三阱区104、第一掺杂区111、第二掺杂区113、第三掺杂区121以及第四掺杂区123。

40.在一实施例中,半导体衬底101可以由任何适合的基础半导体(例如结晶态的硅或锗)、化合物半导体(例如碳化硅、砷化镓、磷化镓、磷化碘、砷化碘和/或锑化碘)或上述的组合所构成。半导体衬底101例如为一p型衬底。半导体衬底101中包括具有p型电性的第一阱

区102及第二阱区103以及具有n型电性的第三阱区104,其中第三阱区104耦接于第一阱区102及第二阱区103之间。此外,半导体衬底101与第一阱区102、第二阱区103及第三阱区104之间例如以深n-阱区101a相隔离。除此之外,半导体衬底101与第一阱区102之间例如以n-阱区101b相隔离,且半导体衬底101与第二阱区103之间例如以n-阱区101c相隔离。

41.第一掺杂区111具有p型电性,且位于第一阱区102之中。第一掺杂区111具有实质大于第一阱区102的掺杂浓度(以p+表示之)。第二掺杂区113具有n型电性,且位于第三阱区104之中,第二掺杂区113具有实质大于第三阱区104的掺杂浓度(以n+表示之)。在一实施例中,第一掺杂区111与第二掺杂区113可分别具有10

15

/cm2的掺杂浓度。第一阱区102及第三阱区104可具有10

13

/cm2的掺杂浓度。

42.第一掺杂区111可通过一焊垫106连接至电压源105。在一般电压操作时(例如,操作电压约2v),电压可通过电压源105施加至第一掺杂区111。多个隔离体107可分别配置于静电放电保护装置100中,隔离体107例如位于第一掺杂区111与第二掺杂区113之间、第二掺杂区113与第三掺杂区121之间、第三掺杂区121与第四掺杂区123之间,以实行其电性隔离的功能。

43.第三掺杂区121具有p型电性,且位于第二阱区103之中。第三掺杂区121具有实质大于第二阱区103的掺杂浓度(以p+表示之)。第四掺杂区123具有n型电性,且位于第二阱区103之中。第四掺杂区123具有实质大于第二阱区103的掺杂浓度(以n+表示之)。在一实施例中,第三掺杂区121与第四掺杂区123可分别具有10

15

/cm2的掺杂浓度,第二阱区103可具有10

13

/cm2的掺杂浓度。

44.由图1a及图1b可知,第二掺杂区113及第三掺杂区121以一金属导线115电性耦接。第一阱区102及第三阱区104彼此直接连接且接触以形成一二极管112,第二阱区103及第四掺杂区123彼此直接连接且接触以形成另一二极管116,二个二极管通过一金属导线115电性耦接而形成一二极管串114。也就是说,静电放电电流可由焊垫106经由第一掺杂区111流入二极管串114,再导入焊垫109,以保护集成电路中的内部电路免于遭受静电放电的损害。

45.此外,请参照图1a及图1b,第一阱区102、第三阱区104及第二阱区103形成一个具有p型多数载子(majority carrier)的pnp双极晶体管(bipolar junction transistor,bjt)寄生电路。第三阱区104、第二阱区103及第四掺杂区123形成一个具有n型多数载子的npn双极晶体管寄生电路。pnp双极晶体管寄生电路的集极(collector)和npn双极晶体管寄生电路的基极(base)连接;且pnp双极晶体管寄生电路的基极和npn双极晶体管寄生电路的集极连接,进而在半导体衬底101中构成一寄生硅控整流器118。在静电放电保护装置100之中,第一掺杂区111为寄生硅控整流器118的阳极(anode),而第四掺杂区123为寄生硅控整流器118的阴极(cathode)。

46.在一实施例中,当静电放电应力(esd stress)施加于内部电路时,静电放电应力透过两个顺向二极管112、116由焊垫106流向焊垫109,焊垫106为pnp晶体管的基极-射极,焊垫109为npn晶体管的基极-射极,焊垫106与109顺向开启的同时,进而使寄生硅控整流器118开启(turn on),无须通过崩溃产生电子电洞。因此,静电放电电流除了流入二极管串114之外,更可由焊垫106经由第一掺杂区111流入寄生硅控整流器118,并经由第四掺杂区123导入焊垫109。

47.请参照图4,其绘示一比较例的静电放电保护装置400的剖面示意图,比较例相较

于第一实施例不具有耦接于第一阱区102与第二阱区103之间的第三阱区104,虽然在比较例的半导体衬底中可构成一寄生硅控整流器418(p+/n-阱区/p-阱区/n-阱区),但是其中之一的二极管(p+/n-well)并非寄生硅控整流器418中npn晶体管(n-well/p-well/n-well)的基极-射极,因此二极管串414开启时,寄生硅控整流器418无法顺利开启(turn on)。在本实施例中,半导体衬底101中构成一寄生硅控整流器118(p-阱区/n-阱区/p-阱区/n+),且寄生硅控整流器118与二极管串114并联而提供二个静电放电路径,提高电流分路(current shunting)能力,使静电放电的有效电路路径增长,静电放电保护装置100的有效电阻降低,不须额外地提供占用较大布局空间的另一个静电放电保护元件,以减少集成电路的整体布局尺寸。

48.第二实施例

49.请参照图2a及图2b,其分别绘示依照本发明另一实施例的静电放电保护装置200的剖面示意图及其等效电路的示意图。静电放电保护装置200的结构是类似于图1a所示的静电放电保护装置100的结构,除了第一掺杂区211的一部分位于第一阱区102,第一掺杂区211的另一部分位于第三阱区104。第一掺杂区211类似于第一掺杂区111。

50.在静电放电保护装置200中,具有2个并联的二极管,其通过第一阱区102及第三阱区104耦接而形成一二极管212,并通过第一掺杂区211及第三阱区104耦接而形成另一二极管214,进而使静电放电的有效电路路径增长。

51.此外,当静电放电应力施加于受静电放电保护装置200保护的内部电路时,静电放电电流除了流入二极管串212、214及116之外,更可由焊垫106经由第一掺杂区211分别流入第一阱区102及第三阱区104,其中第一阱区102、第三阱区104、第二阱区103及第四掺杂区123构成一寄生硅控整流器218的第一分路,而第一掺杂区211、第三阱区104、第二阱区103及第四掺杂区123构成寄生硅控整流器218的第二分路,第一分路及第二分路并联,进而使静电放电的有效电路路径增长,之后,静电放电电流经由第四掺杂区123导入焊垫109。

52.在本实施例中,寄生硅控整流器218的第二分路包括由第一掺杂区211、第三阱区104及第二阱区103形成的一pnp双极晶体管寄生电路以及由第三阱区104、第二阱区103及第四掺杂区123形成的一npn双极晶体管寄生电路。pnp双极晶体管寄生电路的集极(collector)和npn双极晶体管寄生电路的基极(base)连接;且pnp双极晶体管寄生电路的基极和npn双极晶体管寄生电路的集极连接,进而在半导体衬底101中构成寄生硅控整流器218的第二分路,以提高电流分路能力。

53.请参照图4,比较例相较于第二实施例不具有耦接于第一阱区102与第二阱区103之间的第三阱区104,虽然在比较例的半导体衬底中可构成一寄生硅控整流器418(p+/n-阱区/p-阱区/n-阱区),但是其中之一的二极管(p+/n-well)并非寄生硅控整流器418中npn晶体管(n-well/p-well/n-well)的基极-射极,因此当二极管串414(p+/n-阱区及另一个p+/n-阱区)开启时,寄生硅控整流器418无法正常开启(turn on)。在本实施例中,半导体衬底101中构成具有二分路的寄生硅控整流器218(p-阱区/n-阱区/p-阱区/n+以及p+/n-阱区/p-阱区/n+),且寄生硅控整流器218与二极管串212、214、116并联而提供二个或更多静电放电路径,提高电流分路(current shunting)能力,使静电放电的有效电路路径增长,静电放电保护装置200的有效电阻降低,不须额外地提供占用较大布局空间的另一个静电放电保护元件,以减少集成电路的整体布局尺寸。

54.第三实施例

55.请参照图3a及图3b,其分别绘示依照本发明另一实施例的静电放电保护装置的剖面示意图及其等效电路的示意图。静电放电保护装置300的结构是类似于图1a所示的静电放电保护装置100的结构,除了第一掺杂区311的一部分位于第一阱区102,第一掺杂区311的另一部分位于第三阱区104,且第二掺杂区313与第三掺杂区321彼此直接连接而形成一接面316。第一掺杂区311、第二掺杂区313与第三掺杂区321类似于第一掺杂区111、第二掺杂区113与第三掺杂区121。

56.在静电放电保护装置300中,具有2个并联的二极管,其通过第一阱区102及第三阱区104耦接而形成一二极管312,并通过第一掺杂区311及第三阱区104耦接而形成另一二极管314,进而使静电放电的有效电路路径增长。此外,移除第二阱区103与第三阱区104之间的隔离体之后,第二掺杂区313与第三掺杂区321彼此直接连接而形成一接面316,因此可减少静电放电保护装置300占用较大布局空间,以减少集成电路的整体布局尺寸。

57.此外,当静电放电应力施加于受静电放电保护装置300保护的内部电路时,静电放电电流除了流入二极管串312、314、116之外,更可由焊垫106经由第一掺杂区311分别流入第一阱区102及第三阱区104,其中第一阱区102、第三阱区104、第二阱区103及第四掺杂区123构成一寄生硅控整流器318的第一分路,而第一掺杂区311、第三阱区104、第二阱区103及第四掺杂区123构成寄生硅控整流器318的第二分路,第一分路与第二分路并联,进而使静电放电的有效电路路径增长,之后,静电放电电流经由第四掺杂区123导入焊垫109。

58.请参照图4,比较例相对于第三实施例不具有耦接于第一阱区102与第二阱区103之间的第三阱区104且第二掺杂区313与第三掺杂区321未形成一接面316,虽然在比较例的半导体衬底中可构成一寄生硅控整流器418(p+/n-阱区/p-阱区/n-阱区),但是其中之一的二极管(p+/n-well)并非寄生硅控整流器418中npn晶体管(n-well/p-well/n-well)的基极-射极,因此当二极管串414(p+/n-阱区及另一个p+/n-阱区)开启时,寄生硅控整流器418无法顺利开启(turn on)。在本实施例中,半导体衬底101中构成具有二分路的寄生硅控整流器318(p-阱区/n-阱区/p-阱区/n+以及p+/n-阱区/p-阱区/n+),且寄生硅控整流器318与二极管串312、314、116并联而提供二个或更多静电放电路径,提高电流分路能力,使静电放电的有效电路路径增长,静电放电保护装置300的有效电阻降低,不须额外地提供占用较大布局空间的另一个静电放电保护元件,以减少集成电路的整体布局尺寸。

59.至此,已经结合附图对本公开实施例进行了详细描述。

60.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1