一种高耐压低漏电的Ga2O3肖特基势垒二极管

一种高耐压低漏电的ga2o3肖特基势垒二极管

技术领域

1.本发明涉及一种肖特基二极管,尤其涉及一种具有沟槽的ga2o3肖特基势垒二极管。

背景技术:

2.氧化镓(ga2o3)作为新一代宽禁带半导体材料,因其优异的物理及化学性质,得到了研究人员的广泛关注。ga2o3带隙为4.7~4.9ev,临界击穿电场高达8mv

·

cm

‑1,巴利加优值约为3400,是sic和gan的10倍和4倍。可通过提拉法(cz)、悬浮区熔法(fz)、vertical bridgman和边缘定义膜生长等多种方法制备,获得大尺寸、低成本氧化镓单晶。

3.功率器件是最能发挥ga2o3优势的应用领域,目前对于ga2o3功率器件的研究主要集中在肖特基势垒二极管(sbd)、场效应晶体管(fet)、异质结二极管的结构设计及器件制备方面。由于ga2o3仍无法进行有效的p型掺杂,目前的sbd多采用场板等终端来进行器件的电场优化。2017年6月keita konishi等制备了耐压超过1kv、导通电阻5.1mω.cm2的垂直场板ga2o

3 sbd,2018年10月zhuangzhuang hu等设计了耐压超过3kv的横向场板ga2o

3 sbd。2020年西安电子科技大学的周弘、电子科技大学罗小蓉、以及南京大学的叶建东等分别制备了结型sbd二极管、复合终端sbd二极管和异质结二极管。然而器件方向关断状态下在肖特基电极附近会出现高电场、大泄漏电流,严重限制了ga2o3基功率器件低关态损耗的优势。2018年wenshen li等基于降低表面电场(resurf)技术,改善了肖特基电极的电场分布,实现了漏电流为1μa/cm2,反向击穿电压2.44kv的ga2o

3 sbd。但resurf技术会导致电场集中在沟道底部,因此,沟道底部的电场分布及结构优化是进一步提高器件耐压能力的关键。

4.在中国专利cn109075214a中公开了沟槽mos型肖特基势垒二极管,并具体公开了:沟槽mos型肖特基势垒二极管的第2半导体层具有在面上开口的沟槽。在沟槽的底部埋入绝缘体,绝缘膜覆盖绝缘体的上表面和沟槽的内侧侧面。沟槽mos栅极埋入于沟槽内,从而被绝缘膜覆盖。例如,在沟槽的底部埋入绝缘体后,通过蚀刻将绝缘体的上部削成弧形,形成沟槽。然后,在沟槽内形成绝缘膜和沟槽mos栅极。沟槽的底面可以是平坦的,可以如沟槽那样成为弧形。上述专利中认为:沟槽型mos型肖特基势垒二极管中的电场强度会受相邻的2个沟槽之间的台面形状部分的宽度、沟槽的深度、绝缘膜的厚度的影响,但几乎不受沟槽的平面图案的影响。并且,通过实验验证了绝缘膜的介电常数、绝缘膜厚度、第2半导体层厚度以及台面形状部分的1/2宽度对第2半导体层中电场强度最大的点p1、绝缘膜中最大电场强度最大的点p2,以及第2半导体层的阳极电极正下方区域中的最大电场强度最大的点p3处的电场的影响。但是上述专利中的结构设置依然达不到更大的反向击穿电压,无法充分实现器件耐高压的优势。

技术实现要素:

5.本发明的目的在于提供一种通过结构设计达到高耐压、低阻抗、低漏电且工艺兼容性好的ga2o3肖特基势垒二极管。

6.为了达到上述目的,本发明是这样实现的:一种高耐压低漏电的ga2o3肖特基势垒二极管,包括位于底部的阴极电极,位于所述阴极电极上部的衬底,位于所述衬底上部的漂移层,其特征在于:在所述漂移层的背离衬底的面设置有沟槽,所述沟槽具有底壁以及两侧壁,所述底壁与侧壁的转角处设置圆角;在所述沟槽表面覆盖有随形的al2o3介电层,在所述介电层表面覆盖有随形的欧姆接触层,在所述漂移层的背离衬底的面上设置有肖特基栅;其中,所述衬底材料为si重掺杂的ga2o3,所述漂移层材料为si轻掺杂的ga2o3。

7.其中,所述圆角半径r≥0.4μm。优选的,所述圆角半径r为0.6

‑

1.2μm。

8.其中,相邻沟槽顶部的漂移层的宽度为台面宽度w,所述台面宽度w为1

‑

4μm。优选的,所述台面宽度为1

‑

2μm。

9.其中,所述沟道底面未设置圆角的平面长度为横板长度,所述横板长度k为0.2

‑

4μm。优选的,所述横板长度k为0.8

‑

0.9μm。

10.优选的,所述欧姆接触层的材质为ti/au。

11.优选的,所述介电层材料为al2o3,沟槽的结构参数为w=1μm,k=0.8

‑

0.9μm,r=0.6μm。

12.优选的,所述介电层材料为al2o3,沟槽的结构参数为w=2μm,k=0.8

‑

0.9μm,r=0.9μm。

13.有益效果:

14.本发明的ga2o3肖特基势垒二极管,使用al2o3做介电层,对沟槽底部进行了特殊的结构设计:保持沟槽底壁中部的平面段且在沟槽底壁与沟槽侧壁的转角处设计圆角。这样一来,使得沟槽底壁电场强度降低,而电场强度的峰值转移到沟槽底部的两个圆角处,然后优化沟槽底壁中部的平面段长度进一步降低圆角间的叠加场强,有效缓解圆角处的电场集中,极大地提高了本发明肖特基势垒二极管的反向击穿电压。同时,器件外加反向偏压时,沟槽拐角的介电层内会集中大量的电场,设计随形(圆角)的介电层和欧姆接触层,使得靠近阳极的介电层电场分布更加均匀,避免发生介电层击穿。

15.第二,减小台面宽度也可以缓解沟槽拐角的电场集中,提高击穿电压,但会造成电流通道变窄而引起导通电阻大幅增加,进而可能导致器件因过热而损坏。而圆角优化降低了高击穿电压对台面宽度的要求,降低了导通电阻。

16.第三,使用ti/au作为沟槽侧壁的金属层,ti的功函数(4.33ev)接近ga2o3的电子亲和力(4ev),可缓解沟槽侧壁与ga2o3的功函数差造成的电子通道耗尽,降低器件的导通电阻。进一步避免因器件过热导致的烧毁,同时降低了器件的损耗。

17.第四,沟槽底壁与沟槽侧壁的转角处设计圆角与当前的集成制造工艺具有较好的工艺兼容性,可以使用刻蚀和原子层沉积等方法较好的实现圆角半径及表面形貌质量的控制。

18.尤其地:介电层材料采用al2o3,结构参数为w=1μm,k=0.8

‑

0.9μm,r=0.6μm时的肖特基势垒二极管的击穿电压超过3332v,品质因数达1.76gw

·

cm

‑2;结构参数为w=2μm、r=0.9μmk=0.8

‑

0.9μm时,al2o3介电层的击穿电压接近3242v,品质因数高达1.95gw

·

cm

‑2。这个理论预测的品质因素是目前实验制备器件最高品质因素的两倍,目前实验制备器件最高品质因素来自于2020年10月西安电子科技大学的异质结sbd器件(ieee transactions on power electronics,vol.36,no.6,june 2021)。

附图说明

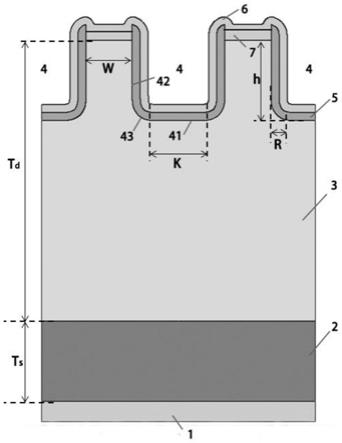

19.图1a为实施例中ga2o3基肖特基势垒二极管的剖视图;

20.图1b为实施例中ga2o3基肖特基势垒二极管的俯视图一;

21.图1c为实施例中ga2o3基肖特基势垒二极管的俯视图二;

22.图2为实施例中ga2o3基肖特基势垒二极管沟槽处放大图;

23.图3a为采用sio2作为介电层材料时图2中a点和b点的电场强度;

24.图3b为采用hfo2作为介电层材料时图2中a点和b点的电场强度;

25.图3c为采用al2o3作为介电层材料时图2中a点和b点的电场强度;

26.图4为al2o3介电层的ga2o3肖特基势垒二极管的正向i

‑

v特性曲线和正向导通电阻(r

on

);

27.图5为不同圆角半径r下的击穿电压;

28.图6a中示出了四种台面宽度(w=1μm/2μm/3μm/4μm)、圆角半径r取对应台面宽度的最优值时,横板长度k对介电层击穿电压的影响;

29.图6b示出了四种台面宽度(w=1μm/2μm/3μm/4μm)时,不同横板长度k所对应的导通电阻r

on

;

30.图6c中示出了四种台面宽度(w=1μm/2μm/3μm/4μm)时,品质因素(fom)随横板长度k的变化;

31.图7为基于优化的结构参数给出的器件在反向偏压下的泄漏电流曲线;

32.图8a

‑

8f为实施例还中制造实例一和例二的ga2o3沟道sbd的工艺过程中每一步骤的示意图。

具体实施方式

33.下面结合附图对本发明的具体实施方式作进一步详细的说明,但本发明并不局限于这些实施方式,任何在本实施例基本精神上的改进或代替,仍属于本发明权利要求所要求保护的范围。

34.实施例:本实施例将提供一种高耐压低漏电的ga2o3基肖特基势垒二极管,见剖视图1a和俯视图1b、图1c。本实施例的ga2o3肖特基势垒二极管由下至上包括阴极电极1、位于所述阴极电极电极上部的衬底2,位于所述衬底上部的漂移层3,在所述漂移层3的背离衬底2的面设置有沟槽4,所述沟槽具有底壁41以及两侧壁42,所述底壁与侧壁的转角处设置圆角43;在所述沟槽表面覆盖有随形的介电层5,在所述介电层表面覆盖有随形的欧姆接触层6,在所述漂移层的背离衬底的面上设置有肖特基极7。

35.在本实施例中,所述阴极电极的材料可采用ti/au,所述衬底材料可为si重参杂的ga2o3衬底,所述漂移层材料可为si轻掺杂的ga2o3,所述介电层材料为al2o3,所述欧姆接触层材料可采用ti/au,所述肖特基接触材料可采用pt,所述阳极电极材料为ti/au。

36.本实施例的al2o3介电层结构的ga2o3肖特基势垒二极管,对沟槽底部进行了特殊的结构设计:保持沟槽底壁中部的平面段且在沟槽底壁与沟槽侧壁的转角处设计圆角。这样一来,使得沟槽底壁电场强度降低,而电场强度峰值出现在沟槽底壁与侧壁转角的两圆角处;通过圆角的设计和优化进一步降低电场强度有效地缓解了电场集中,而通过设计两处圆角共同承担反向电压,极大地提高了本发明肖特基势垒二极管的反向击穿电压。器件

外加反向偏压时,沟槽拐角的介电层内会集中大量的电场,设计随形(圆角)的介电层和欧姆接触层,使得靠近阳极的介电层电场分布更加均匀,避免发生介电层击穿。

37.对于沟道型ga2o3肖特基势垒二极管而言,沟槽底壁与侧壁的转角处电场分布比较集中,是最容易发生击穿的区域。所以重点考虑转角处氧化镓漂移层和介电层的击穿,只需降低此处的电场集中,便能提高肖特基势垒二极管的耐高压能力。为评估沟槽底壁与侧壁的转角处的电场优化,典型地取沟槽处漂移层a点的电场强度(e),取沟槽处介电层b点的电场强度(e),见图2。分别采用sio2、hfo2和al2o3作为介电层材料,对比研究a点和b点处在不同介电层材料时的电场强度,对比研究结果见图3a,3b,3c。通过对比,研究发现介电层的类型对沟槽处的圆角半径r(rounded corner radius/r(μm))的优化效果产生极大影响。如图3a,优化前后,sio2介电层e(b)得到最大降幅,但仍然远高于其临界值,器件的击穿电压依旧很低,击穿性能被sio2介电层严重阻碍。al2o3介电层的e(b)经圆角优化后产生22mv/cm的超高降幅,下跌至远低于其临界击穿场强,成功实现器件的更高击穿电压,见图3b。高k介电层hfo2经圆角优化的e(b)降幅很小的情况下,依靠其不低的临界击穿场强已经获得极高的击穿电压,如图3c所示。然而,hfo2与ga2o3界面的负固定电荷高达1.04

×

10

13

cm

‑2,台面漂移区以及增加附加散射的强度被严重耗尽,造成器件导通电阻过大。因hfo2/ga2o3接触界面存在晶格适配问题,因此本发明中将al2o3作为介电层在沟型ga2o3肖特基势垒二极管有最佳的性能。

38.进一步,本实施例采用tcad工具对基于al2o3介电层的ga2o3肖特基势垒二极管进行了研究,构建沟槽型sbd结构;研究不同的r、w、k对击穿电压的影响。其中,构建的沟道型sbd结构的衬底厚度t

s

取0.4μm,漂移层厚度t

d

取10μm,衬底和漂移层的掺杂浓度分别为2.6x10

18

cm

‑3和2x10

16

cm

‑3,介电层厚度t

0x

取0.1μm,沟道高度h取1.55μm。ga2o3材料的带隙和电子亲和力分别设置为4.8ev和4.0ev,离化计算使用α(e)=0.79

×

106cm

‑1exp[

‑

(2.92

×

107v/cm)/e]。此外,为进一步评估sbd的功率品质因素(p

‑

fom),设置台面区域的迁移率为50cm2/v.s,其中考虑沟道刻蚀损伤和al2o3/ga2o3界面电荷造成的附加散射,设置其余漂移层的迁移率为100cm2/v.s的实验值,提取器件的正向i

‑

v特性曲线和正向导通电阻(r

on

),数据及结果见图4。电极使用pt,功函数为5.65ev。al2o3介电层材料采用相对介电常数9,临界击穿场强取8.7mv cm

‑1。

[0039]

具体的设计,主要通过改变沟道底部圆角半径r和横板长度k,模拟计算sbd器件的电场分布和击穿性能。沟道宽度w分别取1μm、2μm、3μm和4μm 4种情况,圆角半径r总体变化范围为0μm

‑

1.4μm,观察圆角半径r在不同沟道宽度w下对击穿电压的影响,找到较为合适的圆角半径r结构参数。然后,选择合适的圆角半径r,对沟道横板长度k进行优化,横板长度k的范围设置为0.1μm

‑

4μm。最后,为了进一步研究器件的结构参数对器件性能的影响,我们引入表征功率器件性能的参数功率品质因数(p

‑

fom)。利用公式(1)计算器件的功率品质因数,其中式(1)中的r

on

是导通电阻、bv是击穿电压。

[0040]

fom=bv2/r

on

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0041]

第一步:研究沟道底部圆角半径r的优化对击穿电压的影响

[0042]

设横板长度k为固定值4μm,仿真的圆角半径r=0μm

‑

1.4μm范围下的击穿电压。图5示出了不同圆角半径r下的击穿电压。从图中可以看出,圆角半径大于0.1μm后,击穿电压迅速提升,圆角半径大于0.6μm后趋于稳定。将击穿电压转折点所对应的圆角半径定义为器件

结构的最优半径。随着台面宽度w增加,器件的最优半径相应增大,对应台面宽度1um、2um、3um和4um的最优半径分别为0.6um、0.9um、1.1um和1.2um。此外,当台面宽度等于1um,圆角半径高于0.6um时,器件的击穿电压高达3400v。

[0043]

第二步:研究沟道底壁横板长度k的优化对器件击穿电压的影响

[0044]

为了保证对圆角优化效果充分利用,需要继续优化底部横板长度k,从而实现最优化的结构设计。

[0045]

(1)横板长度k对击穿电压的影响

[0046]

图6a中示出了四种台面宽度(w=1μm/2μm/3μm/4μm)、圆角半径r取对应台面宽度的最优值时,横板长度k对介电层击穿电压的影响;图6b示出了四种台面宽度(w=1μm/2μm/3μm/4μm)时,不同横板长度k所对应的导通电阻r

on

。进一步,图6c中示出了四种台面宽度(w=1μm/2μm/3μm/4μm)时,品质因素(fom)随横板长度k的变化。根据图6a、图6b和图6c可得知,当w=1μm、r=0.6μm、k=0.8

‑

0.9μm时,器件击穿电压高达3332v,导通电阻6.3mω.cm2,品质因数为1.75gw

·

cm

‑2。当w=2μm、r=0.9μm横板长度k=0.8

‑

0.9μm时,器件击穿电压3242v,导通电阻5.4mω.cm2,品质因数高达1.95gw

·

cm

‑2。最后,基于优化的结构参数给出了器件在反向偏压下的泄漏电流曲线,见图7,当w=1

‑

2μm时,泄漏电流低于1pa/cm2,可见反向偏压下极低的泄漏电流特性。

[0047]

实例一

[0048]

介电层材料al2o3圆角半径r/μm0.6台面宽度w/μm1横板长度k/μm0.8

‑

0.9反向击穿电压v3332导通电阻mω.cm26.3品质因素fom/gw.cm

‑21.76泄漏电流低于1pa/cm2[0049]

实例二

[0050][0051][0052]

另外,本实施例还提供一种制造实例一和例二的ga2o3沟道sbd的工艺过程及制造

方法,参见图8a

‑

8f。包括以下步骤:

[0053]

步骤(1):外延ga2o3轻掺杂漂移层,利用反应离子刻蚀工艺(bl3和ar)刻蚀衬底背面,蒸镀ti/au欧姆电极;

[0054]

步骤(2):在漂移层的背向衬底的一面,沉积pt肖特基栅,利用光刻技术,刻蚀掉其他金属层部分,留下如图8b的pt层;

[0055]

步骤(3):在相邻pt层之间采用光刻技术形成沟道,先利用选择性腔的干法刻蚀出大概的沟道雏形,再利用各向同性强的湿法刻蚀形成沟槽圆角;

[0056]

步骤(4):在在漂移层的背向衬底的一侧的所有表面(包括pt肖特基栅表面)利用热原子层沉积工艺(ald)沉积高质量的al2o3介电层;

[0057]

步骤(5):利用反应离子刻蚀与光刻工艺去掉pt电极上表面的al2o3材料;

[0058]

步骤(6):在所有介电层表面沉积ti/au金属层作为欧姆接触层并连接肖特基栅pt。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1