一种智能型超结MOS器件及其制造方法与流程

一种智能型超结mos器件及其制造方法

技术领域

1.本发明涉及智能型超结mos器件领域,更具体地说,它涉及一种智能型超结mos器件及其制造方法。

背景技术:

2.智能型超结mos器件产品是在普通超结产品的基础上,集成了采样mos、启动mos、高阻r,或者只集成采样mos与启动mos中的一个mos,普通超结与智能型超结电路示意图对比见图13。可以看到,智能型超结mos器件产品,在同一颗芯片上,会有2~3个mos,应用电路要求mos间功能独立,工作状态下互不影响;

3.超结产品是由多组p型掺杂区柱和n型掺杂区柱交替连接构成,因此采样mos、启动mos的隔离设计中,p型掺杂区柱和n型掺杂区柱如何排列不仅仅影响到mos间隔离电压、还会影响管芯的耐压;

4.图11和12为现有技术的超结mos隔离设计,仅将p型掺杂区柱和n型掺杂区柱进行简单的纵横交叉的排布,此种设计可以满足管芯耐压要求,但是mos间隔离电压只有不到10v,耐压曲线几乎为阻性曲线,经分析,此种设计时,采样mos、启动mos的有源区在经过工艺高温退火过程后,与主mos的有源区是相连的,因此,mos间并没有真正的隔离,所以隔离电压非常低。

技术实现要素:

5.本发明的目的是提供一种智能型超结mos器件及其制造方法,经过工艺高温退火,也仍然可以保证功能mos有源区的独立性,可以保证超高的隔离电压。

6.本发明的上述技术目的是通过以下技术方案得以实现的:一种智能型超结mos器件,其特征是:包括集成连接在一个芯片上的主mos和若干功能mos,所述功能mos设置在所述主mos的范围内,所述功能mos在芯片上的分布包括功能mos隔离区和功能mos有源区,所述功能mos有源区包括若干组相互平行且间隔设置的p型掺杂区柱和n型掺杂区柱,所述功能mos隔离区包括呈方形围绕在所述功能有源区外围的n型掺杂区柱和均匀点阵呈栅格状分布在n型掺杂区柱内部的p型掺杂区柱。

7.作为本发明的一种优选技术方案,所述主mos在芯片上的分布包括主mos终端区和设置在所述主mos终端区内部的主mos有源区;所述功能mos设置在所述主mos有源区的范围内。

8.作为本发明的一种优选技术方案,所述主mos终端区和主mos有源区分别包括若干组相互平行且间隔设置的p型掺杂区柱和n型掺杂区柱。

9.作为本发明的一种优选技术方案,所述功能mos之间的工作状态相互独立。

10.作为本发明的一种优选技术方案,若干功能mos之间相邻设置。

11.作为本发明的一种优选技术方案,所述功能mos包括采样mos和/或启动mos。

12.一种智能型超结mos器件的制造方法,包括如下步骤:

13.s1、在n型衬底片上生长形成n型掺杂外延层,注入n型掺杂物质,再选择性曝光,注入p型掺杂物质,得到单次外延片;

14.s2、重复上述外延生长和注入的步骤,最后一次外延只注入n型掺杂物质,得到多次外延片;

15.s3、对多次外延片进行氧化层和氮化层淀积,退火、刻去氧化层和氮化层,形成n型漂移区和p型柱区,得到p/n结构片;

16.s4、对p/n结构片进行场氧生长、光刻、场氧刻蚀,得到带有场氧的结构片;

17.s5、对场氧结构片进行栅极氧化、淀积多晶并进行掺杂、多晶光刻、多晶刻蚀,形成栅氧化层和多晶层,得到带有栅极的结构片;

18.s6、对带有栅极的结构片,选择性曝光后,注入p型掺杂物质,体区退火,形成p型体区,得到p型体区片;

19.s7、对p型体区片,进行n+光刻及n+推阱,形成mos器件的n+源极结构层,得到带有源极结构的结构片;

20.s8、对带有源极结构的结构片,生长spacer氧化层、刻蚀,在多晶侧壁形成spacer效果,得到带有p+自对准结构的结构片;

21.s9、对带有p+自对准结构的结构片,注入p型掺杂物质,得到带有p+结构的结构片;

22.s10、对带有p+结构的结构片,淀积介质,形成介质层,并进行光刻、刻蚀,在mos源区的位置开孔,得到带有通孔的结构片;

23.s11、对带有通孔的结构片进行金属沉积并光刻,形成金属层,得到具有金属层的结构片;

24.s12、对具有金属层的结构片进行钝化层淀积、光刻、刻蚀,形成栅极和源极的开口区,得到带有钝化层的结构片;

25.s13、对带有钝化层的结构片的背面进行减薄和蒸发ti

‑

ni

‑

ag的操作,形成蒸发层,得到智能型超结mos器件。

26.综上所述,本发明具有以下有益效果:功能mos隔离区设计为呈方形围绕在所述功能有源区外围的n型掺杂区柱和均匀点阵呈栅格状分布在n型掺杂区柱内部的p型掺杂区柱,这样的功能mos隔离区设计即使经过工艺高温退火,也仍然可以保证功能mos有源区的独立性;这样的设计也能为功能mos隔离区的呈方形阵列分布的p型掺杂区柱间多引入了一个方向的电荷平衡效应,使得电场分布更加平缓,因此可以保证超高的隔离电压。

附图说明

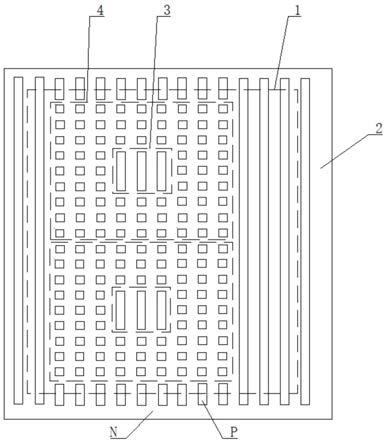

27.图1是本发明的智能型超结mos器件的p型掺杂区柱和n型掺杂区柱分布示意图;

28.图2是本发明的智能型超结mos器件的立体截面图;

29.图3是本发明的智能型超结mos器件的三种结构样式;

30.图4是本发明方法的单次外延片示意图;

31.图5是本发明方法的多次外延片示意图;

32.图6是本发明方法的p/n结构片示意图;

33.图7是本发明方法的带有栅极的结构片示意图;

34.图8是本发明方法的p型体区片片示意图;

35.图9是本发明方法的带有源极结构的结构片示意图;

36.图10是本发明方法的具有金属层的结构片示意图;

37.图11是现有技术的超结mos器件的设计图;

38.图12是现有技术的超结mos器件的立体截面图;

39.图13是普通超结与智能型超结电路对比示意图。

40.图中:1、主mos有源区;2、主mos终端区;3、功能mos有源区;4、功能mos隔离区;p、p型掺杂区柱;n、n型掺杂区柱。

具体实施方式

41.以下结合附图对本发明作进一步详细说明。

42.本发明提供一种智能型超结mos器件,如图1和2所示,包括集成连接在一个芯片上的主mos和若干功能mos,功能mos包括采样mos和/或启动mos。

43.主mos在芯片上的分布包括主mos终端区2和设置在主mos终端区2内部的主mos有源区1;功能mos设置在主mos有源区1的范围内,主mos终端区2和主mos有源区1分别包括若干组相互平行且间隔设置的p型掺杂区柱和n型掺杂区柱;

44.若干功能mos之间相邻设置,功能mos在芯片上的分布包括功能mos隔离区4和功能mos有源区3,功能mos有源区3包括若干组相互平行且间隔设置的p型掺杂区柱和n型掺杂区柱,功能mos隔离区4包括呈方形围绕在功能有源区外围的n型掺杂区柱和均匀点阵呈栅格状分布在n型掺杂区柱内部的p型掺杂区柱,功能mos之间的工作状态相互独立。

45.本发明的工作原理和优势为:功能mos隔离区4设计为呈方形围绕在所述功能有源区外围的n型掺杂区柱和均匀点阵呈栅格状分布在n型掺杂区柱内部的p型掺杂区柱,这样的功能mos隔离区4设计即使经过工艺高温退火,也仍然可以保证功能mos有源区3的独立性;这样的设计也能为功能mos隔离区4的呈方形阵列分布的p型掺杂区柱间多引入了一个方向的电荷平衡效应,使得电场分布更加平缓,因此可以保证超高的隔离电压。

46.本发明还提供一种智能型超结mos器件的制造方法,包括如下步骤:

47.s1、如图4所示,在n型衬底片上生长形成n型掺杂外延层,注入n型掺杂物质,再选择性曝光,注入p型掺杂物质,得到单次外延片;

48.s2、如图5所示,重复上述外延生长和注入的步骤,最后一次外延只注入n型掺杂物质,得到多次外延片;

49.s3、如图6所示,对多次外延片进行氧化层和氮化层淀积,退火、刻去氧化层和氮化层,形成n型漂移区和p型柱区,得到p/n结构片;

50.s4、对p/n结构片进行场氧生长、光刻、场氧刻蚀,得到带有场氧的结构片;

51.s5、如图7所示,对场氧结构片进行栅极氧化、淀积多晶并进行掺杂、多晶光刻、多晶刻蚀,形成栅氧化层和多晶层,得到带有栅极的结构片;

52.s6、如图8所示,对带有栅极的结构片,选择性曝光后,注入p型掺杂物质,体区退火,形成p型体区,得到p型体区片;

53.s7、如图9所示,对p型体区片,进行n+光刻及n+推阱,形成mos器件的n+源极结构层,得到带有源极结构的结构片;

54.s8、对带有源极结构的结构片,生长spacer氧化层、刻蚀,在多晶侧壁形成spacer

效果,得到带有p+自对准结构的结构片;

55.s9、对带有p+自对准结构的结构片,注入p型掺杂物质,得到带有p+结构的结构片;

56.s10、对带有p+结构的结构片,淀积介质,形成介质层,并进行光刻、刻蚀,在mos源区的位置开孔,得到带有通孔的结构片;

57.s11、如图10所示,对带有通孔的结构片进行金属沉积并光刻,形成金属层,得到具有金属层的结构片;

58.s12、对具有金属层的结构片进行钝化层淀积、光刻、刻蚀,形成栅极和源极的开口区,得到带有钝化层的结构片;

59.s13、对带有钝化层的结构片的背面进行减薄和蒸发ti

‑

ni

‑

ag的操作,形成蒸发层,得到智能型超结mos器件。

60.一般的,可根据不同的耐压和隔离需求,可以拓展为三种结构,如图3所示,以结构一为例,其具体的制造方法是:

61.s1、如图4所示,在n型衬底片上生长形成n型掺杂外延层,n型衬底片采用n型(100)晶向,砷元素掺杂,电阻率通常为0.001~0.005ω*cm,采用多次外延的方法生长高阻外延层,通常每层电阻率为15~40ω*cm,以第一层为例,生长一层5~10um的n型掺杂外延;再注入n型掺杂物质,用于扩散形成n型漂移区,注入能量:140keb~160kev,剂量:2e12~4e12,磷元素;对注入的n形掺杂物质进行选择性曝光,并注入p型掺杂物质,用于扩散形成p

‑

pillar,注入能量:50~70kev,注入剂量:6e12~8e12,硼元素,得到单次外延片。

62.s2、如图5所示,重复n型掺杂外延层的外延生长和n型掺杂物质、p型掺杂物质的注入过程至整体外延为50~70um,最后再生长一层n型掺杂外延,厚度3~8um,并且只注入n型掺杂物质,用于体区和源区注入,得到多次外延片。

63.s3、如图6所示,对多次外延片淀积一层1800埃~2400埃的sio2,通过pcvd淀积一层1000埃~1500埃的氮化硅,防止杂质扩散。然后进行p

‑

pillar退火,温度1180℃,时间根据单次外延层的厚度在150min~250min,气体氛围为氮气。通过湿法刻蚀将氮化硅去除,将sio2去除,形成n型漂移区和p型柱区,得到p/n结构片。

64.s4、在p/n结构片上生长场氧厚度8000埃~12000埃,并进行光刻,对有源区曝光&腐蚀,除主mos终端区及功能mos隔离区外,其余主mos有源区、采样mos有源区,启动mos有源区氧化层全部去除,得到带有场氧的结构片。

65.s5、如图7所示,对带有场氧的结构片生长栅氧化层厚度一般700

‑

1200埃,沉积多晶硅厚度6000

‑

8000埃并进行掺杂;再对多晶硅光刻和刻蚀,形成栅氧化层和多晶层,得到带有栅极的结构片。

66.s6、如图8所示,对带有栅极的结构片进行选择性曝光,p型掺杂物质注入剂量为3e13~6e13,注入能量:80kev~110kev,硼元素,注入后退火,1150℃,50~60min,杂质扩散形成p型体区,得到p型体区片。

67.s7、如图9所示,在p型体区片上进行n+光刻及n+推阱,形成主mos管源区,得到带有源极结构的结构片,其中np注入剂量:5e15~1e16,注入能量:40kev

‑

100kev,注入元素:磷。np推阱温度:850℃,时间:40~60分钟。

68.s8、对带有源极结构的结构片,生长一层spacer氧化层,厚度1000埃~1500埃,并使用干法刻蚀将氧化层去除,可以在poly侧壁形成spacer结果,做为p+注入的自对准结构,

得到带有p+自对准结构的结构片。

69.s9、对带有p+自对准结构的结构片进行p+注入,增加p

‑

body体区掺杂浓度,降低rb电阻,有助于提高mos的抗冲击能力,剂量:2e15~4e15,能量:120kev,硼元素,得到带有p+结构的结构片。

70.s10、对带有p+结构的结构片沉积介质bpsg(硼磷硅玻璃)10000埃,然后开孔,形成孔接触,得到带有通孔的结构片。

71.s11、如图10所示,对带有通孔的结构片沉积4um铝,然后光刻腐蚀铝,形成mos的栅区和源区,得到具有金属层的结构片。

72.s12、对具有金属层的结构片沉积钝化层氮化硅6000

‑

10000埃,然后光刻腐蚀,形成gate和source的开口区,得到带有钝化层的结构片。

73.s13、对带有钝化层的结构片减薄背面到200um

‑

300um,再在背面蒸发ti

‑

ni

‑

ag(钛

‑

镍

‑

银),最终得到智能型超结mos器件。

74.以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1