半导体装置及其制造方法与流程

半导体装置及其制造方法

1.相关申请

2.本技术基于2021年03月05日申请的在先日本专利申请第2021-035733号的优先权的利益,且谋求所述利益,内容整体以引用的方式包含于本文中。

技术领域

3.本实施方式涉及一种半导体装置及其制造方法。

背景技术:

4.在半导体装置的封装构造中,存储芯片等的半导体芯片设置于衬底上。理想的是封装小型化。

5.一个实施方式提供一种能使封装更小的半导体装置及其制造方法。

6.本实施方式的半导体装置具备第1积层体、第1柱状电极、第2积层体、及第2柱状电极。第1积层体由多个第1半导体芯片向垂直于积层方向的方向偏移且积层。第1柱状电极与第1半导体芯片的电极垫连接,沿第1半导体芯片的积层方向延伸。第2积层体由多个第2半导体芯片向垂直于积层方向的方向偏移并积层,且积层为比第1积层体更高,且,配置为从积层方向观察,与第1积层体的至少一部分重叠。第2柱状电极与第2半导体芯片的电极垫连接,沿第2半导体芯片的积层方向延伸。

7.根据所述构成,可提供一种能使封装更小的半导体装置及其制造方法。

技术实现要素:

附图说明

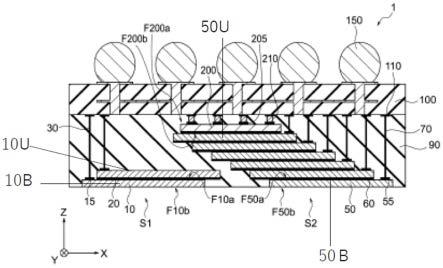

8.图1是表示第1实施方式的半导体装置的构成的一例的剖视图。

9.图2a是表示第1实施方式的半导体装置的构成的一例的剖视图。

10.图2b是表示第1实施方式的半导体装置的构成的一例的俯视图。

11.图3a是表示第1实施方式的半导体装置的制造方法的一例的剖视图。

12.图3b是表示继图3a后的半导体装置的制造方法的一例的剖视图。

13.图3c是表示继图3b后的半导体装置的制造方法的一例的剖视图。

14.图3d是表示继图3c后的半导体装置的制造方法的一例的剖视图。

15.图3e是表示继图3d后的半导体装置的制造方法的一例的剖视图。

16.图4是表示第1比较例的半导体装置的构成的一例的剖视图。

17.图5是表示第2比较例的半导体装置的构成的一例的剖视图。

18.图6a是表示第1实施方式的第1变化例的半导体装置的构成的一例的剖视图。

19.图6b是表示第1实施方式的第1变化例的半导体装置的构成的一例的俯视图。

20.图7a是表示第1实施方式的第2变化例的半导体装置的构成的一例的剖视图。

21.图7b是表示第1实施方式的第3变化例的半导体装置的构成的一例的剖视图。

22.图8a是表示第1实施方式的第4变化例的半导体装置的构成的一例的剖视图。

23.图8b是表示第1实施方式的第5变化例的半导体装置的构成的一例的剖视图。

24.图9a是表示第1实施方式的第6变化例的半导体装置的构成的一例的剖视图。

25.图9b是表示第1实施方式的第7变化例的半导体装置的构成的一例的剖视图。

26.图10是表示第2实施方式的半导体装置的构成的一例的剖视图。

27.图11是表示第2实施方式的变化例的半导体装置的构成的一例的剖视图。

28.图12是表示第3实施方式的半导体装置的构成的一例的剖视图。

29.图13a是表示第3实施方式的半导体装置的制造方法的一例的剖视图。

30.图13b是表示继图13a后的半导体装置的制造方法的一例的剖视图。

31.图13c是表示继图13b后的半导体装置的制造方法的一例的剖视图。

32.图13d是表示继图13c后的半导体装置的制造方法的一例的剖视图。

33.图14是表示第4实施方式的半导体装置的构成的一例的剖视图。

34.图15是表示第4实施方式的第1变化例的半导体装置的构成的一例的剖视图。

35.图16是表示第4实施方式的第2变化例的半导体装置的构成的一例的剖视图。

36.图17是表示第4实施方式的第3变化例的半导体装置的构成的一例的剖视图。

37.图18是表示第5实施方式的半导体装置的构成的一例的剖视图。

38.图19是表示第5实施方式的积层体及虚设芯片的构成的一例的立体图。

具体实施方式

39.以下,参照附图说明本发明的实施方式。本实施方式并非限定本发明。以下实施方式中,上下方向有时表示将半导体芯片的积层方向设为上或下的情况的相对方向,与根据重力加速度的上下方向不同。附图为示意性或概念性的附图,各部分的比例等未必与实物相同。在说明书与附图中,对与已出现的附图相关描述的内容同样的要件,标注相同符号且适当省略详细说明。

40.(第1实施方式)

41.图1是表示第1实施方式的半导体装置1的构成的一例的剖视图。半导体装置1具备积层体s1、柱状电极30、积层体s2、柱状电极70、半导体芯片200、连接柱210、树脂层90、再布线层100、及金属凸块150。半导体装置1也可为例如nand(not-and:与非)型闪存、lsi(large scale integration:大规模集成电路)等的半导体封装。

42.积层体s1具有半导体芯片10、及接着层20。接着层20为例如daf(die attachment film:裸片附着膜)。积层体s1为多个半导体芯片10向垂直于积层方向的方向偏移且积层的积层体。

43.多个半导体芯片10分别具有第1面f10a、及第1面的相反侧的第2面f10b。存储单元阵列、晶体管或电容器等的半导体元件(未图示)形成于各半导体芯片10的第1面f10a上。半导体芯片10的第1面f10a上的半导体元件由未图示的绝缘膜被覆且保护。

44.所述绝缘膜例如使用氧化硅膜或氮化硅膜等的无机系绝缘材料。此外,所述绝缘膜也可使用将有机系绝缘材料形成于无机系绝缘材料上的材料。作为有机系绝缘材料,例如使用苯酚系树脂、聚酰亚胺系树脂、聚酰胺系树脂、丙烯酸系树脂、环氧系树脂、pbo(p-phenylenebenzobisoxazole:聚对苯撑苯并双恶唑)系树脂、硅系树脂、苯并环丁烯系树脂

等的树脂、或所述的混合材料、复合材料等的有机系绝缘材料。半导体芯片10例如也可为nand型闪存的存储芯片或搭载任意lsi的半导体芯片。半导体芯片10可为彼此具有相同构成的半导体芯片,也可为彼此具有不同构成的半导体芯片。

45.多个半导体芯片10积层,且由接着层20接着。作为接着层20,例如使用苯酚系树脂、聚酰亚胺系树脂、聚酰胺系树脂、丙烯酸系树脂、环氧系树脂、pbo(p-phenylenebenzobisoxazole)系树脂、硅系树脂、苯并环丁烯系树脂等的树脂、或所述的混合材料、复合材料等的有机系绝缘材料。多个半导体芯片10分别具有露出于第1面f10a上的电极垫15。积层于半导体芯片10(下阶半导体芯片10)上的其他半导体芯片10(上阶半导体芯片10),以未重合于下阶半导体芯片10的电极垫15上的方式,相对于设置有下阶半导体芯片10的电极垫15的边,在大致垂直方向(x方向)上偏移且积层。

46.电极垫15与设置于半导体芯片10的半导体元件的任一个电连接。电极垫15例如使用cu、ni、w、au、ag、pd、sn、bi、zn、cr、al、ti、ta、tin、tan、crn等的单体、所述中2种以上的复合膜、或所述中2种以上的合金等的低电阻金属。

47.柱状电极30连接于半导体芯片10的电极垫15,且沿多个半导体芯片10的积层方向(z方向)延伸。接着层20以露出电极垫15的一部分的方式被部分地去除,且柱状电极30可连接于电极垫15。或,接着层20设置为贴附于上阶半导体芯片10的第2面f10b,且未与下阶半导体芯片10的电极垫15重合。柱状电极30的下端例如通过引线接合法连接于电极垫15。

48.柱状电极30的上端到达树脂层90的上表面,且在所述上表面露出。柱状电极30的上端连接于再布线层100的电极垫110。

49.此外,积层体s1的半导体芯片10以露出电极垫15的方式向积层体s2偏移积层。柱状电极30在第1面f10a中与配置于积层体s2的相反侧的电极垫15连接。

50.积层体s2具有半导体芯片50、及接着层60。积层体s2为多个半导体芯片50向垂直于积层方向的方向偏移且积层的积层体。积层体s2包含多个半导体芯片中最下层的半导体芯片即第2最下层芯片50b、及最上层的半导体芯片即第2最上层芯片50u。积层体s1包含多个半导体芯片中最下层的半导体芯片即第1最下层芯片10b、及最上层的半导体芯片即第1最上层芯片10u。另外,涉及积层体s1与积层体s2的关系的细节,参照图2a及图2b在下文说明。

51.多个半导体芯片50分别具有第1面f50a、及第1面f50a的相反侧的第2面f50b。存储单元阵列、晶体管或电容器等的半导体元件(未图示)形成于各半导体芯片50的第1面f50a上。半导体芯片50的第1面f50a上的半导体元件由未图示的绝缘膜被覆且保护。所述绝缘膜例如使用氧化硅膜或氮化硅膜等的无机系绝缘材料。此外,所述绝缘膜也可使用将有机系绝缘材料形成于无机系绝缘材料上的材料。作为有机系绝缘材料,例如使用苯酚系树脂、聚酰亚胺系树脂、聚酰胺系树脂、丙烯酸系树脂、环氧系树脂、pbo(p-phenylenebenzobisoxazole)系树脂、硅系树脂、苯并环丁烯系树脂等的树脂、或所述的混合材料、复合材料等的有机系绝缘材料。半导体芯片50例如也可为nand型闪存的存储芯片或搭载任意lsi的半导体芯片。半导体芯片50也可为彼此具有相同构成的半导体芯片,也可为彼此具有不同构成的半导体芯片。又,半导体芯片50也可为具有与半导体芯片10相同构成的半导体芯片,也可为具有与半导体芯片10不同构成的半导体芯片。

52.多个半导体芯片50积层,且由接着层60接着。多个半导体芯片50分别具有露出于

第1面f50a上的电极垫55。积层于其他半导体芯片50上的半导体芯片50,以未重合于其他半导体芯片50的电极垫55上的方式,相对于设置有电极垫55的边,在大致垂直方向(x方向)上偏移且积层。

53.电极垫55与设置于半导体芯片50的半导体元件的任一个电连接。电极垫55例如使用cu、ni、w、au、ag、pd、sn、bi、zn、cr、al、ti、ta、tin、tan、crn等的单体、所述中2种以上的复合膜、或所述中2种以上的合金等的低电阻金属。

54.柱状电极70连接于半导体芯片50的电极垫55,且沿多个半导体芯片50的积层方向(z方向)延伸。接着层60以露出电极垫55的一部分的方式被部分地去除,且柱状电极70可连接于电极垫55。或,接着层60设置为贴附于上阶半导体芯片50的第2面f50b,且未与下阶半导体芯片50的电极垫55重合。柱状电极70的下端例如通过引线接合法连接于电极垫55。

55.柱状电极70的上端到达树脂层90的上表面,且在所述上表面露出。柱状电极70的上端连接于再布线层100的电极垫110。

56.此外,积层体s2的半导体芯片50以露出电极垫55的方式向积层体s1偏移积层。柱状电极70在第1面f50a中与配置于积层体s1的相反侧的电极垫55连接。

57.半导体芯片200具有第1面f200a、及第1面的相反侧的第2面f200b。晶体管或电容器等的半导体元件(未图示)形成于各半导体芯片200的第1面f200a上。半导体芯片200的第1面f200a上的半导体元件由未图示的绝缘膜被覆且保护。所述绝缘膜例如使用氧化硅膜或氮化硅膜等的无机系绝缘材料。此外,所述绝缘膜也可使用将有机系绝缘材料形成于无机系绝缘材料上的材料。作为有机系绝缘材料,例如使用苯酚系树脂、聚酰亚胺系树脂、聚酰胺系树脂、丙烯酸系树脂、环氧系树脂、pbo(p-phenylenebenzobisoxazole)系树脂、硅系树脂、苯并环丁烯系树脂等的树脂、或所述的混合材料、复合材料等的有机系绝缘材料。半导体芯片200例如也可为控制存储芯片(半导体芯片10、50)的控制芯片或搭载任意lsi的半导体芯片。

58.半导体芯片200积层于半导体芯片50上,且由接着层接着于半导体芯片50。半导体芯片200分别具有露出于第1面f200a上的电极垫205。

59.连接柱(连接凸块)210连接于半导体芯片200的电极垫205,且沿z方向延伸。连接柱210的下端连接于半导体芯片200的电极垫205。连接柱210的上端到达树脂层90的上表面,且在所述上表面露出。连接柱210的上端连接于再布线层100的电极垫110。连接柱210的材料可使用例如cu等的导电性金属。柱状电极30及柱状电极70可由引线接合等形成,连接柱210可由镀敷法等形成,因此,柱状电极30及柱状电极70与连接柱210的粗细、材质也可不同。

60.树脂层90被覆(密封)积层体s1、s2、半导体芯片200、柱状电极30、70及连接柱210,且在上表面中露出柱状电极30、70及连接柱210的前端。

61.树脂层90例如使用苯酚系树脂、聚酰亚胺系树脂、聚酰胺系树脂、丙烯酸系树脂、环氧系树脂、pbo(p-phenylenebenzobisoxazole)系树脂、硅系树脂、苯并环丁烯系树脂等的树脂、或所述的混合材料、复合材料等的有机系绝缘材料。

62.再布线层(rdl(re distribution layer:重新分布层))100设置于树脂层90上,且电连接于柱状电极30、70及连接柱210。再布线层100是使多个布线层与多个绝缘层积层的多层布线层,将柱状电极30、70及连接柱210分别电连接于金属凸块150。另外,图1示意性表

示再布线层100内的布线层。

63.金属凸块150设置于再布线层100上,且电连接于再布线层100的布线层。金属凸块150用于与外部装置(未图示)连接。金属凸块150例如使用sn、ag、cu、au、pd、bi、zn、ni、sb、in、ge的单体、所述之中2种以上的复合膜、或合金。

64.接着,对积层体s1与积层体s2的关系进行说明。

65.图2a是表示第1实施方式的半导体装置1的构成的一例的剖视图。图2b是表示第1实施方式的半导体装置1的构成的一例的俯视图。图2b也可以是从z方向观察图2a的积层体s1、s2及半导体芯片200的图。

66.另外,图2a及图2b所示的积层体s1、s2与图1所示的积层体s1、s2的积层数不同。然而,图2a及图1在积层体s2高于积层体s1的点上共通。此外,在图2a及图2b中,省略接着层20、60及电极垫15、55、205等。

67.积层体s1具有积层的7阶半导体芯片10。积层体s2具有积层的9阶半导体芯片50。因此,积层体s2的积层数大于积层体s1的积层数。在图2a所示的例中,半导体芯片10的厚度与半导体芯片50的厚度大致相同。因此,积层体s2高于积层体s1。另外,在图2a及图2b所示的例中,积层体s1、s2设置于支撑衬底2上。

68.如图2a所示,积层体s1的半导体芯片10向积层体s2(沿x方向)偏移积层。积层体s2的半导体芯片50向积层体s1(沿-x方向)偏移积层。如图2b所示,积层体s2配置为从积层方向(z方向)观察,与积层体s1的至少一部分重叠。由此,能将积层体s1与积层体s2交叠配置,且能将积层体s1与积层体s2彼此更接近配置。结果,能使xy平面的封装的面积更小。

69.接着,对半导体装置1的制造方法进行说明。

70.图3a~图3e是表示第1实施方式的半导体装置1的制造方法的一例的剖视图。

71.首先,如图3a所示,通过使多个半导体芯片10积层于支撑衬底2上而形成积层体s1。此时,半导体芯片10以接着层20接着于其他半导体芯片10上。支撑衬底2也可为硅、玻璃、陶瓷、树脂板、引线框架等的金属板等。

72.接着,通过使多个半导体芯片50积层于支撑衬底2上而形成积层体s2。此时,半导体芯片50以接着层60接着于其他半导体芯片50上。

73.另外,可先形成积层体s1、s2的任一个。然而,如果先形成比积层体s1更高的积层体s2,那么有时难以使半导体芯片10积层。因此,更优选的是先形成积层体s1。

74.接着,将半导体芯片200积层于最上阶的半导体芯片50上。连接柱210例如在将半导体芯片200设置于最上阶的半导体芯片50上之前,形成于半导体芯片200的电极垫205。连接柱210例如通过镀敷法形成。连接柱210的材料例如使用cu等的导电性金属。

75.接着,如图3b所示,在半导体芯片10、50的每一个形成柱状电极30、70。在半导体芯片10、50的电极垫15、55上以引线接合法接合金属引线(导电性引线),且将所述金属引线沿相对于第1面f10a、f50a大致垂直方向引出而形成柱状电极30、70。此外,柱状电极30、70在上端被切断,利用柱状电极30、70自身的刚性而维持直立状态。

76.柱状电极30、70例如使用cu、ni、w、au、ag、pd、sn、bi、zn、cr、al、ti、ta的单体、所述中2种以上的复合材料、或所述中2种以上的合金等。优选使用au、ag、cu、pd的单体、所述中2种以上的复合材料、或所述中2种以上的合金等,作为柱状电极30、70的材料。进而优选的是,使用所述中硬度较高的材料,例如cu、cupd合金、将pd被覆于cu上的材料作为柱状电极

30、70的材料。由此,柱状电极30、70不易在由树脂层90被覆时弯曲、倒塌。

77.接着,如图3c所示,以树脂层90被覆包含积层体s1、s2、半导体芯片200、柱状电极30、70及连接柱210的构造体。树脂层90使用例如环氧系、苯酚系、聚酰亚胺系、聚酰胺系、丙烯酸系、pbo系、硅系、苯并环丁烯系等的树脂、所述的混合材料、复合材料。作为环氧树脂的例,并无特别限定,例如列举双酚a型、双酚f型、双酚ad型、双酚s型等的双酚型环氧树脂、苯酚酚醛型、甲酚酚醛型等的酚醛型环氧树脂、间苯二酚型环氧树脂、三酚甲烷三缩水甘油醚等的芳香族环氧树脂、萘型环氧树脂、芴型环氧树脂、二聚环戊二烯型环氧树脂、聚醚改质环氧树脂、二苯甲酮型环氧树脂、苯胺型环氧树脂、nbr(nitrile butadiene rubber:丁腈橡胶)改质环氧树脂、ctbn(carboxylated-terminated liquid acrylonitrile rubber:端羧基液态丁腈橡胶)改质环氧树脂、及所述的氢化物等。所述中,因为与硅的密接性较好,所以优选为萘型环氧树脂、二聚环戊二烯型环氧树脂。此外,因为容易获得快速固化性,所以二苯甲酮型环氧树脂也为优选。所述环氧树脂可单独使用,也可并用2种以上。此外,可在树脂层90中包含硅石等的填充物。

78.形成树脂层90后,以干燥器等加热树脂层90,或对树脂层90照射uv(ultraviolet:紫外线)光,由此使树脂层90固化。

79.接着,如图3d所示,以从树脂层90露出柱状电极30、70及连接柱210的方式研削树脂层90的上表面。例如,使用cmp(chemical mechanical polishing:化学机械研磨)法或机械研磨法等,研磨树脂层90直到露出柱状电极30、70及连接柱210。

80.接着,如图3e所示,在树脂层90上形成再布线层100。再布线层100的绝缘层例如使用环氧系、苯酚系、聚酰亚胺系、聚酰胺系、丙烯酸系、pbo系、硅系、苯并环丁烯系等的树脂、所述的混合材料、复合材料。再布线层100的布线层例如使用cu、ni、w、au、ag、pd、sn、bi、zn、cr、al、ti、ta、tin、tan、crn等的单体、所述中2种以上的复合材料、或所述中2种以上的合金等。

81.接着,使用热、激光等的光将支撑衬底2剥离。或可研磨去除支撑衬底2。另外,也去除设置于最下阶的半导体芯片10、50的第2面f10b、f50b的接着层20、60。

82.图3e的步骤后,在再布线层100上形成金属凸块150。金属凸块150例如可使用球搭载、镀敷法、印刷法而形成。金属凸块150例如使用sn、ag、cu、au、pd、bi、zn、ni、sb、in、ge的单体,所述中2种以上的复合膜、或合金。

83.之后,将图3e的步骤所获得的构造体及树脂层90通过切割按各封装单片化。由此,获得图1所示的半导体装置1。

84.另外,在图3a及图3b的步骤中,积层体s1的形成、柱状电极30的形成、积层体s2的形成及柱状电极70的形成也可按所述顺序进行。

85.此外,封装的厚度有余裕时,在图3e的步骤中,也可不去除支撑衬底2而保持残留。此时,半导体装置1的封装与支撑衬底2一同被切割。利用支撑衬底2,能保护最下阶的半导体芯片10的第2面f10b、及最下阶的半导体芯片50的第2面f50b。支撑衬底2为金属等的情况下,提高电磁波屏蔽性。又,也可将支撑衬底2设为接地电位。此时,在支撑衬底2与第1积层体s1及第2积层体s2之间介存接着层。

86.在所述实施方式中,柱状电极30、70作为一例以引线接合法形成,但也可以镀敷法形成。例如,将到达电极垫15、55的孔形成于树脂层90后,以镀敷法将金属材料嵌入孔。由

此,能通过镀敷法形成柱状电极30、70。柱状电极30、70也可使用此种镀敷法与引线接合法这两种方法而形成。

87.本实施方式的柱状电极30、70也可与将以通常的引线接合法形成的半导体芯片的电极垫间直接连接的引线混杂。又,也可使将半导体芯片间直接连接的引线、以引线接合法形成的柱状电极、及以镀敷法形成的柱状电极混杂。

88.如上所述,根据第1实施方式,高度不同的2个积层体s1、s2以交叠的方式配置。由此,能使2个积层体s1、s2更接近地配置。结果,能使封装更小。

89.图4是表示第1比较例的半导体装置1a的构成的一例的剖视图。

90.在图4所示的例中,设置具有积层的16阶的半导体芯片10a的积层体s1a。在第1比较例中,设置1个积层体s1a。然而,此时,积层数越增加,积层体s1a变得越高。因此,致使封装在z方向上变高。

91.与此相对,在第1实施方式中,如图2a所示,分为2个积层体s1、s2,分别积层半导体芯片10、50。封装的高度由2个积层体s1、s2中较高的积层体的高度决定。在图2a所示的例中,封装的高度由具有9阶的半导体芯片50的积层体s2的高度决定。因此,通过分为2个积层体s1、s2,能将封装的高度设得更小。

92.图5是表示第2比较例的半导体装置1b的构成的一例的剖视图。

93.在图5所示的例中,设置2个积层体s1b、s2b。2个积层体s1b、s2b从积层方向(z方向)观察,彼此未重叠。此时,作为封装的面积,至少需要积层体s1b、s2b每一个的面积。

94.与此相对,在第1实施方式中,积层体s1、s2的高度彼此不同,且积层体s1、s2以彼此交叠的方式配置。由此,能将从积层方向观察的2个积层体s1、s2的面积设得比积层体s1的面积与积层体s2的面积的和更小。结果,能使封装的面积更小。

95.此外,在第1实施方式中,半导体芯片200配置于比积层体s1更高的积层体s2上。如果在图2a中,半导体芯片200配置于比积层体s2更低的积层体s1上的情况下,为研磨树脂层90且使连接柱210露出,必须使连接柱210形成得较长。与此相对,在第1实施方式中,因为半导体芯片200配置于积层体s2上,所以能将形成的连接柱210设得更短。

96.此外,在第1实施方式中,柱状电极30至少按各半导体芯片10设置,柱状电极70至少按各半导体芯片50设置。在通常的引线接合法中,例如以引线连接4个存储芯片,4个中的1个存储芯片经由引线与衬底连接。然而,使半导体装置1高速动作时,更优选的是将多个半导体芯片分别与衬底连接。使用柱状电极的情况下,与通常的引线接合法比较,使多个存储芯片的每一个不经由其他存储芯片而易与衬底连接。在第1实施方式中,半导体芯片10不经由其他半导体芯片10而与再布线层100连接,且半导体芯片50不经由其他半导体芯片50而与再布线层100连接。

97.此外,在第1实施方式中,使用再布线层100作为衬底。再布线层100与柱状电极30、70及连接柱210电连接。如上所述,在将多个存储芯片未经由其他存储芯片而连接的情况下,必须将更多的布线设置于衬底内。此外,在柱状电极30、70及连接柱210的每一个中,相邻的柱状电极的间隔越窄,越需要将更多的布线设置于柱状电极周边的衬底内。因此,衬底内的布线层的数量增加,致使衬底变厚。这导致封装的厚度增大。此处,在使用再布线层100的情况下,与倒装芯片连接于布线衬底的情况比较,能获得更细的布线。因此,能提高布线密度,且能减少布线层的积层数。结果,能将衬底及封装设得更薄。

98.此外,在半导体芯片200的电极垫205,连接有连接柱210。也考虑取代连接柱210,在电极垫205连接柱状电极。然而,电极垫205的垫间距越小,形成柱状电极越困难。因此,也可使用柱状电极,但更优选的是使用连接柱210。

99.另外,所述积层体s1、s2的积层数为一例。

100.(第1实施方式的变化例)

101.图6a是表示第1实施方式的第1变化例的半导体装置1的构成的一例的剖视图。图6b是表示第1实施方式的第1变化例的半导体装置1的构成的一例的俯视图。第1实施方式的第1变化例与第1实施方式比较,半导体芯片200的配置不同。

102.在图6a所示的例中,半导体芯片200配置于比积层体s2更低的积层体s1上。图6a所示的半导体芯片200比图2a所示的半导体芯片200更厚。半导体芯片200例如比半导体芯片10、50更厚。由此,在半导体芯片200配置于积层体s1上时,也能将形成的连接柱210设得较短。通常,半导体芯片200为半导体元件的相反侧即第2面f200b的半导体衬底被研磨,薄化为理想的厚度。在图6a所示的例中,与图2a比较,半导体芯片200半导体衬底的研磨量较少。

103.如图6b所示,积层体s2与第1实施方式的图2b同样,配置为从积层方向(z方向)观察,与积层体s1的至少一部分重叠。

104.图7a是表示第1实施方式的第2变化例的半导体装置1的构成的一例的剖视图。第1实施方式的第2变化例与第1实施方式比较,半导体芯片10、50的积层数不同。

105.在图7a所示的例中,积层体s1具有积层的6阶半导体芯片10。积层体s2具有积层的10阶半导体芯片50。积层体s2配置为,根据积层体s1的高度与积层体s2的高度的差,从积层方向观察,与积层体s1的至少一部分重叠。

106.第2变化例的积层体s2因为比第1实施方式的积层体s2更高,所以致使封装变高。然而,第2变化例的积层体s1比第1实施方式的积层体s1更低。由此,在第2变化例中,与第1实施方式比较,能将积层体s1、s2以进一步交叠的方式配置。也就是说,能将积层体s1、s2彼此接近配置,且能将封装的面积设得更小。因此,在预先决定封装内的半导体芯片10、50的合计片数的情况下,能通过变更积层体s1、s2的高度的配设,而变更封装的高度与面积的比例。结果,能提高封装尺寸的设计自由度。

107.图7b是表示第1实施方式的第3变化例的半导体装置1的构成的一例的剖视图。第1实施方式的第3变化例在半导体芯片200配置于积层体s1上的点上,与第2变化例不同。因此,第3变化例为第1变化例与第2变化例的组合。

108.图8a是表示第1实施方式的第4变化例的半导体装置1的构成的一例的剖视图。第1实施方式的第4变化例与第1实施方式比较,半导体芯片10、50的积层数不同。

109.在图8a所示的例中,积层体s1具有积层的5阶的半导体芯片10。积层体s2具有积层的11阶半导体芯片50。因此,在第4变化例中,与第2变化例的图7a比较,能将积层体s1、s2以进一步交叠的方式配置。结果,能使封装的面积更小。

110.图8b是表示第1实施方式的第5变化例的半导体装置1的构成的一例的剖视图。第1实施方式的第5变化例在半导体芯片200配置于积层体s1上的点上,与第4变化例不同。因此,第5变化例为第1变化例与第4变化例的组合。

111.图9a是表示第1实施方式的第6变化例的半导体装置1的构成的一例的剖视图。第1实施方式的第6变化例与第1实施方式比较,半导体芯片10、50的积层数不同。

112.在图9a所示的例中,积层体s1具有积层的4阶的半导体芯片10。积层体s2具有积层的12阶半导体芯片50。因此,在第6变化例中,与第4变化例的图8a比较,能将积层体s1、s2以进一步交叠的方式配置。结果,能使封装的面积更小。

113.图9b是表示第1实施方式的半导体装置1的构成的第7变化例的剖视图。

114.第1实施方式的第7变化例在半导体芯片200配置于积层体s1上的点上,与第6变化例不同。因此,第7变化例为第1变化例与第6变化例的组合。

115.(第2实施方式)

116.图10是表示第2实施方式的半导体装置1的构成的一例的剖视图。第2实施方式在设置厚度不同的半导体芯片50的点上,与第1实施方式不同。

117.至少1个半导体芯片50比其他半导体芯片50更厚。至少1个半导体芯片50与至少1个半导体芯片10在积层方向(z方向)的位置相同。在图10所示的例中,最下阶的半导体芯片50比其他半导体芯片50更厚。以下,将最下阶的半导体芯片50与其他半导体芯片50区别称为半导体芯片51。积层体s2配置为,根据半导体芯片51的厚度,从积层方向观察,与积层体s1的至少一部分重叠。如果半导体芯片51变厚,那么积层体s1更容易进入积层体s2。也就是说,积层体s1能更接近半导体芯片51。由此,能使积层体s1、s2进一步交叠。结果,能使封装的面积更小。

118.第2实施方式的半导体装置1的其他构成因为与第1实施方式的半导体装置1的对应的构成相同,所以省略详细说明。第2实施方式的半导体装置1能获得与第1实施方式同样的效果。此外,也可使第1实施方式的第1变化例~第7变化例与第2实施方式的半导体装置1组合。

119.(第2实施方式的变化例)

120.图11是表示第2实施方式的变化例的半导体装置1的构成的一例的剖视图。第2实施方式在取代较厚的半导体芯片51而设置间隔件52的点上,与第1实施方式不同。

121.积层体s2具有间隔件52。间隔件52与半导体芯片50积层,且比半导体芯片更厚。此时,因为未设置较厚的半导体芯片51,所以可将积层体s2中半导体芯片的厚度全部设为相同的厚度。间隔件52的材料使用例如硅。

122.(第3实施方式)

123.图12是表示第3实施方式的半导体装置1的构成的一例的剖视图。第3实施方式在取代再布线层100而使用对布线衬底300的倒装芯片连接的点上,与第1实施方式不同。

124.半导体装置1不具备再布线层100,进而具备金属凸块155、布线衬底300、树脂层310、及树脂层320。

125.金属凸块(连接凸块)155设置于柱状电极30、70及连接柱210的上端部。金属凸块155的材料也可与金属凸块150的材料同样。

126.也就是说,金属凸块155使用sn、ag、cu、au、pd、bi、zn、ni、sb、in、ge的单体、所述中2种以上的复合膜、或合金等的导电性金属。

127.布线衬底300为包含布线层与绝缘层的多层衬底。绝缘层为例如预浸料。绝缘层为例如玻璃布等的纤维状增强材料与环氧树脂等的热固性树脂的复合材料。

128.此外,布线衬底300经由金属凸块155,与柱状电极30、70电连接。例如,相邻的柱状电极间的间隔较广的情况下,不需要再布线层100。由此,不需要搭载再布线层100的步骤。

此外,因为不需要再布线层100,所以减少半导体装置1的成本。另外,图11示意性表示布线衬底300内的布线层。

129.树脂层310将树脂层90与布线衬底300之间密封。此外,树脂层310也可用于树脂层90与布线衬底300的接着。

130.树脂层320覆盖树脂层90的整体。另外,剥离支撑衬底2的情况下,树脂层320被覆且保护从树脂层90露出的半导体芯片10、50的第2面f10b、f50b。

131.接着,对半导体装置1的制造方法进行说明。

132.图13a~图13d是表示第3实施方式的半导体装置1的制造方法的一例的剖视图。另外,图13a~图13d表示第1实施方式的图3d中树脂层90的研磨后的步骤。

133.图3d的步骤后,如图13a所示,在柱状电极30、70的上端部形成金属凸块155。

134.接着,将图13a的步骤所获得的构造体及树脂层90通过切割按各封装单片化。

135.接着,如图13b所示,在布线衬底300上涂布树脂层310的材料310a。

136.接着,如图13c所示,将树脂层90搭载于布线衬底300。也就是说,使树脂层90接着于布线衬底300且经由金属凸块155将柱状电极30、70及连接柱210、与布线衬底300电连接。

137.接着,如图13d所示,以树脂层320被覆支撑衬底2及树脂层90、310。

138.之后,通过在布线衬底300上形成金属凸块150,而完成图12所示的半导体装置1。

139.第3实施方式的半导体装置1的其他构成因为与第1实施方式的半导体装置1的对应的构成同样,所以省略详细说明。第3实施方式的半导体装置1能获得与第1实施方式同样的效果。此外,也可使第1实施方式的第1变化例~第7变化例与第3实施方式的半导体装置1组合。此外,也可使第2实施方式及第2实施方式的变化例与第3实施方式的半导体装置1组合。

140.(第4实施方式)

141.图14是表示第4实施方式的半导体装置1的构成的一例的剖视图。第4实施方式在半导体芯片折回并积层的点上,与第1实施方式不同。另外,在图14中,省略树脂层90及再布线层100等。

142.在第4实施方式中,积层体s1、s2的配置与第1实施方式不同。此外,半导体装置1还具备间隔件400。

143.积层体s1例如具有积层的4阶的半导体芯片10。积层体s1的半导体芯片10向间隔件400(-x方向)偏移且积层。

144.柱状电极30与半导体芯片10的电极垫15(未图示)连接,且沿半导体芯片10的积层方向(z方向)延伸。

145.此外,积层体s1的半导体芯片10以露出电极垫15的方式,向间隔件400偏移且积层。柱状电极30在第1面f10a中与配置于间隔件400的相反侧的电极垫15连接。

146.间隔件400与积层体s1同样,设置于支撑衬底2上。因此,间隔件400与最下阶的半导体芯片10的第2面f10b配置于相同面。间隔件400向垂直于积层方向的方向与积层体s1并列配置。间隔件400的高度在积层体s1的高度以上。间隔件400作为支撑积层体s2的台座发挥功能。间隔件400的材料使用例如硅。

147.积层体s2配置于积层体s1及间隔件400的上方。积层体s2例如具有积层的4阶的半导体芯片50。积层体s2的半导体芯片50向积层体s1的偏移方向的相反方向(x方向)偏移且

积层。另外,积层体s以未与柱状电极30接触的方式,离开配置。因此,更优选的是积层体s2配置于间隔件400侧而非积层体s1侧。第2最下层芯片50b设置于第1最上层芯片10u上。第2最下层芯片50b设置于间隔件400上。此时,因为积层体s2与间隔件400的至少一部分相接的面积变大,所以间隔件400能更稳定地支撑积层体s2。

148.最上阶的半导体芯片10与最下阶的半导体芯片50例如介隔接着层60相接。通过以接着层60补偿间隔件400的厚度与积层体s1的高度的差,能将最下阶的半导体芯片50设置为大致水平。例如,更优选的是贴附于最下阶的半导体芯片50的接着层60比贴附于其他半导体芯片50的接着层60更厚。最下阶的半导体芯片50的接着层60的厚度例如为约10μm~约20μm。其他半导体芯片50的接着层60的厚度例如为约5μm。

149.柱状电极70与半导体芯片50的电极垫55(未图示)连接,且沿半导体芯片50的积层方向(z方向)延伸。

150.此外,积层体s2的半导体芯片50以露出电极垫55的方式向柱状电极30偏移积层。柱状电极70在第1面f50a中与配置于柱状电极30的相反侧的电极垫55连接。

151.半导体芯片200配置于积层体s2上。半导体芯片200配置于柱状电极30与柱状电极70之间。半导体芯片200从积层方向观察,配置于积层体s1及积层体s2的区域的大致中心部。由此,能将半导体芯片200配置于封装的大致中央。半导体芯片200从积层方向观察,与第1最下层芯片10b、第1最上层芯片10u、第2最下层芯片50b、第2最上层芯片50u至少一部分重叠。与积层体s1及积层体s2的全部半导体芯片从积层方向观察,至少一部分重叠。

152.连接柱210与半导体芯片200的电极垫205(未图示)连接且沿积层方向延伸。

153.接着,对半导体装置1的制造方法进行说明。

154.在图14所示的例中,更优选的是在形成积层体s2之前,形成柱状电极30。如果在形成积层体s2后形成柱状电极30的情况下,因为有毛细管干扰积层体s2的可能性,所以必须扩大积层体s2与柱状电极30之间。这导致封装面积增大。

155.在第1比较例的图4中,半导体芯片200a配置于向一方向偏移积层的积层体s1a上。因此,半导体芯片200a容易配置于封装的端部,难以配置于封装的大致中央。此外,柱状电极30a集中配置于半导体芯片200a的单侧。由此,对于各半导体芯片10a,到半导体芯片200a的布线长度的不均变大。这导致各半导体芯片10a的电特性的不均增大。另外,柱状电极的长度比再布线层100a内的布线的长度更短,对布线长度的影响较小。例如,越下阶的半导体芯片10a,到半导体芯片200a的布线长度越长。此外,安装半导体装置1a的外部装置的端子与半导体芯片200a之间的布线长度也是同样,不均变大且变长。这导致半导体装置1a的高速化受阻。此外,半导体芯片200越从封装的中央离开,越容易使布线的环绕集中,因而容易增大再布线层100的布线层的数量。另外,有连接于半导体芯片200a的连接柱210a比柱状电极30a配置得更高密度的情况,容易对布线的环绕造成较大影响。

156.与此相对,在第4实施方式中,因为在以从积层体s1折回的方式偏移积层的积层体s2上设置半导体芯片200,所以能容易将半导体芯片200配置于封装的大致中央。此外,柱状电极30、70以从两侧夹着连接柱210的方式配置。由此,能抑制从半导体芯片200到半导体芯片10的布线长度、与从半导体芯片200到半导体芯片50的布线长度之间的不均。此外,能将从半导体芯片200到半导体芯片10、50的布线长度设得更短。因此,能抑制各半导体芯片10、50的电特性的不均。外部装置与半导体芯片200之间的布线长度也同样,能抑制不均且能设

得更短。此外,能使布线的环绕分散,且能抑制再布线层100的布线层的数量增大。因此,能将布线的长度及环绕设得更适当。

157.此外,利用间隔件400,能抑制积层体s1的高度的累积公差的影响。通常,半导体芯片的积层数越大,考虑半导体芯片的累积公差,必须使柱状电极形成得越长。然而,因为柱状电极在树脂层的研磨时会被磨损,所以理想的是不形成得过长。与此相对,在第4实施方式中,形成与设置于间隔件400上的积层体s2的高度的累积公差相应的长度的柱状电极30、70及连接柱210。也就是说,不必考虑比间隔件400更低的积层体s1的高度的累积公差。由此,能将形成的柱状电极30、70及连接柱210设得更短。

158.此外,利用间隔件400,能抑制最下阶的半导体芯片50的厚度增大。在未设置间隔件400的情况下,如果因通常的引线接合使引线碰撞折回的半导体芯片,那么有折回的半导体芯片破损的情况。这是因为电极垫的位置的半导体芯片与支撑衬底之间中空,所以半导体芯片的强度变弱。如果为确保半导体芯片的强度而将折回的半导体芯片(最下阶的半导体芯片50)加厚,那么致使封装变厚。此外,如果为防止半导体芯片50的破损,而使积层体s2靠近柱状电极30侧,那么有致使积层体s2干扰柱状电极30的可能性。与此相对,在第4实施方式中,因为间隔件400支撑最下阶的半导体芯片50,所以不必将最下阶的半导体芯片50加厚。

159.另外,积层体s1也可以是1阶的半导体芯片10,此外,积层体s2也可以是1阶的半导体芯片50。

160.(第4实施方式的变化例)

161.图15是表示第4实施方式的第1变化例的半导体装置1的构成的一例的剖视图。第4实施方式的第1变化例在半导体芯片沿一方向偏移且积层的点上,与第4实施方式不同。

162.在图15所示的例中,积层体s1具有积层的7阶半导体芯片10。积层体s2具有1阶的半导体芯片50。此时,不必考虑积层体s1的高度的累积公差。如此,积层体s1、s2的积层阶数也可变更。

163.图16是表示第4实施方式的第2变化例的半导体装置1的构成的一例的剖视图。第4实施方式的第2变化例在设置多个间隔件的点上,与第4实施方式的第1变化例不同。

164.在图16所示的例中,积层体s1具有积层体s11、及积层体s12。积层体s11具有积层的下侧的4阶半导体芯片10。积层体s12具有积层的上侧的3阶半导体芯片10。

165.半导体装置1还具备间隔件410。间隔件410设置于积层体s1的积层中途。间隔件410向垂直于积层方向的方向与积层体s11并列配置,且支撑积层体s12。如此,间隔件的数量也可变更。

166.图17是表示第4实施方式的第3变化例的半导体装置1的构成的一例的剖视图。第4实施方式的第3变化例与第4实施方式同样,使积层体s1与积层体s2彼此向反方向偏移且积层。此外,第4实施方式的第3变化例在设置多个间隔件的点上,与第4实施方式不同。

167.在图17所示的例中,积层体s2配置于积层体s1的上方,但最下阶的半导体芯片50未与积层体s1的半导体芯片10相接。

168.积层体s2具有积层体s21、及积层体s22。积层体s21具有积层的下侧的6阶半导体芯片50。积层体s22具有上侧的1阶半导体芯片50。

169.半导体装置1还具备间隔件420。间隔件420设置于积层体s2的积层中途。间隔件

420向垂直于积层方向的方向与积层体s21并列配置,且支撑积层体s22。如此,间隔件的数量也可变更。间隔件420设置于积层体1的最上层芯片10u上。

170.(第5实施方式)

171.图18是第5实施方式的半导体装置1的构成的一例的剖视图。第5实施方式在设置连接柱状电极的虚设芯片的点上,与第1实施方式不同。此外,以通常的引线接合法形成的直接连接半导体芯片的电极垫间的引线与柱状电极混杂。

172.半导体装置1具备引线17、57、间隔件400、虚设芯片500、接着层510、及柱状电极520。

173.积层体s1具有积层的2阶半导体芯片10。积层体s1的半导体芯片10向垂直于积层方向的方向偏移且积层。另外,柱状电极未连接于半导体芯片10。

174.引线17将2个半导体芯片10分别具有的电极垫15间连接。此外,引线17将半导体芯片10的电极垫15、与虚设芯片500的电极垫505之间连接。引线17通过通常的引线接合法形成。引线17的材料例如使用au等的导电性金属。

175.积层体s2具有积层的2阶半导体芯片50。积层体s2的半导体芯片50向垂直于积层方向的方向偏移且积层。积层体s2配置于积层体s1的上方。另外,柱状电极未连接于半导体芯片50。

176.引线57将2个半导体芯片50分别具有的电极垫55间连接。此外,引线57将半导体芯片50的电极垫55、与虚设芯片500的电极垫505之间连接。引线57通过通常的引线接合法形成。引线57的材料例如使用au等的导电性金属。

177.间隔件400以向垂直于积层方向的方向与积层体s1并列配置,且支撑虚设芯片500的方式配置。间隔件400具有积层体s1以上的高度。间隔件400与第4实施方式说明的间隔件400大致同样。因此,不必考虑积层体s1的高度公差,能将形成的柱状电极520设得更短。另外,也可不设置间隔件400。

178.虚设芯片(连接部)500积层于积层体s1与积层体s2之间。虚设芯片500利用接着层510与间隔件400及积层体s1接着。虚设芯片500是例如与半导体芯片10、50比较,未设置半导体元件的芯片。虚设芯片500具有用以与半导体芯片10及半导体芯片50连接的电极垫505。

179.柱状电极520与虚设芯片500的电极垫505连接,且沿积层方向延伸。柱状电极520将虚设芯片500与再布线层100电连接。

180.半导体芯片200设置于积层体s2上。半导体芯片的电极垫205经由连接柱210与再布线层100电连接。

181.图19是表示第5实施方式的积层体s1、s2及虚设芯片500的构成的一例的立体图。

182.虚设芯片500具有的多个电极垫505的间隔比半导体芯片10具有的多个电极垫15的间隔、及半导体芯片50具有的多个电极垫55的间隔更广。也就是说,利用虚设芯片500,能扩大与柱状电极520连接的电极垫505的垫间距。结果,能缓解(消除)形成柱状电极520时的毛细管与柱状电极520的干扰,且能形成更长的柱状电极520。

183.此外,虚设芯片500配置于到积层体s1的距离与到积层体s2的距离大致相等的位置。此外,积层体s1的半导体芯片10的积层数、与积层体s2的半导体芯片10的积层数大致相同。由此,能以从半导体芯片10到虚设芯片500的布线长度、与从半导体芯片50到虚设芯片

500的布线长度大致相等的方式配置虚设芯片500。结果,能抑制布线长度的不均,且更容易成为等长布线。因此,能将布线的长度设得更适当。

184.另外,积层体s1也可为1阶的半导体芯片10,此外,积层体s2也可为1阶的半导体芯片50。

185.虽然已说明本发明的若干实施方式,但所述实施方式是作为实例而提出,并非意图限定发明的范围。所述实施方式可以其他多种方式实施,可在不脱离发明主旨的范围内,进行多种省略、置换及变更。所述实施方式或变化与包含于发明的范围或主旨同样,包含于权利要求书所记述的发明与此均等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1