一种IGZO薄膜晶体管及其制造方法

一种igzo薄膜晶体管及其制造方法

技术领域

1.本发明主要涉及薄膜晶体管技术领域,特别是涉及一种创新型结构igzo薄膜晶体管。

背景技术:

2.非晶氧化物半导体铟镓锌氧(

ɑ

‑

igzo)薄膜因具有柔性、透明以及大面积制造等特点备受学术界与产业界的广泛关注。基于igzo薄膜制备的晶体管具有高迁移率、高开关电流比、低关态漏电流等优点。以结构划分,传统igzo薄膜晶体管结构可分为顶栅共面、顶栅交错、底栅共面、底栅交错四种基础结构。在传统结构的基础上,根据实际应用需求衍生出多种新型结构。从2004年首次报道以来,igzo薄膜晶体管的研究主要关于如何提升器件的迁移率、开关比、电流密度等。例如,采用双栅极结构可有效提升器件电流能力。然而关于提升igzo薄膜晶体管耐压能力的研究鲜有报道。

3.现有提升igzo薄膜晶体管耐压的方法主要包括:1)采用原子层沉积(ald)工艺制备的高介电常数、高质量绝缘介电层;2)偏移薄膜晶体管的栅极与漏极距离。采用ald工艺制备具有成本高、不适合大规模生产等缺点;偏移栅极、漏极距离则会显著增加导通电阻,降低器件的电流密度。si基半导体器件的导通电阻正比于击穿电压的2.5次方,存在折中关系。igzo薄膜晶体管必然存在类似的折中关系,提升耐压与提升电流密度不能同时实现。因此有必要提出一种新型igzo薄膜晶体管结构,提升器件耐压能力的同时减小器件电流密度的牺牲。

技术实现要素:

4.鉴于现有提升igzo薄膜晶体管耐压方法中的不足,本发明提出一种非对称双栅极igzo薄膜晶体管及其制作方法,提升器件耐压能力,降低电流密度损失,有效提高功率密度。

5.为了实现上述的igzo薄膜晶体管功能,本发明采用如下技术方案:

6.一种非对称双栅极igzo薄膜晶体管,包括基底、背栅电极层、背栅介电层、源区电极和漏区电极、igzo有源层、顶栅介电层以及顶栅电极层,所述背栅电极层设于所述基底上一侧,所述背栅介电层覆盖在所述背栅电极与基底之上,所述源区电极与漏区电极设于所述背栅介电层上相对的两侧,所述igzo有源层设于所述源区电极、漏区电极以及背栅介电层之上,所述顶栅介电层和所述顶栅电极层依次层叠在所述igzo有源层上。

7.在本实施例中,所述基底包括半导体衬底和所述半导体衬底上的绝缘氧化层。

8.在本实施例中,所述背栅电极层位于背栅介电层下方,水平方向上位于靠近所述漏区电极一侧,水平位置上与漏区电极具有0.2μm的交叠长度,水平位置上距离源区电极18μm的长度。

9.在本实施例中,所述源、漏电极均为ito电极。

10.在本实施例中,所述的igzo有源层分为栅控区域的沟道区和非栅控区域的偏移

区,沟道区长度和宽度均为为20μm,偏移区长度为0.1μm。

11.在本实施例中,所述顶栅介电层覆盖在igzo有源层和源、漏电极上,材质为al2o3。

12.在本实施例中,所述顶栅电极层设于顶栅介电层上,水平位置上距离漏区电极0.1μm的偏移长度,水平位置上与源区电极具有1μm的交叠长度。

13.一种非对称双栅极igzo薄膜晶体管的制造方法,包括:获取基底;采用溶液旋涂工艺在所述基底上形成背栅电极层;采用溶胶凝胶旋涂工艺制作背栅介电层覆盖在所述背栅电极上;在所述背栅介电层的一侧形成源极、另一侧形成漏极;通过溶液工艺在所述背栅介电层上形成igzo有源层,并在所述的igzo层上利用溶胶凝胶旋涂工艺形成顶栅介电层;在所述顶栅介电层上形成顶栅极。

14.在本实施例中,通过溶液旋涂工艺在所述基底上形成背栅电极。

15.在本实施例中,通过溶胶凝胶旋涂工艺形成背栅介电层。

16.在本实施例中,通过溶液工艺在所述背栅介电层上形成igzo层的步骤包括:制作igzo前体溶液;将所述igzo前体溶液旋涂于所述背栅介电层上。

17.在本实施例中,对旋涂了所述igzo前体溶液的背栅介电层在空气环境下退火处理,退火温度为400℃,退火时间为1h。

18.在本实施例中,所述制作igzo前体溶液的步骤包括:将醋酸锌水合物、硝酸铟水合物、硝酸镓水合物溶解于2

‑

甲氧基乙醇溶剂中并在超声发生器中振荡60分钟,得到透明溶液后,在室温下保存48小时;将得到的液体进行过滤得到所述igzo前体溶液。

19.在本实施例中,所述过滤是使用0.45μm厚的聚四氟乙烯滤膜进行。

20.在本实施例中,所述将硝酸铟水合物、醋酸锌水合物、硝酸镓水合物溶解于2

‑

甲氧基乙醇溶剂中的步骤中,硝酸铟水合物、醋酸锌水合物、硝酸镓水合物的摩尔比是2:1:1,并添加单乙醇胺(mea)作为稳定剂。

21.在本实施例中,通过溶胶凝胶旋涂工艺形成顶栅介电层。

22.在本实施例中,通过溶液旋涂工艺形成顶栅电极层。

23.传统对称双栅极igzo薄膜晶体管栅极均与源、漏极存在交叠,高压工作状态下交叠区内的电场较高,是易击穿区域,降低了igzo薄膜晶体管的耐压能力,本实施例通过偏移顶栅极与漏极之间的距离,减小非栅控顶栅介电层内峰值电场,提升器件耐压能力,进一步通过背栅电压提升非栅控igzo有源层内的载流子密度,降低沟道导通电阻,有效提高igzo薄膜晶体管的功率密度。

附图说明

24.为了更好地描述和说明本发明的实施例,本发明提供了多幅附图。用于描述附图的附加细节或示例不应当被认为是对所公开的发明、目前描述的实施例和/或示例以及目前理解的这些发明的最佳模式中的任何一者的范围的限制。

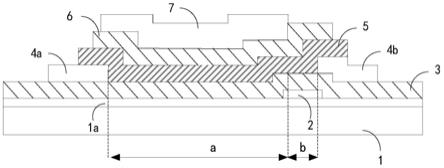

25.图1是本发明实施例中非对称双栅igzo薄膜晶体管的结构示意图;

26.图2是本发明对比例1传统双栅igzo薄膜晶体管的结构示意图;

27.图3是本发明对比例2传统顶栅igzo薄膜晶体管的结构示意图;

28.图4是本发明实施例中非对称双栅igzo薄膜晶体管的制造方法流程图;

29.图5是本发明实施例中步骤s005的子步骤流程图;

30.图6是本发明实施例与对比例1和2的电场分布图。

具体实施方式

31.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。

32.附图1中给出了本发明的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使读者对本发明的公开内容理解得更加透彻全面。除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。

33.发明人认为可以采用新型结构提升器件耐压能力,同时降低电流密度牺牲,提升功率密度。本发明提出了一种创新型的非对称双栅极igzo薄膜晶体管,创新结构中顶栅起主栅调控作用,水平方向顶栅与源端电极交叠1μm长度,而与漏端电极不存在交叠,且相距0.1μm,该长度下的非栅控沟道区域称为偏移区,偏移长度为0.1μm。偏移区可以降低漏极附近的顶栅介电层中的峰值电场,有效提升器件的耐压能力,同时通过背栅提升偏移区中载流子浓度,降低电流密度的损失,提高igzo薄膜晶体管的功率密度。

34.图1是本实施例中igzo薄膜晶体管的示意图,图4是本实施例中igzo薄膜晶体管的制造方法流程图,该方法可以用于制造图1所示的igzo薄膜晶体管,包括如下步骤:

35.s001,获取基底。

36.基底可以是本领域习知的刚性基底(例如玻璃)或柔性基底。在本实施例中,基底为硅衬底。

37.s002,通过溶液旋涂工艺在基底上形成背栅电极层。

38.在本实施例中,在硅衬底上氧化形成二氧化硅层,然后再于二氧化硅层上通过溶液旋涂工艺形成背栅电极层,电极材质为ito,在其他实施例中也可以采用其他材料,这都在本发明的保护范围内。背栅电极(2)水平位置上与漏区电极(4b)具有0.2μm的交叠长度,水平位置上距离源区电极(4a)18μm的长度。

39.s003,通过溶胶凝胶旋涂工艺在背栅电极层及基底上形成背栅介电层。

40.在本实施例中,可以在二氧化硅层和形成的背栅电极层上覆盖背栅介电层,介电层材质为al2o3。

41.s004,在背栅介电层的一侧形成源极、另一侧形成漏极。

42.在本实施例中,是在步骤s003后于背栅介电层两侧通过溶液旋涂工艺分别形成ito源极、ito漏极,在其他实施例中,也可以采用本领域习知的其他源漏材质作为源极和漏极。

43.s005,通过溶液工艺在背栅介电层和源、漏电极上形成igzo层。

44.在本实施例中,通过溶液工艺在背栅介电层上和源、漏电极上形成igzo层。

45.s006,在igzo层上形成顶栅介电层。

46.在本实施例中,顶栅介电层覆盖igzo层的沟道区并延伸至与两侧的ito源极和ito漏极有交叠。在本实施例中,顶栅介电层的材质为al2o3。

47.s007,在顶栅介电层上形成顶栅极。

48.在本实施例中,顶栅极为溶液工艺制备的ito栅极,在其他实施例中也可以采用其他本领域习知的其他材质作为顶栅极。顶栅极与漏电极存在0.1μm的偏移长度,与源电极存

在1μm的交叠长度。

49.在本实施例中,上述方法形成的igzo层为

ɑ

‑

igzo(非晶igzo)薄膜。

50.在本实施例中,步骤s002至s007采用溶液工艺进行制备,从而使得igzo薄膜晶体管可实现全溶液工艺制备,操作简单、成本低.。

51.参见图5,在本实施例中,步骤s005包括:

52.s5a,制作igzo前体溶液。

53.在本实施例中,步骤s5a具体是在室内环境下将硝酸铟(iii)水合物(in(no3)3·

xh2o)、醋酸锌水合物(zn(oac)2·

xh2o)、硝酸镓(iii)水合物(ga(no3)3·

xh2o)按照2:1:1的摩尔比溶解于2

‑

甲氧基乙醇(ch3och2ch2oh)溶剂中,并添加单乙醇胺(mea)作为稳定剂;在超声发生器中振荡60分钟后,得到的透明溶液在室温下保存48小时,通过0.45μm厚的聚四氟乙烯(ptfe)过滤器过滤以此完成igzo前体溶液的制备。

54.s5b,将igzo前体溶液旋涂于背栅介电层上。

55.在本实施例中,是将igzo前体溶液旋涂于背栅介电层上并以4500rpm(转/分)的速度旋转30秒。

56.s5c,进行热退火处理。

57.在本实施例中,是将旋涂有igzo前体溶液的背栅介电层在空气氛围下退火,退火温度为400℃,退火时间为1小时。

58.本技术还提供了一种igzo薄膜晶体管的制备方法。如图1所示,igzo薄膜晶体管包括基底1、背栅2、背栅介电层3、源极4a、漏极4b、igzo层5、顶栅介电层6、顶栅极7。基底1可以是本领域习知的刚性基底(例如玻璃)或柔性基底。在本实施例中,基底为半导体衬底,例如硅衬底。在图1所示的实施例中,igzo薄膜晶体管采用双栅顶栅主控(dual

‑

gate)结构。需要指出的是,各膜层在图1中的尺寸只是一个示意,并不代表其实际尺寸。

59.在图1所示的实施例中,背栅电极层2设于基底之上,材质为ito,含括偏移区长度b,之后是背栅介电层3。

60.源极4a形成于背栅介电层3的一侧、漏极4b形成于背栅介电层3的另一侧。在图1所示的实施例中,源极4a为ito源极、漏极4b为ito漏极。在其他实施例中,也可以采用本领域习知的其他源漏材质作为源极和漏极。

61.igzo层5包括沟道区a和偏移区b,背栅电极负责调控偏移区。igzo层5通过溶液工艺形成。

62.顶栅介电层6形成于igzo层5上。在图1所示的实施例中,顶栅介电层6覆盖沟道区a和偏移区b,并延伸至源极4a和漏极4b上。顶栅极7形成于顶栅介电层6上。

63.在本实施例中,顶栅介电层6材质为al2o3。在本实施例中,顶栅极7为ito栅极。

64.在本实施例中,igzo层5为

ɑ

‑

igzo薄膜。在igzo薄膜晶体管工作时,顶栅极7接正电压,在igzo薄膜沟道中积累电子,通过对漏极4b加电进行载流子输运形成电流。

65.在图1所示的实施例中,igzo薄膜晶体管还包括设于基底1上的绝缘氧化层1a。在本实施例中,绝缘氧化层1a的材质为二氧化硅。

66.在图1所示的实施例中,背栅电极层2的厚度为5nm,背栅长度为2.2μm,背栅介电层3厚度为200nm,源极4a和漏极4b的厚度皆为25nm(背栅介电层层3上的源/漏极厚度),igzo层5的厚度为20nm,沟道区a的长度为20μm,偏移区长度b为0.1μm,顶栅介电层6的厚度为

30nm,栅极7的厚度为50nm。

67.图6是本技术实施例与对比例1和2的电场分布图,纵坐标为电场,由于高电场区域主要分布在栅、漏附近,所以横坐标为以距漏极左边缘向左2μm处为起点向右取2.5μm的长度。对比例1为传统双栅igzo薄膜晶体管;对比例2为传统顶栅igzo薄膜晶体管,无背栅电极;两个对比例均与实施例采用相同工艺步骤,相同工艺尺寸。e1、e2和e3分别表示本实施例、对比例1和对比例2的电场分布曲线。可以看出,当背栅电压v

bg

=10v,顶栅电压v

tg

=10v,实施例和对比例1分别施加漏端电压v

ds

=75v、v

ds

=40v时,顶栅介电层中峰值电场达到文献报道的al2o3膜极限场强6mv/cm,即发生击穿,此时的电流分别为0.495ma,0.45ma;对比例2顶栅电压v

tg

=10v,漏端电压v

ds

=40v时,顶栅介电层达到击穿条件,此时的电流为0.425ma。当顶栅压为10v时,本发明实施例功率密度为16.875w/cm,而对比例1和对比例2的功率密度分别为9.9w/cm,8.5w/cm,实施例相较于对比例1功率密度同比提高了41.3%,实施例相较于对比例2功率密度同比提高了49.6%。具体数据如表1所示。

68.表1 结果参数表

[0069][0070]

以上所述实施例描述较为具体和详细,但不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1