显示设备和制造显示设备的方法与流程

显示设备和制造显示设备的方法

1.相关申请的交叉引用

2.本技术要求于2020年9月03日提交的第10-2020-0112543号韩国专利申请的优先权和权益,上述韩国专利申请的全部内容通过引用包含于此。

技术领域

3.一个或多个实施例涉及显示设备和制造显示设备的方法,并且更具体地,涉及具有改善的产品可靠性的显示设备和制造显示设备的方法。

背景技术:

4.近来,显示设备的应用已经多样化。此外,因为显示设备已经变得更薄和更轻,所以显示设备的用途范围已经增加。

5.考虑到以各种合适的方式利用显示设备,可以使用各种合适的方法设计显示设备的形状,并且可以增加可以与显示设备相关联或相联系的功能。

技术实现要素:

6.本公开的实施例的一个或多个方面涉及一种显示设备以及一种制造显示设备的方法,所述显示设备具有扩展的显示区域,使得即使在布置有作为电子元件的组件的区域中也可以显示图像。然而,一个或多个方面仅是示例,并且本公开的范围不限于此。

7.附加方面将在随后的描述中部分地阐述,并且附加方面将部分地根据所述描述显而易见,或者可以通过实践所提供的本公开的实施例而获悉附加方面。

8.根据一个或多个实施例,一种显示设备,包括:主显示区域;和组件区域,包括彼此间隔开的像素组和在所述像素组之间的透射区域。所述显示设备还包括:基底,包括顺序地堆叠在彼此上的第一基体层、补偿层、第一阻挡层和第二阻挡层;底部金属层,在所述第一阻挡层与所述第二阻挡层之间;缓冲层,在所述第二阻挡层上;主显示元件,在所述主显示区域的所述基底上;以及辅助显示元件,在所述组件区域的所述基底上。

9.所述缓冲层可以包括第一缓冲层和在所述第一缓冲层上的第二缓冲层,所述第一缓冲层的厚度可以为至并且所述第二缓冲层的厚度可以为至

10.所述第一缓冲层可以包括(例如,可以是)氮化硅,并且所述第二缓冲层可以包括(例如,可以是)氧化硅。

11.所述第一缓冲层的折射率可以为1.8至2(2.0),并且所述第二缓冲层的折射率可以为1.3至1.6。

12.所述补偿层的厚度可以为至

13.所述补偿层可以包括(例如,可以是)氮氧化硅。

14.所述补偿层的折射率可以为1.65至1.75。

15.所述第一阻挡层的厚度可以为至

16.所述第一阻挡层可以包括(例如,可以是)氧化硅。

17.所述第一阻挡层的折射率可以为1.3至1.6。

18.所述第二阻挡层的厚度可以为至

19.所述第一阻挡层和所述第二阻挡层可以包括(例如,可以是)相同的材料。

20.所述显示设备还可以包括:第二基体层,在所述第一基体层下方;和第三阻挡层,在所述第一基体层与所述第二基体层之间。

21.所述底部金属层可以包括与所述透射区域相对应的第一孔。

22.所述底部金属层可以布置为对应于所述辅助显示元件。

23.所述底部金属层可以直接布置在所述第一阻挡层上。

24.所述显示设备还可以包括:薄膜封装层,覆盖所述主显示元件和所述辅助显示元件,并且所述薄膜封装层可以包括至少一个无机封装层和至少一个有机封装层。

25.所述第一缓冲层可以直接布置在所述第二阻挡层上。

26.所述第二阻挡层可以包括第一层和在所述第一层上的第二层。

27.所述第二层可以在氯的量方面大于所述第一层。

28.所述显示设备还可以包括:组件,布置在所述基底下方以对应于所述组件区域。

29.根据一个或多个实施例,一种制造显示设备的方法,所述显示设备包括:主显示区域;和组件区域,包括彼此间隔开的像素组和在所述像素组之间的透射区域,所述方法包括如下操作(动作):在第一基体层上形成补偿层;在所述补偿层上形成第一阻挡层;在所述第一阻挡层上形成底部金属层;在所述底部金属层上形成第二阻挡层;以及在所述第二阻挡层上形成缓冲层。

30.所述形成所述缓冲层可以包括:在所述第二阻挡层上形成第一缓冲层;以及在所述第一缓冲层上形成第二缓冲层。

31.所述形成所述第一缓冲层可以包括:通过利用(例如,使用)包括(例如,是)氯的气体在所述第二阻挡层上形成所述第一缓冲层。

32.所述方法还可以包括:在所述形成所述第一缓冲层之前,将包括(例如,是)氯气(cl2)的等离子体辐射到所述第二阻挡层的上表面上。

33.所述第一缓冲层的厚度可以为至并且所述第二缓冲层的厚度可以为至

34.所述第一缓冲层可以包括(例如,可以是)氮化硅,并且所述第二缓冲层可以包括(例如,可以是)氧化硅。

35.所述第一阻挡层的厚度可以为至

36.所述第二阻挡层的厚度可以为至

37.所述第一阻挡层和所述第二阻挡层可以包括(例如,可以是)相同的材料。

38.通过以下对实施例、权利要求和附图的描述,这些和/或其它方面将变得明显且更容易理解。

附图说明

39.通过以下结合附图的描述,本公开的特定实施例的以上及其它方面和特征将变得更加明显,在附图中:

40.图1是根据实施例的显示设备的透视图;

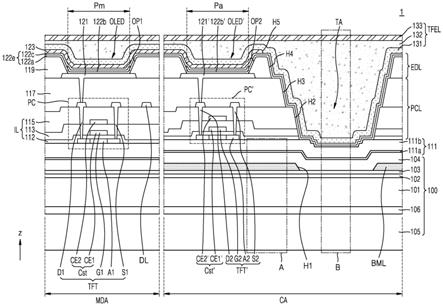

41.图2是根据实施例的显示设备的一部分的示意性截面图;

42.图3是可以被包括在图1的显示设备中的显示面板的示意性平面图;

43.图4和图5各自是根据实施例的用于驱动子像素的像素电路的等效电路图;

44.图6是示出根据实施例的主显示区域的像素排列结构的示意性布局图;

45.图7和图8各自是示出根据实施例的组件区域中的像素排列结构的示意性布局图;

46.图9是根据实施例的显示面板的一部分的示意性截面图,即,主显示区域和组件区域的示意性截面图;

47.图10是根据实施例的图9的部分a的放大图;

48.图11是根据实施例的图9的部分b的放大图;

49.图12是根据实施例的图9的部分a的放大图;

50.图13是根据实施例的图9的部分b的放大图;以及

51.图14至图22是根据实施例的用于说明制造显示设备的方法的示意性截面图。

具体实施方式

52.现在将更详细地参考本公开的实施例,在附图中示出了本公开的示例,其中,同样的附图标记始终表示同样的元件。在此方面,本实施例可以具有不同的合适的形式,并且不应被解释为局限于本文中阐述的描述或受本文中阐述的描述限制。因此,下面仅通过参照附图来描述一些实施例,以解释本说明书的各方面和各特征。如本文中所使用的,术语“和/或”包括一个或多个相关所列项的任意组合和所有组合。在整个公开中,表述“a、b和c中的至少一个(种)”表示仅a、仅b、仅c、a和b两者、a和c两者、b和c两者、a、b和c的全部或者它们的变型。如本文中所使用的,当描述本公开的实施例时,术语“可以”的使用表示“本公开的一个或多个实施例”。

53.由于本公开允许各种合适的改变和许多实施例,因此将在附图中示出一些实施例,并且将在书面描述中更详细地描述一些实施例。在下文中,将参照附图更充分地描述本公开的各方面和各特征以及用于实现本公开的各方面和各特征的方法(例如,用于制造或制作本公开的各方面和各特征的方法),在附图中示出了本公开的实施例。然而,本公开可以以许多不同的合适的形式实现,并且不应被解释为局限于本文中阐述的实施例或受本文中阐述的实施例限制。

54.将理解的是,尽管在本文中可以使用术语“第一”和“第二”等来描述各种组件,但是这些组件不应受这些术语的限制。这些术语仅用于将一个组件与另一组件区分开。

55.如本文中所使用的,除非上下文另外明确指出,否则单数形式“一个”、“一种”和“所述(该)”也意图包括复数形式。

56.将进一步理解的是,在本文中使用的术语“包括”和“包含”说明存在所陈述的特征和/或组件,但不排除存在或附加一个或多个其它特征和/或组件。

57.将理解的是,当层、区或组件被称为“在”另一层、区或组件“上”或者“形成在”另一

层、区或组件“上”时,所述层、区或组件可以直接或间接在所述另一层、区或组件上或者直接或间接形成在所述另一层、区或组件上。例如,可以存在一个或多个居间层、区和/或组件。

58.为了便于解释,可能夸大了附图中的元件的尺寸。例如,因为为了便于解释,可能夸大了附图中的组件的尺寸和厚度,所以以下实施例不限于此。如本文中所使用的,术语“基本上”、“大约”、“近似”和类似术语用作近似术语而非程度术语,并且旨在解释本领域普通技术人员将认识到的测量值或计算值的固有偏差。

59.另外,在本文中列举的任何数值范围旨在包括被包含在列举范围内的相同的数值精度的所有子范围。例如,范围“1.0至10.0”旨在包括在所列举的最小值1.0和所列举的最大值10.0之间(并且包括所列举的最小值1.0和所列举的最大值10.0)的所有子范围,也就是说,范围“1.0至10.0”具有等于或大于1.0的最小值和等于或小于10.0的最大值,诸如以2.4至7.6为例。本文中列举的任何最大数值限制旨在包括其中所包含的所有较低的数值限制,并且本说明书中列举的任何最小数值限制旨在包括其中所包含的所有较高的数值限制。因此,申请人保留修改本说明书(包括权利要求书)的权利,以明确地列举包含在本文中明确地列举的范围内的任何子范围。

60.在本说明书中,“a和/或b”表示a或b,或者a和b。表述“选自a和b中的至少一个(种)”表示仅a、仅b、a和b两者或者它们的变型。

61.在以下实施例中,布线在第一方向或第二方向上延伸不仅可以表示或涵盖在第一方向或第二方向上以直线延伸,而且可以表示或涵盖在第一方向或第二方向上以之字形或曲线延伸。

62.在以下实施例中,术语“平面”可以表示当从上方观察物体时,并且术语“截面”和“横截面”可以表示当从侧面观察通过垂直地切割物体所形成的横截面时。在以下实施例中,术语“重叠”可以涵盖“平面”重叠和“横截面”重叠。

63.下面将参照附图更详细地描述本公开的一个或多个实施例。无论附图编号如何,那些相同或相应的组件由相同的附图标记提供(例如,表示或指示)。

64.图1是根据实施例的显示设备1的透视图。

65.参照图1,显示设备1包括显示区域da和在显示区域da外部的外围区域dpa。显示区域da包括组件区域ca和主显示区域mda,主显示区域mda至少部分地在组件区域ca周围或者至少部分地围绕组件区域ca。例如,组件区域ca和主显示区域mda可以单独地显示图像或共同显示图像。外围区域dpa可以是其中未布置显示元件的非显示区域。显示区域da可以被外围区域dpa部分地或完全地围绕。在一些实施例中,外围区域dpa可以在显示区域da周围。

66.图1示出了定位在主显示区域mda内的一个组件区域ca。根据实施例,显示设备1可以具有两个或更多个组件区域ca,并且组件区域ca可以具有不同的形状和不同的尺寸。当在与显示设备1的上表面近似地或基本上正交或垂直的方向上观察时(例如,当在平面图中观察时),组件区域ca可以具有诸如圆形形状、椭圆形形状、多边形形状(例如,矩形形状、星形形状或菱形形状)的各种合适的形状中的任意一种。在图1中,当在与显示设备1的上表面近似地或基本上正交或垂直的方向上观察时,组件区域ca布置在具有近似于矩形形状的主显示区域mda的(在+y轴方向上的)上部部分的中央处,但是组件区域ca不限于此。例如,组件区域ca可以布置在具有近似或基本上矩形形状的主显示区域mda的一侧(例如,右上侧或

左上侧)处(例如,一侧上)。

67.显示设备1可以通过利用(例如,使用)布置在主显示区域mda中的主子像素pm和布置在组件区域ca中的辅助子像素pa提供(例如,显示)图像。

68.在组件区域ca中,如稍后将参照图2描述的,作为电子元件的组件40可以布置在显示面板下方以对应于组件区域ca。例如,在平面图中,组件40可以在组件区域ca中(例如,可以与组件区域ca重叠)。组件40可以是利用(例如,使用)红外光和/或可见光等的照相机,以及/或者可以是拍摄装置。在一些实施例中,组件40可以是太阳能电池、闪光灯(例如,与照相机或闪光灯装置一起使用的闪光灯)、照度传感器、接近传感器和/或虹膜传感器。在一些实施例中,组件40可以具有接收声音的功能。为了最小化或减少对组件40的功能的限制,组件区域ca可以包括能够透射光和/或声音的透射区域ta,所述光和/或声音从组件40输出到外部以及/或者从外部朝向组件40行进。根据实施例,当光通过组件区域ca透射时,在组件区域ca和/或透射区域ta处的透光率(例如,组件区域ca和/或透射区域ta的透光率)可以为大约15%或更大,例如,25%或更大、40%或更大、50%或更大、85%或更大或者90%或更大。

69.在组件区域ca中,可以布置辅助子像素pa。辅助子像素pa中的每一个可以发光以提供特定图像。由组件区域ca显示的图像是辅助图像,并且因此可以具有比由主显示区域mda显示的图像的分辨率低的分辨率。例如,当组件区域ca包括能够透射光和/或声音的透射区域ta时,并且当没有子像素布置在透射区域ta中时,可以布置在组件区域ca中的单位面积上的辅助子像素pa的数量可以小于布置在主显示区域mda中的单位面积上的主子像素pm的数量。

70.图2是根据实施例的显示设备1的一部分的示意性截面图。

71.参照图2,显示设备1可以包括显示面板10和与显示面板10重叠的组件40。覆盖窗50可以进一步位于显示面板10上方以保护显示面板10。

72.显示面板10可以包括(例如,在z轴方向上)与组件40重叠的组件区域ca和在其上(例如,在其中)将要显示主图像的主显示区域mda。显示面板10可以包括基底100、在基底100上的显示层disl、触摸屏幕层tsl、光学功能层ofl以及在基底100下方的面板保护构件pb。在一些实施例中,显示面板10还可以包括覆盖窗50。

73.显示层disl可以包括电路层pcl、显示元件层edl以及诸如薄膜封装层tfel或封装基底的封装构件encm,电路层pcl包括主薄膜晶体管tft和辅助薄膜晶体管tft',显示元件层edl包括作为显示元件的主有机发光二极管oled和辅助有机发光二极管oled'。在基底100与显示层disl之间,可以布置绝缘层il和il'。在一些实施例中,绝缘层il和il'中的一个或多个可以在显示层disl内。在一些实施例中,绝缘层il'可以在基底100与显示层disl之间,并且绝缘层il可以在显示层disl内。例如,主薄膜晶体管tft和辅助薄膜晶体管tft'可以在绝缘层il中。

74.基底100可以包括(例如,可以是)诸如聚合物树脂的绝缘材料,并且可以是刚性基底或者可弯折的、可折叠的和/或可卷曲的柔性基底。

75.在显示面板10的主显示区域mda中,可以布置主薄膜晶体管tft和耦接(例如,连接)到主薄膜晶体管tft的主有机发光二极管oled,以实现主子像素pm。在显示面板10的组件区域ca中,可以布置辅助薄膜晶体管tft'和耦接(例如,连接)到辅助薄膜晶体管tft'的

辅助有机发光二极管oled',以实现辅助子像素pa。组件区域ca中的布置有辅助子像素pa的区域可以被称为辅助显示区域。

76.在组件区域ca中,可以布置透射区域ta,透射区域ta不具有布置在透射区域ta中的显示元件。透射区域ta可以透射由布置为对应于组件区域ca的组件40发射的光/信号或者将要(例如,从显示设备1外部)入射在组件40上的光/信号。辅助显示区域和透射区域ta可以彼此交替地排列在组件区域ca中。

77.在组件区域ca中,可以布置底部金属层bml。底部金属层bml可以布置在辅助薄膜晶体管tft'下方以(例如,在平面图中)对应于辅助薄膜晶体管tft'(例如,与辅助薄膜晶体管tft'重叠)。例如,底部金属层bml可以在辅助薄膜晶体管tft'与基底100之间。在一些实施例中,绝缘层il'可以覆盖底部金属层bml,使得底部金属层bml在基底100与绝缘层il'之间,并且使得绝缘层il'在底部金属层bml与辅助薄膜晶体管tft'之间。底部金属层bml可以防止或阻挡外部光到达辅助薄膜晶体管tft'。根据实施例,静电电压和/或信号被施加到底部金属层bml,并且因此底部金属层bml可以保护或防止像素电路(例如,辅助子像素pa)被静电放电损坏,或者底部金属层bml可以减少这种损坏。

78.显示元件层edl可以被薄膜封装层tfel或封装基底覆盖。根据一些实施例,如图2中所示,薄膜封装层tfel可以包括至少一个无机封装层和至少一个有机封装层。根据实施例,薄膜封装层tfel可以包括第一无机封装层131和第二无机封装层133以及在第一无机封装层131与第二无机封装层133之间的有机封装层132。

79.第一无机封装层131和第二无机封装层133可以各自包括(例如,各自是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。有机封装层132可以包括(例如,可以是)基于聚合物的材料。基于聚合物的材料的示例可以包括(例如,可以是)丙烯酸树脂、环氧基树脂、聚酰亚胺和/或聚乙烯。

80.根据一些实施例,当显示元件层edl被封装基底密封时,封装基底可以布置为面对基底100(例如,可以与基底100重叠),显示元件层edl在封装基底与基底100之间。在封装基底与显示元件层edl之间可以存在间隙。封装基底可以包括(例如,可以是)玻璃。包括(例如,是)玻璃料等的密封剂可以布置在基底100与封装基底之间,并且可以布置在外围区域dpa(参见图1)中。布置在外围区域dpa(参见图1)中的密封剂可以在显示区域da(参见图1)周围(例如,可以围绕显示区域da(参见图1)),并且可以防止或阻挡湿气渗透通过显示面板10的侧表面。

81.触摸屏幕层tsl可以基于外部输入(例如,触摸事件)获得坐标信息。触摸屏幕层tsl可以包括触摸电极以及耦接(例如,连接)到触摸电极的触摸布线。触摸屏幕层tsl可以根据自电容方法或互电容方法感测外部输入。

82.触摸屏幕层tsl可以在薄膜封装层tfel上。在一些实施例中,触摸屏幕层tsl可以单独地提供在触摸基底上,并且随后经由诸如光学透明粘合剂(oca)的粘合剂层耦接到薄膜封装层tfel的上表面。根据实施例,触摸屏幕层tsl可以直接提供在薄膜封装层tfel上。在这种情况下,在触摸屏幕层tsl与薄膜封装层tfel之间可以没有粘合剂层。

83.可以包括光学功能层ofl以改善可见度。光学功能层ofl可以包括防反射层。防反射层可以降低从外部源朝向显示设备1入射的光(外部光)的反射率。

84.根据实施例,防反射层可以是偏振膜。偏振膜可以包括线性偏振板和诸如四分之一波(λ/4)片的相位延迟膜。相位延迟膜可以在触摸屏幕层tsl上,并且线性偏振板可以在相位延迟膜上。

85.根据实施例,防反射层可以包括滤光层,所述滤光层包括黑矩阵和滤色器。可以通过考虑分别由显示设备1的子像素发射的光束的颜色来布置滤色器。例如,滤光层可以包括红色、绿色和/或蓝色的滤色器。

86.根据实施例,防反射层可以包括相消干涉结构。相消干涉结构可以包括布置在不同的层上的第一反射层和第二反射层。分别由第一反射层和第二反射层反射的第一反射光和第二反射光可以彼此相消地干涉,并且因此可以降低外部光的反射率。

87.覆盖窗50可以布置在显示面板10上方以保护显示面板10。光学功能层ofl可以通过oca耦接(例如,附接)到覆盖窗50(例如,覆盖窗50的下表面),以及/或者光学功能层ofl可以经由oca耦接(例如,附接)到触摸屏幕层tsl(例如,触摸屏幕层tsl的上表面)。

88.面板保护构件pb可以耦接(例如,附接)到基底100的下表面,并且可以支撑和保护基底100。面板保护构件pb可以具有与组件区域ca相对应(例如,在平面图中与组件区域ca重叠)的开口pb_op。在面板保护构件pb中包括开口pb_op可以改善组件区域ca的透光率。面板保护构件pb可以包括(例如,可以是)聚对苯二甲酸乙二醇酯(pet)和/或聚酰亚胺(pi)。

89.组件区域ca可以具有比布置有组件40的区域的面积更大的面积。因此,被包括在面板保护构件pb中的开口pb_op的面积可以不与组件区域ca的面积相同。

90.在组件区域ca中,可以布置多个组件40。多个组件40可以执行不同的功能。例如,多个组件40可以包括选自照相机(例如,成像装置)、太阳能电池、闪光灯、接近传感器、照度传感器和虹膜传感器中的至少两个。

91.图3是可以被包括在图1的显示设备1中的显示面板10的示意性平面图。

92.参照图2和图3,构成显示面板10的各种组件可以布置在基底100上。基底100可以包括显示区域da和在显示区域da周围(例如,围绕显示区域da)的外围区域dpa。显示区域da可以包括主显示区域mda和组件区域ca,在主显示区域mda处(例如,在主显示区域mda上)显示主图像,组件区域ca包括透射区域ta,并且在组件区域ca处(例如,在组件区域ca上)显示辅助图像。辅助图像可以与主图像一起形成单个整体图像,或者可以形成独立于主图像的图像。例如,辅助图像和主图像可以共同地形成单一的、一体的图像,或者辅助图像和主图像可以彼此独立。

93.在主显示区域mda中,可以布置主子像素pm。主子像素pm中的每一个可以实现为诸如主有机发光二极管oled的显示元件。主子像素pm中的每一个可以发射例如红光、绿光、蓝光和/或白光。主显示区域mda可以被封装构件覆盖,并且因此可以保护主显示区域mda免受环境空气和/或湿气等的影响。

94.组件区域ca可以如上所述地定位在主显示区域mda的一侧(例如,上侧)处(例如,定位在主显示区域mda的一侧(例如,上侧)上),以及/或者可以布置在显示区域da内并且被主显示区域mda围绕。在一些实施例中,组件区域ca可以在主显示区域mda的中央处。在一些实施例中,主显示区域mda可以在组件区域ca周围(例如,可以围绕组件区域ca)。在组件区域ca中,可以布置辅助子像素pa。辅助子像素pa中的每一个可以实现为诸如辅助有机发光二极管oled'的显示元件。辅助子像素pa中的每一个可以发射例如红光、绿光、蓝光和/或白

光。组件区域ca可以被封装构件覆盖,并且因此可以保护组件区域ca免受环境空气和/或湿气等的影响。

95.组件区域ca可以具有透射区域ta。透射区域ta可以布置在辅助子像素pa周围(例如,围绕辅助子像素pa)。例如,在辅助子像素pa中的一个或多个辅助子像素pa的一侧或多侧处可以存在透射区域ta中的一个或多个透射区域ta。在一些实施例中,透射区域ta可以与辅助子像素pa一起以格子配置彼此排列。在一些实施例中,透射区域ta和辅助子像素pa可以以矩阵图案彼此排列。

96.因为组件区域ca具有透射区域ta,所以组件区域ca的分辨率可以低于主显示区域mda的分辨率。例如,组件区域ca的分辨率可以是主显示区域mda的分辨率的大约1/2、3/8、1/3、1/4、2/9、1/8、1/9或1/16。例如,主显示区域mda的分辨率可以是大约400ppi或更大,并且组件区域ca的分辨率可以是大约200ppi或大约100ppi。

97.驱动主子像素pm和辅助子像素pa的像素电路可以分别电耦接(例如,电连接)到布置在外围区域dpa中的外部电路。在外围区域dpa中,可以布置第一扫描驱动电路sdrv1、第二扫描驱动电路sdrv2、端子单元pad、驱动电压供应线11和公共电压供应线13。

98.第一扫描驱动电路sdrv1可以将扫描信号经由扫描线sl施加到驱动主子像素pm和辅助子像素pa的像素电路中的每一个。第一扫描驱动电路sdrv1可以将发光控制信号经由发光控制线el施加到所述像素电路中的每一个。第二扫描驱动电路sdrv2可以定位在主显示区域mda的与在其处(例如,在其上)定位有第一扫描驱动电路sdrv1的一侧(例如,左侧)相对的一侧(例如,右侧)处(例如,上),并且可以近似地或基本上平行于第一扫描驱动电路sdrv1(例如,平行于第一扫描驱动电路sdrv1)。布置在主显示区域mda中的主子像素pm的一些像素电路可以电耦接(例如,电连接)到第一扫描驱动电路sdrv1,并且其余像素电路(例如,主子像素pm的其余像素电路)可以电耦接(例如,电连接)到第二扫描驱动电路sdrv2。布置在组件区域ca中的辅助子像素pa的一些像素电路可以电耦接(例如,电连接)到第一扫描驱动电路sdrv1,并且其余像素电路(例如,辅助子像素pa的其余像素电路)可以电耦接(例如,电连接)到第二扫描驱动电路sdrv2。在一些实施例中,不包括第二扫描驱动电路sdrv2。

99.端子单元pad可以在基底100的一侧(例如,下侧)处(例如,可以在基底100的一侧(例如,下侧)上)。端子单元pad可以被暴露而未被绝缘层覆盖,并且可以耦接(例如,连接)到显示电路板30。显示驱动单元32可以在显示电路板30上。

100.显示驱动单元32可以产生控制信号,所述控制信号被传输到第一扫描驱动电路sdrv1和第二扫描驱动电路sdrv2。显示驱动单元32可以产生数据信号,并且所产生的数据信号可以经由扇出布线fw和耦接(例如,连接)到扇出布线fw的数据线dl传输到主子像素pm和辅助子像素pa的像素电路。

101.显示驱动单元32可以将驱动电压elvdd(参见图4)供应到驱动电压供应线11,并且可以将公共电压elvss(参见图4)供应到公共电压供应线13。驱动电压elvdd(参见图4)可以经由耦接(例如,连接)到驱动电压供应线11的驱动电压线pl施加到主子像素pm和辅助子像素pa的像素电路,并且公共电压elvss(参见图4)可以耦接(例如,连接)到公共电压供应线13,并且因此公共电压elvss(参见图4)可以被施加到每个显示元件的相对电极(例如,可以经由公共电压供应线13被施加到每个显示元件的相对电极)。

102.驱动电压供应线11可以沿着x方向(x轴方向)(例如,在x方向(x轴方向)上)延伸

和/或在主显示区域mda的下侧沿着x方向(x轴方向)(例如,在x方向(x轴方向)上)延伸。公共电压供应线13可以具有其一侧开口的环形形状(例如,平面图中的u形,所述u形可以旋转任何合适的角度,例如,180度),并且可以在主显示区域mda的一部分周围(例如,可以围绕主显示区域mda的一部分)。

103.虽然图3示出了单个组件区域ca,但是在一些实施例中,可以包括多个组件区域ca。在这种情况下,多个组件区域ca可以彼此间隔开,并且可以与一个组件区域ca对应地布置第一组件(例如,第一照相机),并且可以与另一组件区域ca对应地布置第二组件(例如,第二照相机)。在一些实施例中,可以与一个组件区域ca对应地布置照相机,并且可以与另一组件区域ca对应地布置ir(红外)照相机。多个组件区域ca可以具有不同的形状和不同的尺寸。

104.每个组件区域ca可以具有多边形形状。例如,每个组件区域ca可以具有八边形形状。每个组件区域ca可以具有诸如矩形和六边形的各种合适的多边形中的任意一种的形状。然而,本公开不限于此,并且每个组件区域ca可以具有任何合适的形状(例如,任何合适的平面形状)。组件区域ca可以被主显示区域mda围绕。

105.图4和图5各自是根据实施例的用于驱动子像素的像素电路的等效电路图。

106.参照图4,像素电路pc1可以耦接(例如,连接)到有机发光二极管oled1,并且像素电路pc1可以实现子像素的发光(例如,可以发射或产生光),其中,像素电路pc1可以是本文中所述的主像素电路pc和/或辅助像素电路pc',并且有机发光二极管oled1可以是本文中所述的主有机发光二极管oled和/或辅助有机发光二极管oled'。像素电路pc1包括驱动薄膜晶体管t1、开关薄膜晶体管t2和存储电容器cst1,其中,存储电容器cst1可以是本文中所述的主存储电容器cst和/或辅助存储电容器cst'。开关薄膜晶体管t2可以耦接(例如,连接)到扫描线sl和数据线dl,并且可以根据经由扫描线sl接收的扫描信号sn将经由数据线dl接收的数据信号dm传输到驱动薄膜晶体管t1。

107.存储电容器cst1可以耦接(例如,连接)到开关薄膜晶体管t2和驱动电压线pl,并且可以存储与从开关薄膜晶体管t2接收的电压和供应到驱动电压线pl的驱动电压elvdd之间的差相对应的电压。

108.驱动薄膜晶体管t1可以耦接(例如,连接)到驱动电压线pl和存储电容器cst1,并且可以根据存储在存储电容器cst1中的电压值控制从驱动电压线pl流到有机发光二极管oled1的驱动电流。有机发光二极管oled1可以由于驱动电流而发射具有特定亮度的光。例如,亮度可以对应于驱动电流(例如,可以与驱动电流成比例)。

109.尽管图4中示出了像素电路pc1包括两个薄膜晶体管和一个存储电容器的情况,但是实施例不限于此。

110.参照图5,像素电路pc1可以包括驱动薄膜晶体管t1、开关薄膜晶体管t2、补偿薄膜晶体管t3、第一初始化薄膜晶体管t4、操作控制薄膜晶体管t5、发光控制薄膜晶体管t6和第二初始化薄膜晶体管t7。

111.虽然在图5中,像素电路pc1包括信号线(例如,扫描线sl、前一扫描线sl-1、下一扫描线sl+1、发光控制线el和数据线dl)、初始化电压线vl以及驱动电压线pl,但是实施例不限于此。根据实施例,选自信号线中的至少一条(例如,选自扫描线sl、前一扫描线sl-1、下一扫描线sl+1、发光控制线el和数据线dl中的至少一条)以及初始化电压线vl可以由邻近

的像素电路共享。

112.驱动薄膜晶体管t1的漏极电极可以经由发光控制薄膜晶体管t6电耦接(例如,电连接)到有机发光二极管oled1。驱动薄膜晶体管t1可以根据开关薄膜晶体管t2的开关操作接收数据信号dm,并且可以将驱动电流供应到有机发光二极管oled1。

113.开关薄膜晶体管t2的栅极电极可以耦接(例如,连接)到扫描线sl,并且开关薄膜晶体管t2的源极电极可以耦接(例如,连接)到数据线dl。开关薄膜晶体管t2的漏极电极可以耦接(例如,连接)到驱动薄膜晶体管t1的源极电极,并且同时可以(例如,并且还可以)经由操作控制薄膜晶体管t5耦接(例如,连接)到驱动电压线pl。

114.开关薄膜晶体管t2可以根据经由扫描线sl接收的扫描信号sn而导通,并且可以执行将从数据线dl接收的数据信号dm传输到驱动薄膜晶体管t1的源极电极的开关操作。

115.补偿薄膜晶体管t3的栅极电极可以耦接(例如,连接)到扫描线sl。补偿薄膜晶体管t3的源极电极可以耦接(例如,连接)到驱动薄膜晶体管t1的漏极电极,并且同时可以(例如,并且还可以)经由发光控制薄膜晶体管t6耦接(例如,连接)到有机发光二极管oled1的像素电极。补偿薄膜晶体管t3的漏极电极可以耦接(例如,连接)到存储电容器cst1的一个电极、第一初始化薄膜晶体管t4的源极电极和驱动薄膜晶体管t1的栅极电极。补偿薄膜晶体管t3根据经由扫描线sl接收的扫描信号sn而导通,并且将驱动薄膜晶体管t1的栅极电极和漏极电极彼此耦接(例如,连接),从而实现驱动薄膜晶体管t1的以二极管方式的连接。

116.第一初始化薄膜晶体管t4的栅极电极可以耦接(例如,连接)到前一扫描线sl-1。第一初始化薄膜晶体管t4的漏极电极可以耦接(例如,连接)到初始化电压线vl。第一初始化薄膜晶体管t4的源极电极可以耦接(例如,连接)到存储电容器cst1的一个电极、补偿薄膜晶体管t3的漏极电极和驱动薄膜晶体管t1的栅极电极。第一初始化薄膜晶体管t4可以根据经由前一扫描线sl-1接收的前一扫描信号sn-1而导通,并且可以将初始化电压vint传输到驱动薄膜晶体管t1的栅极电极,从而将驱动薄膜晶体管t1的栅极电极的电压初始化。

117.操作控制薄膜晶体管t5的栅极电极可以耦接(例如,连接)到发光控制线el。操作控制薄膜晶体管t5的源极电极可以耦接(例如,连接)到驱动电压线pl。操作控制薄膜晶体管t5的漏极电极耦接(例如,连接)到驱动薄膜晶体管t1的源极电极和开关薄膜晶体管t2的漏极电极。

118.发光控制薄膜晶体管t6的栅极电极可以耦接(例如,连接)到发光控制线el。发光控制薄膜晶体管t6的源极电极可以耦接(例如,连接)到驱动薄膜晶体管t1的漏极电极和补偿薄膜晶体管t3的源极电极。发光控制薄膜晶体管t6的漏极电极可以电耦接(例如,电连接)到有机发光二极管oled1的像素电极。操作控制薄膜晶体管t5和发光控制薄膜晶体管t6可以根据经由发光控制线el接收的发光控制信号en而同时地或并发地导通,并且因此驱动电压elvdd可以被传输到有机发光二极管oled1,并且驱动电流可以在有机发光二极管oled1中流动。

119.第二初始化薄膜晶体管t7的栅极电极可以耦接(例如,连接)到下一扫描线sl+1。第二初始化薄膜晶体管t7的源极电极可以耦接(例如,连接)到有机发光二极管oled1的像素电极。第二初始化薄膜晶体管t7的漏极电极可以耦接(例如,连接)到初始化电压线vl。第二初始化薄膜晶体管t7可以根据经由下一扫描线sl+1接收的下一扫描信号sn+1而导通,并且可以将有机发光二极管oled1的像素电极初始化。

120.虽然在图5中,第一初始化薄膜晶体管t4和第二初始化薄膜晶体管t7分别耦接(例如,连接)到前一扫描线sl-1和下一扫描线sl+1,但是实施例不限于此。根据实施例,第一初始化薄膜晶体管t4和第二初始化薄膜晶体管t7两者可以耦接(例如,连接)到前一扫描线sl-1,并且可以根据前一扫描信号sn-1而被驱动。

121.存储电容器cst1的另一电极可以耦接(例如,连接)到驱动电压线pl。存储电容器cst1的一个电极可以耦接(例如,连接)到驱动薄膜晶体管t1的栅极电极、补偿薄膜晶体管t3的漏极电极和第一初始化薄膜晶体管t4的源极电极。

122.有机发光二极管oled1的相对电极(例如,阴极)可以接收公共电压elvss。有机发光二极管oled1可以从驱动薄膜晶体管t1接收驱动电流,并且可以发光。

123.像素电路pc1不限于上面参照图4和图5所描述的薄膜晶体管的数量、存储电容器的数量和电路设计。薄膜晶体管的数量、存储电容器的数量和电路设计可以适当地变化。

124.驱动主子像素pm和辅助子像素pa的像素电路pc1可以彼此相同或者可以彼此不同。例如,图5的像素电路pc1可以用作驱动主子像素pm和辅助子像素pa的像素电路pc1中的每一个。根据实施例,图5的像素电路pc1可以用作驱动主子像素pm的像素电路pc1,并且图4的像素电路pc1可以用作驱动辅助子像素pa的像素电路pc1。

125.图6是示出根据实施例的主显示区域mda中的像素排列结构的示意性布局图。

126.在主显示区域mda中,可以布置多个主子像素pm。如本文所使用的子像素是指作为实现(例如,产生或发射)图像(例如,光)的最小单位的发光区域。当有机发光二极管用作显示元件时,发光区域可以由像素限定层的开口限定。稍后将对此进行描述。

127.如图6中所示,在主显示区域mda中彼此排列的主子像素pm可以具有(三星显示有限公司的商标)结构。例如,在一些实施例中,主子像素pm可以以rgbg矩阵彼此排列。主子像素pm可以包括第一子像素pr、第二子像素pg和第三子像素pb,并且第一子像素pr、第二子像素pg和第三子像素pb可以分别发射红色、绿色和蓝色的光束(例如,光)。

128.多个第一子像素pr和多个第三子像素pb在第一行1n上彼此交替(例如,多个第一子像素pr和多个第三子像素pb在沿着x轴方向延伸的第一行1n上彼此交替地排列),多个第二子像素pg在与第一行1n相邻的第二行2n上彼此间隔开设定或预定的距离(例如,多个第二子像素pg在第二行2n上彼此排列,第二行2n沿着x轴方向延伸并且沿着垂直于x轴方向的y轴方向与第一行1n相邻,其中,多个第二子像素pg中的在第二行2n上的相邻的第二子像素pg彼此间隔开设定或预定的距离),多个第三子像素pb和多个第一子像素pr在与第二行2n相邻的第三行3n上彼此交替,并且多个第二子像素pg在与第三行3n相邻的第四行4n上彼此间隔开设定或预定的距离,并且这种像素排列重复直到第n行。例如,偶数行和奇数行可以沿着y轴方向彼此交替地排列。在这种情况下,第一子像素pr和第三子像素pb可以大于第二子像素pg。

129.位于第一行1n上的多个第一子像素pr和多个第三子像素pb以及位于第二行2n上的多个第二子像素pg以之字形配置布置。

130.多个第一子像素pr和多个第三子像素pb在第一列1m上彼此交替(例如,多个第一子像素pr和多个第三子像素pb在沿着y轴方向延伸的第一列1m上彼此交替地排列),多个第二子像素pg在与第一列1m相邻的第二列2m上彼此间隔开设定或预定的距离(例如,多个第二子像素pg在第二列2m上彼此排列,第二列2m沿着y轴方向延伸并且沿着x轴方向与第一列

1m相邻,其中,多个第二子像素pg中的在第二列2m上的相邻的第二子像素pg彼此间隔开设定或预定的距离),多个第三子像素pb和多个第一子像素pr在与第二列2m相邻的第三列3m上彼此交替,并且多个第二子像素pg在与第三列3m相邻的第四列4m上彼此间隔开设定或预定的距离,并且这种像素排列重复直到第m列。例如,偶数列和奇数列可以沿着x轴方向彼此交替地排列。

131.不同地描述这种像素排列结构,第一子像素pr可以布置在虚设四边形vs的四个顶点中的第一顶点和第三顶点(例如,第一面对顶点和第三面对顶点)处,虚设四边形vs将第二子像素pg的中心点作为虚设四边形vs的中心点,并且第三子像素pb可以布置在其余顶点(即,第二顶点和第四顶点)处。例如,当虚设四边形vs是矩形时,第一顶点和第三顶点可以通过与虚设四边形vs的中心相交的虚设对角线连接,并且第二顶点和第四顶点可以通过与虚设四边形vs的中心相交的虚设对角线连接。虚设四边形vs可以是矩形、菱形或正方形等。

132.这种像素排列结构可以被称为矩阵结构或结构。通过应用其中像素的颜色通过共享该像素的相邻的像素的颜色来表达的渲染,可以经由少量像素获得高分辨率。

133.尽管在图6中,多个主子像素pm以矩阵结构布置,但是实施例不限于此。例如,多个主子像素pm可以以诸如条纹结构、马赛克布置结构和三角形(delta)布置结构的各种合适的配置来布置。

134.图7和图8是示出根据实施例的组件区域ca中的像素排列结构的示意性布局图。

135.参照图7,在组件区域ca中,可以布置多个辅助子像素pa。辅助子像素pa可以包括第一子像素pr'、第二子像素pg'和第三子像素pb',并且第一子像素pr'、第二子像素pg'和第三子像素pb'可以分别发射红色、绿色和蓝色的光束(例如,光)。

136.组件区域ca可以包括像素组pg和透射区域ta,像素组pg包括至少一个辅助子像素pa。像素组pg和透射区域ta可以在x轴方向和y轴方向两者上彼此交替(例如,可以在x轴方向和y轴方向中的每一个方向上彼此交替地排列),并且可以以例如格子配置彼此排列。在这种情况下,组件区域ca可以具有多个像素组pg和多个透射区域ta。

137.像素组pg可以被限定为子像素集,在该子像素集中,多个辅助子像素pa以设定或预定的单位进行分组。例如,如图7中所示,单个像素组pg可以包括以结构布置的八个辅助子像素pa。例如,单个像素组pg可以包括两个第一子像素pr'、四个第二子像素pg'和两个第三子像素pb'。

138.在组件区域ca中,可以在x轴方向和y轴方向中的每一个方向上重复包括特定数量的像素组pg和特定数量的透射区域ta的基本单元u。在图7中,基本单元u可以具有其中两个像素组pg和布置在两个像素组pg周围的两个透射区域ta被分组的四边形形状。基本单元u为重复结构,并且不表示断开的配置。

139.参照图6和图7,在主显示区域mda中,可以设定具有与基本单元u的面积相同的面积的对应单元u'。在这种情况下,被包括在对应单元u'中的主子像素pm的数量可以大于被包括在基本单元u中的辅助子像素pa的数量。例如,被包括在基本单元u中的辅助子像素pa的数量可以是16,并且被包括在对应单元u'中的主子像素pm的数量可以是32,并且因此,布置在相等面积上的辅助子像素pa的数量与主子像素pm的数量可以是1:2的比率。

140.组件区域ca的像素排列结构被称为1/2结构,在该像素排列结构中,辅助子像素pa如图7中所示地以结构布置,并且分辨率是主显示区域mda的分辨率的1/2。被包括在像素组pg中的辅助子像素pa的数量或辅助子像素pa的布置方法可以根据组件区域ca的分辨率而修改。

141.参照图8,组件区域ca的像素排列结构可以是1/4结构。根据实施例,像素组pg包括以结构布置的八个辅助子像素pa,但是基本单元u可以仅包括一个像素组pg。基本单元u的未被一个像素组pg占据的其余区域可以被填充有透射区域ta(例如,可以对应于透射区域ta)。因此,布置在相等面积上的辅助子像素pa的数量和主子像素pm的数量可以是1:4的比率。在这种情况下,一个像素组pg可以被透射区域ta围绕。在一些实施例中,透射区域ta可以在一个像素组pg周围(例如,可以围绕一个像素组pg)。

142.尽管在图7和图8中,多个辅助子像素pa以矩阵结构布置,但是实施例不限于此。例如,多个辅助子像素pa可以以诸如条纹结构、马赛克布置结构和三角形(delta)布置结构的各种合适的配置来布置。

143.尽管在图7和图8中,每个辅助子像素pa的尺寸可以等于每个对应的主子像素pm的尺寸(例如,第一子像素pr的平面面积可以与第一子像素pr'的平面面积相同,第二子像素pg的平面面积可以与第二子像素pg'的平面面积相同,并且第三子像素pb的平面面积可以等于第三子像素pb'的平面面积),但是实施例不限于此。每个辅助子像素pa的尺寸可以大于与辅助子像素pa表示相同的颜色的每个主子像素pm的尺寸。例如,每个辅助子像素pa的第三子像素pb'的尺寸可以大于每个主子像素pm的第三子像素pb的尺寸。可以通过考虑组件区域ca和主显示区域mda的亮度和/或分辨率之间的差异来设计尺寸差异。

144.图9是根据实施例的显示面板的一部分的示意性截面图,即,主显示区域mda和组件区域ca的示意性截面图。

145.参照图9,显示设备1可以包括主显示区域mda和组件区域ca。组件区域ca可以具有透射区域ta。在主显示区域mda中可以布置主子像素pm,并且在组件区域ca中可以布置辅助子像素pa。

146.在主显示区域mda中,可以布置包括主薄膜晶体管tft和主存储电容器cst的主像素电路pc以及耦接(例如,连接)到主像素电路pc的作为显示元件的主有机发光二极管oled。在组件区域ca中,可以布置包括辅助薄膜晶体管tft'和辅助存储电容器cst'的辅助像素电路pc'以及耦接(例如,连接)到辅助像素电路pc'的作为显示元件的辅助有机发光二极管oled'。

147.根据实施例,采用有机发光二极管作为显示元件。然而,本公开不限于此。根据另一实施例,可以采用无机发光二极管和/或量子点发光二极管作为显示元件。

148.现在将描述其中堆叠有被包括在显示设备1中的组件的结构。显示设备1可以是基底100、缓冲层111、电路层pcl、显示元件层edl和薄膜封装层tfel的堆叠。

149.基底100可以包括顺序地堆叠在彼此上的第一基体层101、补偿层102、第一阻挡层103和第二阻挡层104。基底100还可以包括布置在第一基体层101下方的第二基体层105和第三阻挡层106。例如,第三阻挡层106可以在第一基体层101下方,并且第二基体层105可以在第三阻挡层106下方。

150.在组件区域ca中,底部金属层bml可以在第一阻挡层103与第二阻挡层104之间。底部金属层bml可以定位在辅助像素电路pc'下方,并且可以防止、减少或最小化由于从例如图2的组件40发射的光所导致的辅助薄膜晶体管tft'的特性的劣化。底部金属层bml可以防止、减少或最小化从组件40等发射的光或者朝向组件40行进的光通过耦接(例如,连接)到辅助像素电路pc'的布线之间的窄间隙的衍射。底部金属层bml可以不存在于透射区域ta中。例如,在一些实施例中,底部金属层bml可以具有与透射区域ta相对应(例如,与透射区域ta重叠)的第一孔h1。

151.偏置电压可以施加到底部金属层bml。由于底部金属层bml接收偏置电压,因此可以显著地降低发生静电放电的可能性。底部金属层bml可以包括(例如,可以是)铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和/或铜(cu)。底部金属层bml可以是包括(例如,是)前述材料的单层或多层。

152.在一些实施例中,组件区域ca的底部金属层bml可以对应于基本上整个组件区域ca(例如,可以与基本上整个组件区域ca重叠)。然而,底部金属层bml可以具有与透射区域ta重叠的第一孔h1。根据实施例,透射区域ta的形状和尺寸可以由限定在底部金属层bml中的第一孔h1的形状和尺寸来限定。

153.缓冲层111可以定位在基底100上,并且可以减少或防止异物、湿气和/或环境空气从基底100下方渗透,并且可以在基底100上提供平坦的表面。缓冲层111可以包括(例如,可以是)无机材料(诸如氧化物和/或氮化物)、有机材料和/或有机和无机化合物,并且可以是无机材料和有机材料的单层或多个层。例如,缓冲层111可以包括第一缓冲层111a和第二缓冲层111b。

154.电路层pcl可以在缓冲层111上,并且可以包括主像素电路pc和辅助像素电路pc'、第一绝缘层112、第二绝缘层113、第三绝缘层115和平坦化层117。主像素电路pc可以包括主薄膜晶体管tft和主存储电容器cst,并且辅助像素电路pc'可以包括辅助薄膜晶体管tft'和辅助存储电容器cst'。

155.主薄膜晶体管tft和辅助薄膜晶体管tft'可以在缓冲层111上方。主薄膜晶体管tft可以包括第一半导体层a1、第一栅极电极g1、第一源极电极s1和第一漏极电极d1,并且辅助薄膜晶体管tft'可以包括第二半导体层a2、第二栅极电极g2、第二源极电极s2和第二漏极电极d2。主薄膜晶体管tft可以耦接(例如,连接)到主有机发光二极管oled,并且可以用于驱动主有机发光二极管oled。辅助薄膜晶体管tft'可以耦接(例如,连接)到辅助有机发光二极管oled',并且可以用于驱动辅助有机发光二极管oled'。

156.根据实施例,第一半导体层a1和第二半导体层a2可以在缓冲层111上,并且可以各自包括(例如,可以各自是)多晶硅。根据实施例,第一半导体层a1和第二半导体层a2可以各自包括(例如,可以各自是)非晶硅。根据实施例,第一半导体层a1和第二半导体层a2可以各自包括(例如,可以各自是)选自由铟(in)、镓(ga)、锡(sn)、锆(zr)、钒(v)、铪(hf)、镉(cd)、锗(ge)、铬(cr)、钛(ti)和锌(zn)组成的组中的至少一种的氧化物。第一半导体层a1和第二半导体层a2中的每一个可以包括沟道区以及掺杂有杂质的源极区和漏极区。例如,对于第一半导体层a1和第二半导体层a2中的每一个,沟道区可以在源极区和漏极区之间。

157.第二半导体层a2可以与布置在第二半导体层a2下方的底部金属层bml至少部分地重叠。根据实施例,第二半导体层a2的宽度可以小于底部金属层bml的宽度。因此,当在与基

底100近似地或基本上正交或垂直的方向上进行投射时,第二半导体层a2可以与底部金属层bml完全地重叠。例如,在平面图中,第二半导体层a2可以与底部金属层bml完全地重叠。

158.第一绝缘层112可以覆盖第一半导体层a1和第二半导体层a2。第一绝缘层112可以包括(例如,可以是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。第一绝缘层112可以是包括(例如,是)选自前述无机绝缘材料中的一种或多种的单层或多层。

159.第一栅极电极g1和第二栅极电极g2可以布置在第一绝缘层112上方,以分别与第一半导体层a1(例如,第一半导体层a1的沟道区)和第二半导体层a2(例如,第二半导体层a2的沟道区)重叠。第一栅极电极g1和第二栅极电极g2可以各自包括(例如,可以各自是)钼(mo)、铝(al)、铜(cu)和/或钛(ti),并且可以各自是单层或多个层(多层)。例如,第一栅极电极g1和第二栅极电极g2可以各自是mo的单层。

160.第二绝缘层113可以覆盖第一栅极电极g1和第二栅极电极g2。第二绝缘层113可以包括(例如,可以是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。第二绝缘层113可以是包括(例如,是)选自前述无机绝缘材料中的一种或多种的单层或多层。

161.主存储电容器cst的第一上部电极ce2和辅助存储电容器cst'的第二上部电极ce2'可以在第二绝缘层113上方。

162.在主显示区域mda中,第一上部电极ce2可以与布置在第一上部电极ce2下方的第一栅极电极g1重叠。第一栅极电极g1和第一上部电极ce2可以构成主存储电容器cst,第一栅极电极g1和第一上部电极ce2彼此重叠且第二绝缘层113在第一栅极电极g1与第一上部电极ce2之间。根据实施例,第一栅极电极g1可以是主存储电容器cst的第一下部电极ce1。然而,本公开不限于此。根据实施例,可以包括主存储电容器cst的第一下部电极ce1作为单独的独立组件。例如,第一栅极电极g1可以是与第一下部电极ce1分离的组件。

163.在组件区域ca中,第二上部电极ce2'可以与布置在第二上部电极ce2'下方的第二栅极电极g2重叠。第二栅极电极g2和第二上部电极ce2'可以构成辅助存储电容器cst',第二栅极电极g2和第二上部电极ce2'彼此重叠且第二绝缘层113在第二栅极电极g2与第二上部电极ce2'之间。根据实施例,第二栅极电极g2可以是辅助存储电容器cst'的第二下部电极ce1'。然而,本公开不限于此。根据实施例,可以包括辅助存储电容器cst'的第二下部电极ce1'作为单独的独立组件。例如,第二栅极电极g2可以是与第二下部电极ce1'分离的组件。

164.第一上部电极ce2和第二上部电极ce2'可以各自包括(例如,可以各自是)铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和/或铜(cu),并且可以各自是包括(例如,是)选自前述材料中的一种或多种的单层或多层。

165.第三绝缘层115可以覆盖第一上部电极ce2和第二上部电极ce2'。第三绝缘层115可以包括(例如,可以是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌

(zno

x

,zno

x

可以是zno或zno2)。第三绝缘层115可以是包括(例如,是)选自前述无机绝缘材料中的一种或多种的单层或多层。

166.当第一绝缘层112、第二绝缘层113和第三绝缘层115被共同地称为无机绝缘层il时,无机绝缘层il可以具有与透射区域ta相对应(例如,与透射区域ta重叠)的第二孔h2。第二孔h2可以暴露缓冲层111或基底100的上表面的一部分。第二孔h2可以是与第一绝缘层112的对应于透射区域ta的开口、第二绝缘层113的对应于透射区域ta的开口和第三绝缘层115的对应于透射区域ta的开口重叠的结果。例如,第二孔h2可以包括第一绝缘层112的开口、第二绝缘层113的开口和第三绝缘层115的开口,第一绝缘层112的开口、第二绝缘层113的开口和第三绝缘层115的开口中的每一个可以彼此重叠。例如,在一些实施例中,第一绝缘层112的侧壁、第二绝缘层113的侧壁和第三绝缘层115的侧壁可以对齐或者可以形成一个或多个台阶形状,第一绝缘层112的侧壁、第二绝缘层113的侧壁和第三绝缘层115的侧壁分别形成第一绝缘层112的开口、第二绝缘层113的开口和第三绝缘层115的开口。这些开口可以通过单独的工艺单独地形成,或者可以通过相同的工艺同时地或并发地形成。在一些实施例中,当这些开口通过单独的工艺形成时,第二孔h2的内表面不光滑,并且具有诸如楼梯形状的一个或多个台阶。

167.数据线dl、第一源极电极s1和第二源极电极s2以及第一漏极电极d1和第二漏极电极d2可以在第三绝缘层115上。数据线dl、第一源极电极s1和第二源极电极s2以及第一漏极电极d1和第二漏极电极d2中的每一个可以包括(例如,可以是)包括(例如,是)mo、al、cu和/或ti的导电材料,并且可以是包括(例如,是)选自前述材料中的一种或多种的多层或单层。例如,数据线dl、第一源极电极s1和第二源极电极s2以及第一漏极电极d1和第二漏极电极d2中的每一个可以形成为ti/al/ti的多层。

168.平坦化层117可以覆盖数据线dl、第一源极电极s1和第二源极电极s2以及第一漏极电极d1和第二漏极电极d2。平坦化层117可以具有平坦的上表面,使得定位在平坦化层117上的第一像素电极121和第二像素电极121'形成为平坦的(例如,形成在平坦的表面上)。

169.平坦化层117可以包括(例如,可以是)有机材料和/或无机材料,并且可以具有单层结构或多层结构。平坦化层117可以包括(例如,可以是)诸如苯并环丁烯(bcb)、聚酰亚胺、六甲基二硅醚(hmdso)、聚甲基丙烯酸甲酯(pmma)和/或聚苯乙烯(ps)的聚合物(例如,商用聚合物)、具有酚基基团的聚合物衍生物、丙烯酸基聚合物、酰亚胺基聚合物、芳基醚基聚合物、酰胺基聚合物、氟基聚合物、对二甲苯基聚合物和/或乙烯醇基聚合物等。平坦化层117可以包括(例如,可以是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。当形成平坦化层117时,可以形成一层,并且然后可以在该层的上表面上执行化学和/或机械抛光以提供平坦的上表面。

170.平坦化层117可以具有第三孔h3以对应于透射区域ta。第三孔h3可以与第二孔h2重叠。图9示出了第三孔h3大于第二孔h2(例如,具有比第二孔h2大的平面面积)。然而,本公开不限于此。根据实施例,平坦化层117可以覆盖无机绝缘层il的第二孔h2的边缘,并且第三孔h3可以具有比第二孔h2的面积(例如,平面面积)小的面积(例如,平面面积)。

171.平坦化层117可以具有过孔,选自主薄膜晶体管tft的第一源极电极s1和第一漏极

电极d1中的一者经由所述过孔暴露,并且第一像素电极121可以经由所述过孔接触由所述过孔暴露的第一源极电极s1或第一漏极电极d1,并且可以(例如,通过所述过孔)电耦接(例如,电连接)到主薄膜晶体管tft。平坦化层117可以包括另一开口,选自辅助薄膜晶体管tft'的第二源极电极s2和第二漏极电极d2中的一者经由所述另一开口暴露,并且第二像素电极121'可以经由所述另一开口接触由所述另一开口暴露的第二源极电极s2或第二漏极电极d2,并且可以(例如,通过所述另一开口)电耦接(例如,电连接)到辅助薄膜晶体管tft'。

172.在图9中,包括一个平坦化层。然而,本公开不限于此。根据实施例,可以包括两个平坦化层。在一个或多个方面,包括两个平坦化层可能更有利于高集成度。

173.第一像素电极121和第二像素电极121'可以在平坦化层117上。第一像素电极121和第二像素电极121'可以包括(例如,可以是)导电氧化物,诸如氧化铟锡(ito)、氧化铟锌(izo)、氧化锌(zno)、氧化铟(in2o3)、氧化铟镓(igo)和/或氧化铝锌(azo)。第一像素电极121和第二像素电极121'中的每一个可以包括反射层,所述反射层包括(例如,是)例如银(ag)、镁(mg)、铝(al)、铂(pt)、钯(pd)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)或这些材料的化合物。在一些实施例中,第一像素电极121和第二像素电极121'中的每一个可以具有位于前述反射层上方和/或下方的结构,所述结构包括包含(例如,是)ito、izo、zno和/或in2o3的膜。在这种情况下,第一像素电极121和第二像素电极121'中的每一个可以具有ito/ag/ito的堆叠结构。

174.像素限定层119可以定位在平坦化层117上。像素限定层119可以在平坦化层117上,并且可以覆盖第一像素电极121的边缘。在像素限定层119中可以限定第一开口op1,第一开口op1暴露第一像素电极121的至少一部分。像素限定层119可以在平坦化层117上,并且可以覆盖第二像素电极121'的边缘。在像素限定层119中可以限定第二开口op2,第二开口op2暴露第二像素电极121'的至少一部分。

175.第一开口op1和第二开口op2可以分别限定主有机发光二极管oled和辅助有机发光二极管oled'的发光区域(即,主子像素pm和辅助子像素pa)的尺寸和形状。

176.通过增加第一像素电极121和第二像素电极121'的边缘与相对电极123的位于第一像素电极121和第二像素电极121'上方的部分之间的距离,像素限定层119可以防止在第一像素电极121和第二像素电极121'的边缘上发生电弧等,或者可以抑制在第一像素电极121和第二像素电极121'的边缘上形成这种电弧等。像素限定层119可以例如经由旋涂等由诸如聚酰亚胺、聚酰胺、丙烯酸树脂、苯并环丁烯、六甲基二硅醚(hmdso)和/或酚醛树脂的有机绝缘材料形成。

177.在像素限定层119上,可以进一步布置用于防止或减少由于掩模导致的损坏的间隔件。间隔件可以与像素限定层119一体地形成。例如,间隔件和像素限定层119可以通过利用(例如,使用)半色调掩模工艺根据相同的工艺同时地或并发地形成。在一些实施例中,间隔件和像素限定层119可以包括(例如,可以是)相同的材料。

178.像素限定层119可以具有与透射区域ta相对应的第四孔h4。第四孔h4可以与第二孔h2和第三孔h3重叠。由于第二孔h2至第四孔h4,透射区域ta中的透光率可以改善。尽管缓冲层111连续地延伸以对应于图9中的透射区域ta,但是本公开不限于此。在一些实施例中,缓冲层111可以具有定位在透射区域ta中的孔,并且缓冲层111中的孔可以与第二孔h2至第

四孔h4重叠。稍后将描述的相对电极123的一部分可以布置在第二孔h2至第四孔h4的内表面上。

179.第一发射层122b和第二发射层122b'可以分别布置在像素限定层119的第一开口op1和第二开口op2内,以分别对应于第一像素电极121和第二像素电极121'。第一发射层122b和第二发射层122b'可以包括(例如,可以是)高分子量材料和/或低分子量材料,并且可以发射红光、绿光、蓝光和/或白光。

180.根据实施例,有机功能层122e可以在第一发射层122b和第二发射层122b'中的每一者的上方和/或下方。有机功能层122e可以包括第一功能层122a和/或第二功能层122c。根据实施例,可以省略第一功能层122a或第二功能层122c。

181.第一功能层122a可以在第一发射层122b和第二发射层122b'中的每一者的下方。第一功能层122a可以是包括(例如,是)有机材料的单层或多个层。第一功能层122a可以是作为单层的空穴传输层(htl)。在一些实施例中,第一功能层122a可以包括空穴注入层(hil)和/或htl。第一功能层122a可以一体地提供以对应于被包括在主显示区域mda中的主有机发光二极管oled和被包括在组件区域ca中的辅助有机发光二极管oled'。

182.第二功能层122c可以在第一发射层122b和第二发射层122b'中的每一者的上方。第二功能层122c可以是包括(例如,是)有机材料的单层或多个层。第二功能层122c可以包括电子传输层(etl)和/或电子注入层(eil)。第二功能层122c可以一体地提供以对应于被包括在主显示区域mda中的主有机发光二极管oled和被包括在组件区域ca中的辅助有机发光二极管oled'。

183.相对电极123可以在第二功能层122c上。相对电极123可以包括(例如,可以是)具有低功函数的导电材料。例如,相对电极123可以包括(半)透明层,所述(半)透明层包括(例如,是)例如银(ag)、镁(mg)、铝(al)、铂(pt)、钯(pd)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、锂(li)、钙(ca)或这些材料的合金。在一些实施例中,相对电极123还可以包括位于(半)透明层上的诸如ito、izo、zno和/或in2o3的层,所述(半)透明层包括(例如,是)上述材料中的任意一种。相对电极123可以一体地提供以对应于被包括在主显示区域mda中的主有机发光二极管oled和被包括在组件区域ca中的辅助有机发光二极管oled'。

184.布置在主显示区域mda中的从第一像素电极121到相对电极123的各层(例如,第一像素电极121、相对电极123以及第一像素电极121与相对电极123之间的各层)(例如,各层的部分)可以构成主有机发光二极管oled。布置在组件区域ca中的从第二像素电极121'到相对电极123的各层(例如,第二像素电极121'、相对电极123以及第二像素电极121'与相对电极123之间的各层)(例如,各层的部分)可以构成辅助有机发光二极管oled'。

185.包括(例如,是)有机材料的覆盖层可以在相对电极123上。可以提供覆盖层以保护相对电极123,并且还提高光提取效率。覆盖层可以包括(例如,可以是)具有比相对电极123的折射率(折射系数)高的折射率的有机材料。

186.相对电极123可以具有与透射区域ta相对应的第五孔h5。与透射区域ta相对应的第五孔h5可以被理解为与透射区域ta重叠的第五孔h5。在一些实施例中,第五孔h5可以与第二孔h2至第四孔h4中的每一者重叠。在图9中,第五孔h5的面积(例如,宽度、直径和/或平面面积)比形成在无机绝缘层il中的第二孔h2的面积宽。然而,实施例不限于此。在一些实施例中,第五孔h5的面积可以小于或等于第二孔h2的面积。

187.由于第五孔h5,在透射区域ta中不存在相对电极123的一部分,并且因此透射区域ta中的透光率可以显著地增加。可以利用(例如,使用)各种合适的方法形成包括第五孔h5的相对电极123。根据实施例,在用于形成相对电极123的材料沉积在基底100的整个表面上之后,所沉积的材料中的对应于透射区域ta的一部分可以经由激光剥离被去除,并且因此可以形成具有第五孔h5的相对电极123。根据实施例,可以通过金属自构图(msp)形成具有第五孔h5的相对电极123。根据另一实施例,具有第五孔h5的相对电极123可以经由利用(例如,使用)精细金属掩模(fmm)的沉积方法形成。

188.薄膜封装层tfel可以作为封装构件布置在显示设备1的显示元件层edl上方。例如,主有机发光二极管oled和辅助有机发光二极管oled'可以被薄膜封装层tfel密封。薄膜封装层tfel可以在相对电极123上。薄膜封装层tfel可以防止或阻挡外部湿气和/或异物渗透到主有机发光二极管oled和辅助有机发光二极管oled'中。

189.薄膜封装层tfel可以包括至少一个无机封装层和至少一个有机封装层。关于这一点,图9示出了薄膜封装层tfel是第一无机封装层131、有机封装层132和第二无机封装层133的堆叠。根据实施例,可以适当地修改有机封装层的数量、无机封装层的数量以及有机封装层和无机封装层堆叠的顺序。

190.第一无机封装层131和第二无机封装层133可以各自包括(例如,可以各自是)至少一种无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2),并且可以例如通过化学气相沉积(cvd)等形成。有机封装层132可以包括(例如,可以是)基于聚合物的材料。基于聚合物的材料的示例可以包括硅基树脂、丙烯酸基树脂、环氧基树脂、聚酰亚胺和/或聚乙烯。

191.第一无机封装层131、有机封装层132和第二无机封装层133可以各自一体地提供以覆盖主显示区域mda和组件区域ca。因此,第一无机封装层131、有机封装层132和第二无机封装层133可以各自布置在无机绝缘层il的第二孔h2、平坦化层117的第三孔h3、像素限定层119的第四孔h4和相对电极123的第五孔h5内。

192.图10是根据实施例的图9的部分a的放大图,并且图11是根据实施例的图9的部分b的放大图。

193.参照图9、图10和图11,基底100可以包括顺序地堆叠在彼此上的第一基体层101、补偿层102、第一阻挡层103和第二阻挡层104。基底100还可以包括布置在第一基体层101下方的第二基体层105和第三阻挡层106。

194.第一基体层101和第二基体层105中的每一个可以包括(例如,可以是)具有高耐热性的聚合物树脂。例如,第一基体层101和第二基体层105可以各自包括(例如,可以各自是)选自由聚醚砜、聚丙烯酸酯、聚醚酰亚胺、聚萘二甲酸乙二醇酯、聚对苯二甲酸乙二醇酯、聚苯硫醚、聚芳酯、聚酰亚胺、聚碳酸酯、三乙酸纤维素、乙酸丙酸纤维素和聚亚芳基醚砜(polyarylene ether sulfone)组成的组中的至少一种。

195.例如,聚酰亚胺具有高的机械强度,并且具有大约450℃的玻璃化转变温度,并且因此具有比一些其它聚合物树脂高的耐热性。因此,当第一基体层101和第二基体层105包括(例如,是)聚酰亚胺时,即使当在高温下进行在第二基体层105上形成第三阻挡层106的工艺和在第一基体层101上形成补偿层102、第一阻挡层103和第二阻挡层104的工艺时,第

一基体层101和第二基体层105也不会下垂(例如,不会由于高温而变形),并且可以被第三阻挡层106、补偿层102和第一阻挡层103的负荷稳定地支撑。第一基体层101和第二基体层105对于氧和/或湿气是高渗透性的,第一基体层101和第二基体层105各自包括(例如,各自是)包含(例如,是)聚酰亚胺的上述聚合物树脂。因此,在第二基体层105与第一基体层101之间以及在第一基体层101上可以分别包括第三阻挡层106和第一阻挡层103,第三阻挡层106和第一阻挡层103各自阻挡氧和/或湿气的渗透。

196.第二基体层105的厚度t1可以大于第一基体层101的厚度t3。因为包括第二基体层105以支撑布置在第二基体层105上的组件,所以具有比第一基体层101高的机械强度的第二基体层105可以在显示设备的制造工艺中更稳定。因此,第二基体层105的厚度t1可以是大约9μm至11μm(例如,从大约9μm至大约11μm),并且第一基体层101的厚度t3可以是大约5μm至7μm(例如,从大约5μm至大约7μm)。

197.当第二基体层105和第一基体层101包括(例如,是)聚酰亚胺时,对于具有550nm的波长的光,第二基体层105的折射率n1和第一基体层101的折射率n3可以各自具有大约1.9的值。

198.第三阻挡层106可以在第二基体层105与第一基体层101之间。第三阻挡层106可以防止、减少或最小化诸如氧和/或湿气的杂质元素渗透到第一基体层101上方。根据实施例,第三阻挡层106可以包括(例如,可以是)无机绝缘材料,诸如氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。例如,第三阻挡层106可以包括(例如,可以是)氧化硅(sio

x

)。

199.第三阻挡层106的厚度t2可以是至(例如,从大约至大约)。当第三阻挡层106的厚度t2小于时,湿气和/或氧的阻挡率可以显著地降低。当第三阻挡层106的厚度t2超过时,用于形成第三阻挡层106的工艺时间段可能增加。

200.对于具有550nm的波长的光,第三阻挡层106的折射率n2可以具有大约1.3至大约1.6的值。

201.第一阻挡层103可以在第一基体层101上(例如,在补偿层102上)。第一阻挡层103可以防止、减少或最小化诸如氧和/或湿气的杂质元素向上渗透(例如,朝向缓冲层111渗透)。根据实施例,第一阻挡层103可以包括(例如,可以是)无机绝缘材料,诸如氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。例如,第一阻挡层103可以包括(例如,可以是)氧化硅(sio

x

)。

202.第一阻挡层103的厚度t5可以是至对于具有550nm的波长的光,第一阻挡层103的折射率n5可以具有1.3至1.6的值。

203.补偿层102可以在第一基体层101与第一阻挡层103之间。可以包括补偿层102以改善透射区域ta的透光率。根据实施例,补偿层102可以包括(例如,可以是)无机绝缘材料,诸如氮化硅(sin

x

)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。在一些实施例中,补偿层102可以包括(例如,可以是)氮氧化硅(sio

x

ny)(x≥0,y≥0)。

204.补偿层102的厚度t4可以是至当补偿层102的厚度t4小于时,透射区域ta的透光率可能不会改善以及/或者可能不是期望的。当补偿层102的厚度t4超过时,造成了其中被包括在补偿层102中的氮组分与第一半导体层a1和第二半导体层a2的氢元素结合的脱氢,并且第一半导体层a1和第二半导体层a2的特性可能改变。

205.因为包括补偿层102以改善透射区域ta的透光率,所以补偿层102的折射率n4可以具有在第一基体层101的折射率n3与第一阻挡层103的折射率n5之间的值。

206.在补偿层102是氮氧化硅(sio

x

ny)的实施例中,构成补偿层102的氮氧化硅(sio

x

ny)的折射率n4可以根据氧和氮之间的比率进行调整。例如,当被包括在氮氧化硅(sio

x

ny)中的氧的量增加时(例如,当氮氧化硅中的氧与氮的比率增加时),补偿层102的折射率n4可以降低,并且当被包括在氮氧化硅(sio

x

ny)中的氮的量增加时(例如,当氮氧化硅中的氮与氧的比率增加时),补偿层102的折射率n4可以增加。因此,补偿层102的折射率n4可以在1.5与1.8之间调整。根据实施例,补偿层102的折射率n4可以是大约1.65至大约1.75。因为不包括氧的氮化硅(sin

x

)的折射率是大约1.9并且因此类似于聚酰亚胺(pi)的折射率,所以氮化硅(sin

x

)可能不适合于补偿层102。

207.当不包括补偿层102并且第一基体层101和第一阻挡层103彼此直接接触时,由于第一基体层101的折射率n3与第一阻挡层103的折射率n5之间的差异,光可能不被透射并且可能损失。根据实施例,因为第一基体层101与第一阻挡层103之间的补偿层102的折射率n4具有在第一基体层101的折射率n3与第一阻挡层103的折射率n5之间的值,所以损失的光的量可以减少。

208.根据实施例,补偿层102可以在第二基体层105与第三阻挡层106之间。在一些实施例中,补偿层102可以在第一基体层101与第一阻挡层103之间,并且另一补偿层(例如,具有分别选自补偿层102可以具有的如上所述的厚度和组成的厚度和组成的补偿层)可以在第二基体层105与第三阻挡层106之间。

209.第二阻挡层104可以在(例如,直接在)第一阻挡层103上。根据实施例,第二阻挡层104可以包括(例如,可以是)无机绝缘材料,诸如氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。例如,第二阻挡层104可以包括(例如,可以是)与被包括在第一阻挡层103中的材料相同的材料。

210.第二阻挡层104的厚度t6可以是至对于具有550nm的波长的光,第二阻挡层104的折射率n6可以具有1.3至1.6的值。

211.缓冲层111可以在第二阻挡层104上。缓冲层111可以包括第一缓冲层111a和第二缓冲层111b。

212.第一缓冲层111a可以在第二阻挡层104上。例如,第一缓冲层111a可以直接在第二阻挡层104上。根据实施例,第一缓冲层111a可以包括(例如,可以是)无机绝缘材料,诸如氧化硅(sio

x

)、氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。例如,第一缓冲层111a可

以包括(例如,可以是)氮化硅(sin

x

)。

213.第一缓冲层111a的厚度t7可以是至在工艺(例如,制造或制作工艺)中,可能难以将第一缓冲层111a的厚度t7形成为小于另一方面,当第一缓冲层111a的厚度t7超过时,透射区域ta的透光率可能劣化。与被包括在阻挡层和补偿层中的氮相比,在第一缓冲层111a包括(例如,是)氮化硅(sin

x

)的一些实施例中,被包括在第一缓冲层111a中的氮化硅(sin

x

)中的氮可以通过将适量的氢供应到第一半导体层a1和第二半导体层a2来改善第一半导体层a1和第二半导体层a2的特性。因此,第一缓冲层111a可以包括(例如,可以是)氮化硅(sin

x

),并且考虑到透光率,第一缓冲层111a的厚度t7可以是至的厚度。

214.对于具有550nm的波长的光,第一缓冲层111a的折射率n7可以具有1.8至2的值。

215.第二缓冲层111b可以在第一缓冲层111a上。根据实施例,第二缓冲层111b可以包括(例如,可以是)无机绝缘材料,诸如氮化硅(sin

x

)、氮氧化硅(sio

x

ny)、氧化铝(al2o3)、氧化钛(tio2)、氧化钽(ta2o5)、氧化铪(hfo2)和/或氧化锌(zno

x

,zno

x

可以是zno或zno2)。例如,第二缓冲层111b可以包括(例如,可以是)氧化硅(sio

x

)。

216.第二缓冲层111b的厚度t8可以是至当第二缓冲层111b的厚度t8小于时,对于第二缓冲层111b而言,可能难以起到缓冲层的作用(例如,难以执行其意图作为缓冲层的功能),并且,当第二缓冲层111b的厚度t8超过时,用于形成层(例如,第二缓冲层111b和/或第二缓冲层111b从其形成的层)的工艺时间段可能增加。

217.对于具有550nm的波长的光,第二缓冲层111b的折射率n8可以具有1.3至1.6的值。

218.底部金属层bml可以在图9的基底100与缓冲层111之间,并且缓冲层111可以包括第一缓冲层111a和第二缓冲层111b,第一缓冲层111a包括(例如,是)氮化硅(sin

x

),第二缓冲层111b包括(例如,是)氧化硅(sio

x

)。第一缓冲层111a可以具有大约的厚度,并且第二缓冲层111b可以具有大约的厚度。在一些实施例中,底部金属层bml可以在第一阻挡层103与第二阻挡层104之间。

219.然而,当第一缓冲层111a包括(例如,是)氮化硅(sin

x

)并且包括(例如,是)氮化硅(sin

x

)的第一缓冲层111a的厚度从减小到以改善上面结构中的透射区域ta的透光率时,供应到主薄膜晶体管tft的第一半导体层a1的氢的量由于氮化硅(sin

x

)的厚度的减小而减少,并且因此主薄膜晶体管tft的特性变得劣化,但是由底部金属层bml反射的光被辅助薄膜晶体管tft'的第二半导体层a2吸收,并且因此辅助薄膜晶体管tft'的特性可以改善。换句话说,主薄膜晶体管tft的特性变得劣化,并且辅助薄膜晶体管tft'的特性变得改善,并且因此产生主薄膜晶体管tft的特性和辅助薄膜晶体管tft'的特性之间的差异。由于主薄膜晶体管tft的特性和辅助薄膜晶体管tft'的特性之间的差异,在主显示区域mda的亮度和组件区域ca的亮度之间产生差异。

220.根据本公开的实施例,底部金属层bml可以在第一阻挡层103与第二阻挡层104之

间。底部金属层bml布置在第一阻挡层103与第二阻挡层104之间,并且因此,主薄膜晶体管tft和辅助薄膜晶体管tft'具有类似的下部堆叠结构。因此,可以防止、减少或最小化在主薄膜晶体管tft的特性和辅助薄膜晶体管tft'的特性之间产生差异。因此,可以防止、减少或最小化在主显示区域mda的亮度和组件区域ca的亮度之间产生差异。

221.因为从透射区域ta去除图9的无机绝缘层il、图9的平坦化层117、图9的像素限定层119和图9的相对电极123,所以有机功能层122e和薄膜封装层tfel可以顺序地堆叠在透射区域ta的缓冲层111(例如,透射区域ta中的缓冲层111的部分)上。例如,有机功能层122e可以在(例如,直接在)缓冲层111的被第二孔h2暴露的部分上,并且薄膜封装层tfel可以在(例如,直接在)透射区域ta中的有机功能层122e的部分上。薄膜封装层tfel可以包括顺序地堆叠在彼此上的第一无机封装层131、有机封装层132和第二无机封装层133。

222.位于透射区域ta上(例如,位于透射区域ta中)的有机功能层122e的折射率n9可以是大约1.9,并且有机封装层132的折射率n11可以是大约1.5。有机功能层122e与有机封装层132之间的第一无机封装层131的折射率n10可以具有在有机功能层122e的折射率n9与有机封装层132的折射率n11之间的值。根据实施例,当第一无机封装层131包括单层时,第一无机封装层131的折射率n10可以具有1.55至1.7的值。

223.图12是根据实施例的图9的部分a的放大图。图12的实施例与图10的实施例的不同之处在于,第二阻挡层104包括第一层104a和第二层104b。图12和图10中的相同的附图标记表示相同的元件,并且因此可以不提供其重复描述。

224.参照图12,第二阻挡层104可以在(例如,直接在)第一阻挡层103上。第二阻挡层104可以包括顺序地堆叠在彼此上的第一层104a和第二层104b。

225.根据实施例,因为在将第一缓冲层111a沉积到第二阻挡层104上之前,包括(例如,是)氯气(cl2)的等离子体被辐射到第二阻挡层104的上表面,所以可以将第二阻挡层104形成为具有包括第一层104a和第二层104b的结构,第二层104b布置在第一层104a上并且包括比第一层104a更大量的氯(cl)。根据实施例,因为第一缓冲层111a通过利用(例如,使用)包括(例如,是)氯(cl)的气体(例如,二氯硅酸(sih2cl2)、三氯硅酸(sihcl3)或四氯化硅(sicl4))沉积在第二阻挡层104上,所以可以通过包括第一层104a和第二层104b的结构形成第二阻挡层104,第二层104b布置在第一层104a上并且包括比第一层104a更大量的氯(cl)。

226.被包括在第二阻挡层104的第二层104b中的氯的量(例如,浓度、wt%、at%等)可以大于被包括在第一层104a中的氯的量。例如,与第一层104a相比,在第二层104b中可以包括更大量的cl。

227.在第二阻挡层104中包括包含高cl含量的第二层104b可以防止、阻止或最小化氢渗透到第二阻挡层104上方,从而防止、减少或最小化对第一半导体层a1和第二半导体层a2的特性的改变。此外,在第二阻挡层104中包括包含高cl含量的第二层104b可以有助于主薄膜晶体管tft和辅助薄膜晶体管tft'具有目标(例如,期望的或优异的)特性。

228.图13是根据实施例的图9的部分b的放大图。图13的实施例与图11的实施例的不同之处在于,第一无机封装层131包括具有不同的折射率的复合层。图13和图11中的相同的附图标记表示相同的元件,并且因此可以不提供其重复描述。

229.参照图13,薄膜封装层tfel的第一无机封装层131可以包括堆叠在彼此上的第一

折射率层131a和第二折射率层131b,其中,第二折射率层131b布置在第一折射率层131a上。第一折射率层131a的折射率n10a可以大于第二折射率层131b的折射率n10b。根据实施例,第一折射率层131a可以包括(例如,可以是)氮氧化硅(sio

x

ny)(x≥0,y≥0),并且因此可以具有大约1.6至大约1.7的折射率n10a。第二折射率层131b可以包括(例如,可以是)氮氧化硅(sio

x

ny)(x≥0,y≥0),并且因此可以具有大约1.5至大约1.6的折射率n10b。然而,本公开不限于此。根据实施例,第一折射率层131a的折射率n10a可以小于第二折射率层131b的折射率n10b。

230.通过以层为单位调整有机功能层122e与有机封装层132之间的第一无机封装层131的折射率,可以减小各层之间的界面上的折射率的差异,并且因此可以改善透射区域ta的透光率。当第一无机封装层131包括第一折射率层131a和第二折射率层131b时,透光率的根据各个波长的波动可以减小(例如,可以改善透光率在各个波长之间的一致性)。第一无机封装层131的厚度可以是1μm至2μm。

231.图14至图22各自是根据实施例的用于说明制造显示设备的方法的示意性截面图。

232.现在将参照图14至图22描述制造显示设备的方法。

233.制造显示设备的方法可以包括在第一基体层101上形成补偿层102的操作(例如,任务或动作)、在补偿层102上形成第一阻挡层103的操作、在第一阻挡层103上形成底部金属层bml的操作、在底部金属层bml上形成第二阻挡层104的操作、以及在第二阻挡层104上形成缓冲层111的操作。

234.参照图14,第三阻挡层106可以形成在第二基体层105上,并且第一基体层101可以形成在第三阻挡层106上。第一基体层101和第二基体层105中的每一个可以包括(例如,可以是)聚酰亚胺。第二基体层105的厚度可以大于第一基体层101的厚度。对于具有550nm的波长的光,第二基体层105的折射率和第一基体层101的折射率可以各自具有大约1.9的值。

235.第三阻挡层106可以包括(例如,可以是)氧化硅(sio

x

),并且可以具有至的厚度。对于具有550nm的波长的光,第三阻挡层106的折射率可以具有大约1.3至大约1.6的值。

236.参照图15,补偿层102可以形成在第一基体层101上。补偿层102可以包括(例如,可以是)氮氧化硅(sio

x

ny)(x≥0,y≥0),并且可以具有至的厚度。补偿层102的折射率可以是大约1.65至大约1.75。

237.参照图16,第一阻挡层103可以形成在补偿层102上。第一阻挡层103可以包括(例如,可以是)氧化硅(sio

x

),并且可以具有至的厚度。对于具有550nm的波长的光,第一阻挡层103可以具有大约1.3至大约1.6的值。

238.参照图17,底部金属层bml可以形成在(例如,直接形成在)第一阻挡层103上。透射区域ta可以由底部金属层bml限定。底部金属层bml可以不布置在透射区域ta中,并且可以限定(例如,从而限定)透射区域ta。因为底部金属层bml未布置在透射区域ta中,所以可以改善透射区域ta的透光率。

239.参照图18,第二阻挡层104可以形成在底部金属层bml上。第二阻挡层104可以包括(例如,可以是)与被包括在第一阻挡层103中的材料相同的材料。第二阻挡层104可以具有

至的厚度,并且对于具有550nm的波长的光,第二阻挡层104的折射率可以具有1.3至1.6的值。在一些实施例中,底部金属层bml可以形成在组件区域ca中而不是形成在主显示区域mda中,并且第二阻挡层104可以形成为覆盖位于组件区域ca中的底部金属层bml,并且可以形成在位于主显示区域mda中的第一阻挡层103上。

240.参照图19,第一缓冲层111a可以形成在(例如,直接形成在)第二阻挡层104上。第一缓冲层111a可以包括(例如,可以是)氮化硅(sin

x

),并且可以具有至的厚度。对于具有550nm的波长的光,第一缓冲层111a的折射率可以具有1.8至2(2.0)的值。

241.参照图20,第二缓冲层111b可以形成在第一缓冲层111a上。第二缓冲层111b可以包括(例如,可以是)与被包括在第一缓冲层111a中的材料(例如,构成第一缓冲层111a的材料)不同的材料。例如,第二缓冲层111b可以包括(例如,可以是)氧化硅(sio

x

)。第二缓冲层111b可以具有至的厚度。对于具有550nm的波长的光,第二缓冲层111b的折射率可以具有1.3至1.6的值。

242.在主显示区域mda的第二缓冲层111b(例如,在主显示区域mda中的第二缓冲层111b)上可以形成主薄膜晶体管、主存储电容器和主有机发光二极管,并且在组件区域ca的第二缓冲层111b(例如,在组件区域ca中的第二缓冲层111b)上可以形成辅助薄膜晶体管、辅助存储电容器和辅助有机发光二极管。可以形成薄膜封装层以覆盖主有机发光二极管和辅助有机发光二极管。

243.参照图21和图22,根据实施例,在底部金属层bml上形成第二阻挡层104的操作之后,可以进一步执行将包括(例如,是)氯气(cl2)的等离子体辐射到第二阻挡层104的上表面上的操作。

244.通过将包括(例如,是)氯气(cl2)的等离子体辐射到第二阻挡层104的上表面上,氯(cl)的至少一部分可以扩散或渗透到第二阻挡层104中。因此,第二阻挡层104可以包括第一层104a和第二层104b,第二层104b包括比第一层104a更大量的氯(cl)。

245.根据实施例,通过利用(例如,使用)包括氯(cl)的气体(例如,二氯硅酸(sih2cl2)、三氯硅酸(sihcl3)和/或四氯化硅(sicl4))将第一缓冲层111a沉积在第二阻挡层104上,氯(cl)的至少一部分可以扩散或渗透到第二阻挡层104中,并且因此可以通过包括第一层104a和第二层104b的结构形成第二阻挡层104(例如,可以将第二阻挡层104形成为具有包括第一层104a和第二层104b的结构),第二层104b包括比第一层104a更大量的氯(cl)。

246.在第二阻挡层104中包括包含高cl含量的第二层104b可以防止、减少或最小化氢渗透到第二阻挡层104上方,使得主薄膜晶体管和辅助薄膜晶体管可以具有设定或预设的特性。

247.根据如上所述的实施例,主显示区域的主薄膜晶体管和组件区域的辅助薄膜晶体管具有类似的下部堆叠结构,并且因此可以减少主薄膜晶体管的特性和辅助薄膜晶体管的特性之间的差异。

248.此外,减少主薄膜晶体管的特性和辅助薄膜晶体管的特性之间的差异可以防止、减少或最小化在主显示区域的亮度和组件区域的亮度之间产生差异。

249.应当理解,本文中所描述的实施例应当仅在描述性的意义上考虑,而不是出于限制的目的。每个实施例内的特征和/或方面的描述通常应当被认为可以用于其它实施例中的其它类似特征或方面。虽然已经参照附图描述了一个或多个实施例,但是本领域普通技术人员将理解,在不脱离如由权利范围及其等同物限定的本公开的精神和范围的情况下,可以在其中进行形式和细节上的各种适当的改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1