一种带有高铜柱的芯片封装结构的制作方法

1.本发明涉及一种带有高铜柱的芯片封装结构,属于集成电路封装技术领域。

背景技术:

2.集成电路的发展趋势是越来越追求多功能、高性能、高散热、高集成度、高可靠性和低成本。芯片封装技术在集成电路的制作过程中发挥着至关重要的作用,芯片封装工艺的可行性、封装质量、封装可靠性,直接决定了集成电路是否满足设计要求以及能否被制造出来。封装工艺决定了集成电路的结构和性能。封装成本在集成电路总成本中所占的比例也越来越大。随着集成电路的晶圆制程发展到纳米级,芯片上集成的晶体管数量向更高密度发展,输入输出信号io引脚数量越来越高,io引脚的间距发展到低于100μm以下,封装工艺技术朝着更高密度方向发展。铜柱凸点封装技术,以其独特的凸点细间距优势,良好的导热性能、抗电迁移性能、质量一致性和可靠性,已经成为先进芯片封装工艺的核心技术,主导着芯片封装技术向高密度、超细间距方向发展。

3.目前,使用铜柱封装技术方案主要分两种现有技术:(一)直接使用单颗铜柱,单颗铜柱包装成编带方式;(二)激光开槽电镀铜方式。

4.现有技术(一)的缺陷:

5.现有技术(一)是直接使用单颗铜柱。单颗铜柱是采用机械加工方式单颗地加工出来,进行表面处理然后做成编带方式,便于自动化方式使用。该工艺实施的主要步骤如下:

6.(1)铜板、机加工模具的准备;

7.(2)铜柱冲压机械加工成型,得到需要尺寸的单颗铜柱;

8.(3)铜柱表面处理;

9.(4)铜柱编带包装,将单颗铜柱包装在卷带料中,方便封装设备的自动化方式使用。

10.现有技术(一)即单颗铜柱编带使用方式,具有低本、生产率高的特点,但是并未在封装工艺中广泛被使用,主要问题如下:

11.(1)加工焊锡bump凸起难度大:单颗铜柱不利于固定、在铜柱末端加工出焊锡bump难度大;

12.(2)编带包装的单颗铜柱在封装工艺中,是一颗一颗地使用,生产效率低;

13.(3)单颗铜柱的尺寸,由于机械加工方法和电子制造工艺等方面的限制,铜柱直径不能进一步做小,一般200μm是小尺寸,继续微型化受到工艺和应用限制;

14.(4)单颗铜柱的长度不能太长,受制于加工方法和铜柱焊接工艺限制,单颗铜柱容易倾倒,焊接工艺中容易位置偏移,影响铜柱应用质量和客户满意度等。

15.现有技术(二)的缺陷:

16.现有技术(二)是在基板表面焊盘上电镀铜柱技术,该工艺实施的主要步骤如下:

17.(1)在已经完成塑封工艺(molding工艺)的塑封料表面进行激光挖槽,利用高能量、高精度、可编程、可自动化的激光束,烧蚀塑封料,加工出圆形深孔或沟槽;

18.(2)在圆形深孔或沟槽内进行清洁等预处理,便于电镀工艺实现;

19.(3)电镀铜工艺,在激光深孔或沟槽内电镀产生需要形状和深度的铜柱。

20.tmv(throughmoldvia)技术是当前先进封装技术之一,常用在扇出型封装(fanout)工艺中,如fopop、2.5d、双面sip等封装结构,该工艺正在被大量封装厂所使用,其主要的缺点是:

21.(1)设备投资成本高昂;激光烧蚀技术工艺复杂、控制难度大;

22.(2)激光挖槽过程是激光一个一个地进行图形的烧蚀,效率低,成本高;

23.(3)激光能力是否高度方向挖到需要位置,难以控制和检测;

24.(4)激光挖槽过程是质量与基板是否变形、塑封料高度有关。基板变形和塑封料的厚度变化控制难度大,影响到激光挖槽深度的质量,进而影响后续铜柱电镀质量;

25.(5)深孔电镀有工艺的限制,目前常用深宽比10:1,量产铜柱的高度最高是100μm左右。

26.tmv工艺加工铜柱,工序多、质量控制难度大、存在气泡问题、电镀铜柱内部不连续等问题、使用该工艺的封装芯片可靠性问题等不利因素。电镀铜柱工艺受到沟槽深度和宽度尺寸的工艺约束,不能做出高铜柱,因此,一定程度上限制了当前芯片封装工艺的发展。因此,亟待设计出一种带有高铜柱的芯片封装结构及其制备方法。其中,高铜柱是指高度超过50μm的铜柱,铜柱末端为了封装工艺、质量的需要设置有电镀金属层。高铜柱的加工方法可以是精密模具铸造成形、精密冲压加工、精密蚀刻加工、精密激光加工中的任意一种或者所述方法的搭配组合。

技术实现要素:

27.本发明针对现有技术方案的技术问题和挑战,提供一种带有高铜柱的芯片封装结构及其制备方法。本发明技术方案解决了单颗铜柱应用在封装工艺中的技术问题,优化了铜柱在封装工艺中批量使用的工艺、质量、可靠性、效率,将推进铜柱结构在芯片封装工艺中的批量应用。

28.本发明所要解决的技术问题采取以下技术方案来实现:

29.一种带有高铜柱的芯片封装结构,它包括一体化铜柱集成平台、高铜柱(高度为50-5000μm);

30.所述一体化铜柱集成平台上设有多颗高铜柱,高铜柱末端设有电镀层。

31.高铜柱末端电镀层包括电镀镍层和焊锡层,电镀镍层处于高铜柱末端和焊锡层之间,电镀镍层的厚度范围在0.1-10μm之间,焊锡层采用纯锡或焊锡合金,其中焊锡合金的成分采用snpb、snag、sncu、snbi、snagcu、snagcuni中的至少一种,焊锡层厚度范围在1-100μm之间。

32.高铜柱的横截面形状采用但不限于长方形、圆形、椭圆形、正多边形中任意一种。

33.作为优选实例,所述一体化铜柱集成平台采用:(一)铜质一体化铜柱集成平台;(二)带芯片高铜柱集成平台;(三)胶固化一体化铜柱集成平台;(四)带载板高铜柱一体化集成平台。其中:

34.(一)铜质一体化铜柱集成平台以及高铜柱采用但不限于精密模具铸造加工、精密冲压加工、精密蚀刻加工、激光精密加工中任意一种或多种组合的加工方式成型。铜柱与铜

质一体化铜柱集成平台源自同一块材料,具有连接强度大的优势,加工简单、有极高的成本竞争力。

35.(二)带芯片高铜柱集成平台包括芯片本体,以及芯片本体上的bump凸块(bump意为凸块,是芯片领域术语,以完成芯片与外界的组装互连),芯片本体与高铜柱之间通过bump凸块相连,高铜柱采用焊接方式与bump凸块连接。芯片与高铜柱之间的应力,通过bump凸块焊锡进行缓解、吸收,降低芯片bump凸块处应力集中。根据芯片bump凸块类型,分为solderbump(锡膏bump)类高铜柱一体化集成平台、copperpillarbump(短铜柱bump)类高铜柱一体化集成平台。带芯片高铜柱集成平台解决了晶圆bumping电镀工艺中电镀bump高度的工艺极限,获得了超长bump结构;同时焊接工艺连接方式改善了高铜柱的应力问题,适用于封装结构空间上架高芯片的应用场景

36.(三)胶固化一体化铜柱集成平台由固化胶固化高铜柱形成集成平台,多颗高铜柱与固化胶连接为一整体。

37.根据封装工艺应用的场景不同、固化胶平台位置相对铜柱高度不同,胶固化高铜柱集成平台的形态有如下几种方式:

38.1)固化胶全包封整个铜柱高度:固化胶填充并包封整个铜柱高度;电镀镍层、焊锡层在固化胶之外,该类封装结构适用于不需要uf底填充或molding塑封的应用场景;

39.2)固化胶部分包封铜柱高度:固化胶包封一部分铜柱高度,露出一部分铜柱裸露;该类封装结构适用于铜柱完成集成后需要做uf底填充或molding塑封的应用场景。在细分为单侧露出铜柱结构、双侧露出铜柱结构。

40.3)根据胶固化高铜柱集成平台中铜柱焊接方式不同,区分为单侧电镀金属层的铜柱结构,双侧电镀金属层的铜柱结构,无电镀金属层的铜柱结构。

41.(四)带载板高铜柱一体化集成平台由封装载板、载板表面焊盘、塑封胶组成,塑封胶将封装载板、高铜柱胶封,高铜柱以打线方式与封装载板的载板表面焊盘连接,高铜柱高度50-5000μm,封装载板采用包含但不限于有机基板、无机基板、陶瓷基板、金属框架以及rdl线路层,封装载板层数大于等于1层。

42.本发明的有益效果是:

43.(1)采用一体化铜柱集成平台、高铜柱结构,不需要复杂、高成本的电镀工艺加工出高铜柱,铜柱的制造方法得到简化,可以降低制造成本;

44.(2)可以作为基础封装结构,开发出非电镀工艺的带有高铜柱结构的系统集成芯片(sip)封装结构,质量稳定,可靠性高;

45.(3)优化了封装工艺中铜柱的使用方法,把封装工序中流水线化铜柱的加工工作分离开来,模块化封装工艺,可以提前把铜柱结构做好,节省了连续封装生产中电镀铜柱的加工时间,提高了封装效率,模块化自动化加工也提升了封装质量水平,提升了芯片封装可靠性;

46.(4)基于带有高铜柱的芯片封装结构,封装工艺中铜柱的应用技术可以实现封装流程的简化,易于标准化、自动化加工;

47.(5)将单颗、孤立的铜柱汇集到一体化铜柱集成平台,集成为一个整体,一体化铜柱集成平台作为设备吸取、贴放受力点,便于后续封装工艺自动化使用铜柱;

48.(6)重新布局铜柱的位置,实现铜柱之间所需要的细间距,形成阵列,再利用一体

化铜柱集成平台实现铜柱固定;

49.(7)铜柱末端根据需要进行镍金属电镀、焊接合金材料电镀,达到芯片封装工艺焊接要求;

50.(8)基于带有高铜柱的芯片封装结构,可以推动芯片封装技术的发展,提供高铜柱集成平台,为2.5d、3d、sip、fo封装等先进封装工艺提供基础性封装结构;

51.(9)本铜柱结构适用于包括但不限于:半导体封装工艺,晶圆工艺,以及普通电子制造工艺,如通信电子、医疗电子、汽车电子、航空航天电子等,应用广泛。

附图说明

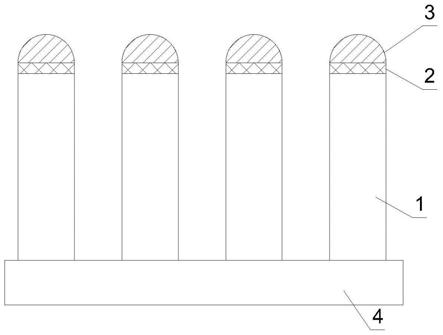

52.图1为实施例1采用铜质一体化高铜柱集成平台的结构示意图;

53.图2为实施例1铜板材料结构示意图;

54.图3为实施例1铜板进行电镀的结构示意图;

55.图4为实施例1进行激光切割后的结构示意图;

56.图5为实施例1进行reflow焊接、清洗和单颗切割的结构示意图;

57.图6为实施例2打线封装载板的结构示意图;

58.图7为实施例2打线焊接的结构示意图;

59.图8为实施例2铜柱塑封的结构示意图;

60.图9为实施例2平磨、电镀、预上助焊剂的结构示意图;

61.图10为实施例2上载具和带短铜柱芯片的结构示意图;

62.图11为实施例2带短铜柱芯片焊接的结构示意图;

63.图12为实施例2带焊锡凸点芯片去胶封的结构示意图;

64.图13为实施例2上载具和带焊锡凸点芯片的结构示意图;

65.图14为实施例2带焊锡凸点芯片焊接的结构示意图;

66.图15为实施例2带焊锡凸点芯片去胶封的结构示意图;

67.图16为实施例3铜板预切割的结构示意图;

68.图17为实施例3铜板底部胶封的结构示意图;

69.图18为实施例3激光切割铜柱的结构示意图;

70.图19为实施例3单颗分割的结构示意图;

71.图20为实施例3二次胶封的结构示意图;

72.图21为实施例3平磨、电镀的结构示意图;

73.图22为实施例3进行reflow焊接与清洗的结构示意图;

74.图23为实施例3去除塑封料的结构示意图;

75.图24为实施例4打线封装载板的结构示意图;

76.图25为实施例4打线焊接的结构示意图;

77.图26为实施例4铜柱塑封的结构示意图;

78.图27为实施例4两端平磨、电镀的结构示意图;

79.图28为实施例4进行reflow焊接与清洗的结构示意图;

80.图29为实施例4保留上半部分塑胶料的结构示意图;

81.图30为实施例4保留上半部分塑胶料后单颗切割的结构示意图;

82.图31为实施例4保留中部塑胶料的结构示意图;

83.图32为实施例4保留中部塑胶料后单颗切割的结构示意图;

84.图33为实施例5打线封装载板的结构示意图;

85.图34为实施例5打线焊接的结构示意图;

86.图35为实施例5铜柱塑封的结构示意图;

87.图36为实施例5上端平磨、电镀的结构示意图;

88.图37为实施例5进行reflow焊接与清洗的结构示意图;

89.图38为实施例5保留下半部分塑胶料的结构示意图;

90.图39为实施例5保留下半部分塑胶料后单颗切割的结构示意图。

91.图中:高铜柱1,铜线101,焊点102,电镀镍层2,焊锡层3,铜质一体化高铜柱集成平台4,铜板401,切割槽402,打线封装载板5,焊盘501,塑封料6,助焊剂7,载具8,芯片9,短铜柱901,焊锡凸点902,容器10,胶水11。

具体实施方式

92.为了对本发明的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施例,进一步阐述本发明。

93.实施例1:一体化铜柱集成平台采用铜质一体化高铜柱集成平台4

94.如图1-图5所示,带有高铜柱的芯片封装结构示意图及流程。非电镀高铜柱1,电镀镍层2,高铜柱1末端由焊锡层3形成bump凸块,高铜柱1集成于铜质一体化高铜柱集成平台4上,形成一个完整的封装结构整体。

95.带有高铜柱的芯片封装结构可以采用但不限于激光精密加工、精密模具铸造加工、精密冲压加工、精密蚀刻加工中的任意一种加工方法或所述加工方法的组合方法。下面以激光切割加工为例进行说明。

96.如图2-图5所示,一种带有高铜柱的芯片封装结构的制备工艺,包括但不限于如下步骤:

97.s1:材料准备。准备一预成型铜板401材料,铜板401的厚度在50-5000μm,(或以上);

98.s2:电镀层。在上述预成型铜板401的表面进行预处理;然后,进行金属层的电镀:电镀镍层2和焊锡层3。焊锡层3作为高铜柱1与封装载板表面焊盘501的焊接合金,起到焊点102形成的作用,控制高铜柱1与封装载板的集成强度和应力缓冲;电镀镍层2在高铜柱1的焊接过程起到金属原子扩散减缓层,提高焊点102质量与可靠性的作用;

99.s3:激光切割成形。利用激光束烧蚀上述预成型铜板401材料,雕刻出高铜柱1和铜质一体化铜柱集成平台。利用精确控制高度的激光设备,预留一定厚度的铜材厚度不切割,使得高铜柱1与铜质一体化铜柱集成平台连接为一个整体;

100.s4:施加助焊剂7、reflow焊接与清洗。在高铜柱1末端焊锡层3的表面施加助焊剂7,助焊剂7的施加可以但不限于雾化喷涂助焊剂7、蘸取助焊剂7、蘸取锡膏等方式。然后,采用reflow回流焊的方式实现焊锡bump凸块的形成,以便铜质一体化铜柱集成平台在后续封装工艺中兼容封装需求。最后,完成高铜柱1焊锡bump凸块表面助焊剂7残留物、污染物等的清洗;

101.s5:切割。集成高铜柱的铜质一体化铜柱集成平台的切割可以但不限于激光切割、机械刀片切割、机械冲压等。优选地选择激光切割,切割后获得单颗集成高铜柱1的铜质一体化铜柱集成平台;

102.s6:包装存放。根据需要选择编带(tapereel)方式,也可以是盘装(tray)方式,便于高铜柱1的bump保护、存储、运输、以及封装工艺自动化使用。

103.实施例2:一体化铜柱集成平台采用带芯片高铜柱集成平台

104.如图6-图15所示,带有高铜柱的芯片封装结构示意图以及该结构的制备工艺流程。

105.带有高铜柱的芯片封装结构可以采用但不限于激光精密加工、精密模具铸造加工、精密冲压加工、精密蚀刻加工中的任意一种加工方法或所述加工方法的组合方法。下面以激光切割加工为例进行说明。

106.一种带有高铜柱的芯片封装结构的制备工艺,包括但不限于如下步骤:

107.s1:准备打线封装载板5。准备一打线封装载板5,该载板表面设有打线工艺(wirebond)焊盘501。打线封装载板5,包含但不限于有机基板、无机基板、陶瓷基板、金属框架以及rdl线路层等。

108.s2:打线焊接。在打线封装载板5表面焊盘501上进行打线作业,优选铜线101(还可采用其他导线),铜线101与打线载板之间形成焊点102,高铜柱1的高度大于50到5000μm之间,打线采用垂直打线工艺。

109.s3:铜柱塑封。通过塑封工艺将打线封装载板5、封装载板表面焊盘501、铜线101与载板上的焊点102、高铜柱1进行塑封固定并形成塑封料6。塑封料6的上边界高于高铜柱1高度的最大值。

110.s4:平磨、电镀、预上助焊剂7。将塑封料6塑封固定的高铜柱1和打线封装载板5结构进行双面研磨,磨掉打线封装载板5、焊盘501、焊点102。塑封料6的上、下表面都露出高铜柱1两端的横截面。然后进行双面电镀,高铜柱1两端分别形成电镀镍层2和焊锡层3。为了焊锡层3的回流焊接工艺要求,预先在电镀镍层2和焊锡层3表面施加助焊剂7。

111.s5:上载具8、上芯片9。将预涂助焊剂7的塑封高铜柱1一面朝向,放入载具8中,载具8内部挖槽处理,挖槽深度满足安全避让电镀镍层2和焊锡层3,不发生空间上的干涉。

112.在塑封料6的另一表面上,施加助焊剂7。助焊剂7的施加方式可以但不限于如下方式:印刷方式、点涂方式、喷涂方式、划线方式、印刷锡膏方式等。

113.然后,采用高速、高精度、自动贴片设备对芯片9吸取、贴放到铜柱焊盘501对应位置,芯片9可以是带短铜柱901bump凸块结构的芯片9或带solder bump焊锡凸点902的芯片9。

114.助焊剂7在芯片9reflow焊接前起到临时固定芯片9的作用,让芯片9位置不发生偏移;焊接过程中起到帮助焊接的作用,让芯片9形成良好的焊接效果,与高铜柱1集成为一体。

115.s6:reflow焊接与清洗。将预涂了助焊剂7带短铜柱901bump凸块结构的芯片9或带solderbump焊锡凸点902的芯片9组成的系统进行reflow回流焊接,实现芯片9与高铜柱1的焊接方式集成;焊锡层3形成圆弧状bump凸块,利于带芯片9的高铜柱一体化封装平台在后续封装工艺中使用。最后,对高铜柱1焊锡bump表面助焊剂7残留物、污染物等进行清洗;

116.s7:去除塑封料6

117.利用激光光源的选择性切割特点,选择性烧蚀有机塑封料6,保留高铜柱1、电镀镍层2、焊锡层3。利用高度可以精确控制的激光设备,将高铜柱1周围的塑封料6进行选择性烧蚀,而不影响到芯片9表面。

118.s8:切割

119.集成带芯片9高铜柱一体化封装平台的切割方式可以但不限于激光切割、机械刀片切割等。优选选择激光切割方式,切割后获得单颗带芯片9的高铜柱1一体化封装平台;

120.s9:包装存放。根据需要选择编带(tapereel)方式,也可以是盘装(tray)方式,便于高铜柱1的bump保护、存储、运输、以及封装工艺自动化使用。

121.实施例3一体化铜柱集成平台采用胶固化高铜柱一体化集成平台

122.胶固化高铜柱一体化集成封装平台4由固化胶制作而成,多颗高铜柱1通过固化胶粘接固化。

123.如图16-图23所示,带有高铜柱的芯片封装结构示意图以及该结构的制备工艺流程图。

124.带有高铜柱的芯片封装结构可以采用但不限于激光精密加工、精密模具铸造加工、精密冲压加工、精密蚀刻加工中的任意一种加工方法或所述加工方法的组合方法。下面以激光切割加工为例进行说明。

125.一种带有高铜柱的芯片封装结构的制备工艺,包括但不限于如下步骤:

126.s1:材料准备。准备一预成型铜板401材料,铜板401的厚度在50-5000μm,(或以上);

127.s2:激光预切割。利用高度可以精确控制的激光设备,在铜板401的一侧进行预切割,形成切割槽402,其深度在10-200μm。

128.s3:预切割铜柱胶封。将激光切割形成的切割槽402方向朝下固定在一容器10中,容器10内填充胶水11进行铜板401材料的固定。

129.s4:激光切割。利用高度可以精确控制的激光设备,可编程、高精度切割,从铜板401材料的表面开始,沿着激光预切割槽402的位置切穿铜板401材料,获得多根独立高铜柱1。

130.s5:切割。该步骤为可选步骤。将步骤s4完成的胶封固定高铜柱1的结构,进行切割。切割可以但不限于激光切割、机械刀片切割、机械冲压等。作为优选实例,选择激光切割,切割后获得单颗胶水11高铜柱1一体化封装平台;

131.s6:第二次胶封。在步骤s4完成的胶封固定的高铜柱1结构的胶水11表面上,进行第二次胶水11的填充、固化,完成高铜柱1的覆盖式填充与固定。

132.s7:平磨、电镀金属层。将胶水11封装固定高铜柱1的结构进行表面研磨,露出高铜柱1的横截面,以及胶水11的表面。然后,在高铜柱1的横截面上进行电镀,形成电镀镍层2和焊锡层3。

133.s8:施加助焊剂7、reflow焊接与清洗。在高铜柱1末端焊锡层3的表面施加助焊剂7,助焊剂7的施加可以但不限于雾化喷涂助焊剂7、蘸取助焊剂7、蘸取锡膏等方式。然后,采用reflow回流焊的方式实现焊锡bump凸块222的形成,以便高铜柱集成平台在后续封装工艺中兼容封装需求。最后,完成高铜柱1焊锡bump222表面助焊剂7残留物、污染物等的清洗;

134.s9:去除塑封料6

135.利用升降高度可以精确控制的激光切割设备,烧蚀固封胶,保留塑封胶,露出高铜柱1。

136.s10:切割。切割方法可以但不限于激光切割、机械刀片切割、机械冲压等。作为优选实例,选择激光切割,切割后获得单颗胶水11高铜柱1一体化集成封装平台;

137.s11:包装存放。根据需要选择编带(tapereel)方式,也可以是盘装(tray)方式,便于高铜柱1的bump保护、存储、运输、以及封装工艺自动化使用。

138.实施例4一体化铜柱集成平台采用胶固化高铜柱一体化集成平台

139.如图24-图32所示,带有高铜柱的芯片封装结构示意图以及该结构的制备工艺流程。

140.带有高铜柱的芯片封装结构可以采用但不限于激光精密加工、精密模具铸造加工、精密冲压加工、精密蚀刻加工中的任意一种加工方法或所述加工方法的组合方法。作为优选实例,以激光切割加工为例进行说明。

141.一种带有高铜柱的芯片封装结构的制备工艺,包括但不限于如下步骤:

142.s1:准备打线封装载板5。准备一打线封装载板5,该载板表面设有打线工艺(wirebond)焊盘501。所述打线封装载板5,包含但不限于有机基板、无机基板、陶瓷基板、金属框架以及rdl线路层等。

143.s2:打线焊接。在打线封装载板5表面焊盘501上进行打线作业,作为优选实例,选择铜线101,铜线101与打线载板之间形成焊点102,高铜柱1的高度大于50到5000μm之间,打线采用垂直打线工艺。

144.s3:高铜柱1塑封。通过塑封工艺将打线封装载板5、封装载板表面焊盘501、铜线101与载板焊接点、铜柱进行塑封固定。塑封料6的上边界高于铜柱高度的最大值。

145.s4:平磨、电镀。将塑封料6塑封固定的高铜柱1和封装载板结构进行双面研磨,磨掉封装载板、焊盘501、打线焊点102。塑封料6的上、下表面都露出铜柱的横截面。然后进行双面电镀,两端分别形成电镀镍层2和焊锡层3。

146.s5:reflow焊接与清洗。将步骤s4形成的结构进行reflow回流焊接,实现高铜柱1双端焊锡bump凸起的制备;焊锡层3形成圆弧状bump凸起,利于带芯片的高铜柱一体化封装平台在后续封装工艺中使用。最后,对高铜柱1焊锡bump表面助焊剂7残留物、污染物等进行清洗;

147.s6:塑封料6部分激光切割

148.利用升降高度可以精确控制的激光切割设备,烧蚀固封胶的一部分,保留一部分固化胶,用以固定高铜柱1。

149.露出高铜柱1以及焊锡bump凸起,有利于胶固化高铜柱一体化封装结构在后续封装工艺中兼容uf地填充工艺、molding模塑封工艺,提高了胶固化高铜柱一体化封装结构的使用性能和灵活性,充分满足封装工艺需求。

150.胶固化集成平台,可以作为自动化使用胶固化高铜柱一体化封装结构的吸取、贴放应力平面。

151.s7:切割

152.集成带芯片高铜柱一体化封装平台的切割方式可以但不限于激光切割、机械刀片

切割等。作为优选实例,选择激光切割方式,切割后获得单颗带芯片9的高铜柱一体化封装平台;

153.s8:包装存放。根据需要选择编带(tapereel)方式,也可以是盘装(tray)方式,便于高铜柱1的bump保护、存储、运输、以及封装工艺自动化使用。

154.实施例5一体化铜柱集成平台采用带载板高铜柱一体化集成平台

155.如图33-图39所示,带有高铜柱的芯片封装结构示意图以及该结构的制备工艺流程。

156.图中:高铜柱1以打线(wirebond)工艺方式与芯片9封装载板表面焊盘501打线焊接固定,形成焊点102。打线工艺采用成熟的垂直打线方式,垂直线高度50-5000μm,或以上。高铜柱1的末端设有电镀镍层2、焊锡层3,焊锡层3用来支撑高铜柱1在芯片9封装工艺中的焊接集成,形成永久性焊点102连接,实现高铜柱1与芯片9封装基板之间电气性能的连接和机械性能增强,保证高铜柱1焊接质量和芯片9封装结构的可靠性。塑封料6用以进一步加强高铜柱1与封装载板的机械可靠性,保护焊点102和封装载板。高铜柱1裸露部分兼容后续封装工艺应用的uf底填充工艺、molding塑封工艺,增强了高铜柱1集成封装结构的使用性。

157.带有高铜柱的芯片封装结构可以采用但不限于激光精密加工、精密模具铸造加工、精密冲压加工、精密蚀刻加工中的任意一种加工方法或所述加工方法的组合方法。作为优选实例,以激光切割加工为例进行说明。

158.一种带有高铜柱的芯片封装结构的制备工艺,包括但不限于如下步骤:

159.s1:准备打线封装载板5。准备一打线封装载板5,该载板表面设有打线工艺(wirebond)焊盘501。所述打线封装载板5,包含但不限于有机基板、无机基板、陶瓷基板、金属框架以及rdl线路层等。

160.s2:打线焊接。在打线封装载板5表面焊盘501上进行打线作业,作为优选实例,选择铜线101,铜线101与打线载板之间形成焊点102,高铜柱1的高度在50到5000μm之间,或者大于5000μm,打线工艺采用垂直打线。

161.s3:高铜柱1塑封。通过塑封工艺将打线封装载板5、封装载板表面焊盘501、铜线101与载板焊接点、铜柱进行塑封固定。塑封料6的上边界高于铜柱高度的最大值。

162.s4:平磨、电镀。将塑封料6塑封固定的高铜柱1和封装载板结构进行双面研磨,磨掉封装载板、焊盘501、打线焊点102。塑封料6的上、下表面都露出铜柱的横截面。然后进行电镀,形成电镀镍层2和焊锡层3。

163.s5:reflow焊接与清洗。将步骤s4形成的结构进行reflow回流焊接,实现高铜柱1双端焊锡bump凸起的制备;焊锡层3形成圆弧状bump凸起,利于带封装载板的高铜柱一体化封装平台在后续封装工艺中焊锡工艺实现。最后,对高铜柱1焊锡bump表面助焊剂7残留物、污染物等进行清洗;

164.s6:塑封料6部分激光切割

165.利用升降高度可以精确控制的激光切割设备,烧蚀塑封胶的一部分厚度,保留一部分厚度,以安全包封焊点102为依据。剩余厚度的塑封料6用以进一步加强高铜柱1与封装载板的机械可靠性,保护焊点102和封装载板。高铜柱1裸露部分兼容后续封装工艺应用的uf底填充工艺、molding塑封工艺,增强了高铜柱1集成封装结构的使用性。

166.s7:切割

167.带封装载板的高铜柱一体化封装平台的切割方式可以但不限于激光切割、机械刀片切割等。作为优选实例,选择激光切割方式,切割后获得单颗带芯片9的高铜柱一体化封装平台;

168.s8:包装存放。根据需要选择编带(tapereel)方式,也可以是盘装(tray)方式,便于高铜柱1的bump保护、存储、运输、以及封装工艺自动化使用。

169.以上显示和描述了本发明的基本原理、主要特征和优点。本领域的技术人员应该了解,本发明不受上述实施例的限制,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入本发明要求保护的范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1