电子封装体的制作方法

1.本实用新型涉及一种电子零件,且特别是涉及一种电子封装体。

背景技术:

2.目前用于多芯片的电子封装技术有很多种类型,其中一种类型是在多芯片上制作重布线路结构,并可在制作重布线路结构的过程中,将一芯片跨接在多个相邻的芯片上这些相邻的芯片之间的信号传递。再一种类型是将多个芯片堆叠在线路载板或中介元件(interposer)上,并通过芯片内的硅通孔 (through silicon via,tsv)来提供垂直的导通路径。而在同一封装体中配置越多的芯片,最常造成的问题是散热问题,而这个问题是目前需要被解决的。

技术实现要素:

3.本实用新型的目的在于提供一种电子封装体,用以提供良好的散热效能。

4.为达上述目的,本实用新型提供的电子封装体包括至少一次封装体。次封装体包括多个芯片、一金属层、至少一桥元件及一中介导通结构。这些芯片的每一个具有一有源面、一背面及连接有源面及背面的多个侧面。金属层直接覆盖这些芯片的每一个的背面及这些侧面,并暴露出这些有源面。桥元件与这些芯片的至少两个局部重叠,并电连接对应的这些有源面。中介导通结构配置在金属层及这些芯片上且包覆桥元件,并电连接这些有源面。

5.该金属层的厚度大于该芯片的厚度。

6.该桥元件是由多个介电层和多个导电层所构成,无半导体晶体管配置。

7.该芯片的散热途径至少包括每一个该芯片的该背面及该些侧面。

8.对一个参考投影面来说,该芯片的投影会落在该重布线路结构的投影的内部。

9.该次封装体还包括重布线路结构,配置在该中介导通结构上。

10.该次封装体还包括多个导电凸块,配置在该重布线路结构上。

11.该次封装体还包括多个导电凸块,配置在该中介导通结构上。

12.该中介导通结构具有中介介电层及多个中介导通孔道,该些中介导通孔道穿过该中介介电层,并分别连接这些芯片的芯片接垫。

13.该次封装体还包括多个导电凸块,配置在该中介导通结构上,其中各该导电凸块连接对应的该中介导通孔道的末端。

14.该至少一桥元件具有多个桥导通孔道,而电连接该桥元件的该些芯片经由该些桥导通孔道与该中介导通结构相电连接。

15.该电子封装体还包括线路载板,该次封装体安装在该线路载板上。

16.该次封装体的数量为多个,且该些次封装体安装在该线路载板的同一面。

17.该次封装体的数量为多个,且该些次封装体分别安装在该线路载板的相对两面。

18.该电子封装体还包括多个导电球,连接至该线路载板。

19.该金属层的导热系数大于300w/mk。

20.该些芯片之一包括中央处理器芯片、逻辑芯片、绘图处理芯片、输出入芯片、存储器芯片、基频芯片、射频芯片或特殊功能集成电路芯片。

21.本实用新型的优点在于,经由金属层直接覆盖芯片的背面及多个侧面,使得金属层与芯片的背面及多个侧面共形,而形成直接接触(directly contact) 的界面(interface),这有助于减少热阻并增加芯片至外界的热传导路径,以提供良好的散热效能。所封装的芯片类型例如是中央处理器芯片、逻辑芯片、绘图处理芯片、输出入芯片、存储器芯片、基频(base band)芯片、射频(rf) 芯片、特殊功能集成电路芯片等,故可用于小芯片(chiplet)封装技术,其类似系统封装(system in a packaging,sip)。通过桥元件(bridge)来连接相邻的芯片可提高电子封装体的线路密度。

附图说明

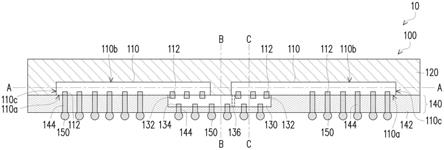

22.图1a是本实用新型的一实施例的一种电子封装体的剖面示意图;

23.图1b是相似图1a的另一实施例的电子封装体沿着线a-a的横向剖面示意图;

24.图1c是图1a的电子封装体沿着线b-b的剖面示意图;

25.图1d是图1a的电子封装体沿着线c-c的剖面示意图;

26.图2是本实用新型的另一实施例的一种电子封装体的示意图;

27.图3是本实用新型的另一实施例的一种电子封装体的示意图;

28.图4是本实用新型的另一实施例的一种电子封装体的示意图;

29.图5是本实用新型的另一实施例的一种电子封装体的示意图;

30.图6是本实用新型的另一实施例的一种电子封装体的示意图;

31.图7a-1至图7n绘示本实用新型的一实施例的一种电子封装体的制作工艺的示意图;

32.图8a至图8b绘示本实用新型的一实施例的一种电子封装体的制作工艺后段的示意图。

33.符号说明

34.10:电子封装体

35.12:线路载板

36.14:导电球

37.100:次封装体

38.110:芯片

39.110a:有源(主动)面

40.110b:背面

41.110c:侧面

42.112:芯片接垫

43.120:金属层

44.120a:金属材料层

45.130:桥元件

46.132:第一桥接垫

47.134:第二桥接垫

48.136:桥导通孔道

49.140:中介导通结构

50.142:中介介电层

51.142a:贯孔

52.144:中介导通孔道

53.150:导电凸块

54.160:重布线路结构

55.162:重布图案化导电层

56.164:重布介电层

57.166:重布导电孔道

58.168:凸块底金属层

59.202:遮蔽层

60.204:临时接合层

61.206:临时载具

62.208:电镀种子层

具体实施方式

63.请参考图1a至图1d,在本实施例中,电子封装体10包括至少一次封装体100。次封装体100包括多个芯片110、一金属层120、一桥元件130 (bridge)及一中介导通结构140。每个芯片110具有一有源面110a、一背面110b及连接有源面110a及背面110b的多个侧面110c。金属层120直接覆盖每个芯片110的背面110b及这些侧面110c,并暴露出这些有源面110a。换言之,金属层120与每个芯片110的背面110b及这些侧面110c共形 (conformal),即具有可直接接触(directly contact)的界面(interface)。目前所绘示的图1a是示意图,共形的金属层120是经过平坦化即薄化步骤。值得一提的是,本实施例的金属层120可以作为散热路径,且在本实施例中,金属层120与芯片110之间并没有散热材料(tim)的配置。除此之外,相较于使用已知的膏状散热材料,本实施例使用金属层不会有在涂覆膏状散热材料时可能会产生气泡,进而影响散热效率的问题。另外,作为散热路径的金属层120,其厚度可以大于芯片110的厚度,以提供更好的散热效率。详细的说明是,共形的金属层120下方因为有足够的结构支撑,所以金属层厚度可以较厚。然而,已知作为散热的金属散热盖或是散热器,仅有局部地接触下方结构,所以可获得的支撑较小,金属散热盖或是散热器的选择受限,故厚度较薄。

64.桥元件130与这些芯片110局部重叠,并电连接对应的这些有源面110a。在一实施例中,桥元件130是由多层的介电层和多导电层构成,而无mos 晶体管配置。亦即,桥元件130只作为信号传递之用,没有mos晶体管的开关效果。中介导通结构140配置在金属层120及这些芯片110上且包覆桥元件130,并电连接这些有源面110a。

65.在本实施例中,各芯片110具有芯片接垫112,桥元件130具有多个第一桥接垫132。这些第一桥接垫132可分别直接接合这些芯片接垫112。在另一未绘示的实施例中,这些第一桥接垫132也可分别经由焊料(solder) 来接合这些芯片接垫112。

66.在本实施例中,这些芯片110之一可以是中央处理器芯片、逻辑芯片、绘图处理芯片、输出入芯片、存储器芯片、基频(base band)芯片、射频(rf) 芯片或特定功能的集成电路芯片110。换言之,这些芯片110可包括前述不同功能类型的芯片110的组合,使得电子封装体10可用于小芯片(chiplet) 封装技术,其类似系统封装(system in a packaging,sip)。由于这些芯片110 可能有不同功用,这些芯片110的尺寸可以是不同,如图1b所示。在一些实施例中,例如是:中央处理器芯片和逻辑芯片的组合、中央处理器芯片和输出入芯片的组合、绘图处理芯片和存储器芯片的组合、射频芯片和基频芯片的组合。

67.在本实施例中,金属层120的材质例如是铜、银、金、铝,以提供良好的导热能力。从导热能力来看,所选择的金属层120的导热系数可大于 300w/mk(瓦特/(米

×

度))。在一些实施例中,铜的导热系数大约是398w/mk、银的导热系数大约是429w/mk、金的导热系数大约是315w/mk。

68.在本实施例中,桥元件130的介电层材质可与这些芯片110的基底材质相同或相近。桥元件130可具有多个桥导通孔道136(图1a仅绘示这些桥导通孔道136的其中之一作为示意),而电连接桥元件130的这些芯片110 经由这些桥导通孔道136与中介导通结构140相电连接。在一实施例中,桥元件130只作为信号传输,而无mos晶体管配置。

69.在本实施例中,中介导通结构140具有一中介介电层142及多个中介导通孔道144。这些中介导通孔道144穿过中介介电层142,并分别连接这些芯片110的这些芯片接垫112及桥元件130的多个第二桥接垫134。

70.在本实施例中,次封装体100还可包括多个导电凸块150。每个导电凸块150配置在对应的中介导通孔道144的末端。

71.值得一提的是,因为本实施例的芯片110有至少五个散热路径,意即芯片110的热可经由芯片110的背面110b(上表面)及四个侧面110c直接传递至金属层120,相较已知使用散热材料(tim)来散热,仅有上表面的单一散热,本实施例可以大幅提升散热效果。此外,芯片110有源面110a也可以是另一个散热途径。请参考图2,相较于图1a的实施例,在本实施例中,电子封装体10还包括一线路载板12,而次封装体100安装在线路载板12 上。此外,电子封装体10还可包括多个导电球14,例如锡球,其连接至线路载板12,用以连接下一级的电子零件。

72.请参考图3,相较于图2的实施例,在本实施例中,次封装体100的数量为多个,且这些次封装体100安装在线路载板12的同一面。

73.请参考图4,相较于图2的实施例,在本实施例中,次封装体100的数量为多个,且这些次封装体100分别安装在线路载板12的相对两面。

74.请参考图5,相较于图2的实施例,在本实施例中,次封装体100还包括重布线路结构160,其配置在中介导通结构140,以将这些芯片110的芯片接垫112及桥元件130的多个第二桥接垫134重新布局。在本实施例中,桥元件130可以具有多个桥导通孔道136,而这些芯片110经由这些桥导通孔道136与重布线路结构160相电连接。相较图1至图4,图5具有重布线路结构160。这些芯片110上的芯片接垫112其信号可通过重布线路结构160 往芯片110两侧布局,以增加信号布局的弹性。对一个参考投影面来说,芯片110的投影会落在重布线路结构160的投影的内部。

75.请参考图6,相较于图5的实施例,在本实施例中,电子封装体10还包括一线路载板

12,而次封装体100安装在线路载板12上。此外,电子封装体10还可包括多个导电球14,例如锡球,其连接至线路载板12,用以连接下一级的电子零件(例如pcb)。

76.下文将配合图7a-1至图7n来描述本实用新型的一实施例的一种电子封装体10的制作工艺,其可制作出如同图1a的实施例的电子封装体10。

77.请参考图7a-1、图7a-2,提供多个芯片110。

78.请参考图7b-1、图7b-2,在各芯片110的有源面110a上形成一遮蔽层 202。

79.请参考图7c,将这些芯片110通过一临时接合层204或离型层(未绘示) 固定至临时载具206。

80.请参考图7d,全面性形成一电镀种子层208在这些芯片110、这些遮蔽层202及临时接合层204上。在一实施例中,可通过溅镀方式来形成共形(conformal)的电镀种子层208。

81.请参考图7e,在电镀种子层208上电镀一金属材料层120a,以覆盖电镀种子层208下的各芯片110的背面110b及这些侧面110c、各遮蔽层202 的周缘及临时接合层204,使得金属材料层120a与各芯片110的背面110b 及这些侧面110c共形(conformal)。

82.请参考图7f,在形成金属材料层120a之后,可以平坦化金属材料层 120a,并同时薄化,以形成一金属层120。平坦化的方式例如是一般研磨或化学机械研磨(chemical-mechanical polishing,简称cmp)。在一实施例中,用于形成金属层120的材质的导热系数可大于300w/mk(瓦特/(米

×

度)),例如:铜、银、金、铝。在一些实施例中,铜的导热系数大约是398w/mk、银的导热系数大约是429w/mk、金的导热系数大约是315w/mk。此外,电镀种子层208将构成金属层120的一部分,所以在其他实施例中,电镀种子层208会省略绘示。在本实施例中,金属层120可以作为散热路径,且金属层120与芯片110之间并没有散热材料(tim)的配置。除此之外,相较于使用已知的膏状散热材料,本实施例使用金属层不会有在涂覆膏状散热材料时可能会产生气泡,进而影响散热效率的问题。另外,作为散热路径的金属层 120,通过本实施的制作工艺,其形成的厚度可以大于芯片110的厚度,以提供更好的散热效率。详细的说明是,共形的金属层120下方因为有足够的结构支撑,所以可以形成较大的厚度。然而,已知作为散热的金属散热盖或是散热器,仅有局部地接触下方结构,所以可获得的支撑较小,金属散热盖或是散热器的选择受限,故厚度较薄。

83.请参考图7g,移除临时载具206及临时接合层204。

84.请参考图7h,移除部分金属层120及电镀种子层208,以暴露出各遮蔽层202的周缘,并使金属层120的表面与各芯片110的有源面110a相互齐平。移除部分金属层120的方式例如是蚀刻。在一实施例中,金属层120的表面与各芯片110的有源面110a例如是共平面。

85.请参考图7i,移除各遮蔽层202,以暴露出各芯片110的有源面110a。

86.请参考图7j,将一桥元件130安装在相邻的多个芯片110上,使得桥元件130与这些芯片110分别局部重叠,且这些第一桥接垫132可分别直接接合这些芯片接垫112。在一实施例中,桥元件130是由多层的介电层和多导电层构成,无mos晶体管配置。亦即,桥元件130只作为信号传递之用,而无mos晶体管的开关效果。

87.请参考图7k,在这些芯片110、金属层120及桥元件130上全面性地形成一中介介电层142。

88.请参考图7l,在中介介电层142上形成多个贯孔142a,以暴露出各个芯片110的多个芯片接垫112及桥元件130的多个第二桥接垫134。中介介电层142例如是感光介电层,并

通过曝光及显影的方式在中介介电层142上形成这些贯孔142a。

89.请参考图7m,在每个贯孔142a内填入导电材料,以形成一中介导电孔道144,而这些中介导电孔道144分别连接这些芯片110及桥元件130。中介介电层142及这些中介导电孔道144形成如同图1a的实施例的中介导电结构140。

90.请参考图7n,在每个中介导电孔道144的末端形成一导电凸块150。至此,完成了如同图1a的实施例的电子封装体10。

91.在另一实施例中,也可从图7l开始续行图8a及图8b的步骤,其可制作出如同图5的实施例的电子封装体10。

92.具体而言,在图7l的步骤之后,请参考图8a,在中介导电结构140上例如以增层法(build-up process)形成一重布线路结构160。接着,请参考图8b,在重布线路结构160上形成多个导电凸块150。至此,完成了如同图 5的实施例的电子封装体10。

93.在本实施例中,重布线路结构160包括多个重布图案化导电层162、多个重布介电层164及多个重布导电孔道166。这些重布图案化导电层162与这些重布介电层164交替叠合。这些重布导电孔道166分别连接这些重布图案化导电层162。此外,在最远离这些芯片110的重布图案化导电层162的多个部分上更形成多个凸块底金属层168。另外,在每个凸块底金属层168 上形成导电凸块150。

94.综上所述,在本实用新型的上述实施例中,经由金属层直接覆盖芯片的背面及多个侧面,使得金属层与芯片的背面及多个侧面共形,而形成直接接触(directly contact)的界面(interface),这有助于减少热阻并增加芯片至外界的热传导路径,以提供良好的散热效能。在本实施例中,芯片至少有背面及侧面等五个散热路径。值得一提的是,因为本实施例的芯片有至少五个散热路径,相较已知使用散热材料(tim)来散热,仅有上表面的单一散热,本实施例可以大幅提升散热效果。

95.另外,所封装的芯片类型例如是中央处理器芯片、逻辑芯片、绘图处理芯片、输出入芯片、存储器芯片、基频(base band)芯片、射频(rf)芯片、特殊功能集成电路芯片等,故可用于小芯片(chiplet)封装技术,其类似系统封装(system in a packaging,sip)。在一些实施例中,例如是:中央处理器芯片和逻辑芯片的组合、中央处理器芯片和输出入芯片的组合、绘图处理芯片和存储器芯片的组合、射频芯片和基频芯片的组合。通过桥元件(bridge) 来连接相邻的芯片可提高电子封装体的线路密度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1