1.本发明涉及沟槽栅极半导体器件及其制造方法。

背景技术:2.用于诸如沟槽金属氧化物半导体场效应晶体管(mosfet)等半导体器件的沟槽技术广泛用于各种类型的电子器件中。在已知的沟槽mosfet中,mosfet的栅极电极埋入蚀刻在半导体区中的沟槽中以形成竖直结构,这提高了器件的沟道密度。

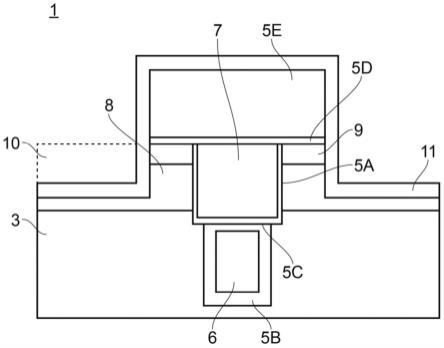

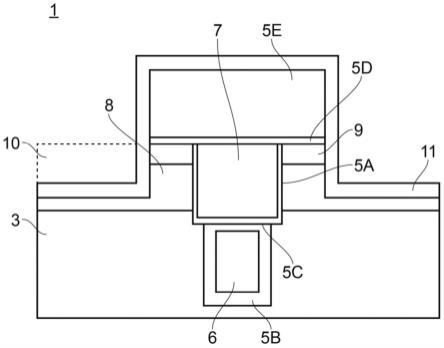

3.图1示出了一种已知的沟槽mosfet结构20的一部分的截面图。已知器件包括设置在布置于硅半导体区内部的沟槽22中的多晶硅栅极区21。如图1所示,半导体区包括第一电荷类型的基板以及布置在基板上并且同样是第一电荷类型的外延层23。在外延层23内,通过离子注入来形成第二电荷类型的体区25和第一电荷类型的源极区24。以下,外延层23的非注入区将称为漂移区23。此外,在基板的底部上设置有沟槽mosfet的漏极端子。

4.沟槽mosfet结构20包括第一氧化物层26a,第一氧化物层26a形成沟槽mosfet的栅极氧化物并且将多晶硅栅极区21与体区25分离。多晶硅栅极区21与栅极端子(未示出)电连接。通过对多晶硅栅极区21上的电荷或电压进行控制,可以在源极区24和漂移区23之间的体区25中形成沟道,从而使电流能够从沟槽mosfet的漏极端子流至与源极区24电连接的mosfet的源极端子。

5.降低表面电场(resurf)结构可以用于增强沟槽mosfet的击穿电压的目的。参照图1,resurf结构是由布置在沟槽22的侧壁和底部的一部分上的第二氧化物层26b与沟槽22内部的掩埋多晶硅源极区27组合形成,并且resurf结构通过第二氧化物层26b与沟槽22的侧壁和底部分离。掩埋多晶硅源极区27布置在多晶硅栅极区21的下方并且通过第三氧化物层26c与多晶硅栅极区21分离。可以控制在掩埋多晶硅源极区27处的电荷或电压以改变半导体器件内部的电场分布,从而增加在器件击穿时的临界漏源电压。例如,通过在零伏特下对掩埋多晶硅源极区27进行偏置来获得resurf效应,将漏极电位均匀分布在漂移区23上,从而产生矩形电场分布。另外,掩埋多晶硅源极区27将多晶硅栅极区21与漏极区23部分屏蔽,从而减小栅漏电容,并且因此改善了器件的开关性能。

6.当包括resurf结构时,需要第三氧化物层26c来分离多晶硅栅极区21和掩埋多晶硅源极区27。第三氧化物层26c在交叉区28处与第一氧化物层26a和第二氧化物层26b连结。

7.接下来对图1所示的结构20的制造过程进行描述。首先,将例如氮化硅的掩模层沉积并且图案化在外延层23的顶部上。使用掩模层,蚀刻外延层23以形成沟槽22。通常,沟槽22延伸穿过外延层23的主要部分。在蚀刻之后,将氧化物层沉积在包括沟槽22和掩模层的结构上,随后在沟槽22中和掩模层上沉积多晶硅材料。将沉积的氧化物材料和多晶硅材料蚀刻至沟槽22内部的第一深度,使得剩余的沉积氧化物材料限定第二氧化物层26b,并且剩余的沉积多晶硅材料限定掩埋多晶硅源极区27。此后,移除掩模层并且在外延层23上和沟槽22中热生长二氧化硅层,以形成第一氧化物层26a和第三氧化物层26c。然后,沉积多晶硅材料并且将该多晶硅材料回蚀(etched back)至沟槽22的上表面,使得沟槽22中第三氧化

物层26c上方的剩余多晶硅材料限定多晶硅栅极区21。接下来,执行毯覆式离子注入(blanket ion implantation)以形成体区25,并且执行后续的离子注入以形成源极区24。掩蔽后续的离子注入以确保离子注入仅在半导体区的有源区中进行。这些注入步骤还形成漂移区23作为外延层23的非注入区,并且限定漂移区23从体区25的底部到基板的长度。

8.上述已知结构和工艺的缺点是难以相对于体区25和漂移区23将第二氧化物层26b和多晶硅掩埋源极区27适当对准。通过模拟,申请人发现需要高度的工艺控制来实现在器件的击穿电压方面的完全resurf效益(entitlement)。换言之,当已知器件使用已知制造工艺进行制造时,该已知器件对工艺变化特别敏感,因此在多沟槽mosfet结构20之间的击穿电压性能方面可能为不可靠。

技术实现要素:9.本发明的目的是提供一种防止或限制上述问题的沟槽栅极半导体器件及其制造方法。

10.根据本发明的一个方面,提供一种沟槽栅极半导体器件。该半导体器件包括布置在半导体区中的一个或多个单位单元(unit cell),每个单位单元包括:第一沟槽;第二沟槽,其从第一沟槽的底部延伸;第一氧化物层,其布置在第一沟槽的第一侧壁上并且形成单位单元的栅极氧化物;以及第二氧化物层,其布置在第二沟槽的第二侧壁和底部上。每个单位单元还包括:第一多晶硅区,其布置在第一沟槽内部,通过第一氧化物层与第一侧壁分离,并且形成单位单元的栅极;第二多晶硅区,其布置在第二沟槽内部,通过第二氧化物层与第二沟槽的第二侧壁和底部分离,并且形成单位单元的掩埋源极;以及第三氧化物层,其布置在第一多晶硅区和第二多晶硅区之间。

11.通过将第二沟槽布置在第一沟槽的底部的明确限定的深度处,可以使掩埋多晶硅源极区相对于体区更精确地定位,从而提高跨多个单位单元或甚至晶片的均匀性。更特别地,用于形成第一沟槽的沟槽蚀刻措施可以类似地用于回蚀第二多晶硅区,从而实现相对于体区和漂移区精确定位的第二多晶硅区和第三氧化物层。结果,根据本发明的器件或单位单元对工艺变化不敏感。

12.图1的已知器件的另一个缺点涉及当与模拟和/或理论预测相比时这些器件的泄漏和击穿行为有所劣化。申请人已经发现,这些不利影响可以归因于单位单元中氧化物结构的可靠性。更特别地,申请人已经发现,已知制造工艺导致在器件中第一氧化物层26a至第三氧化物层26c之间的连结在交叉区28处将通常表现出不连续性,这对器件性能产生不利影响。更特别地,申请人已经发现,第一氧化物层26a、第二氧化物层26b和第三氧化物层26c之间的不良和不平滑连结对器件的击穿电压性能是不利的。在不受理论约束的情况下,推测这可能归因于由于在第一氧化物层26a和第二氧化物层26b连结处的不均匀的氧化物厚度而导致的交叉区28处的高电场。另外,由于这种不良连结,观察到器件的漏电流的增加和整体栅极质量的降低。

13.为此,根据本发明,第一氧化物层、第二氧化物层和第三氧化物层中的每一个均可以为热生长的,其中这些氧化物层共同形成连续氧化物区。

14.申请人已经发现,由于首先使用沉积来设置第二氧化物层、同时使第一氧化物层和第三氧化物层热生长的原因,在图1所示器件中出现第一氧化物层至第三氧化物层之间

的不良连结。因此,如果第一氧化物层、第二氧化物层和第三氧化物层全部是热生长的,则可以实现这些氧化物层之间的更平滑连结,从而避免或减轻上述不利影响。

15.半导体区可以由第一电荷类型的半导体基板和布置在半导体基板顶部上的第一电荷类型的外延层形成,其中外延层的掺杂剂浓度小于半导体基板的掺杂剂浓度。此外,第一沟槽和第二沟槽可以仅布置在半导体区的外延层中。

16.第三氧化物层可以布置在第一沟槽与第二沟槽之间的边界处或附近。类似地,掩埋多晶硅源极区可以延伸至第一沟槽和第二沟槽之间的边界。

17.一个或多个单位单元还可以各自包括与第一电荷类型不同的第二电荷类型的体区,其中体区通过第一氧化物层与第一多晶硅区分离。体区的底表面可以高于第三氧化物层的顶表面,以确保对第一氧化物层的适当厚度控制。另外地或可替代地,一个或多个单位单元还可以各自包括第一电荷类型的源极区,其中源极区从半导体主体的顶表面竖直延伸至体区。此外,源极区的掺杂剂浓度优选地大于外延层的掺杂剂浓度,源极区的掺杂剂浓度更优选地大外延层的掺杂剂浓度至少两个数量级(at least two orders of magnitude greater)。

18.外延层中的掺杂通常为1e12cm-2。设计良好的resurf漂移区应能够支持区域中30v/微米的漏极电位。体区通常以1e13cm-2掺杂并且长度为约1.2微米。当从半导体区的表面测量时,源极区通常为5e15cm-2并且深度为约0.25微米。因此,典型的沟道长度在微米的范围内,但取决于击穿电压额定值。由于漏极的沟道耗尽(channel depletion from the drain),所以高额定值通常需要长的沟道。从沟道的端部至栅极多晶硅区的底部的距离通常为约0.2微米。

19.每个单位单元还可以包括壕沟区(moat region)。壕沟区使源极区和体区电短路,以实现良好的欧姆接触。可以利用源极金属化部(source metallization)来填充壕沟。在包括多个单位单元的一些实施例中,源极金属化部施加至所有壕沟区,使得所有单位单元处于相同的源极电位。壕沟区可以布置(优选居中地布置)在相应单位单元的第一沟槽和第二沟槽与相邻单位单元的第一沟槽和第二沟槽之间。壕沟区与相应单位单元的第一壕沟与第二壕沟间隔开,并且壕沟区通过蚀刻穿过源极区进入体区而形成。

20.一个或多个单位单元还可以包括布置在第一沟槽的顶部和源极区的顶部上的第四氧化物层,以及布置在第四氧化物层的顶部上的第五氧化物层。应注意的是,可以使用其它绝缘材料来代替第四氧化物层和/或第五氧化物层。此外,第五氧化物层可以用作对壕沟区进行蚀刻的掩模,并且第四氧化物层可以用于改善形成体区和源极区的离子注入。

21.半导体器件还可以包括诸如铝等第一金属层,该第一金属层布置在半导体器件的一个或多个单位单元中的一个或多个上,其中金属层可以构造成为一个或多个单位单元提供源极接触部(源极触点)、构造成与体区电接触以及构造成可选地将源极区与掩埋源极电连接。此外,半导体器件还可以包括金属接触部(金属触点),该金属接触部布置在所述一个或多个单位单元中的一个或多个单位单元的第一多晶硅区的顶部上并且构造成为所述一个或多个单位单元提供栅极接触部(栅极触点),其中金属接触部优选地布置在一个或多个单位单元的不存在金属层的端部处或附近。

22.通常,单位单元为细长的。在形成壕沟区后,铝被沉积或溅射并且被掩蔽和蚀刻以形成源极和栅极金属化部。通常在掩埋多晶硅源极区延伸至第一沟槽的顶部的端部处实现

源极金属化部与掩埋多晶硅源极区的接触。(通常)可以在单位单元的相反侧处实现栅极金属化部与栅极多晶硅区的接触。

23.一个或多个单位单元可以彼此相同。优选地,一个或多个单位单元为细长的,其具有0.5mm至4.0mm之间的长度和0.6微米至2.0微米之间的宽度。典型的半导体器件则可以包括100个以上的彼此相邻布置的这些单位单元。

24.第一沟槽相对于半导体区的顶表面的深度可以在0.5微米和2.0微米之间的范围内,优选在1.0微米和1.5微米之间的范围内,和/或第二沟槽相对于第一沟槽的底部的深度可以在0.2微米和2微米之间的范围内,优选在0.4微米和1.0微米之间的范围内。

25.半导体区优选包括硅基半导体区和/或第一氧化物层、第二氧化物层以及第三氧化物层可以包括热生长的二氧化硅。此外,半导体器件可以是沟槽栅极金属氧化物半导体场效应晶体管(mosfet)。

26.根据本发明的另一方面,提供一种制造上述沟槽栅极半导体器件的单位单元的方法。该方法包括使用第一掩模层在半导体区中形成第一沟槽,在第一沟槽的第一侧壁和底部上设置第一氧化物层,第一侧壁上的第一氧化物层形成单位单元的栅极氧化物。该方法还包括将第二掩模层沉积在第一沟槽内部,并且优选地使用干蚀刻对第二掩模层进行蚀刻以露出在第一沟槽的底部处下方的半导体区,同时第二掩模至少很大程度保持覆盖第一沟槽的侧壁上的第一氧化物层。该方法还包括使用蚀刻的第二掩模层形成第二沟槽。由此形成的第二沟槽从第一沟槽的底部延伸。该方法还包括:在蚀刻的第二掩模层仍至少部分就位的情况下,在第二沟槽的侧壁和底部上设置第二氧化物层;将第二多晶硅层沉积在第二沟槽中的第二氧化物层上,所述第二多晶硅层形成单位单元的掩埋源极。该方法还包括:在第二多晶硅层的顶部上设置第三氧化物层;移除第二掩模层;以及将第一多晶硅层沉积在第三氧化物层和第一氧化物层上,所述第一多晶硅层形成单位单元的栅极。

27.设置第一氧化物层、第二氧化物层和第三氧化物层可以包括使所述第一氧化物层、所述第二氧化物层和所述第三氧化物层热生长,其中所述第一氧化物层、所述第二氧化物层和所述第三氧化物层共同形成连续氧化物区。

28.该方法还可以包括在使第三氧化物层热生长之前,对蚀刻的第二掩模层的在第一沟槽的底部处或附近的部分进行蚀刻。对蚀刻的第二掩模的部分蚀刻改善了第一氧化物层、第二氧化物层和第三氧化物层之间的连结。更特别地,申请人已经发现,第二氧化物层的热生长使紧邻第一氧化物层布置的第二掩模层变形。这种例如向内取向弯曲的变形可能使第一氧化物层、第二氧化物层和第三氧化物层之间的连结劣化。然而,在使第三氧化物层热生长之前,可以通过执行蚀刻步骤(例如干蚀刻步骤)来移除该变形。

29.半导体区可以包括布置在第一电荷类型的半导体基板的顶部上的第一电荷类型的外延层,其中外延层区的掺杂剂浓度小于半导体基板的掺杂剂浓度。第一沟槽和第二沟槽优选地仅形成在半导体区的外延层中。

30.形成第一沟槽还可以包括沉积和图案化第一掩模层,并且使用图案化的第一掩模层形成第一沟槽。

31.该方法还可以包括:沉积第四氧化物层;通过将与第一电荷类型不同的第二电荷类型的掺杂剂注入穿过第四氧化物层而在半导体区中形成体区,其中体区通过第一氧化物层与第一多晶硅区分离;以及通过将第一电荷类型的掺杂剂注入穿过第四氧化物层而在半

导体主体中形成源极区,其中源极区从半导体主体的顶表面竖直延伸至体区。

32.体区的底表面可以高于第三氧化物层的顶表面,和/或第一多晶硅区的底表面可以低于体区的底表面。

33.该方法还可以包括将第五氧化物层沉积并且图案化在第四氧化物的顶部上。该方法还可以包括使用第五氧化物层作为掩模,在半导体主体中形成壕沟区。更特别地,半导体区的未被第五氧化物层覆盖的那些部分被刻蚀至体区。

34.该方法还可以包括在所述一个或多个单位单元中的一个或多个单位单元的顶部上设置金属层,其中该金属层构造成为单位单元提供源极接触部、构造成与体区电接触并且构造成可选地将源极区与掩埋源极电连接。另外,该方法还可以包括在第一多晶硅区的顶部上形成金属接触部以为单位单元提供栅极接触部,其中金属接触部优选形成在单位单元的不存在金属层的端部处或附近。

35.通过执行该方法可以同时形成多个单位单元,其中单位单元优选彼此相同。

36.第一沟槽相对于半导体区的顶表面的深度可以在0.5微米和2.0微米之间的范围内,优选在1.0微米和1.5微米之间的范围内,和/或第二沟槽相对于第一沟槽底部的深度可以在0.2微米和2微米之间的范围内,优选在0.4微米和1.0微米之间的范围内。

37.半导体区优选为硅基半导体区。第一掩模层和第二掩模层中的至少一个可以包括氮化硅或者氧化物-氮化物-氧化物(oxide nitride oxide)(ono)。

38.沟槽栅极半导体器件可以是沟槽栅极金属氧化物半导体场效应晶体管(mosfet)。

附图说明

39.接下来,将参照附图对本发明进行描述,其中:

40.图1是根据现有技术已知的沟槽mosfet的截面图;

41.图2a至图2h是根据本发明的一些实施例在各种处理步骤处的沟槽栅极半导体器件的单位单元的截面图;

42.图3是根据本发明的实施例的沟槽栅极半导体器件的单位单元的截面图;并且

43.图4是根据本发明的实施例的具有多个单位单元的沟槽栅极半导体器件的简化顶视图。

具体实施方式

44.以下将参照附图。应当注意的是,相同的附图标记可以用于表示相同或相似的部件。此外,图1和图2a至图2h中描绘的单位单元沿这些图中的竖直轴线对称。因此,出于说明目的,仅示出了单位单元的一半。

45.图2a至图2h示出了制造其中使用硅半导体区的沟槽栅极半导体器件100的单位单元1的第一部分工艺。将参照图3描述其余的工艺步骤。应注意的是,该工艺可以用于单独制造单个单位单元,或在同一半导体区上同时制造多个单位单元。

46.参照图2a,将第一掩模层2a沉积并且图案化至半导体区的表面上。例如,将第一掩模层2a设置在布置于半导体基板(半导体衬底)(未示出)顶部上的外延层3的顶部上。将第一掩模层2a图案化,使得半导体区的将设置沟槽4a的部分被露出,而半导体区的其余部分被覆盖。例如,氮化硅或氧化物-氮化物-氧化物(ono)可以用于第一掩模层2a。

47.参照图2b,随后通过回蚀半导体区(例如外延层3)的露出部来形成第一沟槽4a。例如,第一沟槽4a可以具有在1.0微米和1.5微米之间的范围内的深度。然而,第一沟槽4a的深度不局限于此,并且可以取决于半导体器件100的期望击穿电压额定值或所需沟道长度。

48.参照图2c,在形成第一沟槽4a后,将第一氧化物层5a设置在第一沟槽4a的侧壁和底部上。第一氧化物层5a的在第一沟槽4a的侧壁上的部分将最终形成半导体器件100的栅极氧化物。例如,第一氧化物层5a热生长至第一沟槽4a的侧壁和底部上。第一氧化物层5a的最佳厚度可以取决于将使用半导体器件100的应用。本发明特别适用于可以在dc(直流)和500khz之间的频率范围内操作并且处理5a/mm2之间的电流的沟槽mosfet。对于这种器件,第一氧化物层5a通常具有与给定额定电压匹配的厚度。

49.参照图2d,在已经设置第一氧化物层5a后,将第二掩模层2b沉积至特别是第一沟槽5a的底部和侧壁上的第一氧化物层5a上。

50.参照图2e,干蚀刻第二掩模层2b,从而使第一沟槽4a底部处的第一氧化物层5a露出,而覆盖第一沟槽4a侧壁上的第一氧化物层5a。然后,干蚀刻露出的第一氧化物层5a以露出下方的半导体区。此后,将第二沟槽4b蚀刻至从第一沟槽4a的底部延伸的半导体区(例如外延层3)中,并且使用蚀刻的第二掩模层2b作为保护掩模,即,第二掩模层2b限定用于第二沟槽4b的沟槽掩模。第二沟槽4b可以用作resurf结构的基础。第二沟槽4b可以具有0.4微米和1.0微米之间的深度,诸如0.6微米。

51.参照图2f,将第二氧化物层5b设置在第二沟槽4b的第二侧壁和底部上。特别地,在图案化的第二掩模层2b仍然至少部分就位的情况下设置第二氧化物层5b。例如,使第二氧化物层5b热生长至第二沟槽4b的第二侧壁和底部上。

52.参照图2g,将多晶硅材料沉积至第二氧化物层5b上。在已经沉积多晶硅材料后,回蚀该多晶硅材料,例如直到露出第一沟槽的第一侧壁上的第二掩模层2b的底部为止。换言之,将多晶硅材料回蚀至第一沟槽4a和第二沟槽4b之间的边界,并且剩余的多晶硅材料形成第二多晶硅区6,该第二多晶硅区6形成单位单元1的掩埋源极。然后,将第三氧化物层5c设置在第二多晶硅区6的顶部上,该第三氧化物层5c与第一氧化物层5a和第二氧化物层5b连结以形成连续氧化物区。可选地,在设置第三氧化物层5c之前额外蚀刻第二掩模层2b的一部分,以确保氧化物层5a至5c之间的平滑连结。作为示例,第三氧化物层热生长至第二多晶硅区6上。

53.申请人已经发现,通过使第二氧化物层5b热生长,已经布置的第二掩模层2b可能变形。这在图2f中使用箭头z示出。更特别地,第二掩模层2b可能向内延伸。在使第三氧化物层5c热生长之前,可以使用干蚀刻技术来移除第二掩模层2b的该向内取向部。通过这种方式,可以改善氧化物层5a至5c之间的连结。

54.参照图2h,将多晶硅材料沉积至第三氧化物层5c和第一氧化物层5a上,并且将多晶硅材料回蚀至半导体区的顶表面。剩余的多晶硅材料形成第一多晶硅区7,该第一多晶硅区7形成单位单元1的栅极。

55.图3示出了完成的单位单元1的截面图。在利用多晶硅和氧化物层来填充第一沟槽4a和第二沟槽4b之后,可以可选地将第四氧化物层设置在半导体区的顶部上。尽管不是必需的,但第四氧化物层5d在掺杂剂注入至半导体区期间可能是有益的,这是因为第四氧化物层5d防止或限制掺杂剂的沟道效应(channelling)并且增加注入区中的注入均匀性的缘

故。

56.使用例如毯覆式注入技术将不同于第一电荷类型的第二电荷类型的掺杂剂可选地通过第四氧化物层5d而注入体区(body region)8。然后,将第一电荷类型的掺杂剂可选地通过第四氧化物层5d而注入源极区9。特别地,体区8可以与第一多晶硅区7横向邻接形成,并且可以通过第一氧化物层5a与第一多晶硅区7分离。源极区9可以从半导体区的顶表面延伸至体区8。例如,将源极区9注入至器件的主体(body)中并且在体区中的深度通常为0.2微米,该体区的深度通常为1.2微米。

57.然后将第五氧化物层5e沉积在第四氧化物层5d上并且随后图案化第五氧化物层5e。然后,可以将壕沟区10蚀刻至半导体区中,从而蚀刻至体区8中,其中第五氧化物层5e用作保护掩模以防止沟槽结构、源极区9和体区8被蚀刻。壕沟区10构造成向源极区9和体区8提供电接触(电触点)。

58.然后,将金属层11设置在半导体器件100中的单位单元1和其它单位单元的顶部上。金属层11向半导体器件100中的一个或多个单位单元1的一个或多个源极区9提供单一接触(触点)。第五氧化物层5e将沟槽结构与金属层11隔离。在设置金属层11之前,可以使用离子注入来改善金属层11和体区8之间的欧姆接触。

59.图4示出了包括多个单位单元的半导体器件100的简化顶视图。在这些单位单元中,示出了在有源区12上延伸的金属层11。

60.第一沟槽4a和第二沟槽4b共同形成沟槽带,该沟槽带在有源区12上方延伸并且超出有源区。金属层11还在有源区12外部的沟槽带的端部13处与掩埋多晶硅源极区接触,其中如图2g所示,在形成第二多晶硅区6期间对多晶硅进行掩蔽以阻止多晶硅被蚀刻。与源极区9的接触在与图案化单位单元中的氧化物5e的阶段相同的阶段限定。图案化栅极金属化部14在沟槽带的相反端处与多个单位单元的第一多晶硅区7接触。与第一多晶硅区7的接触同样在与图案化单位单元中的氧化物5e的阶段相同的阶段限定。

61.在上述实施例中,第一电荷类型可以指n型,并且第二电荷类型可以指p型,反之亦然。

62.以上,已经使用本发明的详细实施例对本发明进行说明。然而,应当理解的是,本发明不局限于这些实施例,并且在不脱离由所附权利要求限定的本发明的范围的情况下可以进行各种修改。