半导体装置及其制造方法与流程

1.本发明涉及半导体装置及其制造方法。

背景技术:

2.在专利文献1中,公开了沟槽型的纵型mosfet(metal-oxide-semiconductor field-effect transistor)。就该mosfet而言,成为栅极的沟槽的形状是如γ字这样朝向沟槽内部的凸的形状。其结果,沟槽的表面积减小,能够降低栅极-源极间、栅极-漏极间的电容,能够缩短通断时间。

3.专利文献1:日本特开平11-111983号公报

4.就专利文献1的半导体装置而言,沟槽形状呈γ字型,因此,在具有沟道的部位处产生倾斜。因此,饱和电流的波动有可能变大。

技术实现要素:

5.本发明就是为了解决上述课题而提出的,其目的在于得到能够抑制饱和电流的波动的半导体装置及其制造方法。

6.本发明涉及的半导体装置具有:基板,其具有上表面和与该上表面相反侧的背面;第1导电型的漂移层,其设置于该基板的该上表面侧;与该第1导电型不同的第2导电型的基极层,其设置于该漂移层的该上表面侧;该第1导电型的上部半导体层,其设置于该基极层的该上表面侧;第1电极,其设置于该基板的该上表面,与该上部半导体层电连接;第2电极,其设置于该基板的该背面;沟槽,其从该基板的该上表面将该上部半导体层和该基极层贯穿而延伸至该漂移层为止;以及栅极电极,其设置于该沟槽的内部,该沟槽的内侧面具有第1面和设置于比该第1面更靠下方处的第2面,该第2面相对于该第1面而向该沟槽的内侧倾斜,该第1面与该第2面的交点设置于比该基极层更靠下方处。

7.在本发明涉及的半导体装置的制造方法中,在具有上表面和与该上表面相反侧的背面的基板的该上表面侧形成第1导电型的漂移层,在该漂移层的该上表面侧形成与该第1导电型不同的第2导电型的基极层,在该基极层的该上表面侧形成该第1导电型的上部半导体层,通过蚀刻而形成从该基板的该上表面延伸至比该基极层更靠下方的深度为止的第1沟槽,实施与该第1沟槽的形成时相比提高蚀刻气体的压力、与该第1沟槽的形成时相比使蚀刻所使用的离子的加压电压下降、或者设为与该第1沟槽的形成时相比伴随蚀刻而产生的副产物更容易沉积的条件中的至少一者,从该第1沟槽的底部进行蚀刻,形成第2沟槽,在该基板的该上表面形成与该上部半导体层电连接的第1电极,在该基板的该背面形成第2电极,在由该第1沟槽和该第2沟槽形成的沟槽的内部形成栅极电极。

8.发明的效果

9.就本发明涉及的半导体装置及其制造方法而言,第1面与相对于第1面而向沟槽的内侧倾斜的第2面之间的交点设置于比基极层更靠下方处。由此,能够抑制饱和电流的波动。

附图说明

10.图1是实施方式1涉及的半导体装置的俯视图。

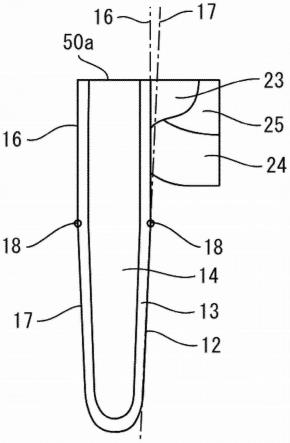

11.图2是将图1在a-a直线切断而得到的剖视图。

12.图3是图2的放大图。

13.图4是实施方式1涉及的沟槽周边的放大图。

14.图5是表示在基板形成漂移层、基极层及发射极层后的状态的图。

15.图6是表示对基板进行蚀刻后的状态的图。

16.图7是表示从第1沟槽的底部进行蚀刻而形成第2沟槽后的状态的图。

17.图8是第1对比例涉及的半导体装置的剖视图。

18.图9是第2对比例涉及的半导体装置的剖视图。

19.图10是实施方式1涉及的半导体装置的剖视图。

20.图11是表示集电极电流对栅极电压的依赖性的特性图。

21.图12是交点的深度tc相对于基极层的深度tb之比与集电极电流的波动的相关图。

22.图13是tc/tb相对于沟槽的深度的相关图。

23.图14是对实施方式1涉及的半导体装置的构造进行说明的图。

24.图15是实施方式2涉及的半导体装置的剖视图。

25.图16是实施方式3涉及的半导体装置的剖视图。

26.图17是实施方式4涉及的半导体装置的剖视图。

27.图18是实施方式5涉及的半导体装置的剖视图。

28.图19是实施方式6涉及的半导体装置的剖视图。

29.图20是实施方式7涉及的半导体装置的剖视图。

具体实施方式

30.参照附图,对各本实施方式涉及的半导体装置及其制造方法进行说明。对相同或相应的结构要素标注相同的标号,有时省略重复说明。

31.实施方式1

32.图1是实施方式1涉及的半导体装置100的俯视图。图2是将图1在a-a直线切断而得到的剖视图。半导体装置100例如是igbt(insulated gate bipolar transistor)。半导体装置100例如被用作电力半导体装置。

33.半导体装置100具有基板50,该基板50具有上表面50a和与上表面50a相反侧的背面50b。基板50为n型,例如由si形成。n型对应于第1导电型,p型对应于第2导电型。各层的导电型也可以相反。

34.在基板50的上表面50a侧设置n型的漂移层20。在漂移层20的上表面50a侧设置p型的基极层24。在基极层24的上表面50a侧设置n型的发射极层23。发射极层23对应于上部半导体层。在基极层24的上表面50a侧设置p型的接触层25。发射极层23和接触层25分别形成于基极层24的上表面50a侧的一部分。

35.在基板50的背面50b侧形成n型的缓冲层21。在缓冲层21的背面50b侧形成有p型的集电极层22。

36.在基板50形成沟槽12。沟槽12从基板50的上表面50a起将发射极层23和基极层24

贯穿而延伸至漂移层20。沟槽12的内侧面由栅极绝缘膜13覆盖。在沟槽12的内部隔着栅极绝缘膜13而埋设有栅极电极14。层间绝缘膜15将栅极电极14的上表面覆盖。栅极电极14与图1所示的栅极焊盘19电连接。

37.在基板50形成有多个单元区域40。各单元区域40具有发射极层23、基极层24、接触层25、栅极电极14及层间绝缘膜15。在基板50的上表面50a设置与发射极层23电连接的发射极电极10。发射极电极10对应于第1电极。发射极电极10形成于多个单元区域40之上。发射极电极10与发射极层23、基极层24、接触层25连接。栅极电极14通过层间绝缘膜15而与发射极电极10绝缘。在基板50的背面50b形成有集电极(collector)电极(electrode)11。集电极电极11对应于第2电极。

38.图3是图2的放大图。图4是实施方式1涉及的沟槽12周边的放大图。就沟槽12而言,越是下方,宽度越窄。沟槽12的内侧面具有第1面16和设置于比第1面16更靠下方处的第2面17。第2面17相对于第1面16朝向沟槽12的内侧而倾斜。在图4中,作为一个例子,第1面16与第2面17的交点18配置于与基极层24的下端相同的深度处。即,交点18配置于与沟道掺杂的下端相同的深度处。第1面16与第2面17的交点18也可以设置于比基极层24更靠下方处。另外,沟槽12的底面由曲面形成,呈圆弧状。将沟槽12的底面与第2面17连接的角部被倒圆角。

39.如图4所示,第2面17与基板50的上表面50a所成的角θ2比第1面16与基板50的上表面50a所成的角θ1小。即,就沟槽12而言,与比交点18更靠上方的部分相比,下方的部分的每单位深度的宽度的减小量更大。

40.接下来,对半导体装置100的制造方法进行说明。首先,在基板50的上表面50a侧形成漂移层20,在漂移层20的上表面50a侧形成基极层24,在基极层24的上表面50a侧形成发射极层23。图5是表示在基板50形成漂移层20、基极层24及发射极层23后的状态的图。基极层24、发射极层23能够通过离子注入等技术而形成。漂移层20、基极层24、发射极层23的形成顺序不受限定。

41.接下来,在发射极层23的上表面形成具有开口55的掩模56。接下来,使用掩模56而进行干蚀刻,形成第1沟槽12a。图6是表示对基板50进行蚀刻后的状态的图。第1沟槽12a例如延续至基极层24的下端为止。根据最终的沟槽12的深度,第1沟槽12a的深度不同。例如,在最终的沟槽12的深度为5.0μm的情况下,第1沟槽12a的深度成为直至基极层24的下端为止的深度。另外,也可以以如下方式形成第1沟槽12a,即,通过蚀刻而使第1沟槽12a从基板50的上表面50a起延伸至比基极层24更靠下方的深度为止。

42.第1沟槽12a的侧面与基板50的上表面50a大致垂直。第1沟槽12a的内侧面与基板50的上表面50a所成的角θ1例如大于或等于89

°

。角θ1能够通过调整干蚀刻中的蚀刻气体的压力或蚀刻所使用的离子的加压电压而进行控制。另外,角θ1能够通过调整伴随蚀刻而产生的副产物的沉积条件而进行控制。例如,如果提高气体中的碳比率,则副产物变得容易沉积。具体地说,蚀刻气体的压力越低、或者离子的加压电压越高,则越能够使角θ1变大。另外,越是在伴随蚀刻而产生的副产物的量少的条件下,越能够使角θ1变大。

43.接下来,从第1沟槽12a的底部进行干蚀刻,形成第2沟槽12b。图7是表示从第1沟槽12a的底部进行蚀刻而形成第2沟槽12b后的状态的图。第2沟槽12b的内侧面与第1沟槽12a的内侧面相比,相对于基板50的上表面50a而大幅度地倾斜。第2沟槽12b的内侧面与基板50的上表面50a所成的角θ2例如小于或等于88

°

。

44.与形成第1沟槽12a时的蚀刻条件相比,用于形成第2沟槽12b的蚀刻条件在能够将角θ2控制得小的条件下进行。与例如第1沟槽12a的形成时相比,用于形成第2沟槽12b的蚀刻例如是提高了蚀刻气体的压力而实施的。另外,也可以是与第1沟槽12a的形成时相比,用于形成第2沟槽12b的蚀刻为使蚀刻所使用的离子的加压电压下降而进行的。另外,也可以是与第1沟槽12a的形成时相比,用于形成第2沟槽12b的蚀刻为在伴随蚀刻而产生的副产物容易沉积的条件下进行的。用于形成第2沟槽12b的蚀刻条件只要是实施这3个条件的至少1者而进行的即可。

45.这样,本实施方式的第1沟槽12a和第2沟槽12b通过不同的蚀刻条件而形成。沟槽12只要至少在基板50形成基极层24的工序之后形成即可。然后,在沟槽12的内壁之上形成氧化膜作为栅极绝缘膜13。接下来,在沟槽12的内部,在栅极绝缘膜13之上形成栅极多晶硅作为栅极电极14。由此,在沟槽12的内部形成栅极电极14。另外,在基板50的上表面50a形成发射极电极10,在基板50的背面50b形成集电极电极11。

46.接下来,一边与对比例进行比较一边对本实施方式的效果进行说明。图8是第1对比例涉及的半导体装置101的剖视图。图9是第2对比例涉及的半导体装置102的剖视图。图10是实施方式1涉及的半导体装置100的剖视图。就第1对比例涉及的半导体装置101而言,沟槽121的内侧面整体以一定的角度倾斜。另外,就第2对比例涉及的半导体装置102而言,与本实施方式相比,沟槽122的内侧面处的交点18设置于更浅的位置处。沟槽122处的交点18例如设置于与发射极层23的下端相同的深度处。沟槽121及本实施方式的沟槽12的深度例如是5.8μm,沟槽122的深度是3.8μm。

47.图11是表示集电极电流对栅极电压的依赖性的特性图。在图11中,针对半导体装置100、101、102而比较了直至vg=15v为止的ice。在图11中,栅极电压vg表示向栅极电极14的正向偏置。另外,集电极电流ice表示从集电极电极11向发射极电极10流通的电流。

48.就第1对比例涉及的半导体装置101而言,基板50的上表面50a与沟槽121的内侧面所成的角θ3越小,则饱和电流越是减小。在角θ3为86

°

~89

°

的范围中,饱和电流的波动大致为30%。与此相对,就本实施方式的半导体装置100而言,得到比θ3=90

°

所示的u字型沟槽及半导体装置101、102更大的集电极电流。

49.通常,就θ3=90

°

所示的u字型的沟槽而言,随着沟槽变深,反馈电容增加。并且,有时沟槽越深,则越难以保持u字型的形状。另外,在第1对比例涉及的沟槽121具有一定以上的倾斜的情况下,沟道长度存在变长的倾向。另外,沟槽121的倾斜角度有可能波动。如图11所示,如果沟槽121的倾斜角度波动,则饱和电流有可能大幅度地波动。

50.就igbt而言,如果向集电极电极11及栅极电极14施加正向偏置,则在与栅极绝缘膜13接触的基极层24处产生反转层,形成沟道。由此,开始从集电极电极11向发射极电极10的通电,igbt成为接通状态。如果沟道的长度不稳定,则在向栅极电极14施加了高的正向偏置的状态下,通电能力波动。由此,有可能导致接通电压的增加、通断时的接通特性的增加、短路耐量的下降等。特别地,在将多个芯片并联连接地使用的情况下,通电时的电流有可能产生波动。由此,soa(safety operating area)的耐量有可能下降。

51.与此相对,就本实施方式的半导体装置100而言,沟槽12中的与基极层24接触的第1面16与基板50的上表面50a大致垂直。因此,能够抑制沟道长度。另外,能够抑制第1面16的倾斜角度的波动。由此,能够抑制沟道长度的波动。因此,能够抑制向栅极电极14的高的正

向偏置时的通电能力的波动。即,能够抑制饱和电流的波动。另外,能够抑制阈值电压的波动。由此,能够抑制接通电压,实现短路耐量的提高。另外,即使在将多个半导体装置100并联连接的情况下,也能够抑制电流波动。因此,能够在soa中抑制电流向电流容易流过的芯片集中,能够使耐量增加。

52.在沟槽12中,第1面16与基板50的上表面50a所成的角θ1只要比89

°

大且小于或等于90

°

即可。如图11所示,如果是该角度范围,则依赖于角θ1的集电极电流的变动变小,能够抑制集电极电流的波动。另外,第2面17与基板50的上表面50a所成的角θ2只要大于86

°

且小于或等于88

°

即可。由此,特别地,在深度为6μm等的深的沟槽12中,能够将沟槽12底部的形状保持为圆形。由此,能够抑制电压施加时的电场集中,能够抑制耐压下降。

53.图12是交点18的深度tc相对于基极层24的深度tb之比与集电极电流的波动的相关图。深度tb表示从基板50的上表面50a至基极层24中的与沟槽12相邻的部分的下端为止的深度。即,深度tb相当于将面向沟槽12的侧壁的发射极层23的宽度与在基极层24形成的沟道长度相加后的值。深度tc表示从基板50的上表面50a至交点18为止的深度。

54.在图12中,针对沟槽12的深度为5.8μm、4.8μm、3.8μm的情况而示出tc/tb与饱和电流的波动的关系。沟槽12越浅则饱和电流的波动越大。但是,在沟槽12的深度为3.8μm的构造中,同样地,通过使tc/tb例如大于1,从而能够抑制饱和电流的波动。即,通过将第1面16与第2面17的交点18配置于比基极层24更靠下方处,从而在浅的沟槽12时也能够抑制饱和电流的波动。

55.图13是tc/tb相对于沟槽12的深度的相关图。在图13中,示出了饱和电流的波动为2%的情况下的沟槽12的至底部为止的深度td与tc/tb的关系。从图13所示的数据的近似曲线可知,交点18的深度tc、基极层24的深度tb和沟槽12的深度td只要满足下式(1)即可。

56.【式1】

57.tc/tb≥20.563

×

exp(t

d0.973

)+1

…

(1)

58.由此,能够将饱和电流的波动抑制为小于或等于2%。另外,从图13可以确认:如果沟槽12变深,则tc/tb的比率接近1。

59.图14是对实施方式1涉及的半导体装置100的构造进行说明的图。如图14所示,在本实施方式中,作为一个例子,将第1面16与第2面17的交点18配置于比基极层24更靠下方处。由此,如图12所示,在浅的沟槽12时也能够抑制饱和电流的波动。另外,如图13所示,通过沟槽12的深度,从而即使将交点18配置于与基极层24的下端相同的深度处,也能够充分地抑制饱和电流的波动。

60.另外,半导体装置100的反馈电容c

res

能够由下式(2)表示。

61.【式2】

[0062][0063]

这里,w

t

是沟槽12的宽度,c

ox

是在沟槽12的内部设置的栅极绝缘膜13的静电电容,cm是耗尽层的静电电容。w

t

是沟槽12中的基板50的上表面50a处的宽度最宽的部分的宽度。在本实施方式中,与u字型的沟槽相比,能够以式(2)的2(t

d-tb)/tanθ2这一项的量而抑制反馈电容c

res

。因此,在本实施方式中,能够实现反馈电容c

res

的减小。这样,在本实施方式中,能够一边抑制反馈电容一边抑制饱和电流的波动。

[0064]

在本实施方式中,对半导体装置100是igbt的例子进行了说明,但半导体装置100也可以是mosfet。

[0065]

另外,半导体装置100也可以由宽带隙半导体形成。宽带隙半导体例如是碳化硅、氮化镓类材料或金刚石。对于由宽带隙半导体形成的半导体装置100,在流过高电流的情况下,根据本实施方式,也能够抑制由饱和电流的波动造成的耐压下降。因此,能够有效地利用半导体装置100的性能。

[0066]

这些变形能够适当应用于以下实施方式涉及的半导体装置及其制造方法。此外,关于以下实施方式涉及的半导体装置及其制造方法,由于与实施方式1之间的共通点多,因而以与实施方式1的不同点为中心进行说明。

[0067]

实施方式2

[0068]

图15是实施方式2涉及的半导体装置200的剖视图。半导体装置200具有呈n型、浓度比漂移层20高的载流子储存层26。载流子储存层26在漂移层20的上表面50a侧设置至比基极层24更深的位置为止。其它结构与半导体装置100的结构相同。

[0069]

在本实施方式中,在通电时从集电极层22供给的空穴被积蓄于载流子储存层26。由此,能够降低传导率,降低接通电阻。

[0070]

实施方式3

[0071]

图16是实施方式3涉及的半导体装置300的剖视图。半导体装置300具有在沟槽12之下设置的p型的底层28。其它结构与半导体装置100的结构相同。通过底层28,能够抑制在通断时电场集中于沟槽栅极的底部。因此,能够进一步提高soa耐量。

[0072]

实施方式4

[0073]

图17是实施方式4涉及的半导体装置400的剖视图。就半导体装置400而言,发射极电极10具有沟槽接触(trench contact)29。沟槽接触29在彼此相邻的一对沟槽12之间从基板50的上表面50a起将发射极层23贯穿,凸出至基极层24的内部。接触层25在基极层24的内部以与沟槽接触29的底部接触的方式设置。其它结构与半导体装置100的结构相同。

[0074]

就半导体装置400而言,在igbt的通断时集电极电流不流过发射极层23的正下方,而是例如如箭头80所示流过沟槽接触29。即,集电极电流在到达发射极层23正下方之前流过沟槽接触29。由此,能够实现闩锁耐量的提高。

[0075]

实施方式5

[0076]

图18是实施方式5涉及的半导体装置500的剖视图。就半导体装置500而言,栅极电极具有第1栅极电极14a和隔着栅极绝缘膜13而设置于第1栅极电极14a的下方的第2栅极电极14b。第1栅极电极14a设置于比交点18更靠上方处,第2栅极电极14b设置于比交点18更靠下方处。其它结构与半导体装置100的结构相同。通过应用2层栅极构造,能够确保栅极绝缘膜13的厚度,降低反馈电容。

[0077]

实施方式6

[0078]

图19是实施方式6涉及的半导体装置600的剖视图。半导体装置600具有多个沟槽12。多个沟槽12包含以不隔着基极层24和发射极层23的方式相邻的一对沟槽12。在该一对沟槽12之间设置p型的载流子积蓄层27。其它结构与半导体装置100的结构相同。

[0079]

在本实施方式中,与实施方式1相比,单元区域40被稀疏化。根据该结构,能够将在通电时从集电极层22供给的空穴积蓄于载流子积蓄层27。由此,能够降低传导率,降低接通

电阻。

[0080]

在图19中,单元区域40与载流子积蓄层27交替地设置。不限于此,半导体装置600只要具有至少1个单元区域40被稀疏化且设置有载流子积蓄层27的区域即可。

[0081]

实施方式7

[0082]

图20是实施方式7涉及的半导体装置700的剖视图。半导体装置700是rc(reverse-conducting)-igbt。就半导体装置700而言,二极管和igbt形成于同一基板50。在二极管区域,集电极层22被置换为n型的阴极层32。另外,在二极管区域不设置发射极层23及接触层25。就半导体装置700而言,也能够得到与实施方式1相同的效果。

[0083]

此外,在各实施方式中说明过的技术特征也可以适当地组合使用。

[0084]

标号的说明

[0085]

10发射极电极,11集电极电极,12沟槽,12a第1沟槽,12b第2沟槽,13栅极绝缘膜,14栅极电极,14a第1栅极电极,14b第2栅极电极,15层间绝缘膜,16第1面,17第2面,18交点,19栅极焊盘,20漂移层,21缓冲层,22集电极层,23发射极层,24基极层,25接触层,26载流子储存层,27载流子积蓄层,28底层,29沟槽接触,32阴极层,40单元区域,50基板,50a上表面,50b背面,55开口,56掩模,100、101、102半导体装置,121、122沟槽,200、300、400、500、600、700半导体装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1