半导体组件及其形成方法与流程

1.本发明实施例提供一种半导体组件及其形成方法。

背景技术:

2.由于各种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度的持续改善,半导体行业已经历快速发展。在很大程度上,集成密度的改善源自于最小特征大小(minimum feature size)的不断减小,此使得更多的组件能够集成到给定面积中。随着对缩小电子器件的需求已增加,已出现对更小且更具创造性的半导体管芯封装技术的需要。此种封装系统的实例是叠层封装(package-on-package,pop)技术。在pop器件中,顶部半导体封装被堆叠在底部半导体封装的顶部上,以提供高集成水平及组件密度。pop技术一般能够生产功能性得到增强且在印刷电路板(printed circuit board,pcb)上占用空间小的半导体器件。

技术实现要素:

3.本发明实施例提供一种半导体组件,包括:重布线结构;集成电路封装,贴合到所述重布线结构的第一侧;芯体衬底,利用第一导电连接件及第二导电连接件耦合到所述重布线结构的第二侧,所述第二侧与所述第一侧相对,所述芯体衬底的顶部层包含介电材料;以及芯片,设置在所述重布线结构与所述芯体衬底之间,所述芯片夹置在所述介电材料的侧壁之间。

4.本发明实施例提供一种半导体组件,包括:第一通孔及第二通孔,从重布线结构的第一侧延伸,凸块下金属与所述重布线结构相对地位于所述第二通孔上;电压调节器,实体耦合及电耦合到所述第一通孔;集成电路封装,通过所述重布线结构耦合到所述电压调节器,所述集成电路封装位于所述重布线结构的与所述第一侧相对的第二侧上;以及芯体衬底,利用导电连接件贴合到所述凸块下金属,所述芯体衬底上的介电材料夹置在所述导电连接件与所述电压调节器之间。

5.本发明实施例提供一种形成半导体组件的方法,所述方法包括:在第一衬底上形成重布线结构;将芯片贴合到所述重布线结构的第一侧;在芯体衬底中形成开口;将所述芯体衬底贴合到所述重布线结构的所述第一侧,所述芯片夹置在所述开口的侧壁之间;利用包封体包封所述芯体衬底,其中所述包封体沿着所述芯体衬底的侧壁延伸,其中所述包封体进一步包封所述芯片;从所述第一衬底移除所述重布线结构;以及将集成电路封装贴合到所述重布线结构的第二侧,所述第二侧与所述第一侧相对。

附图说明

6.结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的尺寸。

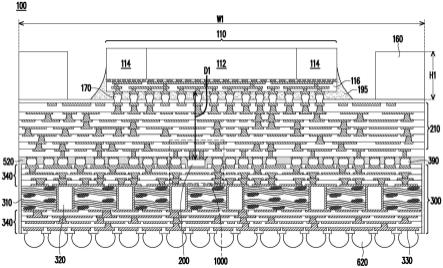

7.图1示出根据一些实施例的封装组件的剖视图。

8.图2示出根据一些实施例的图1所示剖视图的一部分的详细视图。

9.图3到图15、图18及图19示出根据一些实施例的用于形成封装组件的工艺期间的中间步骤的剖视图。

10.图16示出根据一些实施例的晶片衬底上的封装区的布局的剖视图与平面图。

11.图17示出根据一些实施例的面板衬底上的封装区的布局的剖视图与平面图。

12.图20示出根据一些实施例的封装组件的剖视图。

13.[符号的说明]

[0014]

100、400:经单体化封装组件

[0015]

101a:第一封装区/封装区

[0016]

101b:第二封装区/封装区

[0017]

101c~101i:封装区

[0018]

102、802:载体衬底

[0019]

103、208a~208f:绝缘层

[0020]

104、209a~209f:重布线层

[0021]

104a:接触焊盘

[0022]

104b:导电线

[0023]

110、410:集成电路封装

[0024]

112:逻辑管芯

[0025]

114:i/o管芯

[0026]

116、210、340、340a、340b:重布线结构

[0027]

160:保护环

[0028]

170、202、390:导电连接件

[0029]

195、206:底部填充胶

[0030]

200:集成电压调节器

[0031]

204:焊料区

[0032]

212:通孔

[0033]

214、330、330a、330b:凸块下金属

[0034]

220:介电层

[0035]

240、360:开口

[0036]

300、300a、300b:芯体衬底

[0037]

310:芯体

[0038]

320:导通孔

[0039]

320a:导电材料

[0040]

320b:填充材料

[0041]

350a、350b:阻焊剂

[0042]

352、1000、1002:区

[0043]

401、402:线

[0044]

412:cpu或gpu

[0045]

414:存储器管芯

[0046]

500:集成无源器件芯片

[0047]

520:包封体

[0048]

620:外部连接件

[0049]

d1:最短距离

[0050]

d2、d3:距离

[0051]

h1、h2、h3:高度

[0052]

w1:最大宽度

[0053]

w2:宽度

具体实施方式

[0054]

以下公开内容提供用于实施本发明的不同特征的许多不同的实施例或实例。以下阐述组件及排列的具体实例以简化本公开。当然,这些仅为实例而非旨在进行限制。举例来说,在以下说明中,在第二特征之上或第二特征上形成第一特征可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成有附加特征从而使得第一特征与第二特征可不直接接触的实施例。另外,本公开在各种实例中可重复使用参考编号和/或字母。此种重复使用是出于简洁及清晰的目的,且自身并不表示所论述的各个实施例和/或配置之间的关系。

[0055]

此外,为易于说明,本文中可能使用例如“在...之下”、“在...下方”、“下部的”、“在...上方”、“上部的”等空间相对性用语来阐述图中所示一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括器件在使用或操作中的不同取向。设备可具有其他取向(旋转90度或处于其他取向),且本文中所用的空间相对性描述语可同样相应地进行解释。

[0056]

本文中论述的实施例可在特定的上下文(即包括一个或多个集成电路管芯的封装组件)中进行论述。在一些实施例中,封装组件是集成衬底上系统(system-on-integrated-substrate,sois)封装。封装组件包括芯片,例如集成电压调节器(integrated voltage regulator,ivr),所述集成电压调节器设置在重布线结构与芯体衬底之间,与集成电路封装相对。在重布线结构与芯体衬底之间放置集成电压调节器能够使得集成电路封装与集成电压调节器之间的距离更短,此实现改善的电源完整性(power integrity)及更好的性能。

[0057]

图1示出根据一些实施例的经单体化封装组件100的剖视图。图2示出根据一些实施例的图1所示剖视图的区1000的详细视图。经单体化封装组件100包括半导体器件(例如,集成电路封装110),所述半导体器件通过多个导电连接件170耦合到具有一个或多个重布线层的重布线结构210。保护环(protective ring)160可耦合到重布线结构210且沿着集成电路封装110的外围延伸。保护环160的顶表面可与集成电路封装110的顶表面齐平。在一些实施例中,保护环160具有从保护环160的顶表面到重布线结构210的顶表面测量的高度h1,高度h1介于50μm到1500μm的范围内。在一些实施例中,经单体化封装组件100具有在相对的侧壁之间测量的最大宽度w1,最大宽度w1介于30mm到500mm的范围内。

[0058]

芯体衬底(core substrate)300通过多个导电连接件390在与集成电路封装110相对的侧上耦合到重布线结构210。多个外部连接件620在芯体衬底300的与重布线结构210相

对的侧上提供通往芯体衬底300的电连接。

[0059]

在重布线结构210与芯体衬底300之间设置有集成电压调节器(ivr)200。集成电压调节器200可向集成电路封装110供应电力及调节电力。与集成电路封装110相对地将集成电压调节器200贴合到重布线结构210可在集成电压调节器200与集成电路封装110之间提供最短距离d1(最短距离d1介于0.1mm到1.0mm的范围内,例如介于0.1mm到0.3mm的范围内),此对于提供具有减轻的电压降及功率降(voltage and power drop)的更高效的电压域(voltage domain)为有用的,此可改善集成电路封装110的电源完整性。经改善的电源完整性可能够提高工作频率(operation frequency)及降低电源电压,以满足高性能计算(high performance computing,hpc)要求。通过在重布线结构210与芯体衬底300之间封装集成电压调节器200,可形成提供更高的sois良率的紧凑的系统(compact system),所述紧凑的系统可利用现有的硅制作工具及工艺进行制作。

[0060]

最短距离d1介于0.1mm到1.0mm的范围内可提供上述优点,例如改善集成电路封装110的电源完整性。最短距离d1小于0.05mm可能是不利的,因为它可能导致对集成电路封装110不利的热影响。最短距离d1大于1.0mm可能是不利的,因为它可能导致集成电路封装110中的电压降及功率降,此可能降低器件性能。

[0061]

集成电路封装110可包括多个集成电路管芯(integrated circuit die),例如逻辑管芯(例如,中央处理器(central processing unit,cpu)、图形处理单元(graphic processing unit,gpu)、系统芯片(system-on-a-chip,soc)、应用处理器(application processor,ap)、微控制器等)、存储器管芯(例如,动态随机存取存储器(dynamic random access memory,dram)管芯、静态随机存取存储器(static random access memory,sram)管芯等)、功率管理管芯(例如,功率管理集成电路(power management integrated circuit,pmic)管芯)、射频(radio frequency,rf)管芯、传感器管芯(sensor die)、微机电系统(micro-electro-mechanical-system,mems)管芯、信号处理管芯(例如,数字信号处理(digital signal processing,dsp)管芯)、前端管芯(例如,模拟前端(analog front-end,afe)管芯)、输入/输出(input/output,i/o)管芯、类似管芯、或其组合。如图所示,出于例示目的,集成电路封装110包括逻辑管芯112(例如,soc)及两个i/o管芯114。所述集成电路管芯可形成在一个或多个晶片中,所述一个或多个晶片可包括在后续步骤中被单体化的不同器件区。所述集成电路管芯可使用例如集成扇出型(integrated fan-out,info)封装等制造技术与其他类似或不同的集成电路管芯封装在一起。集成电路封装110可包括:重布线结构116,在例如逻辑管芯112与i/o管芯114之间提供电路径及电连接,以及提供从集成电路封装110到导电连接件170的连接。

[0062]

导电连接件170在重布线结构210与集成电路封装110之间提供电连接。可包括底部填充胶(underfill)195,以将集成电路封装110牢固地接合到重布线结构210且提供结构支撑及环境保护。

[0063]

如以下所更详细地论述,重布线结构210通过导电连接件170及导电连接件390在集成电路封装110与芯体衬底300之间提供电路径及电连接。在一些实施例中,重布线结构210具有一个或多个重布线层,所述一个或多个重布线层包括多个金属化图案以及多个介电层,所述金属化图案包括例如多个导电线及多个导通孔,所述介电层将相邻层的导电线隔开,如以下例如关于图4到图5所论述的。金属化图案的导电线可使用导通孔与上覆的导

电特征或下伏的导电特征内连。

[0064]

重布线结构210电贴合及机械贴合到芯体衬底300。芯体衬底300可包括:芯体(core)310、具有延伸穿过芯体310的多个导通孔320、以及附加可选的多个重布线结构340(沿着芯体310的相对的侧)。在一些实施例中,芯体310在中心芯体的顶表面与底表面之间具有介于30μm到2000μm的范围内的厚度。一般来说,芯体衬底300为封装组件提供结构支撑,并在集成电路封装110与外部连接件620之间提供电信号路由(electrical signal routing),外部连接件620可实体耦合和电耦合到下部的重布线结构340的底表面上的凸块下金属(under-bump metallurgy,ubm)330。

[0065]

在重布线结构210与芯体衬底300之间可包括包封体520,以牢固地接合相关联的元件并提供结构支撑及环境保护。包封体520可由例如模制化合物、模制底部填充胶、环氧树脂、树脂、或类似物等有机材料形成或包含所述有机材料。

[0066]

如在图2中所更详细地示出,集成电压调节器200在芯体衬底300上方贴合到重布线结构210的下侧。集成电压调节器200可具有介于20μm到100μm的范围内的高度h2。集成电压调节器200的与重布线结构210相对的侧可具有介于500μm2到20000μm2的范围内的表面积。在一些实施例中,集成电压调节器200贴合到延伸穿过介电层220以接触重布线结构210的重布线层209f的多个通孔212,且芯体衬底300的凸块下金属330a上的多个导电连接件390耦合到通孔212上的多个凸块下金属(ubm)214。在其他实施例中,不存在通孔212及介电层220,且集成电压调节器200及导电连接件390实体耦合及电耦合到重布线结构210的重布线层209f的多个导电特征。

[0067]

集成电压调节器200可通过位于集成电压调节器200的顶表面上的多个导电连接件202耦合到通孔212。导电连接件202可通过多个焊料区204(例如,如微凸块)耦合到通孔212。然而,可使用任何合适的导电连接件来将集成电压调节器200与通孔212或重布线结构210的导电特征耦合。在一些实施例中,导电连接件202及焊料区204具有介于10μm到25μm的范围内的高度h3。可围着导电连接件202及焊料区204在介电层220之上设置底部填充胶206。底部填充胶206可通过毛细流动工艺或另一种合适的沉积方法在集成电压调节器200与介电层220之间环绕导电连接件202及焊料区而形成。底部填充胶206可减少导电连接件202上的应力。底部填充胶206的材料可为液态环氧树脂、可变形凝胶(deformable gel)、硅橡胶(silicon rubber)、其组合。

[0068]

集成电压调节器200可设置在芯体衬底300的顶表面中(例如,如在芯体衬底300的重布线结构340a的顶表面之上的阻焊剂350a中)的开口360中。可形成穿过阻焊剂350a(参见下文,图12)的开口360,以提供用于将集成电压调节器200装配在重布线结构210与芯体衬底300之间的空间。集成电压调节器200的此种位置可提供具有减轻的电压降及功率降的更高效的电压域,此可改善后续贴合的集成电路封装110(参见下文,图18)的电源完整性。开口360可由集成电压调节器200及包封体520填充。开口360可分别在阻焊剂350a与集成电压调节器200的相对的侧壁之间具有宽度w2(宽度w2介于5μm到200μm的范围内),此对于提供用于将集成电压调节器200装配在重布线结构210与芯体衬底300之间的空间,从而改善集成电路封装110的电源完整性是为有用的。宽度w2小于5μm可能是不利的,因无提供足够的空间来装配集成电压调节器200。宽度w2大于200μm可能是不利的,因为它可能导致耦合重布线结构210与芯体衬底300的导电连接件390更少,此可能降低器件性能。

[0069]

在芯体衬底300的重布线结构340a与介电层220的相对的表面之间测量的距离d2介于147μm到500μm的范围内,此对于提供用于将集成电压调节器200装配在重布线结构210与芯体衬底300之间的空间,从而改善集成电路封装110的电源完整性是为有用的。小于147μm的距离d2可能可能是不利的,因无提供足够的空间来装配集成电压调节器200。大于500μm的距离d2可能是不利的,因为它可能导致重布线结构210与芯体衬底300之间的连接变差(其在导电连接件390中具有更高的电阻),此可能降低器件性能。

[0070]

图3到图15、图18及图19示出根据一些实施例的用于形成经单体化封装组件100的工艺期间的中间步骤的剖视图。示出第一封装区(又称封装区)101a及第二封装区(又称封装区)101b,且对多个集成电压调节器200中的一或多者进行封装以在封装区101a及101b中的每一者中形成封装组件。为易于例示,已在图3到图19中简化各个特征的例示。

[0071]

在图3中,提供载体衬底102。载体衬底102可包含例如硅系材料(例如硅衬底(例如,硅晶片)、玻璃材料、氧化硅)、或其它材料(例如氧化铝、类似物,或组合)。在一些实施例中,载体衬底102可为面板结构(panel structure),所述面板结构可为例如由合适的介电材料(例如玻璃材料或有机材料)形成的支撑衬底,且所述面板结构可具有矩形形状。载体衬底102可为平坦的,以便适应附加特征(例如绝缘层103)的形成。

[0072]

在一些实施例中,可在载体衬底102的顶表面上形成释放层(未示出),以有利于载体衬底102的后续剥离。释放层可由聚合物系材料形成,释放层可与载体衬底102一起从将在后续步骤中形成的上覆结构被移除。在一些实施例中,释放层是在受热时会失去其粘合性质的环氧树脂系热释放材料,例如光-热转换(light-to-heat-conversion,lthc)释放涂层。在其他实施例中,释放层可为在暴露于紫外(ultra-violet,uv)光时会失去其粘合性质的紫外(uv)胶。释放层可作为液体进行分配并被固化,可为被层压(laminated)到载体衬底102上的层压膜、或者类似物。释放层的顶表面可被整平(leveled)且可具有高度的共面性(co-planarity)。

[0073]

图4及图5示出在载体衬底102上形成重布线结构210。图4示出重布线结构210的绝缘层103及重布线层104的形成,且图5示出重布线结构210的多个绝缘层208a到208f及多个重布线层209a到209f的形成。

[0074]

在图4中,可在载体衬底102之上形成绝缘层103。绝缘层103的底表面可与释放层(未示出)的顶表面接触。在一些实施例中,绝缘层103由聚合物(例如聚苯并恶唑(polybenzoxazole,pbo)、聚酰亚胺(polyimide,pi)、苯并环丁烯(benzocyclobutene,bcb)、或类似物)形成。在其他实施例中,绝缘层103由以下材料形成:氮化物,例如氮化硅;氧化物,例如氧化硅、磷硅酸盐玻璃(phosphosilicate glass,psg)、硼硅酸盐玻璃(borosilicate glass,bsg)、掺杂硼的磷硅酸盐玻璃(boron-doped phosphosilicate glass,bpsg)或类似物;或者类似材料。绝缘层103可通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)、层压、类似工艺、或其组合等任何可接受的沉积工艺来形成。在一些实施例中,绝缘层103具有介于5μm到50μm的范围内的厚度,但可使用任何合适的厚度。

[0075]

在图4中,可通过使用例如物理气相沉积(physical vapor deposition,pvd)、cvd、溅镀、或类似工艺等合适的形成工艺初始地形成钛、铜或钛铜合金的一个或多个层的晶种层(未示出)来形成重布线层104。在一些实施例中,重布线层104包括多个接触焊盘

104a及多个导电线104b,接触焊盘104a可为后续形成的多个连接件(参见下文,图15)的着落位置。在载体衬底102或绝缘层103(如果存在的话)之上形成晶种层。然后可形成光刻胶(同样未示出)以覆盖晶种层,且然后将光刻胶图案化以暴露出晶种层的位于随后将形成重布线层104的地方的那些部分。一旦已形成光刻胶且将光刻胶图案化,便可在晶种层上形成导电材料。导电材料可为例如铜、钛、钨、铝、另一种金属、类似物、或其组合等材料。导电材料可通过例如电镀(electroplating)或化学镀(electroless plating)等沉积工艺或者类似工艺来形成。然而,尽管所论述的材料及方法适合于形成导电材料,但这些仅仅是实例。可替代地使用任何其他合适的材料或任何其他合适的形成工艺(例如cvd或pvd)来形成重布线层104。一旦已形成导电材料,便可通过合适的移除工艺(例如灰化或化学剥除)来移除光刻胶。另外,在移除光刻胶之后,可通过例如合适的湿式刻蚀工艺或干式刻蚀工艺来移除晶种层的被光刻胶覆盖的那些部分,所述湿式刻蚀工艺或干式刻蚀工艺可使用导电材料作为刻蚀掩模。晶种层的剩余部分及导电材料的剩余部分形成重布线层104。在一些实施例中,重布线层104的导电材料具有介于2μm到50μm的范围内的厚度,但可使用任何合适的厚度。

[0076]

接下来,在图5中,根据一些实施例,在重布线层104、绝缘层103及载体衬底102之上形成重布线结构210的附加层。所示重布线结构210包括绝缘层103、重布线层104、绝缘层208a到208f(为清晰起见,仅标记出绝缘层208a及208f)且包括重布线层209a到209f(为清晰起见,仅标记出重布线层209a及209f)。在其他实施例中,可在重布线结构210中形成与本文所述不同数目的绝缘层或重布线层。在一些实施例中,重布线结构210可以与本文所述不同的工艺来形成。在一些实施例中,重布线结构210可为例如扇出型结构。

[0077]

仍然参照图5,在重布线层104及绝缘层103之上形成绝缘层208a。绝缘层208a可由例如以下等一种或多种合适的介电材料制成:氧化物(例如,氧化硅)、氮化物(例如,氮化硅)、聚合物材料(例如,感光性聚合物材料)、聚酰亚胺材料、低介电常数(low dielectric constant,low-k)介电材料、另一种介电材料、类似介电材料、或其组合。绝缘层208a可通过例如旋转涂布、层压、cvd、类似工艺、或其组合等工艺来形成。在一些实施例中,绝缘层208a具有介于5μm到50μm的范围内的厚度,但可使用任何合适的厚度。可使用合适的光刻掩模及刻蚀工艺来形成绝缘层208a中的多个开口。举例来说,可在绝缘层208a之上形成光刻胶且将光刻胶图案化,并且利用一种或多种刻蚀工艺(例如,湿式刻蚀工艺或干式刻蚀工艺)来移除绝缘层208a的多个部分。在一些实施例中,绝缘层208a由感光性聚合物(例如pbo、聚酰亚胺、bcb、或类似物)形成,其中可使用光刻掩模及刻蚀工艺直接图案化出多个开口。绝缘层208a中的开口可暴露出重布线层104。

[0078]

然后可形成重布线层209a,以在重布线结构210内提供附加布线以及电连接。在实施例中,可使用类似于重布线层104的材料及工艺来形成重布线层209a。举例来说,可形成晶种层,在晶种层的顶部上放置光刻胶且按照重布线层209a所期望的图案将光刻胶图案化。然后可使用例如镀覆工艺在光刻胶的经图案化的多个开口中形成导电材料(例如,铜、钛、或类似物)。然后可移除光刻胶且刻蚀晶种层,从而形成重布线层209a。以这种方式,重布线层209a可形成通往重布线层104的电连接。在一些实施例中,重布线层209a的导电材料具有介于2μm到50μm的范围内的厚度,但可使用任何合适的厚度。

[0079]

然后,可在重布线层209a及绝缘层208a之上形成附加的绝缘层208b到绝缘层208f

及重布线层209b到重布线层209f,以在重布线结构210内提供附加布线以及电连接。绝缘层208b到绝缘层208f与重布线层209b到重布线层209f以交替层的形式形成,且可使用与用于绝缘层208a或重布线层209a的工艺及材料类似的工艺及材料来形成。举例来说,可在重布线层(例如,重布线层209a)之上形成绝缘层(例如,绝缘层208b),且然后使用合适的光刻掩模及刻蚀工艺穿过绝缘层形成多个开口以暴露出下伏的重布线层的多个部分。可在绝缘层之上形成晶种层且在晶种层的多个部分上形成导电材料,从而形成上覆的重布线层(例如,重布线层209b)。可重复这些步骤以形成具有合适数目及配置的绝缘层及重布线层的重布线结构210。作为另外一种选择,绝缘层208b到绝缘层208f或重布线层209b到重布线层209f可与绝缘层208a或重布线层209a不同地形成。绝缘层208b到绝缘层208f可被形成为各自具有介于5μm到50μm的范围内的厚度,但可使用任何合适的厚度。以这种方式,可形成电连接到重布线层104的重布线结构210。在一些实施例中,重布线结构210是扇出型结构。在其他实施例中,重布线结构210可以不同于本文所述的工艺来形成。

[0080]

接下来,在图6中,在重布线层209f的多个导电特征上形成多个通孔212。通孔212可穿过后续形成的介电层220(参见下文,图7)为后续贴合的集成电压调节器200(参见下文,图10a到图10b)与芯体衬底300(参见下文,图13)提供电连接。作为形成通孔212的实例,在绝缘层208f及重布线层209f上形成光刻胶且将光刻胶图案化。光刻胶可通过旋转涂布或类似工艺来形成且可暴露于光以进行图案化。光刻胶的图案对应于导通孔。所述图案化形成穿过光刻胶的多个开口以暴露出晶种层。在光刻胶的开口中及重布线层209f的被暴露出的部分上形成导电材料,从而形成通孔212。导电材料可通过镀覆(例如电镀或化学镀)或类似工艺来形成。导电材料可包括金属,如铜、钛、钨、铝、或类似物。例如通过例如使用氧等离子体或类似物进行的可接受的灰化或剥除工艺来移除光刻胶。

[0081]

在图7中,在重布线结构210及通孔212之上形成介电层220。介电层220对于提供上面随后会贴合集成电压调节器200(参见下文,图10a到图10b)的表面可为有用的。在一些实施例中,介电层220由聚合物(例如聚苯并恶唑(pbo)、聚酰亚胺、苯并环丁烯(bcb)、或类似物)形成。在其他实施例中,介电层220由以下材料形成:氮化物,例如氮化硅;氧化物,例如氧化硅、磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、掺杂硼的磷硅酸盐玻璃(bpsg)或类似物;或者类似材料。介电层220可通过例如层压、旋转涂布、cvd、类似工艺、或其组合等任何可接受的沉积工艺来形成。

[0082]

在图8中,实行例如研磨或化学机械抛光(chemical-mechanical polish,cmp)等平坦化以通过移除介电层220的顶部部分来暴露出通孔212的顶表面。暴露出通孔212的顶表面使得后续形成的凸块下金属214(参见下文,图9)及后续贴合的集成电压调节器200能够实体耦合及电耦合到通孔212。

[0083]

接下来,在图9中,在介电层220上形成多个凸块下金属214,且将凸块下金属214实体耦合及电耦合到通孔212中的一些通孔212。凸块下金属214可为后续形成的导电连接件390提供着落位置,以将重布线结构210与芯体衬底300(参见下文,图13)耦合。凸块下金属214可由与通孔212相同的材料形成。

[0084]

在图10a及图10b中,将多个集成电压调节器200贴合到重布线结构210上的介电层220且将集成电压调节器200耦合到未被凸块下金属214覆盖的通孔212。图10b示出图10a所示区1002的详细视图。在一些实施例中,可使用拾取及放置工艺或另一种合适的工艺将集

成电压调节器200放置在介电层220上,且通过倒装芯片接合工艺或其他合适的接合工艺将焊料区204接合到通孔212的顶表面。通过将导电连接件202直接接合到通孔212,可在重布线结构210及后续贴合的芯体衬底300(参见下文,图13)之间为集成电压调节器200提供更多的空间。

[0085]

可在介电层220的表面上在导电连接件202及焊料区204周围设置底部填充胶206。底部填充胶206可通过毛细流动工艺或另一种合适的沉积方法在集成电压调节器200与介电层220之间环绕导电连接件202而形成。底部填充胶206可减少导电连接件202及焊料区204上的应力。底部填充胶206的材料可为液态环氧树脂、可变形凝胶、硅橡胶、其组合。

[0086]

在一些实施例中,可省略通孔212及介电层220的形成。然后,可将集成电压调节器200直接实体耦合及电耦合到重布线层209f的导电特征。可在重布线层209f的其他导电特征上形成后续形成的导电连接件390(参见下文,图13)。

[0087]

图11示出芯体衬底300,随后将芯体衬底300接合到重布线结构210(参见下文,图13)。利用芯体衬底300,具有芯体衬底300在分开的工艺中制造的优点。另外,由于芯体衬底300是在分开的工艺中形成,因此可分开对芯体衬底300进行测试,从而使用已知良好的芯体衬底300。举例来说,在一些实施例中,在将芯体衬底300接合到重布线结构210之前,可单独地或批量地对芯体衬底300进行测试、确认和/或验证。

[0088]

芯体衬底300可为例如有机衬底、陶瓷衬底、硅衬底或类似衬底。使用后续形成的导电连接件390(参见图12)将芯体衬底300贴合到重布线结构210。对芯体衬底300进行贴合可包括:将芯体衬底300放置在重布线结构210上,且对导电连接件390进行回焊(reflow)以将芯体衬底300与重布线结构210实体耦合及电耦合。

[0089]

在贴合到重布线结构210之前,可根据适用的制造工艺对芯体衬底300进行处理,以在芯体衬底300中形成重布线结构。举例来说,芯体衬底300包括芯体310。芯体310可由以下材料的一个或多个层形成:玻璃纤维、树脂、填料、预浸料、环氧树脂、二氧化硅填料、味之素构成膜(ajinomoto build-up film,abf)、聚酰亚胺、模制化合物、其它材料、和/或其组合。举例来说,在一些实施例中,两层材料构成芯体310。芯体310可由有机材料和/或无机材料形成。在一些实施例中,芯体310包括嵌置在内部的一个或多个无源组件(未示出)。芯体310可包含其他材料或组件。形成延伸穿过芯体310的多个导通孔320。在一些实施例中,导通孔320包含导电材料320a,例如铜、铜合金或其他导体,且可包括阻挡层(未示出)、衬垫(未示出)、晶种层(未示出)、和/或填充材料320b。导通孔320提供从芯体310的一个侧到芯体310的另一侧的垂直电连接。举例来说,导通孔320中的一些导通孔320耦合在位于芯体310的一个侧处的导电特征与位于芯体310的相对的侧处的导电特征之间。作为实例,可使用钻孔工艺、光刻、激光工艺或其他方法来形成导通孔320的多个孔洞,且然后利用导电材料填充或镀覆导通孔320的孔洞。在一些实施例中,导通孔320是中空导电穿孔(hollow conductive through via),所述中空导电穿孔具有填充有绝缘材料的中心。在芯体310的相对的侧上形成重布线结构340a与重布线结构340b。重布线结构340a与重布线结构340b通过导通孔320电耦合,导通孔320可承载扇入/扇出型电信号。

[0090]

重布线结构340a及重布线结构340b各自包括由abf、预浸料、或类似物形成的多个介电层以及多个金属化图案。每一相应的金属化图案具有位于相应的介电层的主表面上且沿着所述主表面延伸的多个线部分,且具有延伸穿过相应的介电层的多个通孔部分。在一

些实施例中,相应的介电层具有介于5μm到50μm的范围内的厚度,且相应的金属化图案具有介于2μm到50μm的范围内的厚度,但可使用任何合适的厚度。重布线结构340a及重布线结构340b各自分别包括:多个凸块下金属(ubm)330a及多个凸块下金属330b,用于外部连接;以及阻焊剂350a及阻焊剂350b,用于保护重布线结构340a及重布线结构340b的多个特征。重布线结构340a随后可通过凸块下金属330a利用导电连接件390贴合到重布线结构210,如以下图13中所示。与图11中所示相比,在重布线结构340a及重布线结构340b中可形成更多或更少的介电层及金属化图案。

[0091]

芯体衬底300可包括有源器件及无源器件(未示出),或者可不具有有源器件、无源器件中的任一者或两者。可使用各种各样的器件,例如晶体管、电容器、电阻器、电感器、这些器件组合、及类似物。可使用任何合适的方法来形成器件。

[0092]

阻焊层350a可包括直接形成在重布线结构340a的不存在凸块下金属330a的区域之上的区352。随后可移除这些区352以形成开口360(参见下文,图12),以在将芯体衬底300贴合到重布线结构210时容纳集成电压调节器200。

[0093]

在图12中,移除阻焊剂350a的区352以形成开口360,且在凸块下金属330a上形成多个导电连接件390。在一些实施例中,阻焊剂350a包括可光可图案化的绝缘材料(例如聚苯并恶唑(pbo)、聚酰亚胺(pi)、苯并环丁烯(bcb)、或类似物)的一个或多个层,且可使用旋转涂布工艺或类似工艺来形成。此种可光可图案化的绝缘材料可使用与光刻胶材料类似的光刻方法进行图案化,以移除区352且形成开口360。然而,可使用任何合适的方法来形成开口360。在一些实施例中,导电材料(例如,如凸块下金属330的铜)的一部分存在于区352中且也通过合适的工艺(例如刻蚀)来移除。

[0094]

可使用导电连接件390将芯体衬底300a及芯体衬底300b接合到重布线结构210,如以下图13中所示。可首先在芯体衬底300a及芯体衬底300b中的任一者上,或者在重布线结构210(参见上文,图9)的凸块下金属214上形成导电连接件390,且然后对导电连接件390进行回焊以完成接合。举例来说,在图12中所示的实施例中,以介于100μm到1500μm的范围内的节距在顶部的重布线结构(如重布线结构340a)的凸块下金属330a上形成多个导电连接件390。导电连接件390可为球栅阵列(ball grid array,bga)连接件、焊料球、金属柱、受控塌陷芯片连接(controlled collapse chip connection,c4)凸块、微凸块、无电镀镍钯浸金技术(electroless nickel-electroless palladium-immersion gold technique,enepig)形成的凸块、或类似物。导电连接件390可包含例如焊料、铜、铝、金、镍、银、钯、锡、类似材料、或其组合等导电材料。此种导电连接件390的集成可为半导体器件(例如集成无源器件(integrated passive device,ipd)芯片、集成电压调节器(ivr)、有源芯片以及其他电子组件)的放置提供灵活性,以实施系统芯片类型的封装组件,因此降低制作复杂性。此种实施例同样也可为各种其他封装配置提供更大的灵活性。

[0095]

在一些实施例中,导电连接件390通过利用蒸镀、电镀、印刷、焊料转移、植球、或类似工艺初始地形成焊料层来形成。一旦已在结构上形成焊料层,便可实行回焊,以便将材料成形为期望的凸块形状。在另一实施例中,导电连接件390包括通过溅镀、印刷、电镀、化学镀、cvd或类似工艺形成的金属柱(例如铜柱)。金属柱可不含有焊料且具有实质上垂直的侧壁。在一些实施例中,在金属柱的顶部上形成金属顶盖层。金属顶盖层可包含镍、锡、锡-铅、金、银、钯、铟、镍-钯-金、镍-金、类似物、或其组合,且可通过镀覆工艺来形成。

[0096]

在图13中,分别在第一封装区101a及第二封装区101b中将芯体衬底300a及芯体衬底300b接合到重布线结构210(参见上文,图10a),且在各种组件上及周围形成包封体520。在一些实施例中,可使用拾取及放置工艺或另一种合适的工艺将芯体衬底300a及芯体衬底300b放置在重布线结构210上,且导电连接件390通过倒装芯片接合工艺或其他合适的接合工艺进行接合。在一些实施例中,对导电连接件390进行回焊,以通过凸块下金属214将芯体衬底300a及芯体衬底300b贴合到重布线结构210。导电连接件390通过重布线结构210将芯体衬底300a及芯体衬底300b电耦合和/或实体耦合到后续贴合的集成电路封装110(参见下文,图18)。导电连接件390在回焊之前可具有形成在其上的环氧焊剂(未示出),在将芯体衬底300a及芯体衬底300b贴合到重布线结构210之后,环氧焊剂的环氧部分中的至少一些保留下来。

[0097]

可将集成电压调节器200装配到芯体衬底300a及芯体衬底300b中的开口360中,以便装配在重布线结构210与芯体衬底300a及芯体衬底300b之间,从而改善后续贴合的集成电路封装110(参见下文,图18)的电源完整性。

[0098]

仍然参照图13,通过在各种组件上及周围形成包封体520来实行包封。在所述形成之后,包封体520环绕芯体衬底300a及芯体衬底300b,包括环绕导电连接件390、集成电压调节器200、及介电层220的上部暴露表面。包封体520可由模制化合物、环氧树脂、底部填充胶、模制底部填充胶、类似物、或其组合来形成或包含模制化合物、环氧树脂、底部填充胶、模制底部填充胶、类似物、或其组合,且可通过压缩模制、转移模制或类似工艺来施加。可以液体或半液体形式施加包封体520,且然后随后将包封体520固化。包封体520可形成在各种组件之上,从而使得芯体衬底300a及芯体衬底300b被掩埋或覆盖。集成电压调节器200的侧壁及集成电压调节器200的与重布线结构210相对的底表面可被包封体520覆盖。

[0099]

进一步参照图13,如果需要,可对包封体520实行执行平坦化工艺,以暴露出芯体衬底300a及芯体衬底300b的凸块下金属330b。在工艺变化内在平坦化工艺之后,包封体520的最顶部表面与凸块下金属330b的最顶部表面为平整的(例如,平坦的)。平面化工艺可为例如化学机械抛光(cmp)、研磨工艺、或类似工艺。在一些实施例中,例如如果凸块下金属330b已被暴露出,则可省略平坦化。可使用其他工艺来实现类似的结果。举例来说,在形成包封体520之前,可在凸块下金属330b之上形成电介质或钝化层(dielectric or passivation layer)。在这种情况下,可在后续步骤中将电介质或钝化层图案化,以暴露出凸块下金属330b的部分。

[0100]

在图14中,实行载体衬底剥离,以将载体衬底102从包括芯体衬底300a及300b以及重布线结构210以及其他结构的先前阐述步骤的所得积层分离(或“剥离”)。根据一些实施例,所述剥离包括将例如激光或uv光等光投射在载体衬底102(参见上文,图3)的释放层上,从而使得释放层在光的热量下分解,且可移除载体衬底102。然后将所述结构翻转并放置在另一载体衬底802及释放层(未示出)上。

[0101]

仍然参照图14,在重布线结构210的绝缘层103中形成暴露出接触焊盘104a的多个开口240。开口240可通过刻蚀、例如激光钻孔、机械钻孔等钻孔工艺、或类似工艺来形成。图案化形成暴露出接触焊盘104a的开口240。可通过可接受的工艺进行图案化,例如当绝缘层103是感光性材料时,通过将绝缘层103暴露于光及显影来进行图案化,或者当使用例如氧化硅、氮化硅或类似物等非感光性材料时,通过使用例如各向异性刻蚀进行刻蚀来进行图

案化。

[0102]

可使用多个导电连接件170将重布线结构210接合到集成电路封装110(参见下文,图18),且可首先在集成电路封装110或重布线结构210中的任一者上形成导电连接件170,且然后对导电连接件170进行回焊以完成接合。举例来说,在图15中所示的实施例中,首先在开口240(参见上文,图14)中形成耦合到被暴露出的接触焊盘104a的导电连接件170。导电连接件170可为球栅阵列(bga)连接件、焊料球(如图所示)、金属柱、受控塌陷芯片连接(c4)凸块、微凸块、无电镀镍钯浸金技术(enepig)形成的凸块、或类似物。导电连接件170可包含例如焊料、铜、铝、金、镍、银、钯、锡、类似材料、或其组合等导电材料。在一些实施例中,导电连接件170通过利用蒸镀、电镀、印刷、焊料转移、植球、或类似工艺初始地形成焊料层来形成。一旦已在结构上形成焊料层,便可实行回焊,以便将材料成形为期望的凸块形状。在另一实施例中,导电连接件170包括通过溅镀、印刷、电镀、化学镀、cvd或类似工艺形成的金属柱(例如铜柱)。金属柱可不含有焊料且具有实质上垂直的侧壁。在一些实施例中,在金属柱的顶部上形成金属顶盖层。金属顶盖层可包含镍、锡、锡-铅、金、银、钯、铟、镍-钯-金、镍-金、类似物、或其组合,且可通过镀覆工艺来形成。

[0103]

如上所述,重布线结构210可更大且包括多个封装区,例如第一封装区101a及第二封装区101b。举例来说,图16示出如以上图15中所示的重布线结构210,其包括具有多个封装区的圆形形状的晶片。在所示实施例中,晶片上包括四个封装区101a、101b、101c及101d,从而使得能够在单个晶片上制作四个最终封装组件且稍后将所述四个最终封装组件单体化。在其他实施例中,可在单个晶片上利用更少或更多的封装区。工艺中的后续步骤使用载体衬底802上的重布线结构210作为基础,在此基础上继续以下所进一步详细阐述的制作工艺。如以下所进一步详细阐述,通过沿着线401且围着封装区101a、101b、101c及101d的外边缘进行锯切来将各个封装区单体化。

[0104]

图17示出使用具有多个封装区的面板形式(panel form)制作工艺进行重布线结构210的制造。在所示实施例中,在晶片上包括九个封装区101a到101i,从而使得能够在单个晶片或面板上制作九个最终封装组件。在其他实施例中,可在单个晶片或面板上利用更少或更多的封装区。工艺中的后续步骤使用载体衬底802上的重布线结构210作为基础,在此基础上继续以下所进一步详细阐述的制作工艺。如以下所进一步详细阐述,通过沿着线402且围着封装区101a到101i的周边进行锯切来将各个封装区单体化。

[0105]

在图18中,通过沿着切割道区(例如,在第一封装区101a与第二封装区101b之间)进行锯切来实行单体化工艺,且将集成电路封装110贴合到重布线结构210。所述锯切将第一封装区101a从相邻的封装区单体化出来,以形成多个经单体化封装组件100。如以上在图15中所示,利用包封体520覆盖芯体衬底300a及芯体衬底300b的侧壁,由此在单体化期间及之后保护芯体衬底300a及芯体衬底300b的侧壁。包封体520在芯体衬底300的侧壁上可具有介于0μm到300μm的范围内的厚度。

[0106]

仍然参照图18,可通过导电连接件170将集成电路封装110贴合到重布线结构210。导电连接件170将集成电路封装110贴合到重布线结构210的接触焊盘104a。对集成电路封装110进行贴合可包括:将集成电路封装110放置在导电连接件170上,且对导电连接件170进行回焊以将集成电路封装110与重布线结构210实体耦合及电耦合。集成电路封装110可包括逻辑管芯112、用于与逻辑管芯112进行接口(interfacing)的一个或多个i/o管芯114

以及重布线结构116,重布线结构116在例如逻辑管芯112与i/o管芯114之间提供电路径及电连接,以及提供从集成电路封装110到导电连接件170的连接。集成电路封装110中包括的管芯的数目、类型及排列不受限制,且在不同的实施例中可利用其他替代的管芯及排列。通过重复上述步骤可包括多个集成电路封装,结合金属化特征,以提供通往所述多个集成电路封装的电连接。

[0107]

在一些实施例中,形成环绕导电连接件170及集成电路封装110的底部填充胶195。底部填充胶195可减少应力且保护由导电连接件170的回焊形成的多个接头(joint)。底部填充胶195可在集成电路封装110被贴合之后通过毛细流动工艺来形成,或者可通过合适的沉积方法来形成。在一些实施例中,在多个相邻器件之下形成底部填充胶195的单个层,并且可在放置在重布线结构210的顶部上的附加器件之下和/或周围形成又一些后续底部填充胶(未示出)。

[0108]

在图19中,在经单体化封装组件100的顶表面上安装保护环160,且在芯体衬底300的底表面上形成多个外部连接件620。将保护环160安装到经单体化封装组件100的顶部,保护环160围绕集成电路封装110。在一些实施例中,可添加保护环160以向经单体化封装组件100提供附加的刚性(rigidity)且保护所安装的集成电路封装110免受可能损坏集成电路封装110与重布线结构210之间的电连接或集成电路封装110本身的实体碰撞及撞击。

[0109]

进一步参照图19,在芯体衬底300的凸块下金属330b上形成外部连接件620。外部连接件620可为球栅阵列(bga)连接件、焊料球、金属柱、受控塌陷芯片连接(c4)凸块、微凸块、或类似物。外部连接件620可包含例如焊料、铜、铝、金、镍、银、钯、锡、类似材料、或其组合等导电材料。在一些实施例中,外部连接件620是通过利用蒸镀、电镀、印刷、焊料转移、植球、或类似工艺在凸块下金属330b上初始地形成可回焊材料层来形成。一旦已在凸块下金属330b上形成可回焊材料层,便可实行回焊,以将材料成形为期望的凸块形状。在一些实施例中,外部连接件620以介于100μm到1500μm的范围内的节距形成。

[0110]

图20示出根据一些实施例的经单体化封装组件400的剖视图。经单体化封装组件400可类似于以上参照图1及图19所述的经单体化封装组件100,其中相同的参考编号表示使用相同工艺形成的相同元件,但其中在重布线结构210与芯体衬底300之间设置集成无源器件(ipd)芯片500来取代集成电压调节器200。尽管示出两个ipd芯片500,但可在重布线结构210与芯体衬底300之间设置任何合适数目的ipd芯片500。在一些实施例中,ipd芯片500具有介于20μm到500μm的范围内的厚度,且ipd芯片500的底侧具有介于2mm2到30mm2的范围内的面积。在一些实施例中,经单体化封装组件100的通孔212及介电层220被省略,且ipd芯片500及导电连接件390直接实体耦合及电耦合到重布线结构210的底侧上的导电特征。

[0111]

经单体化封装组件400的重布线结构210与芯体衬底300可隔开介于20μm到600μm的范围内的距离d3,此可能因具有足够的空间来装配ipd芯片500而是有利的。小于20μm的距离d3可能因无提供足够的空间来装配ipd芯片500而是不利的。大于600μm的距离d3可能是不利的,因为它可能导致重布线结构210与芯体衬底300之间的连接变差(其中导电连接件390中具有更高的电阻),此可能降低器件性能。

[0112]

如图所示,出于例示目的,贴合到重布线结构210的顶表面的集成电路封装410包括cpu或gpu 412及两个存储器管芯414。在一些实施例中,如根据图20所示,经单体化封装组件400不包括保护环160(参见上文,图1)。在其他实施例中,保护环160贴合到重布线结构

210,如以上图1中所示。

[0113]

实施例可提供多个优点。可在sois封装中在重布线结构与芯体衬底之间设置例如集成电压调节器(ivr)或者集成无源器件(ipd)芯片等芯片。集成电压调节器可向重布线结构上的集成电路封装供应电力及调节电力。与集成电路封装相对地将集成电压调节器贴合到重布线结构,可在集成电压调节器与集成电路封装之间提供最短距离,此对于提供具有减轻的电压降及功率降的更高效的电压域可为有用的。此可改善集成电路封装的电源完整性且可能够提高工作频率及降低电源电压,以满足高性能计算(hpc)要求。通过在重布线结构与芯体衬底之间封装集成电压调节器,可形成紧凑的系统,由于利用现有的硅制作工具及工艺进行制作,因此所述系统可提供更高的sois良率。

[0114]

根据实施例,一种半导体组件包括:重布线结构;集成电路封装,贴合到所述重布线结构的第一侧;芯体衬底,利用第一导电连接件及第二导电连接件耦合到所述重布线结构的第二侧,所述第二侧与所述第一侧相对,所述芯体衬底的顶部层包含介电材料;以及芯片,设置在所述重布线结构与所述芯体衬底之间,所述芯片夹置在所述介电材料的侧壁之间。在实施例中,所述半导体组件还包括:介电层,位于所述重布线结构的所述第二侧上;以及第一通孔、第二通孔及第三通孔,延伸穿过所述介电层。在实施例中,所述芯片实体耦合及电耦合到所述第一通孔。在实施例中,所述半导体组件还包括:第一凸块下金属,位于所述介电层上,所述第一凸块下金属实体耦合及电耦合到所述第二通孔,所述第一导电连接件实体耦合及电耦合到所述第一凸块下金属;以及第二凸块下金属,位于所述介电层上,所述第二凸块下金属实体耦合及电耦合到所述第三通孔,所述第二导电连接件实体耦合及电耦合到所述第二凸块下金属。在实施例中,在所述芯体衬底与所述介电层的相对的表面之间测量的距离介于147μm到500μm的范围内。在实施例中,所述半导体组件还包括包封体,所述包封体覆盖所述芯体衬底的侧壁、所述芯片的侧壁、以及所述芯片的与所述重布线结构相对的底表面。在实施例中,所述芯片是内部电压调节器。在实施例中,所述芯片与所述集成电路封装之间的最短距离小于0.3mm。

[0115]

根据另一实施例,一种半导体组件包括:第一通孔及第二通孔,从重布线结构的第一侧延伸,凸块下金属与所述重布线结构相对地位于所述第二通孔上;电压调节器,实体耦合及电耦合到所述第一通孔;集成电路封装,通过所述重布线结构耦合到所述电压调节器,所述集成电路封装位于所述重布线结构的与所述第一侧相对的第二侧上;以及芯体衬底,利用导电连接件贴合到所述凸块下金属,所述芯体衬底上的介电材料夹置在所述导电连接件与所述电压调节器之间。在实施例中,所述半导体组件还包括底部填充胶,所述底部填充胶夹置在所述电压调节器与所述重布线结构之间。在实施例中,所述介电材料与所述电压调节器之间的宽度介于5μm到200μm的范围内。在实施例中,所述电压调节器具有介于20μm到100μm的范围内的高度。在实施例中,所述电压调节器的底侧具有介于500μm2到20000μm2的范围内的表面积。

[0116]

根据又一实施例,一种形成半导体组件的方法包括:在第一衬底上形成重布线结构;将芯片贴合到所述重布线结构的第一侧;在芯体衬底中形成开口;将所述芯体衬底贴合到所述重布线结构的所述第一侧,所述芯片夹置在所述开口的侧壁之间;利用包封体包封所述芯体衬底,其中所述包封体沿着所述芯体衬底的侧壁延伸,其中所述包封体进一步包封所述芯片;从所述第一衬底移除所述重布线结构;以及将集成电路封装贴合到所述重布

线结构的第二侧,所述第二侧与所述第一侧相对。在实施例中,所述方法还包括:在所述重布线结构上形成第一通孔及第二通孔;在所述重布线结构之上形成介电层,所述介电层覆盖所述第一通孔及所述第二通孔;以及将所述介电层平坦化以暴露出所述第一通孔的顶表面及所述第二通孔的顶表面。在实施例中,将所述芯片贴合到所述重布线结构的所述第一侧包括:将所述芯片上的第一导电连接件实体耦合及电耦合到所述第一通孔。在实施例中,所述方法还包括:在所述芯片与所述介电层之间形成底部填充胶。在实施例中,所述方法还包括:在所述介电层上形成凸块下金属,所述凸块下金属实体耦合及电耦合到所述第二通孔。在实施例中,将所述芯体衬底贴合到所述重布线结构的所述第一侧包括:在所述凸块下金属与所述芯体衬底之间耦合第二导电连接件。在实施例中,所述方法还包括:在所述重布线结构上安装保护环,所述保护环围绕所述集成电路封装。

[0117]

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下在本文中作出各种改变、代替及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1