基于超结结构的高压逆阻型功率半导体器件及制备方法与流程

1.本发明涉及一种功率半导体器件及制备方法,尤其是一种基于超结结构的高压逆阻型功率半导体器件及制备方法。

背景技术:

2.现有的igbt(insulated gate bipolar transistor)器件,为了实现通态压降和关断损耗之间良好的折中关系,一般地,在集电极附近都会设置一个高掺杂的fs层,fs层的存在用来调制背面p+区的注入效率,由于高掺杂fs层的存在,在反向耐压时,元胞背面是不能够耐压的,因此,双向耐压的igbt多采用在漂移区内设置一相当厚的npt(no punch through)结构,由于较厚的npt结构存在,igbt器件的通态压降会很大,静态损耗会很高,尤其是对于有更高耐压需求的igbt器件,漂移区厚度相应增加,而高损耗的原因导致器件无法向高压方向发展。

技术实现要素:

3.本发明的目的是克服现有技术中存在的不足,提供一种基于超结结构的高压逆阻型功率半导体器件及制备方法,其在有效实现高耐压的同时,又能降低通态压降,并且可以实现双向耐压,与现有工艺兼容,安全可靠。

4.按照本发明提供的技术方案,所述基于超结结构的高压逆阻型功率半导体器件,包括具有第一导电类型的半导体基板、制备于所述半导体基板中心区的元胞区以及制备于所述半导体基板背面的背面电极结构;所述半导体基板包括第一导电类型衬底、设置于第一导电类型衬底正面上的第一导电类型漂移区以及外延设置于第一导电类型漂移区上的第一导电类型外延层;

5.在所述第一导电类型漂移区内设置超结结构,超结结构内的第一导电类型柱以及第二导电类型柱相应的高度均小于第一导电类型漂移区的厚度,元胞区内的元胞位于第一导电类型外延层对应,超结结构内的第二导电类型柱通过第一导电类型外延层与元胞区内的第二导电类型基区隔离,且所述超结结构内的第二导电类型柱通过第一导电类型衬底与背面电极结构内的第二导电类型集电区相隔离,第二导电类型集电区与第一导电类型衬底邻接。

6.所述第一导电类型漂移区包括若干通过外延工艺依次生长得到的漂移基层,漂移基层在第一导电类型衬底上呈层叠分布;

7.外延生长得到一漂移基层后,对所生长得到的漂移基层进行刻蚀,以能得到漂移基层槽,在漂移基层槽内填充第二导电类型杂质,以在填充后形成第二导电类型的漂移基层柱;

8.每个漂移基层内的漂移基层柱正对应,且相邻漂移基层内的漂移基层柱相互接触,以利用所有的漂移基层形成所需的第一导电类型漂移区时,通过相互接触的漂移基层柱形成第二导电类型柱,以在所形成的第一导电类型漂移区内得到超结结构,超结结构内

第一导电类型柱与第二导电类型柱在第一导电类型漂移区内交替分布。

9.在耐压时,所述漂移基层柱的第一导电类型柱和第二导电类型柱相互耗尽后的电荷量相同。

10.在所述功率半导体器件的截面上,所述元胞区内的元胞包括设置于第一导电类型外延层内的第二导电类型基区以及设置于第一导电类型外延层内的元胞沟槽,所述元胞沟槽贯穿第二导电类型基区,元胞沟槽的槽底位于第二导电类型基区的下方,第二导电类型基区与元胞沟槽的外侧壁接触,且元胞沟槽的深度小于第一导电类型外延层的厚度;

11.在元胞沟槽的侧壁以及底壁设置有绝缘氧化层,并在设置有绝缘氧化层的元胞沟槽内填充栅极导电多晶硅;在第二导电类型基区内设置第一导电类型源区,所述第一导电类型源区与元胞沟槽外侧壁接触,且第二导电类型基区以及第一导电类型源区与第一导电类型外延层上方的发射极金属欧姆接触。

12.在第二导电类型基区内还设置第二导电类型注入区,所述第二导电类型注入区的掺杂浓度大于第二导电类型基区的掺杂浓度,且第二导电类型注入区与发射极金属欧姆接触。

13.所述背面电极结构包括设置于第一导电类型衬底背面的第二导电类型集电区以及设置于第二导电类型集电区上的集电极金属层,所述集电极金属层与第二导电类型集电区欧姆接触。

14.一种基于超结结构的高压逆阻型功率半导体器件的制备方法,所述制备方法包括如下步骤:

15.步骤1、提供第一导电类型衬底;

16.步骤2、在衬底的正面通过外延工艺制备第一导电类型漂移区以及制备于所述第一导电类型漂移区内的超结结构,其中,超结结构内的第一导电类型柱以及第二导电类型柱相应的高度均小于第一导电类型漂移区的厚度,第一导电类型漂移区包括若干通过外延工艺依次生长得到的漂移基层,漂移基层在第一导电类型衬底上呈层叠分布;

17.外延生长得到一漂移基层后,对所生长得到的漂移基层进行光刻和沟槽刻蚀工艺,以能得到漂移基层槽,在漂移基层槽内填充第二导电类型杂质,以在填充后形成第二导电类型的漂移基层柱;

18.每个漂移基层内的漂移基层柱正对应,且相邻漂移基层内的漂移基层柱相互接触,以利用所有的漂移基层形成所需的第一导电类型漂移区时,通过相互接触的漂移基层柱形成第二导电类型柱,以在所形成的第一导电类型漂移区内得到超结结构,超结结构内第一导电类型柱与第二导电类型柱在第一导电类型漂移区内交替分布;

19.步骤3、通过外延生长工艺在上述第一导电类型漂移区上制备得到第一导电类型外延层,所述第一导电类型外延层支撑在第一导电类型漂移区上,超结结构内的第二导电类型柱与第一导电类型外延层接触;

20.步骤4、制备与第一导电类型外延层对应的元胞区,元胞区包括若干元胞,元胞区包括第二导电类型基区,第二导电类型基区通过第一导电类型外延层与超结结构内的第二导电类型柱隔离;

21.步骤5、在第一导电类型衬底的背面制备所需的背面电极结构,所述背面电极结构内的第二导电类型集电区通过第一导电类型衬底与超结结构内的第二导电类型柱隔离。

22.在所述功率半导体器件的截面上,所述元胞区内的元胞包括设置于第一导电类型外延层内的第二导电类型基区以及设置于第一导电类型外延层内的元胞沟槽,所述元胞沟槽贯穿第二导电类型基区,元胞沟槽的槽底位于第二导电类型基区的下方,第二导电类型基区与元胞沟槽的外侧壁接触,且元胞沟槽的深度小于第一导电类型外延层的厚度;

23.在元胞沟槽的侧壁以及底壁设置有绝缘氧化层,并在设置有绝缘氧化层的元胞沟槽内填充栅极导电多晶硅;在第二导电类型基区内设置第一导电类型源区,所述第一导电类型源区与元胞沟槽外侧壁接触,且第二导电类型基区以及第一导电类型源区与第一导电类型外延层上方的发射极金属欧姆接触。

24.所述背面电极结构包括设置于第一导电类型衬底背面的第二导电类型集电区以及设置于第二导电类型集电区上的集电极金属层,所述集电极金属层与第二导电类型集电区欧姆接触。

25.所述衬底的材料包括硅,元胞沟槽的深度为5μm~6μm。

26.所述“第一导电类型”和“第二导电类型”两者中,对于n型功率半导体器件,第一导电类型指n型,第二导电类型为p型;对于p型功率半导体器件,第一导电类型与第二导电类型所指的类型与n型功率半导体器件正好相反。

27.本发明的优点:在制备第一导电类型漂移区以及超结结构时,在第一导电类型漂移区内漂移基层可以通过外延工艺制备得到;制备得到超结结构时,通过刻蚀和填充工艺最终能形成第二导电类型柱以及与所述第二导电类型柱交替分布的第一导电类型柱,制备第一导电类型漂移区以及在第一导电类型漂移区内制备超结结构时,在实现与现有工艺兼容的情况下,既能降低高深宽比的刻蚀和填充难度,可以得到较薄且掺杂浓度较低的第一导电类型漂移区,从而可以实现高耐压的需求,尤其适合于1200v以上的高压igbt器件,高掺杂和更薄的第一导电类型漂移区使得整个功率半导体器件的通态压降急剧减小,降低了通态损耗,利于器件性能提升。

28.在正向耐压时,第一导电类型外延层与第二导电类型基区形成pn结耗尽层,并向第一导电类型漂移区拓展,由于第一导电类型漂移区电势高,会使得第一导电类型柱和第二导电类型柱相互耗尽,第一导电类型漂移区的电场拓展到背面区域;在反向耐压时,第一导电类型衬底和第二导电类型集电区形成pn结耗尽层,相同方式向中间超结结构相互耗尽,电场到达正面区域,无论在正向还是反向时,都可以相互耗尽,从而实现双向的耐压。

附图说明

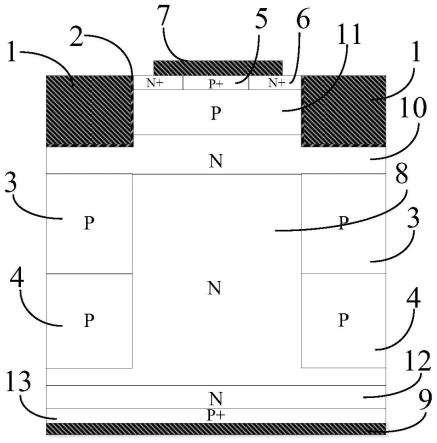

29.图1为本发明功率半导体器件的剖视图。

30.图2~图8为本发明的具体实施工艺步骤剖视图,其中

31.图2为本发明n型衬底的剖视图。

32.图3为本发明制备得到第一漂移基层后的剖视图。

33.图4为本发明对第一漂移基层刻蚀得到漂移基层槽后的剖视图。

34.图5为本发明在第一漂移基层内填充得到第一漂移基层柱后的剖视图。

35.图6为本发明制备得到第二漂移基层以及填充在第二漂移基层内的第二漂移基层柱后的剖视图。

36.图7为本发明制备得到外延层后的剖视图。

37.图8为本发明制备得到背面电极结构的剖视图。

38.附图标记说明:1-栅极导电多晶硅、2-绝缘氧化层、3-第二漂移基层柱、4-第一漂移基层柱、5-p型注入区、6-n+源区、7-发射极金属、8-n柱、9-集电极金属层、10-n型外延层、11-p型基区、12-n型衬底、13-p+集电区、14-第一漂移基层、15-第一漂移基层槽以及16-第二漂移基层。

具体实施方式

39.下面结合具体附图和实施例对本发明作进一步说明。

40.如图1和图8所示:为了在有效实现高耐压时,又能降低通态压降,以n型功率半导体器件为例,本发明包括具有n导电类型的半导体基板、制备于所述半导体基板中心区的元胞区以及制备于所述半导体基板背面的背面电极结构;所述半导体基板包括n型衬底12、设置于n型衬底12正面上的n型漂移区以及外延设置于n型漂移区上的n型外延层10;

41.在所述n型漂移区内设置超结结构,超结结构内的n柱8以及p柱相应的高度均小于n型漂移区的厚度,元胞区内的元胞与n型外延层10对应,超级结构内的p柱通过n型外延层10与元胞区内的p型基区11隔离,且所述超结结构内的p柱通过n型衬底12与背面电极结构内的p+集电区13相隔离,p+集电区13与n型衬底12邻接。

42.具体地,半导体基板具有n导电类型,元胞区可通过本技术领域常用的半导体工艺制备在半导体基板的中心区,元胞区的作用以及具体制备工艺等均可根据实际需要选择,以能满足实际需求为准。一般地,在元胞区的外圈还可设置终端区,利用终端区对元胞区进行保护,终端区对元胞区的保护原理等可均与现有相一致,此处不再赘述。

43.本发明实施例中,半导体基板包括n型衬底12、n型漂移区以及n型外延层10,其中,n型漂移区设置于n型衬底12上,n型外延层10设置于n型漂移区上,即n型衬底12、n型漂移区以及n型外延层10相应的导电类型均为n型,且n型外延层10通过外延工艺设置于n型漂移区上,即n型漂移区位于n型衬底12与n型外延层10之间,n型漂移区分别与n型衬底12以及n型外延层10接触。

44.具体实施时,在n型漂移区内设置超结结构,本技术领域人员可知,n型漂移区内的超级结构包括若干交替分布的n柱8以及p柱,超级结构内的n柱8以及p柱的高度均小于n型漂移区的厚度,超结结构可采用现有常用的形式,以能形成所需的超结结构为准,此处不再赘述。元胞区的元胞与n型外延层10对应,一般地,在元胞区内至少需要设置一p型基区11,p型基区11位于n型外延层10内,p型基区11在n型外延层10内的深度小于n型外延层10的厚度,从而超结结构内的p柱通过n型外延层10与p型基区11隔离,此外,超结结构内的p柱通过n型衬底12与p+集电区13隔离。本发明实施例中,在n型漂移区内设置超结结构后,在工作时,能在n型漂移区内引入横向电场,通过引入的横向电场,可以实现电场由三角形分布变为梯形分布,提高击穿电压,能降低n型漂移区的厚度,从而可在较低厚度的n型漂移区下,还能降低n型漂移区的电阻率,即在有效实现高耐压时,又能降低通态压降。

45.具体实施时,逆阻具体是指功率半导体器件具备双向耐压能力,即功率半导体器件的正面、背面均有耐压pn结;本发明实施例中,p型基区11与n型外延层10形成正面耐压的pn结,而背面的p+集电区13与n型的n型衬底12形成背面耐压的pn结。为了满足耐压需求,n型外延层10、n型衬底12的电阻率可设置为20ohm*cm-40ohm*cm。

46.进一步地,所述n型漂移区包括若干通过外延工艺依次生长得到的漂移基层,漂移基层在n型衬底12上呈层叠分布;

47.外延生长得到一漂移基层后,对所生长得到的漂移基层进行刻蚀,以能得到漂移基层槽,在漂移基层槽内填充p型杂质,以在填充后形成p型的漂移基层柱;

48.每个漂移基层内的漂移基层柱正对应,且相邻漂移基层内的漂移基层柱相互接触,以利用所有的漂移基层形成所需的n型漂移区时,通过相互接触的漂移基层柱形成p柱,以在所形成的n型漂移区内得到超结结构,超结结构内n柱8与p柱在n型漂移区内交替分布。

49.本发明实施例中,为了能适应高压领域的耐压需求,n型漂移区包括若干通过外延工艺依次生长得到的漂移基层,多个漂移基层在n型衬底12上方呈层叠分布,即每个漂移基层均采用外延工艺制备得到,通过依次外延工艺制备得到的漂移基层能最终形成n型漂移区。具体实施时,n型漂移区内漂移基层的数量与功率半导体器件的耐压要求相关,如当功率半导体器件的耐压在1200v时,n型漂移区内一般至少需要设置两个漂移基层,具体数量以能满足实际耐压需求为准,此处不再赘述。

50.为了能在n型漂移区内形成超结结构,在外延生长得到一漂移基层后,对所生长得到的漂移基层刻蚀,得到若干漂移基层槽,在漂移基层槽填充p型杂质,利用填充在漂移基层槽内的p型杂质,能形成漂移基层柱。在n型漂移区的所有漂移基层内,漂移基层柱正对应,相邻漂移基层内的漂移基层柱间相互接触,从而利用利用所有的漂移基层形成所需的n型漂移区时,通过相互接触的漂移基层柱形成p柱,而相邻p柱间的n型漂移区形成n柱8,即可在n型漂移区能形成交替分布的n柱8与p柱。

51.图1和图8中,示出了n型漂移区内设置两个漂移基层的具体实施情况示意图,支撑于n型衬底12的漂移基层内设置若干第一漂移基层柱4,在邻接n型外延层10的漂移基层内设置若干第二漂移基层柱3,第一漂移基层柱4与第二漂移基层柱3间呈一一对应,且第一漂移基层柱4与第二漂移基层柱3间相互邻接,利用邻接的第一漂移基层柱4与第二漂移基层柱3能形成一p柱,利用多个第一漂移基层柱4与第二漂移基层柱3形成的p柱,即可得到在n型漂移区内相互交替分布的n柱8与p柱。

52.综上,通过外延工艺制备得到漂移基层,并通过沟槽刻蚀以及填充工艺得到漂移基层柱,利用正对应且接触的漂移基层柱形成超结结构时,可以有效降低高深宽比沟槽的刻蚀和填充难度,在制备得到较薄且较底电阻率的n型漂移区时,能与现有工艺兼容。n型漂移区的电阻率一般可根据实际需求进行调节,具体电阻率以能满足实际应用为准。

53.在具体实施时,漂移基层的掺杂浓度不高于n型衬底12的掺杂浓度;而在耐压时,所述漂移基层的n柱和p柱耗尽后的电荷量相同。本发明实施例中,填充得到的漂移基层p柱耗尽后的电荷量与漂移基层n柱的电荷量相同,具体实施时,可以通过调节p柱、n柱相应的宽度与掺杂浓度,以能达到耐压时n柱与p柱在耗尽后的电荷量相同,具体配置超结结构内的n柱、p柱在耗尽后电荷量相同的方式可根据需要选择,以能满足n柱和p柱耗尽后的电荷量相同均可。漂移基层的掺杂浓度不高于n型衬底12的掺杂浓度,即漂移基层的掺杂浓度低于或等于n型衬底12的掺杂浓度,具体可以根据需要选择。

54.进一步地,在所述功率半导体器件的截面上,所述元胞区内的元胞包括设置于n型外延层10内的p型基区11以及设置于n型外延层10内的元胞沟槽,所述元胞沟槽贯穿p型基区11,元胞沟槽的槽底位于p型基区11的下方,p型基区11与元胞沟槽的外侧壁接触,且元胞

沟槽的深度小于n型外延层10的厚度;

55.在元胞沟槽的侧壁以及底壁设置有绝缘氧化层2,并在设置有绝缘氧化层2的元胞沟槽内填充栅极导电多晶硅1;在p型基区11内设置n+源区6,所述n+源区6与元胞沟槽外侧壁接触,且p型基区11以及n+源区6与n型外延层10上方的发射极金属7欧姆接触。

56.图1和图8中,示出了一种元胞的剖视图,即示出了元胞采用沟槽结构的剖视图,当元胞采用沟槽结构时,在n型外延层10内设置若干元胞沟槽,元胞沟槽的深度小于n型外延层10的厚度,元胞沟槽的深度为5μm~6μm。在n型外延层10内设置p型基区11,一般地,p型基区11贯穿n型外延层10的中心区,即p型基区11贯穿整个元胞区,p型基区11一般从n型外延层10的上端面垂直向下延伸,p型基区11位于元胞沟槽槽底的上方,从而元胞沟槽贯穿p型基区11,p型基区11与元胞沟槽的外侧壁接触。

57.在制备得到元胞沟槽后,在元胞沟槽的侧壁以及底壁设置绝缘氧化层2,绝缘氧化层2为二氧化硅层,绝缘氧化层2可以采用热氧化工艺生长得到。在生长有绝缘氧化层2的元胞沟槽内填充栅极导电多晶硅1,栅极导电多晶硅1通过绝缘氧化层2与元胞沟槽的侧壁以及底壁绝缘隔离。

58.在p型基区11内设置n+源区6,n+源区6与元胞沟槽的外侧壁接触,n+源区6的深度远小于p型基区11的深度。为了能得到功率半导体器件的发射极,需要在n型外延层10的上方制备发射极金属7,发射极金属7与p型基区11以及n+源区6欧姆接触,发射极金属7与栅极导电多晶硅1绝缘隔离。当然,在制备发射极金属7时,一般也会制备栅极金属,栅极金属能与栅极导电多晶硅1电连接,利用栅极金属与栅极导电多晶硅1间的电连接能形成功率半导体器件的栅电极,具体与现有相一致,为本技术领域人员所熟知,此处不再赘述。

59.进一步地,在p型基区11内还设置p型注入区5,所述p型注入区5的掺杂浓度大于p型基区11的掺杂浓度,且p型注入区5与发射极金属7欧姆接触。

60.本发明实施例中,p型注入区5的深度与n+源区6可相一致,p型注入区5的掺杂浓度大于p型基区11的掺杂浓度。对于相邻的元胞沟槽,p型注入区5与两侧的n+源区6接触。当在p型基区11内设置p型注入区5时,发射极金属7与p型注入区5欧姆接触,p型基区11利用p型注入区5与发射极金属7电连接。

61.当然,在具体实施时,元胞还可以采用的形式,如可以采用平面元胞的形式,具体可以根据实际需要选择,以能满足具体耐压等要求为准,此处不再赘述。

62.进一步地,所述背面电极结构包括设置于p+集电区13上的集电极金属层9,所述集电极金属层9与p+集电区13欧姆接触。

63.本发明实施例中,在n型衬底12的背面设置p+集电区13,在p+集电区13上设置集电极金属层9,集电极金属层9与p+集电区13欧姆接触,即利用集电极金属层9以及p+集电区13形成的背面电极结构,使得功率半导体器件形成igbt器件。

64.当形成的功率半导体器件为igbt器件时,超结结构内的p柱通过n型衬底12与p+集电区13隔离。igbt器件工作时:正向耐压时,空间电荷区从正面p基区11和n型外延层10形成的pn结开始向外拓展,n柱8内的n型杂质可以和p柱的p型杂质相互补偿,进而表现为电中性特性,使得纵向电场为梯形分布,从而提高击穿电压;在反向耐压时,同样,由于通过n型衬底12以及n型漂移区使得p柱与p+集电区13隔离,空间电荷区从n型衬底12和p+集电区13形成的pn结开始向外拓展,n柱8内的n型杂质可以与p柱相互耗尽形成耐压层,从而可以使得

形成的igbt器件具备双向耐压能力。

65.如图2~图8所示,上述基于超结结构的高压逆阻型功率半导体器件,可以通过下述工艺制备得到,具体地,所述制备方法包括如下步骤:

66.步骤1、提供n导电类型的n型衬底12;

67.如图2所示,n型衬底12可以为现有常用的形式,如硅衬底等,n型衬底12的厚度以及电阻率等可以根据实际需要选择,具体为本技术领域人员所熟知,此处不再赘述。

68.步骤2、在n型衬底12的正面通过外延工艺制备n型漂移区以及制备于所述n型漂移区内的超结结构,其中,超结结构内的n柱8以及p柱相应的高度均小于n型漂移区的厚度,n型漂移区包括若干通过外延工艺依次生长得到的漂移基层,漂移基层在n型衬底12上呈层叠分布;

69.外延生长得到一漂移基层后,对所生长得到的漂移基层进行光刻和沟槽刻蚀工艺,以能得到漂移基层槽,在漂移基层槽内填充p型杂质,以在填充后形成p导电类型的漂移基层柱;

70.每个漂移基层内的漂移基层柱正对应,且相邻漂移基层内的漂移基层柱相互接触,以利用所有的漂移基层形成所需的n型漂移区时,通过相互接触的漂移基层柱形成p柱,以在所形成的n型漂移区内得到超结结构,超结结构内n柱8与p柱在n型漂移区内交替分布;

71.具体地,制备得到的n型漂移区以及超结结构均可以参考上述说明,下面以n型漂移区内包括两个漂移基层为例,对具体的工艺过程进行详细说明。

72.如图3所示,为在n型衬底12的正面通过外延工艺制备得到第一漂移基层14后的示意图,第一漂移基层14的厚度以及电阻率可以根据实际需要选择,第一漂移基层14的电阻率不高于n型衬底12的电阻率。

73.如图4所示,在制备得到第一漂移基层14后,选择性地掩蔽和刻蚀第一漂移基层14,以能在第一漂移基层14内刻蚀得到第一漂移基层槽15,第一漂移基层槽15的深度小于第一漂移基层14的厚度,具体刻蚀得到第一漂移基层槽15的工艺条件以及过程均可与现有相一致,具体为本技术领域人员所熟知,此处不再赘述。图4中示出了在第一漂移基层14内存在一个第一漂移基层槽15的具体情况,但实际工艺中,在第一漂移基层槽14内设置多个第一漂移基层槽15,所有的第一漂移基层槽15为同一工艺步骤层,每个第一漂移基层槽15具有相同的宽度以及深度,相邻第一漂移基层槽15间的距离等可设置为相同。

74.如图5所示,在得到第一漂移基层槽15后,进行p型杂质的填充,以能得到第一漂移基层柱4。具体实施时,可现在第一漂移基层14上生长牺牲氧化层,然后对牺牲氧化层刻蚀去除,然后进行外延填充工艺,并在填充后再进行刻蚀与cmp工艺,以形成填满第一漂移基层槽15内的第一漂移基层柱4。

75.在第一漂移基层14内制备得到若干第一漂移基层柱4后,在第一漂移基层14上采用外延工艺制备第二漂移基层16,第二漂移基层16的厚度以及电阻率可与第一漂移基层14相同,具体外延生长第二漂移基层16的工艺条件以及过程均可与现有相一致。

76.在制备得到第二漂移基层16后,采用上述工艺对第二漂移基层16进行沟槽刻蚀,以能得到贯通第二漂移基层16的第二漂移基层槽,第二漂移基层16内的第二漂移基层槽与第一漂移基层14内的第一漂移基层槽15呈一一对应,即可利用相同的光刻版对第一漂移基层14以及第二漂移基层16进行沟槽刻蚀,具体对第二漂移基层16刻蚀得到第二漂移基层槽

的方式等为本技术领域人员所熟知,此处不再赘述。

77.在第二漂移基层16内制备得到第二漂移基层槽后,利用上述填充工艺得到第二漂移基层柱3,在填充得到第二漂移基层柱3后,第二漂移基层柱3的下端部与第一漂移基层柱4的上端接触,如图6所示。

78.当n型漂移区由第一漂移基层14以及第二漂移基层16构成时,则利用相互接触的第一漂移基层柱4与第二漂移基层柱3能形成p柱,相邻p柱间的区域形成n柱8,具体与现有相一致,此处不再赘述。

79.当n型漂移区内漂移基层的数量多于两层时,可以参考上述第二漂移基层16的工艺,以能得到多个层叠分布的漂移基层,漂移基层数量不同时,则在n型漂移区内形成的p柱的高度等不同,具体为本技术领域人员所熟知,此处不再赘述。

80.步骤3、通过外延生长工艺在上述n型漂移区上制备得到n型外延层10,所述n型外延层10支撑在n型漂移区上,超结结构内的p柱与n型外延层10接触;

81.具体地,在制备得到n型漂移区后,采用本技术领域常用的外延工艺制备得到n型外延层10,n型外延层10支撑在n型漂移区上,如图7所示。一般地,n型外延层10的掺杂浓度与n型衬底12的掺杂浓度相一致,具体制备得到n型外延层10的工艺条件以及过程等均可与现有相一致,为本技术领域人员所熟知,此处不再赘述。

82.步骤4、制备与n型外延层10正对应的元胞区,元胞区包括若干元胞,元胞区包括p型基区11,p型基区11通过n型外延层10与超结结构内的p柱隔离;

83.具体地,在制备得到n型外延层10后,采用本技术领域常用的技术手段制备所需的元胞,即能得到元胞区,元胞区内元胞的具体结构形式可以参考图1和图8的具体实施情况,当然,元胞还可以采用其他的形式,元胞的结构不同时,相应的制备工艺有所不同,具体可以根据实际需要选择,以能得到所需的元胞以及元胞区为准,此处不再赘述。

84.步骤5、在n型衬底12的背面制备所需的背面电极结构,所述背面电极结构内的p+集电区13通过n型衬底12与超结结构内的p柱隔离。

85.具体地,在制备得到元胞区以及相应的正面结构时,需要在n型衬底12的背面制备背面电极结构,背面电极结构的具体情况可以参考图1、图8以及上述说明,具体本技术领域人员所熟知,此处不再赘述。

86.综上,在制备n型漂移区时,在n型漂移区内漂移基层可以通过外延工艺制备得到;制备得到超结结构时,通过刻蚀和填充工艺最终能形成p柱以及与所述p柱交替分布的n柱8,制备n型漂移区以及在n型漂移区内制备超结结构时,既能降低高深宽比的刻蚀和填充难度,可以得到较薄且掺杂浓度较低的n型漂移区,从而可以实现高耐压的需求,尤其适合于1200v以上的高压igbt器件,高掺杂和更薄的n型漂移区使得整个功率半导体器件的通态压降急剧减小,降低了通态损耗,利于器件性能提升。

87.在正向耐压时,n型外延层10与p型基区11形成pn结耗尽层,并向n型漂移区拓展,由于n型漂移区电势高,会使得n型漂移区内的n柱8和p柱相互耗尽,n型漂移区的电场拓展到背面区域;在反向耐压时,n型衬底12和p+集电区13形成pn结耗尽层,相同方式向中间超结结构相互耗尽,电场到达正面区域,无论在正向还是反向时,都可以相互耗尽,从而实现双向的耐压。

88.由上述说明可知,与现有工艺相兼容,即可以降低高压超结高深宽比的深槽刻蚀

和填充难度,又可以在实现高耐压的同时,降低通态压降和静态损耗,同时由于可以正向和反向的耐压pn结,可以实现双向的耐压,适用于逆阻型igbt结构。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1