一种多口电源电路及其辅助电路的制作方法

1.本发明涉及电源技术领域,尤其涉及一种多口电源电路及其辅助电路。

背景技术:

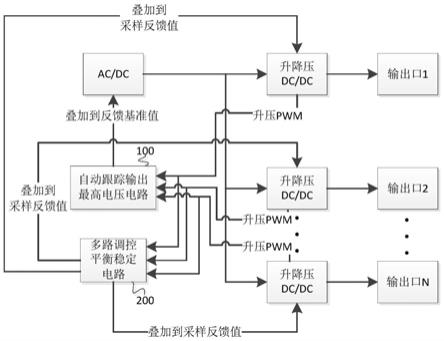

2.参考图1,目前市场上多口电源大多数是电源先经过ac/dc电路处理后输出,然后配多路dc/dc电路来实现多口输出。一般ac/dc电路都会定一个输出电压,然后各路升降压dc/dc电路再降压或升降压输出,这样就可以实现多口输出,但是此种方案存在的问题是效率差。

技术实现要素:

3.本发明要解决的技术问题在于,针对现有技术的上述成本高、效率差的缺陷,提供一种多路调控平衡稳定电路。

4.本发明解决其技术问题所采用的技术方案是:构造一种多口电源电路的辅助电路,应用于多口电源电路,所述多口电源电路包括ac/dc电路和与所述ac/dc电路分别连接的多路升降压dc/dc电路,所述ac/dc电路基于设定的反馈基准值调节输出电压,所述dc/dc电路通过升压pwm信号将ac/dc电路的输出电压跟踪调整成自身需求输出的最高电压,各路升降压dc/dc电路的升压部分直通,所述辅助电路包括:

5.自动跟踪输出最高电压电路,与所述ac/dc电路以及所述多路升降压dc/dc电路分别连接,用于将所有升降压dc/dc电路的所述升压pwm信号进行叠加处理整合成一个基准信号,并将所述基准信号进行处理后叠加到所述ac/dc电路的反馈基准值上以使所述ac/dc电路调节输出电压到多路升降压dc/dc电路中需求最高的电压;

6.多路调控平衡稳定电路,与多路升降压dc/dc电路分别连接,用于在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,将各路升降压dc/dc电路的升压pwm信号对应叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高。

7.优选地,所述自动跟踪输出最高电压电路包括:

8.升压pwm信号叠加电路,与所述多路升降压dc/dc电路分别连接,用于分别获取所述多路升降压dc/dc电路的所述升压pwm信号,并将所有的所述升压pwm信号进行叠加处理整合成一个基准信号;

9.基准信号处理电路,与所述升压pwm信号叠加电路以及所述ac/dc电路连接,用于将所述基准信号进行处理后叠加到所述ac/dc电路的反馈基准值上以使所述ac/dc电路调节输出电压到多路升降压dc/dc电路中需求最高的电压。

10.优选地,所述升压pwm信号叠加电路包括第一电容、第一电阻以及与所述多路升降压dc/dc电路分别对应的多个第二电阻,所述第一电容与所述第一电阻并联,所述第一电阻的第一端接地,所述多个第二电阻的第一端同时连接至所述第一电阻的第二端,所述多个

第二电阻的第二端一一对应的连接至所述多路升降压dc/dc电路以分别获取所述多路升降压dc/dc电路的所述升压pwm信号,所述第一电阻的第二端还连接至所述基准信号处理电路以将整合得到的所述基准信号传递给所述基准信号处理电路。

11.优选地,所述ac/dc电路包括可控精密稳压源和用于采样ac/dc电路的输出电压的采样电路,所述可控精密稳压源的参考极连接所述采样电路,所述可控精密稳压源的阳极经由第三电阻接地;

12.所述基准信号处理电路包括反馈放大电路,所述反馈放大电路的输入端与所述升压pwm信号叠加电路连接以接收所述基准信号,反馈放大电路的反馈端连接所述采样电路,所述反馈放大电路的输出端连接至所述可控精密稳压源的阳极。

13.优选地,所述反馈放大电路包括运算放大器、第四电阻、第五电阻、第六电阻、第二电容,所述运算放大器的同相输入端经由所述第四电阻连接所述升压pwm信号叠加电路以接收所述基准信号,所述运算放大器的反相输入端经由所述第五电阻连接所述运算放大器的输出端,所述第二电容与所述第五电阻并联,所述运算放大器的输出端连接所述可控精密稳压源的阳极,所述运算放大器的反相输入端还经由所述第六电阻连接所述采样电路以反馈与所述ac/dc电路的输出电压对应的电压信号给所述运算放大器。

14.优选地,所述采样电路包括串接在所述ac/dc电路的输出端和地之间的第七电阻、第八电阻和第九电阻,所述可控精密稳压源的参考极连接至第七电阻、第八电阻之间,所述运算放大器的反相输入端还经由所述第六电阻连接至所述第八电阻和第九电阻之间。

15.优选地,所述多路调控平衡稳定电路包括:

16.平衡稳定电路,与多路升降压dc/dc电路分别连接,用于获取各路升降压dc/dc电路的所述升压pwm信号,并将各路升降压dc/dc电路的所述升压pwm信号对应叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高;

17.平衡启动电路,与所述平衡稳定电路以及多路升降压dc/dc电路分别连接,用于获取多路升降压dc/dc电路的输出电压,并在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,启动所述平衡稳定电路。

18.优选地,所述平衡启动电路包括第一开关管、与多路升降压dc/dc电路对应的多个第十电阻和多个第一二极管、第十一电阻、第三电容、第十二电阻,所述第十二电阻连接于第一开关管的控制端和输入端之间,第一开关管的输出端与平衡稳定电路连接,第一开关管的控制端经由第三电容接地,各路升降压dc/dc电路的输出端分别连接至对应的第一二极管的正极,各个第一二极管的负极共接于第一开关管的输入端,各路升降压dc/dc电路的输出端还经由对应的第十电阻连接至第十一电阻的第一端,第十一电阻的第二端连接第一开关管的控制端。

19.优选地,所述平衡稳定电路包括上拉电阻、下拉电阻、与多路升降压dc/dc电路对应的多个叠加电路,每一所述叠加电路包括第二开关管、第十三电阻、第十四电阻、第四电容,每一所述升降压dc/dc电路均包括第一采样电阻和第二采样电阻,第一采样电阻和第二采样电阻串联在对应的升降压dc/dc电路的输出端和第二开关管的输出端之间,第二开关管的输出端经由第十三电阻接地,第四电容与第十三电阻并联,第二开关管的输入端经由对应的第十四电阻获取对应的升降压dc/dc电路的升压pwm信号,所有第二开关管的控制端

共接后经由上拉电阻连接至所述平衡启动电路中的第一开关的输出端,所有第二开关管的控制端共接后还经由下拉电阻接地。

20.本发明另一方面还构造了一种多口电源电路,包括ac/dc电路和与所述ac/dc电路分别连接的多路升降压dc/dc电路,所述ac/dc电路基于设定的反馈基准值调节输出电压,所述dc/dc电路通过升压pwm信号将ac/dc电路的输出电压跟踪调整成自身需求输出的最高电压,各路升降压dc/dc电路的升压部分直通,所述多口电源电路还包括如前任一项所述的辅助电路。

21.本发明的多口电源电路及其辅助电路,具有以下有益效果:本发明的多口电源电路中增加了自动跟踪输出最高电压电路,其将所有的所述升压pwm信号进行叠加处理整合成一个基准信号,处理后叠加到所述ac/dc电路的反馈基准值上,所以任意升压pwm信号改变则会叠加到ac/dc电路的反馈基准值上,如此,ac/dc电路可以实现自动调节输出电压到多路输出口中需求最高的电压,有利于提高电源效率;而且,为了解决前述自动跟踪输出最高电压电路带来的多路升降压dc/dc电路中有二路以上输出电压接近且高于其他路升降压dc/dc电路的输出电压时存在振荡的问题,本发明还配套设计了多路调控平衡稳定电路,用于将各路升降压dc/dc电路的所述升压pwm信号叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高,这样就可以避免自动跟踪输出最高电压电路在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,产生震荡。

附图说明

22.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图:

23.图1是现有多口电源电路的原理图;

24.图2是改进后的多口电源电路的原理图;

25.图3是升降压dc/dc电路的改进示意图;

26.图4是一个具体实施例中的自动跟踪输出最高电压电路的电路图;

27.图5是一个具体实施例中的多路调控平衡稳定电路的电路图。

具体实施方式

28.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的典型实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

29.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

30.本说明书中使用的“第一”、“第二”等包含序数的术语可用于说明各种构成要素,

但是这些构成要素不受这些术语的限定。使用这些术语的目的仅在于将一个构成要素区别于其他构成要素。例如,在不脱离本发明的权利范围的前提下,第一构成要素可被命名为第二构成要素,类似地,第二构成要素也可以被命名为第一构成要素。“相连”或“连接”,不仅仅包括将两个实体直接相连,也包括通过具有有益改善效果的其他实体间接相连。

31.参考图2,本发明总的思路是:设计一种多口电源电路。多口电源电路包括ac/dc电路和与所述ac/dc电路分别连接的多路升降压dc/dc电路,如图中示意的n个升降压dc/dc电路,n为大于1的正整数。其中,所述ac/dc电路的输入端连接交流源,输出端同时连接n个升降压dc/dc电路的输入端,n个升降压dc/dc电路的输出端一一对应的连接输出口1至输出口n,如此实现多路电源输出。ac/dc电路用于将交流源转换为直流源输出,且ac/dc电路是基于设定的反馈基准值调节输出电压,输出采样电阻不变的前提下,反馈基准值越大,则输出电压越大,反之反馈基准值越小,则输出电压越小。各个所述升降压dc/dc电路利用升压pwm信号将ac/dc电路的输出电压跟踪调整成自身需求输出的最高电压,比如,升降压dc/dc电路会采样自己输出电压产生对应的采样反馈值,然后根据采样反馈值的大小来调整升压pwm信号的占空比,最终使得升降压dc/dc电路的输出达到所需的输出电压即可。可以理解的是,各升降压dc/dc电路的输出可以相同也可以不同。当升降压dc/dc电路的输入电压大于等于输出电压时,升降压dc/dc电路通过调节降压pwm来控制输出电压的,当输入电压小于输出电压时dc/dc电路通过调节升压pwm来控制输出电压的,升压pwm信号的大小与升降压dc/dc电路的输出电压是正相关的。也正是基于此,本发明一方面将各路升降压dc/dc电路的升压部分直通,参考图3,左图是常规的升降压dc/dc电路,右图是升压部分直通后的升降压dc/dc电路,比如将q2的输入、输出用导线接通;另一方面,利用各个升降压dc/dc电路的升压pwm信号来反馈控制ac/dc电路的输出,具体是将各个ac/dc电路的升压pwm信号叠加、处理后与ac/dc电路的反馈基准值叠加。

32.为此,参考图2,可以设计一种自动跟踪输出最高电压电路100,自动跟踪输出最高电压电路100与所述ac/dc电路以及所述多路升降压dc/dc电路分别连接,用于将所有升降压dc/dc电路的所述升压pwm信号进行叠加处理整合成一个基准信号,并将所述基准信号进行处理后叠加到所述ac/dc电路的反馈基准值上以使所述ac/dc电路调节输出电压到多路升降压dc/dc电路中需求最高的电压。如此,任意升压pwm信号改变则会叠加到ac/dc电路的反馈基准值,如此,ac/dc电路可以实现自动调节输出电压到多路输出口中需求最高的电压,有利于提高电源效率。

33.但是,自动跟踪输出最高电压电路100的跟踪方式存在的一个缺陷是,如果有二路以上升降压dc/dc电路的输出接近且高于其他路升降压dc/dc电路的输出电压,则会产生震荡。比如说,假设有两个升降压dc/dc电路,两者的输出电压vout1和vout2接近,假设vout1略高于vout2,两个升降压dc/dc电路的升压pwm信号中pwm1高于pwm2,对于vout1来说,ac/dc电路的输出电压对于第一个升降压dc/dc电路来说足够,但是对于第二个升降压dc/dc电路来说是不够的,所以第二个升降压dc/dc电路会通过控制pwm2升高的方式来提高输出,而一旦pwm2升高,则会导致ac/dc电路的输出电压增加,进而引发pwm1降低,如此会出现周而复始的反复震荡。

34.为了解决有二路以上升降压dc/dc电路的输出接近且高于其他路升降压dc/dc电路的输出电压时产生的振荡问题,本发明设计了多路调控平衡稳定电路200,多路调控平衡

稳定电路200与多路升降压dc/dc电路分别连接,用于在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,将各路升降压dc/dc电路的升压pwm信号对应叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高。这样就可以避免自动跟踪输出最高电压电路在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,产生震荡。

35.需要说明的是,本发明中所提到的有二路以上(假设是n路)升降压dc/dc电路的输出接近,此处的接近可以是n路升降压dc/dc电路的n路输出之中,两两输出之间的绝对误差在预设幅值误差范围内(比如

‑

x~x伏特的范围,x是正数),还可以是指的两两输出之间的比值与1的差值在预设比例误差范围内(比如

‑

y~y的范围,y是小于1的数)。

36.为了更好的理解上述技术方案,下面将结合说明书附图以及具体的实施方式对上述技术方案进行详细的说明,应当理解本发明实施例以及实施例中的具体特征是对本申请技术方案的详细的说明,而不是对本申请技术方案的限定,在不冲突的情况下,本发明实施例以及实施例中的技术特征可以相互组合。

37.参考图3、4,本实施例中,自动跟踪输出最高电压电路100包括升压pwm信号叠加电路101和基准信号处理电路102。多路调控平衡稳定电路200,包括平衡启动电路201和平衡稳定电路202。

38.其中,升压pwm信号叠加电路101与所述多路升降压dc/dc电路分别连接,用于分别获取所述多路升降压dc/dc电路的所述升压pwm信号,并将所有的所述升压pwm信号进行叠加处理整合成一个基准信号。

39.其中,基准信号处理电路102与所述升压pwm信号叠加电路101以及所述ac/dc电路连接,用于将所述基准信号进行处理后叠加到所述ac/dc电路的反馈基准值上。如此,任意升压pwm信号改变则会叠加到ac/dc电路的反馈基准值,如此,ac/dc电路可以实现自动调节输出电压到多路输出口中需求最高的电压,有利于提高电源效率。

40.其中,平衡启动电路201与所述平衡稳定电路202以及多路升降压dc/dc电路分别连接,用于获取多路升降压dc/dc电路的输出电压,并在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,启动所述平衡稳定电路202。

41.其中,平衡稳定电路202与多路升降压dc/dc电路分别连接,用于获取各路升降压dc/dc电路的所述升压pwm信号,并将各路升降压dc/dc电路的所述升压pwm信号叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高。因为升降压dc/dc电路的升压pwm越高,则叠加到采样反馈值上的叠加量越大,所以会导致升压pwm信号调低,升压pwm信号调低则升降压dc/dc电路的输出电压会调低;反之,升降压dc/dc电路的升压pwm越低,则叠加到采样反馈值上的叠加量越小,所以会导致升压pwm信号调高,升压pwm信号调低调高则升降压dc/dc电路的输出电压会调高。如此可以最终实现对平衡稳定,不会出现震荡。

42.我们以图4、5的两路升降压dc/dc电路为例对本发明进行详细说明。假设两路升降压dc/dc电路是dc/dc1、dc/dc2,dc/dc1 pwm表示dc/dc1的升压pwm信号,dc/dc2 pwm表示dc/dc2的升压pwm信号。dc/dc1、dc/dc2的输出电压分别是vout1、vout2。

43.其中,所述升压pwm信号叠加电路101包括第一电容c21、第一电阻r47以及与两路升降压dc/dc电路分别对应的两个第二电阻r44、r45,所述第一电容c21与所述第一电阻r47并联,所述第一电阻r47的第一端接地,两个第二电阻r44、r45的第一端同时连接至所述第一电阻r47的第二端,两个第二电阻r44、r45的第二端一一对应的连接至两路升降压dc/dc电路以分别获取两路升降压dc/dc电路的升压pwm信号:dc/dc1 pwm和dc/dc2 pwm,所述第一电阻r47的第二端还连接至所述基准信号处理电路102以将整合得到的所述基准信号传递给所述基准信号处理电路102。

44.其中,所述基准信号处理电路102包括反馈放大电路。本实施例中,所述ac/dc电路包括可控精密稳压源u3和用于采样ac/dc电路的输出电压的采样电路,所述可控精密稳压源的参考极连接所述采样电路。比如u3具体采用的是tl432,还可以是tl431。采样电路具体是分压电路,比如本实施例中是由第七电阻r35、第八电阻r39和第九电阻r40组成。u3的参考极连接至第七电阻r35和第八电阻r39之间。所述可控精密稳压源u3的阳极经由第三电阻r33接地。所述反馈放大电路的输入端与所述第一电阻r47的第二端连接以接收所述基准信号,所述反馈放大电路的输出端连接至所述可控精密稳压源u3的阳极,反馈放大电路的反馈端连接所述采样电路的r39和r40之间。

45.具体来说,所述反馈放大电路包括运算放大器u4、第四电阻r43、第五电阻r42、第二电容c20、第六电阻r41,所述运算放大器u4的同相输入端经由所述第四电阻r43连接所述第一电阻r47的第二端以接收所述基准信号,u4的反相输入端经由所述第五电阻r42连接所述运算放大器u4的输出端,所述第二电容c20与所述第五电阻r42并联,所述运算放大器u4的输出端连接所述可控精密稳压源u3的阳极。所述运算放大器u4的反相输入端作为反馈放大电路的反馈端并经由所述第六电阻r41连接至第八电阻r39和第九电阻r40之间,所述运算放大器u4的输出信号经过可控精密稳压源u3的阳极与参考极叠加到第八电阻r39和第九电阻r40上,然后通过所述第六电阻r41、第五电阻r42反馈给所述运算放大器u4的反相输入端。

46.为了解决震荡问题,参考图5,平衡启动电路201包括第一开关管、与两路升降压dc/dc电路对应的两个第十电阻r104、r46和两个第一二极管d9、d10,以及第十一电阻r105、第三电容c1、第十二电阻r34,所述第一开关管具体为pnp型三极管q37。所述平衡稳定电路202包括上拉电阻r131、下拉电阻r164、与多路升降压dc/dc电路对应的两个叠加电路,每一所述叠加电路包括第二开关管、第十三电阻r165和r166、第十四电阻r174和r173、第四电容c4和c6,每一所述升降压dc/dc电路均包括第一采样电阻r125/r102和第二采样电阻r126/r103,第二开关管具体为pmos管q38、q39。

47.所述第十二电阻r34连接于q37的基极和发射极之间q37的基极经由第三电容c1接地,两路升降压dc/dc电路的输出端分别连接至对应的第一二极管d9/d10的正极,各个第一二极管d9、d10的负极共接于q37的发射极,各路升降压dc/dc电路的输出端还经由对应的第十电阻r104/r46连接至第十一电阻r105的第一端,第十一电阻r105的第二端连接q37的基极。

48.第一采样电阻r125/r102和第二采样电阻r126/r103串联在对应的升降压dc/dc电路的输出端和q38、q39的漏极之间,第一采样电阻r125/r102和第二采样电阻r126/r103之间的节点处的电压信号为对应的升降压dc/dc电路的采样反馈值,升降压dc/dc电路的会根

据此采样反馈值调节升压pwm信号的占空比以达到控制升降压dc/dc电路的输出电压为所需电压的目的。q38、q39的漏极经由第十三电阻r165、166接地,第四电容c4、c6分别与对应的第十三电阻r165、166并联,q38、q39的源极经由对应的第十四电阻r174、r173获取对应的升降压dc/dc电路的升压pwm信号,q38、q39的栅极共接后经由上拉电阻r131连接至q37的集电极,q38、q39的栅极共接后还经由下拉电阻r164接地。

49.下面结合图4、5,说明两路升降压dc/dc电路的控制原理:

50.①

、dc/dc1 pwm与dc/dc2 pwm通过r44、r45、r47、c21将两路pwm信号整合成一个基准信号,不管那一路pwm信号往上调都能调高基准信号。基准信号通过运放u4按一定倍数放大给u3底下的r33,从而改变ac/dc电路的反馈基准值,进而实现ac/dc输出电压调节。当dc/dc1需求电压不够时,dc/dc1 pwm就会往上调,从而基准信号也往上调,进而ac/dc电压上调,以此达到ac/dc自动调节电压到输出口需求最高的电压;反之,dc/dc1的输入电压超出时,dc/dc1 pwm就会往下调,从而基准信号也往下调,进而ac/dc电压下调。dc/dc2也是一样的控制原理。

51.②

、q37的发射极的电压是vout1与vout2筛选的最大电压,而q37的基极的电压是由vout1经过r104、vout2经过r46后得到,当vout1与vout2相差较大时,r104和r46相当于分压,所以q37的基极和发射极的电压会产生使q37导通的压差,即此时q37是导通的,因此q38和q39的栅极电压被拉高而无法导通,即平衡稳定电路202没有启动;而当vout1与vout2电压相近时,q37的基极和发射极的电压接近,因此q37断开,因此q38和q39的栅极电压被拉低到地而导通,即平衡稳定电路202启动。平衡稳定电路202启动后,dc/dc1 pwm通过r174、r165、c4给dc/dc1的采样反馈值加一个反馈信号,dc/dc2 pwm通过r173、r166、c6给dc/dc2的采样反馈值加一个反馈信号。由于输出电压高的那一路升降压dc/dc电路的升压pwm信号高,所以叠加到采样反馈值上的反馈量就高,从而使得升降压dc/dc电路的升压pwm信号下调;输出电压低的那一路升降压dc/dc电路的pwm信号低,所以叠加到采样反馈值上的反馈量就低,从而使得升降压dc/dc电路的升压pwm信号往上调,最终就可以保证ac/dc电路的达到一个平衡稳定的输出电压。

52.需要说明的是,假设总共有m路升降压dc/dc电路,n路升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时启动平衡稳定电路202,m是大于等于2的正整数,n是小于等于m且大于等于2的正整数。如果n=m,则优选适用图5的电路进行拓展。如果是n小于m的情况,则优选利用单片机的m个引脚来监测m路升降压dc/dc电路的输出电压,进而比较是否存在如果存在n路升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压,如果存在,则利用单片机来启动平衡稳定电路202,比如控制m个叠加电路的开关管导通即可。比如说如果有三路升降压dc/dc电路,输出电压分别为5、5、9v,则不启动平衡稳定电路202,如果输出电压分别为5、9、9v,则启动平衡稳定电路202。

53.综上所述,本发明的多口电源电路中增加了自动跟踪输出最高电压电路,其将所有的所述升压pwm信号进行叠加处理整合成一个基准信号,处理后叠加到所述ac/dc电路的反馈基准值上,所以任意升压pwm信号改变则会叠加到ac/dc电路的反馈基准值,如此,ac/dc电路可以实现自动调节输出电压到多路输出口中需求最高的电压,有利于提高电源效率;而且,为了解决前述自动跟踪输出最高电压电路带来的多路升降压dc/dc电路中有二路以上输出电压接近且高于其他路升降压dc/dc电路的输出电压时存在振荡的问题,本发明

还配套设计了多路调控平衡稳定电路,用于将各路升降压dc/dc电路的所述升压pwm信号叠加到各路升降压dc/dc电路的采样反馈值上,以使得升压pwm信号高的升降压dc/dc电路的升压pwm信号调低、升压pwm信号低的升降压dc/dc电路的升压pwm信号调高,这样就可以避免自动跟踪输出最高电压电路在有二路以上升降压dc/dc电路的输出电压接近且高于其他路升降压dc/dc电路的输出电压时,产生震荡。

54.上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,这些均属于本发明的保护之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1