一种栅源电压保护电路的制作方法

1.本发明涉及总线驱动器技术领域,特别涉及总线驱动器的栅源电压保护。

背景技术:

2.总线驱动器是指连接在双向总线设备之间发送和接收信息的接口,rs485和rs232等接口芯片的设计均需遵循相应通讯协议电气特性标准的规定。例如根据485通讯接口标准协议的要求,总线的共模电压vcm范围在

‑

7v~12v范围,不但有正负方向的电压,且正负方向的电压都比接口芯片总线驱动器常规的最大栅极至源极电压的安全工作电压(通常工艺厂推荐安全工作范围为5v+10%)还要高。如图1所示为总线驱动器的常规电路原理图,图中vcc端口代表电源电压输入端口,vss端口代表接地端口(在图1中记为gnd),y/z端口代表总线端口,y/z端口输入上述共模电压vcm,y/z端口还输出差分电压,通常设计在上述

‑

7v~12v共模电压范围内的总线驱动器工作在三种状态:

3.当vcm>vcc时,y/z端口向上到vcc端口的支路防倒灌,y/z端口向下到vss端口的支路经短路检测后限流;

4.当vcm<vss时,y/z端口向下到vss端口的支路防倒灌,y/z端口向上到vcc端口的支路经短路检测后限流;

5.当vss<vcm<vcc时,y/z端口上下支路正常导通或关断工作,此时依据rs485标准的要求,驱动器在满载(54ω)下输出的差分电压需保持在1.5v以上。

6.图1中二极管dp和二极管dn均为用于防倒灌的常规二极管,当电源电压vcc由5v降低,如降低至3.3v时,为保证驱动器输出充裕的差分电压,二极管dp和二极管dn可以采用正向导通压降更低的肖特基二极管,或者采用基于逻辑控制其导通和关断状态的mos管来替代。

7.mos管p1和mos管n1分别为上下支路的开关管,当y/z端口为大于电源电压vcc的高压时,要求开关管p1和n1为高压管,满足漏极高压的需求。由于开关管p1的前级驱动电压来自内部电源,源极会接收来自y/z端口的共模电压vcm,这样其栅源压差也会存在高压情况。大多数主流工艺不提供栅源耐压较高的厚栅管,且即便提供厚栅管,一般它的导通阈值也会很高(1.5

‑

2v),低电源电压应用时会影响驱动能力,故不宜采用厚栅管。因此如何处理薄栅功率管p1的栅源钳位问题成为总线驱动器的一个设计难点。

8.针对总线驱动器开关管栅源电压钳位的处理,一篇公开号为cn107346969a,发明名称为《总线驱动器线路驱动器》的中国发明专利,公开了一种解决方案,如图2所示,其中mos管104和124分别对应图1中的上下防倒灌管dp和dn,mos管102和122则对应图1中的上下开关管,由于全部采用mos管做防倒灌和开关管,故四个mos管都需要做栅源耐压钳位,以其p开关管的钳位设计为例,采用电阻112,pmos管150,防倒灌二极管162和nmos管160构成。结合逻辑控制,设计当vcm>vcc时,s1点的电平被置高,即150导通且nmos管160关断,以此来阻断mos管102的源极高压向栅极走的电流支路,保持mos管102的栅源压差为0,以此解除mos管102栅极的击穿风险。但此种方案存在两个问题:

9.一是当驱动负载极轻或空载时,受y/z端口由键合线引起的寄生电感的影响,端口容性负载上存储的电压无处释放,而导致y/z端口的电压比vcc高,此时如果判定vcm>vcc而关断nmos管160进而关断mos管102,则会使该负载下输出的差分电压明显下降。故需选择一个合适的比vcc稍微高一点的阈值点去判定后才能确切地去关断nmos管160,但受外围寄生大小不确定的影响,这个阈值点很难找精准;

10.二是如果端口出现瞬态尖峰电压,检测电路无法及时响应,若短时间内nmos管160仍处于导通的状态,电阻112两端的压差值也会出现瞬间尖峰值,这对于mos管102的栅源也有很大的击穿风险。

技术实现要素:

11.有鉴于此,本发明要解决的技术问题是提供一种栅源电压保护电路,应用于总线驱动器,有效解决总线端口在高共模电平下驱动器上支路开关管栅源被击穿的风险问题,解决的同时既不影响轻载输出的差分电压值,也无需十分精准的总线端口电压与电源电压比较的阈值做判定,且在总线端口出现瞬态高压时,能保证功率管栅源压差被钳位在安全范围内。

12.本发明解决上述技术问题的技术方案如下:

13.一种栅源电压保护电路,应用于总线驱动器,所述的总线驱动器包括上支路开关管和下支路开关管,其特征在于,所述的栅源电压保护电路包括:第三二极管、齐纳二极管、第二低压pmos管、第二高压dnmos管、第三低压nmos管和第四低压nmos管;

14.所述的第二低压pmos管的漏极连接所述的第三二极管的阳极,所述的第二低压pmos管的源极用于输入电源电压,所述的第二低压pmos管的栅极连接所述的第二高压dnmos管的栅极;所述的第二高压dnmos管的漏极、所述的第三二极管的阴极和所述的齐纳二极管的阳极连接在一起后用于连接至所述的上支路开关管的栅极,所述的第二高压dnmos管的源极同时连接所述的第三低压nmos管的漏极和所述的第四低压nmos管的漏极;所述的第三低压nmos管的源极和所述的第四低压nmos管的源极连接在一起后用于接地;所述的齐纳二极管的阴极用于连接所述的上支路开关管的源极。

15.优选地,所述的第二高压dnmos管为能承受漏源间高压的薄栅型nmos器件。

16.优选地,所述的第三二极管采用肖特基二极管。

17.进一步地,所述的第三低压nmos管的宽长比大于所述的第四低压nmos管的宽长比。

18.优选地,所述的第三低压nmos管的宽长比为20um/1um,所述的第四低压nmos管的宽长比为1um/10um。

19.进一步地,还包括多只齐纳二极管,所述的多只齐纳二极管与所述的齐纳二极管串联后连接在所述的上支路开关管的栅极和漏极之间,所述的多只齐纳二极管与所述的齐纳二极管串联连接的方向与所述的上支路开关管的栅极和漏极的耐压程度相适应。

20.术语含义:

21.上支路:总线驱动器中y/z端口向上到vcc端口的支路;

22.下支路:总线驱动器中y/z端口向下到vss端口的支路。

23.本发明所提方案综合工作原理,解决了现有技术中的不足,其有益效果为通过在

驱动级pmos开关管栅源间的齐纳二极管结合逻辑控制驱动前级下支路上设计的低压nmos管,实现有效的功率管栅源钳位,解除了稳态和瞬态下的栅源击穿风险,具体如下:

24.1)通过逻辑控制第三低压nmos管303的导通和关断结合常通的第四低压nmos管304,使驱动正常工作时,较大尺寸的低压nmos管303工作在线性区导通,而不影响信号的正常传输速率;使驱动端口过压时,大尺寸的第三低压nmos管303被关断,击穿电流则将被小尺寸的第四低压nmos管304的饱和导通电流限制,最低可低至ua级别。

25.2)区别于现有技术,如专利cn107346969中的结构,会在判定端口过压后直接控制前级下拉支路关断而让pmos开关管102无法开启,导致空载差分输出电压下降。而本发明当端口发生过压,会判定生成逻辑信号s3=0来控制第三低压nmos管303被关断,但第四低压nmos管304仍导通,此时pmos开关管201管仍处于导通状态,不影响差分输出电压的值。

26.3)本发明对过压检测关断第三低压nmos管303的速度要求较低,当端口出现瞬态尖峰电压,检测电路可能无法及时响应,但第三和第四低压nmos管的导通让pmos开关管102管的栅源钳位起作用并始终保持在齐纳管压降电压值6.5v附近,无栅源击穿风险。

附图说明

27.图1为现有技术总线驱动器常规电路原理图;

28.图2为公开号为cn107346969a的现有技术中栅源电压保护电路在总线驱动器中应用的电路图;

29.图3为本发明第一实施例的栅源电压保护电路在总线驱动器中应用的电路图;

30.图4为本公发明第二实施例的栅源电压保护电路在总线驱动器中应用的电路图。

具体实施方式

31.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图和具体实施例对本发明作具体的介绍。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明,本发明的工作原理在有益效果处已详细分析,在此不赘述。

32.第一实施例

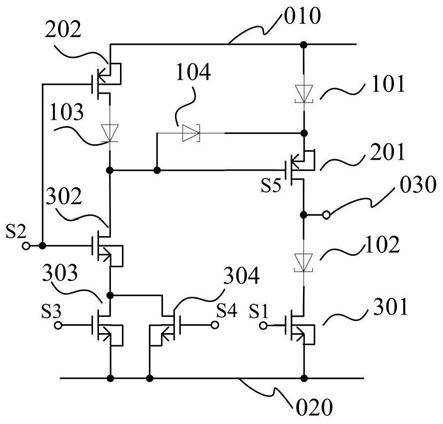

33.如图3所示为本发明第一实施例的栅源电压保护电路在总线驱动器中应用的电路图,本实施例的栅源电压保护电路包括:第三二极管103、齐纳二极管104,第二低压pmos管202、第二高压dnmos管302、第三低压nmos管303和第四低压nmos管304;所应用的总线驱动器包括:第一二极管101、第一高压dpmos管201、第二二极管102、第一高压dnmos管301和总线端口030(对应图1中的y/z端口);电路中的逻辑信号包括:第一逻辑信号s1、第二逻辑信号s2、第三逻辑信号s3、第四逻辑信号s4和第五逻辑信号s5。

34.vcc电源连接第一二极管101阳极和第二低压pmos管202的源极;第一二极管101阴极、第一高压dpmos管201的源极与齐纳二极管104的阴极连接在一起;齐纳二极管104的阳极、第一高压dpmos管201的栅极、第三二极管103的阴极和第二高压dnmos管302的漏极连接于同一个结点;第三二极管的阳极103与第二低压pmos管202的漏极连接;第二低压pmos管202和第二高压dnmos管302的栅极均接第二逻辑信号s2;第一高压dpmos管201的漏极和第二二极管102的阳极连接接至总线端口030;第二二极管102的阴极与第一高压dnmos管301的漏极连接,第一高压dnmos管301的源极和栅极分别接地和第一逻辑信号s1;第二高压

dnmos管302的源极与第三低压nmos管303和第四低压nmos管304的漏极连接于同一结点,第三低压nmos管303和第四低压nmos管304的源极均接地,第三低压nmos管303的栅极接第三逻辑信号s3,第四低压nmos管304的栅极接第四逻辑信号s4。

35.本实施例第一高压dpmos管201和第一高压dnmos管301均优选为能够承受漏源间高压且拥有低导通状态电阻的薄栅型pmos器件;第二高压dnmos管302优选为能承受漏源间高压的薄栅型nmos器件;第一二极管101、第二二极管102和第三二极管103存在正向导通压降且能防止倒灌电压,优选采用肖特基二极管;齐纳二极管104正向导通压降为0.7v左右,反向齐纳击穿稳压电压在5.8v附近;特别地设计第三低压nmos管303的宽长比较大,而第四低压nmos管304的宽长比较小,原因在于其中第三低压nmos管303在端口030电压处于0到vcc期间用于与第二高压dnmos管302一起配合实现驱动第一高压dpmos管201所需的传输速率,故尺寸需要足够大;而当端口030电压大于vcc电源电压时,第三低压nmos管303将处于关断状态,此时由尺寸较小的第四低压nmos管304的饱和电流限定整个支路可能存在的漏电电流,因此尺寸需设计足够小。

36.本实施例各逻辑信号案如下表1进行配置:

[0037][0038]

结合表1对本实施例的工作原理即发明目的的实现分析如下:

[0039]

(1)当总线端口030输入的共模电压处于0v至vcc之间时,此时总线驱动器处于正常工作状态

[0040]

第一二极管101与第一高压dpmos管201串联,第五逻辑信号s5控制201管的开启和关断,使得总线端口030节点被拉高到电源电压(降低一个二极管101的正偏压降)或者是处于高阻状态。第二二极管102与第一高压dnmos管201串联,第一逻辑信号s1控制301管的开启和关断,使得总线端口030节点被拉低至地电压(抬升一个二极管102的正偏压降)或者是处于高阻状态。高压dmos管201和301被互补驱动,使得任何时刻下,二者都不会同时导通。针对总线端口030输出的差分电压分两种情况进行讨论:

[0041]

在正常工作状态下,第三逻辑信号s3和第四逻辑信号s4均处于高电平状态,导通第三、第四低压nmos管303和304。

[0042]

假设希望总线端口030输出低电平,则第二逻辑信号s2被置为低电平,第二高压nmos管302将被关断,第二低压pmos管202导通经正偏的第三二极管103后将第五逻辑信号s5拉高而关断第一高压dpmos管201,第一逻辑信号s1被置为高电平,导通第一高压dnmos管301,总线端口030的电平被拉低至地电压(实际为抬升一个二极管102的正偏压降);

[0043]

假设希望端口030输出高电平,则逻辑信号s1被置低,第一高压dnmos管301关断,同时第二逻辑信号s2将被置为高电平,第二低压pmos管202关断,且第二高压nmos管302将被导通,由于第三逻辑信号s3和第四逻辑信号s4均被置为高电平,则第三低压nmos管303、第四低压nmos管304均导通,且此时第三低压nmos管303和第四低压nmos管304均处于线性区导通,设计时采用较大的w/l(w表示mos管的宽,l表示mos管的长)值的低压nmos管303,来得到较小的线性区阻抗,从而不会影响到信号的传输速率,dnmos管302、nmos管303和nmos管304的导通将第五逻辑信号s5拉低,vcc高电平经第一二极管101和导通的第一高压dpmos管201后,传递给端口030节点,使得总线端口030节点被拉高到电源电压(实际为降低一个二极管101的正偏压降)。

[0044]

(2)当总线端口030输入的共模电压小于或等于地电位(即小于或等于0)时防倒灌二极管102工作并阻止端口030向下支路的电流流动。而第一高压dpmos管201的导通需其源极或漏极的电压高于栅极电压一个阈值0.7v,而其栅极最低电压为0,因此第一高压dpmos管201将不会导通,其体二极管也不会正偏导通,因此端口030向下和向上的支路均无风险。

[0045]

(3)当总线端口030输入的共模电压大于或等于vcc时,此时发生过压,存在vcc带电或者不带电的情形。

[0046]

此时第一高压dpmos管201将处于导通状态,其源极接收了端口来自030的高电压值,第一二极管101将起到防倒灌作用阻止高压传递到电源端,但此时需重点关注201管的栅源电压的损坏风险。本发明采用齐纳二极管104、第三低压nmos管303和第四低压nmos管304及其相关的逻辑控制信号s3和s4来实现,使得不论在逻辑信号s2和s1处于何种状态下,高压dpmos管201的栅源电压都能被钳位在安全范围内,针对第二逻辑信号的设置分两种情况讨论如下:

[0047]

当第二逻辑信号s2为低电平,控制第二高压dnmos管302关断,则第一高压dpmos管201的源极高压没有可流通的电流支路可流动,其栅源压差将维持在0,无击穿风险;

[0048]

当第二逻辑信号s2为高电平,控制第二高压dnmos管302导通,逻辑信号s3为低电平关断了尺寸较大的第三低压nmos管303,仅由一直为vcc电平的逻辑信号s4保持第四低压nmos管304处于常通状态,此时高压dnmos管302和低压nmos管304串联导通且都将处于饱和区工作,端口030的高压经第一高压dpmos管201传递至其源极,经齐纳二极管104发生齐纳击穿,击穿后第一高压dpmos管201管的栅源电位将被齐纳二极管104钳位在5.8v的安全值下,击穿电流则将被小尺寸的第四低压nmos管304的饱和导通电流限制,最低可低至ua级别。举例但不限定第三低压nmos管303管的w/l=20um/1um,第四低压nmos管304管的w/l=1um/10um。这样即便端口030高压传递到开关管201的源极,其栅源压差也会被钳位在齐纳击穿电压下,201的栅源无击穿风险,同时齐纳二极管104齐纳击穿后的电流值也被低压nmos管304限制在很小的值。

[0049]

第二实施例

[0050]

图4所示为本发明第二实施例的栅源电压保护电路在总线驱动器中应用的电路图,图4示出了对图3的电路的修改,图3中的驱动器上支路防倒灌管101并不限定于二极管,本实施例采用图4中111部分的二极管连接形式的低压pmos管来代替也是可行的;图3中的第一高压dpmos的栅源之间所接的齐纳管104也并不限定接一个还是多个,如图四的222部分可根据201管栅极耐压程度选取串联齐纳二极管的个数和方向。

[0051]

本发明提供的栅源电压保护电路,通过在驱动器的上支路开关管栅源间并联一个齐纳二极管,结合逻辑控制驱动下支路开关管,实现有效的上支路开关管栅源钳位,解除了高共模电平下驱动器上支路开关管栅源被击穿的风险,解决的同时既不影响轻载输出差分电压值,也无需十分精准的总线端口电压与电源电压比较的阈值去做判定,且在总线端口出现瞬态高压时,能保证功率管栅源压差被钳位在安全范围内。

[0052]

以上显示和描述了本发明的基本原理、主要特征和优点。本行业的技术人员应该了解,以上驱动器的栅源电压保护电路和结构仅仅是示例性的,本领域的技术人员现在可以意识到,根据前面的描述,可以将此发明用于任意共模电压超过电源电压大小的总线端口,而并不限制于应用在示例中的由本方案中所示的逻辑信号控制的驱动结构中;上述实施例不以任何形式限制本发明,凡采用等同替换或等效变换的方式所获得的技术方案,均落在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1