一种支持MIPI的多协议IO模块的制作方法

一种支持mipi的多协议io模块

技术领域

[0001]

本发明涉及电源门控领域,尤其涉及一种支持mipi的多协议io模块。

背景技术:

[0002]

随着mipi协议使用日益广泛,fpga芯片上支持多协议的io单元,对mipi协议支持的需求越来越大。现有fpga里面是用的io多是支持多种协议多功能io,增加mipi协议的支持非常重要。

技术实现要素:

[0003]

为解决现有技术中存在的缺陷。

[0004]

本发明实施例提出了一种支持mipi的多协议io模块,基于常规io模块进行设计,该多协议io模块包括模拟io模块和数字io模块;其中,模拟io模块包括动态差分终端模块、输入选择器、单端接收模块、差分接收模块、单端发送模块和差分发送模块;数字io模块包括输入数据转换ilogic模块、输出数据转换ologic模块、第一动态选择器、第二动态选择器和三态控制模块。

[0005]

多协议io模块接收外部的动态终端控制信号;通过动态调节动态终端控制信号,实现mipi协议下高速度模式和低功耗模式间的动态转换。

[0006]

当处于mipi输入时,根据动态终端控制信号,动态差分终端模块内的电阻关闭,输入选择器选择单端接收模块的输出作为第一输入信号,第一动态选择器选择第一输入信号作为第二输入信号输出;或,动态差分终端模块内的电阻打开,输入选择器选择差分接收模块的输出作为第一输入信号,第一动态选择器选择由输入数据转换ilogic模块处理第一输入信号后输出的并行信号作为第二输入信号输出;

[0007]

当处于mipi输出时,根据动态终端控制信号,第二动态选择器选择内部输出信号作为第一输出信号,单端发送模块根据三态控制模块输出的三态控制信号打开,由打开的单端发送模块接收第一输出信号;或,第二动态选择器选择由输出数据转换ologic模块处理该内部输出信号得到的串行信号作为第一输出信号,差分发送模块根据三态控制模块输出的三态控制信号打开,由打开的差分发送模块接收第一输出信号;

[0008]

一个可实现的实施例中,数字io模块工作在第一电源电压下,第一电源电压为core域的电源电压;对单端接收模块增加第二电源电压;对差分接收模块增加第三电源电压。

[0009]

优选的,配置第一电源电压为0.9v;配置第二电源电压为1.2,1.8v或2.5v;配置第三电源电压为1.8v或2.5v。

[0010]

当处于mipi的高速度模式接收时,差分接收模块工作在第三电源电压下,保证性能要求;当处于mipi的低功耗模式接收时,单端接收模块工作在第二电源电压下。

[0011]

进一步优选的,当处于mipi的低功耗模式接收时,单端接收模块工作在第二电源电压下,配置第二电源电压为1.2v,进一步降低功耗。

[0012]

一个可实现的实施例中,差分发送模块基于lvds电路进行设计,包括第一nmos管(mn)、第一pmos管(mp)、第二nmos管(m0)、第三nmos管(m1)、第二pmos管(m2)、第三pmos管(m3)、第四nmos管(m4)、第五nmos管(m5);其中,

[0013]

mn为根据信号ndr开关的电流源,m0和m1的源极连接mn,m0的栅极根据信号dn0打开或关闭,m1的栅极根据信号dn1打开或关闭,m0和m1的漏极产生差分信号对pad0/pad1;mp为根据信号pdr开关的电流源,m2的栅极根据信号dp0打开或关闭,m3的栅极根据信号dp1打开或关闭,m2的漏极连接m0的漏极,m3的漏极连接m1的漏极;m4和m5的源极连接外部动态的第四电源电压,m4的栅极根据信号dn2打开或关闭,m5的栅极根据信号dn3打开或关闭,m4的漏极连接m0的漏极,m5的漏极连接m1的漏极。

[0014]

当dn2=0,dn3=0时,关闭m4和m5,使差分发送模块适应于lvds协议的功能。

[0015]

当dp0=1,dp1=1,pdr=1,ndr=1时,关闭mp、m2和m3,使差分发送模块适应于mipi协议的功能。优选的,在mipi工作在高速度模式时,动态调节dn0、dn1、dn2和dn3的电压为1.8v或2.5v;在mipi工作在低功耗模式时,动态调节dn0、dn1、dn2和dn3的电压为1.2v。

[0016]

优选的,第四电源电压通过内部的电源转换模块获得,或由低压线性稳压模块ldo提供。

[0017]

本申请实施例的优点在于:基于现有的支持lvds协议的io模块进行改造,在不改变原有电路的基础上,通过增加第一动态选择器和第二动态选择器,动态开关差分端接电阻以及动态调节差分发送模块,使常规io模块满足mipi工作的要求。

附图说明

[0018]

图1为现有技术的一种lvds发送模块电路;

[0019]

图2为本发明实施例的差分发送模块电路图;

[0020]

图3为现有技术的io模块示意图。

[0021]

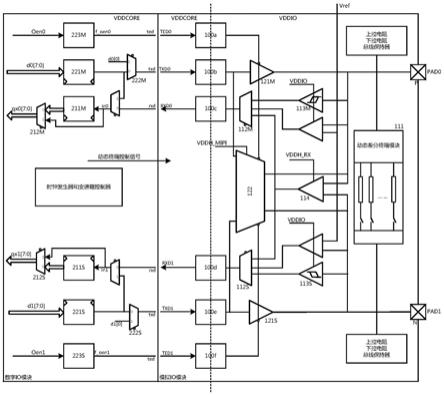

图4为本发明实施例的一种支持mipi的多协议io模块示意图。

具体实施方式

[0022]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0023]

现有的多协议io模块包括模拟io模块和数字io模块。其中的模拟io模块负责从io端口(pad0/pad1)上接收和发送多种协议的电平标准信号;数字io模块负责实现接收、发送信号的时钟同步,高速的串并转换,以及输入输出控制等功能。

[0024]

然而,对于现有的多协议io模块而言,如果应用于mipi协议。由于mipi信号工作时有多种模式,使得io模块需要根据模式的切换实现不同的电平标准。例如,在mipi的高速度hs模式下,输入输出是高速差分信号,输出信号幅度最低到150mv,输入信号幅度最低到70mv,共模电平在100~200mv;而在mipi的低功耗lp模式下,输入输出是低速的单端信号,电源电压是1.2v。

[0025]

因此,本发明实施例提供了一种基于现有多协议io模块进行改造的,增加支持

mipi的多协议io模块。该支持mipi的多协议io模块包括模拟io模块和数字io模块。其中,模拟io模块内包括动态差分终端模块、输入选择器、单端接收模块、差分接收模块、单端发送模块和差分发送模块;数字io模块内包括输入数据转换ilogic模块、第一动态选择器、输出数据转换ologic模块、第二动态选择器和三态控制模块。

[0026]

支持mipi的多协议io模块接收动态终端控制信号(dynamic termination control),根据该信号实现mipi下的高速度模式和低功耗模式间的转换。

[0027]

在输入时,输入选择器根据动态终端控制信号,选择来自单端接收模块或差分接收模块的输出信号作为第一输入信号;第一动态选择器根据动态终端控制信号,选择第一输入信号,或由输入数据转换ilogic模块处理第一输入信号得到的并行信号作为第二输入信号。

[0028]

如果mipi工作在高速度模式下,输入选择器选择差分接收模块的输出信号作为第一输入信号,动态差分终端模块内的电阻打开,输入数据转换ilogic模块接收第一输入信号,并将第一输入信号转换为n位并行信号输出,第一动态选择器选择该并行信号并作为第二输入信号。

[0029]

如果mipi工作在低功耗模式下,输入选择器选择单端接收模块的输出信号作为第一输入信号,动态差分终端模块内的电阻关闭,第一动态选择器选择第一输入信号作为第二输入信号。

[0030]

为更好的保证io模块接收时的信号质量。对模拟io模块中的单端接收模块增加第二电源电压vddio,差分接收模块增加第三电源电压vddh_rx。

[0031]

在一个可行的实施例中,通过配置使vddio为1.2v,vddh_rx为1.8v或2.5v。如果处于高速度模式,则采用vddh_rx;如果处于低功耗模式,则采用vddio。

[0032]

在输出时,第二动态选择器根据动态终端控制信号,选择内部输出信号或由输出数据转换ologic模块处理该内部输出信号得到的串行信号作为第一输出信号;根据三态控制模块输出的三态控制ted信号,控制的单端发送模块和差分发送模块的打开和关闭;由打开的单端发送模块或差分发送模块接收第一输出信号。

[0033]

如果mipi工作在高速度模式下,第二动态选择器选择由输出数据转换ologic模块处理内部输出信号得到的串行信号作为第一输出信号。差分发送模块根据三态控制信号打开,发送第一输出信号。

[0034]

如果mipi工作在低功耗模式下,第二动态选择器选择内部输出信号作为第一输出信号。单端发送模块根据三态控制信号打开,发送第一输出信号。

[0035]

由于mipi发送协议在高速度模式下,其共模电压典型值为0.2v,而现有的差分发送模块主要根据lvds协议进行设计。因此,可对现有的差分发送模块进行相应的改造,使其既可以面向lvds协议,也可以更好的应用在mipi工作时。

[0036]

如图1所示的lvds电路包括第一nmos管mn、第一pmos管mp、第二nmos管m0、第三nmos管m1、第二pmos管m2和第三pmos管m3。在此基础上增加第四nmos管m4、第五nmos管m5、以及连接m4和m5源极的第四电源电压vddh_mipi,得到如图2所示的差分发送模块。该差分发送模块中,mn为根据ndr开关的电流源,m0和m1的源极连接mn,m0的栅极根据信号dn0打开或关闭,m1的栅极根据信号dn1打开或关闭,m0和m1的漏极产生差分信号对pad0/pad1;mp为根据pdr开关的电流源,m2的栅极根据信号dp0打开或关闭,m3的栅极根据信号dp1打开或关

闭,m2的漏极连接m0的漏极,m3的漏极连接m1的漏极;m4和m5的源极连接vddh_mipi,m4的栅极根据信号dn2打开或关闭,m5的栅极根据信号dn3打开或关闭,m4的漏极连接m0的漏极,m5的漏极连接m1的漏极。

[0037]

通过配置不同的mos管栅极信号,可实现原有的lvds电路实现的差分发送模块的功能,还可以实现适用于mipi协议的差分发送模块的功能。

[0038]

当dn2=0,dn3=0时,关闭m4和m5,使该电路为原lvds电路差分发送模块的功能。

[0039]

当dp0=1,dp1=1,pdr=1,ndr=1时,关闭mp、m2和m3,使该电路等效m0、m1、m4和m5工作。此时,可以根据vddh_mipi调节差分信号对pad0/pad1的电压以及其产生的共模电压。在一个可行的实施例中,vddh_mipi由低压线性稳压模块提供。

[0040]

可动态控制信号dn0、dn1、dn2和dn3的电压,在mipi工作在高速度模式时,dn0、dn1、dn2和dn3的电压为1.8v或2.5v;在mipi工作在低功耗模式时,dn0、dn1、dn2和dn3的电压为1.2v。调节vddh_mipi保证m0、m1、m4和m5处于合理的工作范围,同时实现根据不同应用场景优化输出特性。

[0041]

在一个具体地实施例中,对如图3所示的现有的多协议io模块进行改造,增加用于实现支持mipi的相关模块,得到如图4所示的支持mipi的多协议io模块。该io模块包括模拟io模块和数字io模块。模拟io模块包括动态差分终端模块111、输入选择器112m、输入选择器112s、单端接收模块113m、单端接收模块113s、差分接收模块114、单端发送模块121m、单端发送模块121s、差分发送模块122以及用于实现core域和io域之间电平转换的各个电平转换模块100a~100f;数字io模块包括输入数据转换ilogic模块211m、输入数据转换ilogic模块211s、第一动态选择器212m、第一动态选择器212s、输出数据转换ologic模块221m、输出数据转换ologic模块221s、第二动态选择器222m、第二动态选择器222s、三态控制模块223m和三态控制模块223s。

[0042]

其中的差分发送模块122采用如图2所示的电路结构。

[0043]

当io模块工作在mipi协议时,配置io域的第二电源电压vddio为1.2v,第三电源电压vddh_rx为1.8或2.5v;配置dp0=1,dp1=1,pdr=1,ndr=1,使得mp、m2、m3关闭,此时差分发送模块122等效为m0,m1,m4,m5工作。

[0044]

io模块接收并根据动态终端控制信号,第四电源电压vddh_mipi,以及dn0、dn1、dn2、dn3信号电压实现mipi协议下高速度模式和低功耗模式的动态切换。

[0045]

在高速度模式下输入时,差分接收模块114在vddh_rx下工作。

[0046]

输入选择器112m根据动态终端控制信号,选择差分接收模块114的输出信号作为第一输入信号;动态差分终端模块111内的电阻打开;电平转换模块100c将io域的第一输入信号转换为core域的第一输入信号;输入数据转换ilogic模块211m接收core域的第一输入信号,并将其转换为n位并行信号输出;第一动态选择器212m根据动态终端控制信号,选择该并行信号,并将其作为第二输入信号输出。

[0047]

输入选择器112s根据动态终端控制信号,选择差分接收模块114的输出信号作为第一输入信号;动态差分终端模块111内的电阻打开;电平转换模块100c将io域的第一输入信号转换为core域的第一输入信号;输入数据转换ilogic模块211s接收core域的第一输入信号,并将其转换为n位并行信号输出;第一动态选择器212s根据动态终端控制信号,选择该并行信号,并将其作为第二输入信号输出。

[0048]

在低功耗模式下输入时,单端接收模块113m、单端接收模块113s和差分接收模块114在vddio下工作。

[0049]

输入选择器112m根据动态终端控制信号,选择单端接收模块113m的输出信号作为第一输入信号;动态差分终端模块111内的电阻关闭;电平转换模块100c将io域的第一输入信号转换为core域的第一输入信号;第一动态选择器212m根据动态终端控制信号,选择该core域的第一输入信号作为第二输入信号输出。

[0050]

输入选择器112s根据动态终端控制信号,选择单端接收模块113s的输出信号作为第一输入信号;动态差分终端模块111内的电阻关闭;电平转换模块100d将io域的第一输入信号转换为core域的第一输入信号;第一动态选择器212s根据动态终端控制信号,选择该core域的第一输入信号作为第二输入信号输出。

[0051]

在高速度模式下输出时,动态控制dn0、dn1、dn2、dn3信号,电压可为第三电压域。

[0052]

第二动态选择器222m根据动态终端控制信号,选择由输出数据转换ologic模块221m处理内部输出信号得到的串行信号作为第一输出信号;电平转换模块100b将core域的第一输出信号转换为io域的第一输出信号;电平转换模块100a将core域的三态控制信号转换为io域的三态控制信号;差分发送模块122根据io域的三态控制信号打开,并根据vddh_mipi使差分发送模块122正常工作,单端发送模块121m根据io域的三态控制信号关闭;差分发送模块122接收io域的第一输出信号。

[0053]

第二动态选择器222s根据动态终端控制信号,选择由输出数据转换ologic模块221s处理内部输出信号得到的串行信号作为第一输出信号;电平转换模块100e将core域的第一输出信号转换为io域的第一输出信号;电平转换模块100f将core域的三态控制信号转换为io域的三态控制信号;差分发送模块122根据io域的三态控制信号打开,并根据vddh_mipi使差分发送模块122正常工作,单端发送模块121s根据io域的三态控制信号关闭;差分发送模块122接收io域的第一输出信号。

[0054]

在低功耗模式下输出时,动态控制dn0、dn1、dn2、dn3信号,电压可为第二电压域。

[0055]

第二动态选择器222m根据动态终端控制信号,选择内部输出信号作为第一输出信号;电平转换模块100b将core域的第一输出信号转换为io域的第一输出信号;电平转换模块100a将core域的三态控制信号转换为io域的三态控制信号;差分发送模块122根据io域的三态控制信号关闭,单端发送模块121m根据io域的三态控制信号打开;单端发送模块121m接收io域的第一输出信号。

[0056]

第二动态选择器222s根据动态终端控制信号,选择内部输出信号作为第一输出信号;电平转换模块100b将core域的第一输出信号转换为io域的第一输出信号;电平转换模块100a将core域的三态控制信号转换为io域的三态控制信号;差分发送模块122根据io域的三态控制信号关闭,单端发送模块121s根据io域的三态控制信号打开;单端发送模块121s接收io域的第一输出信号。

[0057]

本发明公开的一种支持mipi的多协议io模块,基于现有的支持lvds协议的io模块进行改造,在不改变原有电路的基础上,通过增加第一动态选择器和第二动态选择器,动态控制动态差分终端模块,动态控制输入选择器,以及修改输出发送器电路,使常规io模块满足mipi工作的要求。

[0058]

以上的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细

说明,所应理解的是,以上仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1