一种用于PUF芯片的动态可编程仲裁器的电路结构的制作方法

一种用于puf芯片的动态可编程仲裁器的电路结构

技术领域

[0001]

本发明属于硬件安全防护领域,具体涉及一种用于puf芯片的动态可编程仲裁器的电路结构。

背景技术:

[0002]

puf(物理不可克隆函数,physical unclonable function)是一种新兴的硬件安全防护技术,该技术主要利用的是芯片制造过程中随机掺杂涨落和线边沿粗糙程度等不可控的工艺偏差,产生随机电学特性偏差,之后将电学特性偏差转换为数字信号,从而实现将一组激励信号映射为另一组唯一的、不可预测的响应信号。目前有很多种puf技术的实现方法,如基于存储器的存储特性实现的sram puf和dram puf方法,基于数字电路的信号延迟特性实现的仲裁器puf和环形振荡器puf方法。

[0003]

其中,仲裁器puf是一种常见的puf电路结构,主要包括延时电路和仲裁器电路,如附图1所示。仲裁器puf的基本原理是:同一个上升沿信号,通过两条完全对称的传输路径时,由于随机工艺偏差的存在,两条路径的上升沿信号传输快慢会有差别。仲裁器根据两个上升沿信号到达的顺序来判决输出,比如上面路径的上升沿信号先到达,则仲裁器判决输出结构为高电平,反之,仲裁器判决输出结果为低电平。

[0004]

根据应用场景的不同,仲裁器puf在硬件安全领域主要有两种用途,其一是用作芯片id,其二是用作真随机数发生器。用作芯片id时,要求当环境因素发生一定变化,多次施加同一激励,对应的puf响应也要尽可能保持稳定;用作真随机数发生器时,要求当环境因素没有发生变化,并且多次施加的是同一激励,对应的puf响应也是随机的。

[0005]

针对不同应用场景,仲裁器puf芯片的激励响应特性也有不同的要求,研究者们提出了很多专门的电路结构来提升puf响应的稳定性或增强puf响应的随机性,但是这些电路结构都只能实现单一功能,不能实现puf响应特性的动态调节,即不能将芯片id和真随机数发生器两种功能集成到同一块puf芯片当中,这将导致芯片硬件资源的利用效率较低,制造成本也比较大。

[0006]

因此,亟需一种用于puf芯片的动态可编程仲裁器的电路结构,能够实现将芯片id和真随机数发生器两种功能集中到一块puf芯片上。

技术实现要素:

[0007]

有鉴于此,本发明提供一种用于puf芯片的动态可编程仲裁器的电路结构,该电路结构应用于puf芯片,可实现将芯片id和真随机数发生器两种功能集成到同一块puf芯片当中。

[0008]

为达此目的,本发明采用以下技术方案:一种用于puf芯片的动态可编程仲裁器的电路结构,所述电路结构包括:

[0009]

sr锁存器,所述sr锁存器包括pmos管i:pm0、pmos管ii:pm1、pmos管iii:pm2、pmos管iv:pm3,nmos管i:nm0、nmos管ii:nm1、nmos管iii:nm2和nmos管iv:nm3;

[0010]

一级调节电路,所述一级调节电路包括多个nmos管;

[0011]

二级调节电路,所述二级调节电路包括第一子调节电路和第二子调节电路,所述第一子调节电路和第二子调节电路均包括多个nmos管对,每个nmos管对均由两个nmos管组成;所述第一子调节电路和第二子调节电路对称布置于一级调节电路两侧;

[0012]

所述pm0的源极、pm1的源极、pm2的源极和pm3的源极均连接电源;

[0013]

所述pm0的漏极、pm1的漏极、nm0的漏极、pm2的栅极和nm1的栅极电连接,形成第一节点a1;

[0014]

所述pm1的栅极、nm0的栅极、pm2的漏极、pm3的漏极及nm1的漏极电连接,形成第二节点a2;

[0015]

所述二级调节电路的每一个nmos管对中的第一nmos管的源极与该nmos管对中的第二nmos管的漏极连接;

[0016]

所述pm0的栅极、nm2的栅极及第一子调节电路中每个nmos管对的第一nmos管的栅极电连接,形成第三节点a3;

[0017]

所述nm0的源极、nm2的漏极、第一子调节电路中每个nmos管对的第一nmos管的漏极及一级调节电路中所有nmos管的漏极电连接,形成第四节点a4;

[0018]

所述pm3的栅极、nm3的栅极及第二子调节电路中每个nmos管对的第一nmos管的栅极电连接,形成第五节点a5;

[0019]

所述nm1的源极、nm3的漏极、第二子调节电路中所有nmos管对的第一nmos管的漏极及一级调节电路中所有nmos管的源极电连接,形成第一节点a6;

[0020]

所述nm2的源极、nm3的源极、二级调节电路中的每个nmos管对的第二nmos管的源极均接地;

[0021]

所述一级调节电路中所有nmos管的栅极以及二级调节电路的所有nmos管对的第二nmos管的栅极均连接控制信号。

[0022]

优选的,所述一级调节电路中所有nmos管的栅极连接的控制信号为高电平;所述二级调节电路的每个nmos管对的第二nmos管的栅极连接的控制信号为低电平。

[0023]

优选的,所述一级调节电路中所有nmos管的栅极连接的控制信号为低电平;所述二级调节电路的所有第二nmos管的栅极连接的控制信号为高电平。

[0024]

优选的,所述二级调节电路数位第一子调节电路与第二子调节电路中的nmos管对数量相同。

[0025]

本发明有益效果是:采用本发明公开的用于puf芯片的动态可编程仲裁器的电路结构,可以设计激励响应特性可调的仲裁器puf芯片,从而将puf芯片用作真随机数发生器和芯片id的两种功能集成在同一块芯片上,因此,采用本发明公开的电路结构可以实现puf芯片的一芯两用,提高了芯片硬件资源的利用效率,降低了制造成本。

附图说明

[0026]

图1为现有技术中的仲裁器puf电路结构示意图;

[0027]

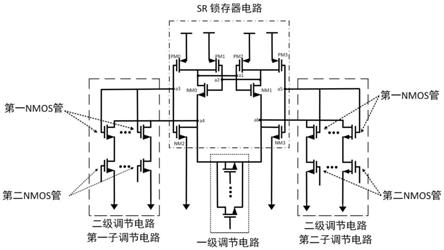

图2为本发明的用于puf芯片的动态可编程仲裁器的电路结构示意图;

[0028]

图3为二级调节电路设置为6对nmos管的用于puf芯片的动态可编程仲裁器的电路结构示意图;

[0029]

图4为本发明所述的仲裁器电路在两种工作模式下的输出概率曲线图。

具体实施方式

[0030]

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

[0031]

下面结合附图和具体实施例对本发明进行详细说明。

[0032]

实施例1

[0033]

如图2和图3所示的一种用于puf芯片的动态可编程仲裁器的电路结构,其中二级调节电路的每个子调节电路均设置为3个nmos管对,一级调节电路设置有4个nmos管。

[0034]

本实施例电路结构包括:sr锁存器,pmos管i:pm0、pmos管ii:pm1、pmos管iii:pm2、pmos管iv:pm3,nmos管i:nm0、nmos管ii:nm1、nmos管iii:nm2和nmos管iv:nm3;;

[0035]

一级调节电路,一级调节电路包括4个nmos管,分别命名为nm4、nm5、nm6和nm7;

[0036]

二级调节电路,二级调节电路的第一子调节电路和第二子调节电路均设置了3个nmos管对,每个nmos管对又包括两个nmos管;两个子调节电路对称布置于一级调节电路的两侧;

[0037]

其中第一子调节电路的每个nmos管对的第一nmos管分别命名为nm10、nm12、nm14,第二nmos管分别命名为nm11、nm13、nm15;第二子调节电路的每个nmos管对的第一nmos管分别命名为nm20、nm22、nm24,第二nmos管分别命名为nm21、nm23、nm25。

[0038]

其中,pm0的源极、pm1的源极、pm2的源极和pm3的源极均连接电源;

[0039]

pm0的漏极、pm1的漏极、nm0的漏极、pm2的栅极和nm1的栅极电连接,形成第一节点a1;

[0040]

pm1的栅极、nm0的栅极、pm2的漏极、pm3的漏极及nm1的漏极电连接,形成第二节点a2;

[0041]

二级调节电路中,nm10的源极与nm11的漏极连接,nm12的源极与nm13的漏极连接、nm14的源极与nm15的漏极连接,nm20的源极与nm21的漏极连接,nm22的源极与nm23的漏极连接、nm24的源极与nm25的漏极连接;

[0042]

pm0的栅极、nm2的栅极、nm10的栅极、nm12的栅极及nm14的栅极电连接,形成第三节点a3;

[0043]

nm0的源极、nm2的漏极、nm10的漏极、nm12的漏极、nm14的漏极、nm4的漏极、nm5的漏极、nm6的漏极和nm7的漏极电连接,形成第四节点a4;

[0044]

pm3的栅极、nm3的栅极、nm20的栅极、nm22的栅极及nm24的栅极电连接形成第五节点a5;

[0045]

nm1的源极、nm3的漏极、nm20的漏极、nm22的漏极、nm24的漏极、nm4的源极、nm5的源极、nm6的源极和nm7的源极电连接,形成第一节点a6;

[0046]

nm2的源极、nm3的源极、nm11的源极、nm13的源极、nm15的源极、nm21的源极、nm23的源极、nm25的源极均接地;

[0047]

nm4的栅极、nm5的栅极、nm6的栅极、nm7的栅极、nm11的栅极、nm13的栅极、nm15的

栅极、nm21的栅极、nm23的栅极、nm25的栅极均连接控制信号。

[0048]

当nm4、nm5、nm6和nm7的控制信号为高电平,设置nm11、nm13、nm15、nm21、nm23和nm25的控制信号为低电平时,这种配置条件下的仲裁器电路工作在随机模式,竞争响应曲线如附图4的实线所示,是一条对称的、平缓的曲线。在仲裁器电路的输入端再接入一个由多个延时单元所组成的多级延时电路模块,就构成了一个完整的仲裁器puf电路,该puf电路可以作为一个真随机数发生器。

[0049]

当nm4、nm5、nm6和nm7的控制信号为低电平时,设置nm11、nm13、nm15、nm21、nm23和nm25的控制信号为高电平时,这种配置条件下的仲裁器电路工作在稳定模式,竞争响应曲线如附图4的虚线所示,是一条对称的、陡峭的曲线。在仲裁器电路的输入端再接入一个由多个延时单元所组成的多级延时电路模块,就构成了一个完整的仲裁器puf电路,该puf电路可以用作芯片id。

[0050]

因此,本发明公开的用于puf芯片的动态可编程仲裁器的电路结构,可以用于设计激励响应特性可调的仲裁器puf芯片,从而将puf芯片用作真随机数发生器和芯片id的两种功能集成在同一块芯片上,实现了puf芯片的一芯两用,提高了芯片硬件资源的利用效率,降低了制造成本。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1