一种带记忆功能的防电源抖动电路的制作方法

1.本发明属于照明电路技术领域,涉及一种带记忆功能的防电源抖动电路。

背景技术:

2.消费类电子产品快速增长,技术发展越发快速,电子集成度越来越高,芯片成本越来越低。在此前提下,电子产品的外围元器件的成本在整个电子产品中成本的占比越来越大,例如,电阻、电容和电感等等。为达到降低成本的目的,业界在越来越多的消费类电子产品应用开发过程中,已经提出尽量减少或不用滤波电容。

3.随着手机、平板电脑和移动电源等便携式电子产品的普及,锂电池作为供电装置得到了广泛应用。然而,便携式电子产品由于便携性,在应用中存在碰撞和跌落等等异常状况,而供电电池在应用中大多数采用弹簧和顶针等接触式连接的,很容易造成电源短暂的断电情况发生。

4.本领域技术人员清楚,电源断电后,很容易造成芯片复位,尤其是在无电源滤波电容供电情况下,造成芯片工作的不连续性,造成用户的体验感差。

5.因此,如何应对电源防抖动设计应用需求范围广,获得适用性强且可靠的电源防抖动技术,成了业界一个急需探讨的问题。

技术实现要素:

6.为解决的上述技术问题,本发明提出一种全新的带记忆功能的防电源抖动电路及方法,其能够有效解决led恒流应用中,过温保护led闪烁或关断的问题,当芯片温度升高后,可通过降低输出电流从而达到芯片温度及led照明的平衡,从而避免出现led闪烁及关断的问题。

7.为实现上述目的,本发明的技术方案如下:

8.一种带记忆功能的防电源抖动电路,其包括逻辑锁存电路、时钟电路和内部电源模块;所述内部电源模块的输入端接电源vdd,其输出端接所述逻辑锁存电路的供电端;所述逻辑锁存电路在所述时钟电路的控制下进行数据的输入和输出;其中,当电源vdd掉电电源电压低于一预定阈值时,所述内部电源模块输出所述逻辑锁存电路的供电端v端所需的电源,将所述电源vdd掉电后的一个时期内进入所述逻辑锁存电路的数据锁存。

9.进一步地,所述内部电源模块电路包括一个p型mos管和电容c;所述p型mos管的漏极外接电源vdd,所述p型mos管的源极和栅极短接一起与所述电容c的一端连接,所述电容c的另一端接地,所述p型mos管的栅极接地。

10.进一步地,所述内部电源模块电路包括p型mos管和电容c;所述p型mos管的漏极外接电源vdd,所述p型mos管的源极和栅极短接一起与所述电容c的一端连接,所述电容c的另一端接地,所述p型mos管的栅极接一个分压电压。

11.进一步地,所述内部电源模块电路包括p型mos管mp1、p型mos管mp2、p型mos管mp3和一个电容c;所述p型mos管mp1的漏极外接电源vdd,所述p型mos管mp1的源极和栅极短接

一起与所述电容c的一端连接,所述电容c的另一端接地,所述p型mos管mp2的漏极接所述p型mos管mp3的源极,所述p型mos管mp3的漏极连接地端;所述p型mos管mp2的源极接v端。

12.进一步地,所述逻辑锁存模块包括rs触发器、d触发器、锁存器和/或ram。

13.进一步地,所述时钟电路包括一个与非门或一个或非门,用于在低压状态下或上电一段时间内阻止时钟clk信号变化。

14.进一步地,所述的带记忆功能的防电源抖动电路还包括解锁定电路,所述解锁定电路包括防抖检测单元、上升沿检测单元、锁存单元、导向器和或非门,用于在低压状态下或上电一段时间内阻止所述逻辑锁存电路复位,并确保所述逻辑锁存模块在正常工作时,输出复位信号。

15.从上述技术方案可以看出,本发明的带记忆功能的防电源抖动电路,其实现了电源vdd短暂断电情况下,可以使电信号具备记忆功能,确保数据的不流失;并且,本发明的电路结构简单,抗干扰能力强,可适用于多种无输入电容电路,应用广泛,实用性强。

附图说明

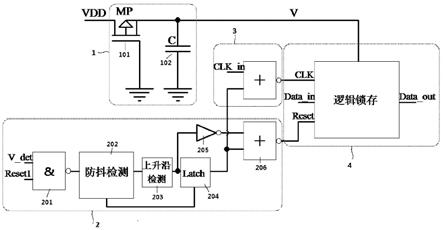

16.图1所示为本发明实施例中带记忆功能的防电源抖动电路结构的示意图

17.图2所示为本发明实施例中电源vdd短暂抖动为0v信号时,v端电压波形示意图

18.图3所示为本发明实施例中内部电源模块的电路示意图

具体实施方式

19.下面结合附图1

‑

3,对本发明的具体实施方式作进一步的详细说明。

20.请参阅图1,图1所示为本发明实施例中带记忆功能的防电源抖动电路的示意图。如图所示,本发明的带记忆功能的防电源抖动电路实现方式是不采用带记忆存贮单元模式,采用纯cmos电路的设计方法实现;该带记忆功能的防电源抖动电路包括逻辑锁存电路4、时钟电路3和内部电源模块1、解锁定电路2及供电端vdd。

21.所述内部电源模块1的输入端接电源vdd,其输出端接所述逻辑锁存电路4的供电端;所述逻辑锁存电路4在所述时钟电路的控制下进行数据的输入和输出;其中,当电源vdd掉电电源电压低于一预定阈值时,所述内部电源模块输出所述逻辑锁存电路的供电端所需的电源,将所述电源vdd掉电后的一个时期内进入所述逻辑锁存电路4的数据锁存。

22.请参阅图2,图2所示为本发明实施例中电源vdd短暂抖动为0v信号时,v端电压波形示意图。

23.本领域技术人员清楚,要使cmos电路保存信号,则必须要有一定的供电电压。在本发明的实施例中,该带记忆功能的防电源抖动电路,其包括延迟供电能力的供电模块,在电源vdd为0v或接近于0v时,由于p型mos处于截止工作状态,v端电压放电时间、放电曲线则由v端所接所有负载的大小决定,通过上述本发明的电路设计工作逻辑,可以实现v端在电源vdd失去供电能力情况下依然具有供电能力。

24.具体地,当外部电路处于放电状态时,v_det信号为“0”(该电压有外部电压检测电路决定),此时逻辑锁存电路4中reset被锁定,禁止复位信号产品,同时clk也被锁定,逻辑锁存电路4中的逻辑电路工作,降低v端所有模块所产生的负载电流,以达到延长保存信号所需电压的时间。

25.在电源vdd正常情况下,芯片重要信号通过data_in保存在逻辑锁存电路4,通过定时读取data_out信号来确定工作状态,以保证电路的逻辑时序。

26.在本发明的实施例中,所述解锁定电路2可以包括防抖检测单元202、上升沿检测单元203、锁存单元204、导向器205和或非门206,用于在低压状态下或上电一段时间内阻止所述逻辑锁存电路复位,并确保所述逻辑锁存模块在正常工作时,输出复位信号。较佳地,该导向器205可以是一个反相器。

27.具体地,当电源vdd出现如图2中波动时,v_det信号为“0”时逻辑锁存电路4中reset直接被锁定,该reset由或非门206输出。当v_det信号为“1”时,防抖检测电路202设定防抖时间(例如200ms,300ms),在此时间内reset依然被锁定,时钟电路clk同样也被锁定,待电源vdd稳定后,防抖检测电路202设定防抖时间到了,逻辑锁存电路4才能正常工作,以达到信号不被误触发的目的。

28.具体地,在本发明的实施例中,所述解锁定电路2可以包括但不限于与非门201、防抖检测202、上升沿检测203、锁存模块(latch)4及导向器205或非们206组合逻辑,其目的是在低压状态下或上电一段时间内输出reset“0”信号,阻止逻辑锁存电路4复位,确保逻辑锁存模块信息不变化。

29.请再参阅图2,图2中的所述内部电源模块电路包括一个p型mos管和电容c;所述p型mos管的漏极外接电源vdd,所述p型mos管的源极和栅极短接一起与所述电容c的一端连接,所述电容c的另一端接地,所述p型mos管的栅极接地。

30.具体地,解锁定电路2中与非门201、防抖检测202、上升沿检测203、锁存模块204及导向器205或非们206组成reset信号连接到逻辑锁存电路4;或非门3输出连接到逻辑锁存电路4和时钟clk输入端;逻辑锁存电路4的data_in及data_out是需要记忆保存的数据输入输出端。

31.此外,所述内部电源模块电路所包括p型mos管及内部电容连接方法,包括但不限于是一级连接,也有可能存在多级级联,请参阅图3,图3所示为本发明实施例中的电容调节电路的结构示意图。如图3所示,所述内部电源模块电路包括p型mos管mp1、p型mos管mp2、p型mos管mp3和一个电容c;所述p型mos管mp1的漏极外接电源vdd,所述p型mos管mp1的源极和栅极短接一起与所述电容c的一端连接,所述电容c的另一端接地,所述p型mos管mp2的漏极接所述p型mos管mp3的源极,所述p型mos管mp3的漏极连接地端;所述p型mos管mp2的源极接v端。另外,图3实施案例中mp2、mp3也可以用nmos或二极管来代替,分压mos管数量也可以是3个或多个mos管串联组成。

32.所述逻辑锁存模块4建议包括rs触发器、d触发器、锁存器和/或ram。所述时钟电路包括一个与非门或一个或非门,用于在低压状态下或上电一段时间内阻止时钟clk信号变化。

33.综上所述,本发明一种带记忆功能的防电源抖动电路实现了电源vdd短暂断电情况下,可以使电信号具备记忆功能,确保数据的不流失;并且,本发明的电路结构简单,抗干扰能力强,可适用于多种无输入电容电路,应用广泛,实用性强。

34.以上所述的仅为本发明的优选实施例,所述实施例并非用以限制本发明的专利保护范围,因此凡是运用本发明的说明书及附图内容所作的等同结构变化,同理均应包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1