双向电压电平转换器的制作方法

1.本发明总体涉及电压电平转换器领域。更具体地,并且不作为任何限制,该说明书涉及双向电压电平转换器,其具有由电压供应差控制的输出驱动器交错(staggering)。

技术实现要素:

2.一些实施例提供双向电压电平转换器,其能够以在3.6伏和0.65伏之间变化的电压输入工作。用于电压电平转换器的输出缓冲器结合输出信号的输出边沿控制,也称为交错,其主要用于在电压供应差很大时进行低到高电压转换。电压电平转换器感测输入和输出供应电压的差异,并在从低电压转换为高电压时为了较大电压差而接通交错电路,并且或在从高电压转换为低电压时为了低电压差而切断交错电路。

3.一些实施例包括双向电压电平转换器芯片,其包括用于耦合以接收用于第一电压域的第一供应电压的第一供应电压引脚;用于耦合以接收用于第二电压域的第二供应电压的第二供应电压引脚;用于耦合到接地平面以提供下轨的第三供应电压引脚;和电压电平转换器通道,其经耦合以在第一数据引脚上接收在第一电压域中工作的输入信号并在第二数据引脚上提供在第二电压域中工作的输出信号,电压电平转换器通道包括经耦合以提供输出信号的输出缓冲器,输出缓冲器包括:并联耦合在第二供应电压和输出信号之间的第一多个p型场效应晶体管(pfet),第一多个pfet具有标准阈值电压vt,第一多个pfet中的每个peet的栅极耦合到多个第一电阻器中的相应电阻器,多个第一电阻器中的相应电阻器串联耦合并经耦合以接收第一栅极控制信号;第一多个开关,第一多个开关中的每个开关与多个第一电阻器中的相应电阻器并联耦合;第一多个n型场效应晶体管(nfet),其并联耦合在输出信号和下轨之间,第一多个nfet具有标准vt,第一多个nfet中的每个nfet的栅极耦合到多个第二电阻器中的相应电阻器,多个第二电阻器中的相应电阻器串联耦合且经耦合以接收第二栅极控制信号;以及第二多个开关,第二多个开关中的每个开关与多个第二电阻器中的相应电阻器并联耦合,其中第一多个开关和第二多个开关经耦合以在第一供应电压大于或等于用于第二供应电压的相应vcci触发电压(trigger)时闭合,并且在第一供应电压小于相应vcci触发电压时断开。

4.一些实施例包括用于电压电平转换器的输出缓冲器,该电压电平转换器经耦合以将在具有第一供应电压的第一电压域中工作的输入信号转换成在具有第二供应电压的第二电压域中工作的输出信号。输出缓冲器包括并联耦合在第二供应电压和输出信号之间的第一多个p型场效应晶体管(pfet),第一多个pfet具有标准阈值电压(vt),第一多个pfet中的每个pfet的栅极耦合到多个第一电阻器中的相应电阻器,多个第一电阻器中的相应电阻器串联耦合并经耦合以接收第一栅极控制信号;第一多个开关,第一多个开关中的每个开关与多个第一电阻器中的相应电阻器并联耦合;第一多个n型场效应晶体管(nfet),其并联耦合在输出信号和下轨之间,第一多个nfet具有标准vt,第一多个nfet中的每个nfet的栅极耦合到多个第二电阻器中的相应电阻器,多个第二电阻器中的相应电阻器串联耦合并且经耦合以接收第二栅极控制信号;以及第二多个开关,第二多个开关中的每个开关与多个

第二电阻器中的相应电阻器并联耦合,其中第一多个开关和第二多个开关经耦合以在第一供应电压大于或等于用于第二供应电压的相应vcci触发电压时闭合并且在第一供应电压小于相应vcci触发电压时断开。

5.一些实施例包括操作电压电平转换器的方法,该方法包括提供体现在集成电路(ic)芯片上的电压电平转换器,电压电平转换器的每个输出缓冲器包括经耦合以提供输出信号交错的多个场效应晶体管和多个电阻器;将用于第一电压域的第一供应电压耦合到第一供应电压引脚;将用于第二电压域的第二供应电压耦合到第二供应电压引脚;耦合用于第一通道的第一数据引脚以接收在第一电压域中工作的第一信号;耦合用于第一通道的第二数据引脚以提供在第二电压域中工作的经转换的第一信号,其中电压电平转换器经耦合以确定第一供应电压是否大于或等于用于第二供应电压的第一vcci触发电压并且进一步经耦合以响应于确定第一供应电压大于或等于第一vcci触发电压而禁用第一通道的第一输出缓冲器中的交错。

附图说明

6.在附图的图中通过示例而非限制的方式示出描述的实施例,其中相同的附图标记指示相同的元件。对“一”或“一个”实施例的引用不一定是指相同的实施例,并且此类引用可意指“至少一个”。此外,当结合实施例描述特定特征、结构或特性时,此类特征、结构或特性可以结合其他实施例来实现,无论是否明确描述。如本文所用,术语“耦合(couple/couples)”是指间接或直接电连接,除非在可包括无线连接的“可通信耦合”中限定。因此,如果第一设备耦合到第二设备,则该连接可以是通过直接电连接,或通过经由其他设备和连接的间接电连接。

7.附图示出此描述的示例。各种优点和特征从以下具体实施方式和所附权利要求并参考附图得出,其中:

8.图1描绘根据实施例的输出缓冲器的示例;

9.图1a描绘根据实施例的用于禁用不必要交错的供应差感测电路的示例;

10.图1b描绘根据实施例的输出供应电压与输入供应电压的触发电压之间的关系图;

11.图2a描绘曲线图,其描绘具有和不具有供应差感测电路和相关联开关的电路的数据速率模拟;

12.图2b和图2c描绘根据实施例的在由图1的输出缓冲器处理的最大差下从第一电压域到第二电压域以及从第二电压域到第一电压域的信号的上升沿和下降沿;

13.图2d描绘根据实施例的由输出缓冲器提供的示例输出波形;

14.图3描绘根据实施例的操作电压转换器的方法;

15.图4示出其中可以利用根据描述的实施例的系统;

16.图5a和图5b分别描绘其中噪声在输出信号中引起非单调行为的波形的上升沿和波形的下降沿;和

17.图6描绘可以将实施例并入其中的双向电压电平转换器的一个通道中的电路的示例。

具体实施方式

18.现在将参考附图详细描述具体实施例。在权利要求的范围内,在所描述的实施例中的修改是可能的,并且其他实施例也是可能的。

19.图4描绘系统400,其中双向电压电平转换器芯片404经耦合以转换在控制器402和系统406之间传递的信号的电压电平。第一供应电压引脚vcc1用于耦合到第一电压域,其使用由控制器402使用的第一供应电压vcca;第二供应电压引脚vcc2用于耦合到第二电压域,其使用由系统406使用的第二供应电压vccb;并且第三供应电压引脚gnd用于耦合第三供应电压(其可以是接地平面),以便提供下轨。在所示的实施例中,双向电压电平转换器芯片404还具有用于转换的四个通道,但是双向电压电平转换器芯片404也可以具有八个、十六个或任何数量的通道。数据引脚a1和数据引脚b1耦合到第一通道;数据引脚a2和数据引脚b2耦合到第二通道;数据引脚a3和数据引脚b3耦合到第三通道;并且数据引脚a4和数据引脚b4耦合到第四通道。

20.在此实施例中,第一方向引脚dirl、第二方向引脚dir2、第三方向引脚dir3和第四方向引脚dir4均经耦合以指示相应通道上的信息流方向。在其他实施例中,方向引脚可以与一组两个或更多个通道相关联。将方向引脚中的任一个耦合到第一供应电压vcca指示在相应通道或通道组上的信息流是从第一电压域到第二电压域,而将方向引脚中任一个耦合到第三供应电压(例如,下轨)指示相应通道或通道组上的信息流是从第二电压域到第一电压域。在所示实施例中,具有数据引脚a1和数据引脚b1的第一通道、具有数据引脚a2和数据引脚b2的第二通道以及具有数据引脚a3和数据引脚b3的第三通道经耦合以处理从第一电压域流动到第二电压域的数据,而具有数据引脚a4和数据引脚b4的第四通道处理从第二电压域流动到第一电压域的信息。

21.由于随着半导体器件稳定地缩小,半导体器件工作的电压已经变得更低,因此控制器402和系统406工作的电压可以取决于芯片的创建时间。给定本领域的当前状态,第一供应电压vcca和第二供应电压vccb可以按照数量级变化。例如,控制器402和系统406中的一个可以使用3.6v的电压而另一个使用0.65v的电压。提供在这两个极端之间转换信号的能力给电路设计带来许多挑战。

22.一个此类挑战在图5a和图5b中示出,它们分别示出来自电压转换器的输出信号500a的上升沿和输出信号500b的下降沿。在图5a、图5b中的每个中,输出信号500a、500b的单调性分别被图中圈出的毛刺505a、505b破坏。例如在输出信号500a、500b中看到的毛刺通常是由电压转换器引起的,电压转换器转换在低电压域(例如,0.65v)和高电压域(例如,3.6v)之间的在两个方向上传递的信号。随着多个信号通过电压电平转换器芯片(诸如双向电压电平转换器芯片404),彼此靠近的信号线之间的寄生相互作用引起由低到高转换产生的噪声耦合到来自正在执行从高到低转换的电压转换器的信号。当信号的上升或下降阶段期间出现毛刺时,接收器可能错误解释信号并导致误差。

23.在说明最坏情况的一个示例中,图4的控制器402具有0.65v的第一供应电压vcca并且系统406具有3.6v的第二供应电压vccb。第一通道、第二通道和第三通道用于将信号从a转换为b,即0.65v至3.6v,并且第四通道用于将信号从b转换为a,即3.6v至0.65v。第一通道、第二通道和第三通道从第二供应电压vccb汲取大电流。此大电流将产生供应弹跳(supply bounce)和接地弹跳(ground bounce)两者。如果所有通道共享相同接地和供应电

压,则提供从3.6v到0.65v的转换的第四通道的输出会受到来自其他通道的噪声耦合的影响。此噪声在信号的上升或下降阶段期间的出现接着导致图5a和图5b中看到的毛刺类型,这反过来可以导致信号的错误解释。

24.图6描绘用于在a电压域和b电压域之间转换信号的示例电压电平转换器通道600的一半,并且取自2018年7月17日以christopher michael graves的名义发布的美国专利no.10,027,325,其以全文引用的方式并入本文。如图6所示的电路将信号从a电压域转换到b电压域,而相同的电路(未具体示出)经耦合以将信号从b电压域转换到a电压域。一次只有构成电压电平转换器通道600的这两个电路中的一个处于活动状态,而非活动电路的输出缓冲器处于高阻抗模式;转换的方向性由如参考图4描述的相应方向引脚的电压耦合确定。

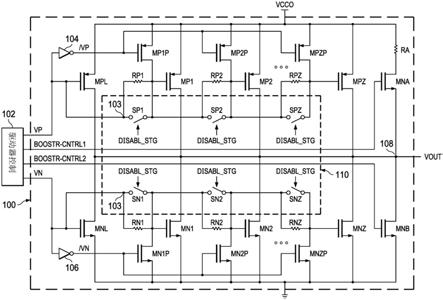

25.以下描述提供图6的电路的快速概览;另外的细节可以在上述专利中找到。电压电平转换器通道600包括输入缓冲电路605、电压转换器电路610、栅极控制电路615、输出缓冲电路620和启用/禁用控制电路625。输入缓冲电路605接收输入信号vin,产生第一控制信号s1和第二控制信号s2,并且是由处于“a”电压域中的第一供应电压vcca供电的电路中的唯一一个。第一控制信号s1和第二控制信号s2用于驱动电压转换器电路610中的晶体管以提供输出控制信号s3t,其目前在“b”电压域中工作。在栅极控制电路615中,第一控制信号s1和第二控制信号s2和输出控制信号s3t都用于驱动此电路中的晶体管以产生传递给输出缓冲电路620的栅极控制信号vp、vn。栅极控制信号vp和vn控制用于提供输出信号vout的输出晶体管的栅极。启用/禁用电路625提供启用信号en1、en2,其确保栅极控制信号vp和vn在需要时可以将输出缓冲电路置于高阻抗状态。

26.由于在宽电压范围内提供电压转换所固有的困难,电压电平转换器通道600被设计为提供并联阈值电压(vt)架构,其中低vt晶体管与标准vt晶体管并联耦合。尽管没有特别标记,与标准vt晶体管并联耦合的低vt晶体管的示例可以在输入缓冲电路605、电压转换器电路610和栅极控制电路615中的每个中看到,其中并联耦合的两个晶体管均由输入信号vin、第一控制信号s1、第二控制信号s2或输出控制信号s3t中的任一个控制。在输出缓冲电路620中,两个p型晶体管,即低vt p型场效应晶体管(pfet)mpl和标准vt晶体管mps,并联耦合在第二供应电压vccb和输出信号vout之间,并且每个都接收栅极控制信号vp。类似地,两个n型晶体管,即低vt n型场效应晶体管(nfet)mnl和标准vt nfet mns并联耦合在输出信号vout和下轨之间,并且每个都接收栅极控制信号vn。

27.耦合到用于转换的特定电路的电压确定是标准vt晶体管还是低vt晶体管对转换贡献最大。例如,当0.65v的电压用于电路的供应电压时,标准vt晶体管一般不导通,而低vt晶体管占主导。当3.6v的电压用于电路的供应电压时,低vt晶体管无法通过足够电流来提供必要的输出电压,因此在此情况下标准vt晶体管占主导。

28.2018年12月7日以amar kanteti和ankur kumar singh的名义提交的共同未决的美国专利申请第16/213,230号(以下称为'230申请),名称为《具有降噪和数据速率改进的双向电平转换器(bidirectional level translator having noise reduction and improved data rate)》,在此以全文引用方式并入本文。'230申请描述作为电压电平转换器通道600的输出缓冲电路620的修改的输出缓冲器。修改的输出缓冲器包括标准vt nfet和p型场效应晶体管(pfet)的交错组合,其通过升压改善高电压输出上的噪声,这改善单调行为并可以改善低电压输出的数据速率。

29.'230申请中提供的电路在来自第一电压域的第一供应电压和来自第二电压域的第二供应电压之间的差很大(例如第一供应电压vcca为3.6v且第二供应电压vccb为0.65v)的情况下在提供单调输出方面有效。申请人关于'230申请确定的一个问题是每个输入/输出电压组合都存在交错,即使在较低供应电压差异下不需要交错时,例如,当一个供应电压为1.8v且第二供应电压为3.6v时。当电压差较低时,由较高输出通道产生的接地噪声可以被较低电压输出通道容忍。然而,无论供应电压差如何,交错的使用都降低所有供应电压范围的数据速率。

30.图1示出输出缓冲器100的电路图,其提供对'230申请的输出缓冲器的进一步修改,该修改可以在不需要交错时禁用交错。对于输出缓冲器100作为其一部分的通道,输出供应电压vcco代表输出信号vout的上供应电压,而下文提到的vcci是图6所示的输入信号vin的上供应电压。例如,给定图4中方向引脚的耦合,第一供应电压vcca提供输入供应电压vcci,并且第二供应电压vccb为第一通道、第二通道和第三通道提供输出供应电压vcco。类似地,第二供应电压vccb提供输入供应电压vcci,并且第一供应电压vcca为第四通道提供输出供应电压vcco。

31.输出缓冲器100包括低vt pfet mpl和具有标准vt的第一多个pfet mp1

‑

mpz。低vt pfet mpl和第一多个pfet mp1

‑

mpz中的每个并联耦合在输出供应电压vcco和输出信号vout之间。第一多个pfet mp1

‑

mpz的栅极各自耦合到多个第一电阻器rp1

‑

rpz中的相应电阻器,并且多个第一电阻器rp1

‑

rpz串联耦合在节点103和pfet mpz的栅极之间。提供第一多个开关sp1

‑

spz,其中第一多个开关sp1

‑

spz中的每个与多个第一电阻器rp1

‑

rpz中的相应电阻器并联耦合,使得当第一多个开关sp1

‑

spz中的每个闭合时,多个第一电阻器rp1

‑

rpz中的相应电阻器被绕过。第一多个开关sp1

‑

spz通过禁用

‑

交错信号disabl_stg而被控制。

32.在输出缓冲器100的操作期间,驱动器控制102将第一栅极控制信号vp和第二栅极控制信号vn提供到输出缓冲器100。第一升压器控制信号boostr

‑

cntrl1和第二升压器控制信号boostr

‑

cntrl2也被示为由驱动器控制102提供;在一个实施例中,这些升压器控制信号是来自输入缓冲电路605的第一控制信号s1和第二控制信号s2。第一栅极控制信号vp被提供给低vt pfet mpl的栅极和第一节点103。在一个实施例中,当禁用

‑

交错信号disabl_stg为低时,第一多个开关sp1

‑

spz断开并且第一栅极控制信号vp从第一节点103依次传递通过多个第一电阻器rp1

‑

rpz中的每个并到达第一多个pfet mp1

‑

mpz中的相应晶体管。随着第一栅极控制信号vp传递通过多个第一电阻器rp1

‑

rpz中的每个,每个电阻器引入小的延迟,例如一纳秒,使得第一多个pfet mp1

‑

mpz的栅极以交错间隔导通。此交错降低由输出缓冲器100的切换引起的噪声。在相同实施例中,当禁用

‑

交错信号disabl_stg为高时,第一多个开关sp1

‑

spz闭合并且第一栅极控制信号vp从第一节点103传递通过第一多个开关sp1

‑

spz中的每个到第一多个pfet mp1

‑

mpz中的相应晶体管。因为没有由传递通过顺序电阻器引起的延迟,所以第一多个pfet mp1

‑

mpz中的每个同时导通,从而提供更快的信号。

33.第二多个pfet mp1p

‑

mpzp各自耦合在输出供应电压vcco和第一多个pfet mp1

‑

mpz中的相应一个的栅极之间,以充当可以快速关断第一多个pfet mp1

‑

mpz的上拉晶体管。反相器104提供第一栅极控制信号/vp的反相以提供控制第二多个pfet mp1p

‑

mpzp的栅极的信号。

34.输出缓冲器100还包括低vt nfet mnl和具有标准vt的第一多个nfet mn1

‑

mnz。低vt nfet mnl和第一多个nfet mn1

‑

mnz中的每个并联耦合在输出信号vout和下轨之间。第一多个nfet mn1

‑

mnz的栅极各自耦合到多个第二电阻器rn1

‑

rnz中的相应电阻器,并且多个第二电阻器rn1

‑

rnz串联耦合。提供第二多个开关sn1

‑

snz,其中第二多个开关sn1

‑

snz中的每个与多个第二电阻器rn1

‑

rnz中的相应电阻器并联耦合,使得当第二多个开关sn1

‑

snz中的每个闭合时,多个第二电阻器rn1

‑

rnz中的相应电阻器被绕过。第二多个开关sn1

‑

snz也由禁用

‑

交错信号disabl_stg控制。

35.在输出缓冲器100的工作期间,驱动器控制102将第二栅极控制信号vn提供到低vt nfet mnl的栅极和第二节点105。在一个实施例中,当禁用

‑

交错信号disabl_stg为低时,第二多个开关sn1

‑

snz断开并且第二栅极控制信号vn从第二节点105依次传递通过多个第二电阻器rn1

‑

rnz中的每个并到达第一多个nfet mn1

‑

mnz的相应栅极。随着第二栅极控制信号vn传递通过多个第二电阻器rn1

‑

rnz中的每个,每个电阻器再次引入小的延迟,使得第一多个nfet mn1

‑

mnz的栅极以交错间隔导通。在相同实施例中,当禁用

‑

交错信号disabl_stg为高时,第二多个开关sn1

‑

snz闭合并且第二栅极控制信号vn从第二节点105依次传递通过第二多个开关sn1

‑

snz中的每个到第一多个nfet的栅极。因为没有由传递通过顺序电阻器引入的延迟,所以第一多个nfet mn1

‑

mnz中的每个同时导通,从而提供更强信号。

36.第一多个开关sp1

‑

spz和第二多个开关sn1

‑

snz一起形成交错

‑

启用

‑

禁用电路110,其与提供禁用

‑

交错信号disabl_stg的电路结合来提供必要时利用输出信号vout的交错,但在其他时间绕过交错的能力。交错

‑

启用

‑

禁用电路110的控制关于图1a进行描述,其描绘提供禁用

‑

交错信号disabl_stg的电路的实施例。

37.继续图1,第二多个nfet mn1p

‑

mnzp各自耦合在第一多个nfet mn1

‑

mnz中的相应一个的栅极与下轨之间以充当可以迅速地关断第一多个nfet mn1

‑

mnz的下拉晶体管。反相器106提供第二栅极控制信号/vn的反相以提供控制nfet mn1p至mnzp的栅极的信号。

38.第三电阻器ra在输出供应电压vcco和下轨之间与第一升压器nfet mna和第二升压器nfet mnb串联耦合,其中点108在nfet mna的源极和nfet mnb的漏极之间耦合以帮助提供输出信号vout。第一升压器nfet mna和第二升压器nfet mnb都是标准vt晶体管。驱动器控制电路102提供第一栅极控制信号vp和第二栅极控制信号vn两者,并且还提供两个附加升压器控制信号boostr

‑

cntrl1、boostr

‑

cntrl2,它们分别提供给第一升压器nfet mna和第二升压器nfet mnb的栅极。

39.与在输出供应电压vcco的电压域中产生的第一栅极控制信号vp和第二栅极控制信号vn不同,第一升压器控制信号boostr

‑

cntrl1和第二升压器控制信号boostr

‑

cntrl2在输入供应电压vcci(例如图6中的第一供应电压vcca)的电压域中产生。在一个实施例中,升压器控制信号boostr

‑

cntrl1、boostr

‑

cntrl2是来自输入缓冲电路605的第一控制信号s1和第二控制信号s2。如果输出缓冲器100被禁用,即置于高阻抗模式,则升压器信号boostr

‑

cntrl1、boostr

‑

cntrl2具有二进制低值。

40.当输出缓冲器100正在接收高的输出供应电压vcco时,例如3.6v,而输入供应电压vcci为低(例如0.65v)时,交错被启用并且第一多个pfet mp1

‑

mpz和第一多个nfet mn1

‑

mnz工作以减少供应电压上和下轨上的噪声。低vt pfet mpl和低vt nfet mnl完全导通,但没有传递足够的电流来显著贡献于输出信号vout。同时,由于第一升压器nfet mna和第二

升压器nfet mnb受第一升压器控制信号boostr

‑

cntrl1和第二升压器控制信号boostr

‑

cntrl2控制,它们是使用输入供应电压vcci产生的,因此升压器nfet mna、mnb将不导通,因为相应的控制信号没有超过第一升压器nfet mna和第二升压器nfet mnb的阈值电压。在输入供应电压vcci和输出供应电压vcco之间的差异不大的类似示例中,例如输入供应电压vcci为1.2v且输出供应电压vcco为3.6v,升压器nfet mna和mnb,其是标准vt晶体管,可以接通,但来自升压器nfets mna和mnb的电流将不足以改变输出状态。

41.在相反的情况下,当输入供应电压vcci为高(3.6v)且输出供应电压vcco为低(0.65v)时,第一多个pfet mp1

‑

mpz和第一多个nfet mn1

‑

mnz将不会导通;低vt pfet mpl和低vt nfet mnl将导通,并且第一升压器nfet mna和第二升压器nfet mnb将非常快速地导通,因为它们具有强大升压器控制信号boostr

‑

cntrl1、boostr

‑

cntrl2。通过快速切换第一升压器nfet mna和第二升压器nfet mnb,接收到的噪声不出现在信号的上升沿或下降沿上。

42.尽管如前面段落中描述的较高电压信号的交错可以避免许多噪声问题,但是交错也降低数据速率并增加传播延迟。对于可以耦合到结合输出缓冲器100的电压转换器的高电压差,噪声和数据速率之间的折衷是必要的,但是当电压差较小时,不必要地降低数据速率不合需要。因此,确定在不需要时应禁用交错。为此,根据如下表1确定各种电压的接地弹跳幅度(其提供伴随噪声)和峰值接地电流:

43.表1

44.vcco接地弹跳接地峰值电流3.60.66120ma3.30.6107ma30.5591ma2.70.577.4ma2.40.4364ma

45.随着输出电压的降低,击穿电流(shoot through current)和接地弹跳都下降,从而减少对交错的需要。如表1所示,将供应电压降低10%也会将接地弹跳降低10%。确定可以为每个输出电压确定vcci触发电压,即,对于每个输出电压,可以确定不需要交错的最小输入电压。如果到转换器通道的输入电压处于或高于vcci触发电压,则将使用多个第一开关sp1

‑

spz和多个第二开关sn1

‑

snz禁用针对该通道的交错。

46.图1a描绘供应差感测电路100a的示例,如果特定通道的输入供应电压vcci大于或等于对应输出供应电压vcco的vcci触发电压,则该供应差感测电路100a可以提供用于禁用交错的禁用

‑

交错信号disabl_stg。在此实施例中,供应差感测电路100a为反相器电路,其由具有标准电压阈值的p型金属氧化物硅(pmos)晶体管、具有低电压阈值的pmos晶体管和具有低电压阈值的n型金属氧化物硅(nmos)晶体管组成。具有标准电压阈值的第一多个堆叠pmos晶体管122在输出供应电压vcco和下轨vss之间与具有低电压阈值的第一多个堆叠nmos晶体管124串联耦合。第一多个堆叠pmos晶体管122的栅极和第一多个堆叠nmos晶体管124的栅极均接收输入供应电压vcci。第一多个堆叠pmos晶体管122和第一多个堆叠nmos晶体管124之间的点经耦合以提供禁用

‑

交错

‑

条信号disabl

‑

stg

‑

bar。具有低电压阈值的第二多个堆叠pmos晶体管126也在输出供应电压和下轨(此处示出为vss)之间与具有低电压

阈值的第二多个堆叠nmos晶体管128串联耦合。禁用

‑

交错

‑

条信号disabl

‑

stg

‑

bar提供到第二多个堆叠pmos晶体管126和第二多个堆叠nmos晶体管128的栅极,而第二多个堆叠pmos晶体管126和第二多个堆叠nmos晶体管128之间的点经耦合以提供禁用

‑

交错信号disabl_stg。

47.通常构造的反相器电路(即所有晶体管具有相同的标称阈值电压)将在两个轨之间在电压差的中点处在低状态和高状态之间切换。在图1a中,通过使用标准vt pmos晶体管和低vt nmos晶体管,将低状态和高状态之间的转换转移以反映vcci触发电压vtrigger,其可用于提供禁用

‑

交错信号disabl_stg以闭合第一多个开关sp1

‑

spz和第二多个开关sn1

‑

snz并绕过输出信号vout的交错。vcci触发电压vtrigger基于以下等式:

[0048][0049]

其中vdd是输出缓冲器100中使用的输出供应电压vcco,

[0050]

vtrigger是输入供应电压vcci,在该电压下可以关闭交错,

[0051]

vtn和vtp分别是低vt nmos晶体管和标准vt pmos晶体管的阈值电压,并且

[0052]

p型晶体管的β(βp)和n型晶体管的β(βn)由以下等式定义:

[0053]

以及

ꢀꢀꢀꢀꢀꢀꢀ

等式2

[0054][0055]

其中μn和μp分别是nmos和pmos掺杂剂的迁移率,

[0056]

cox是栅极氧化物的电容,

[0057]

wn和wp分别是n型和p型晶体管的宽度,并且

[0058]

ln和lp分别是n型和p型晶体管的长度。

[0059]

图1b描绘曲线图100b,其示出输出供应电压vcco和对应vcci触发电压vtrigger之间的对应关系,而下表2提供输出缓冲器100的输出供应电压vcco和对应vcci触发电压vtrigger的具体值。如果相应输入供应电压vcci处于或高于vcci触发电压vtrigger,则可以安全地关闭或绕过交错,而不会影响整体噪声:

[0060]

表2

[0061]

vcco(v)vcci触发电压(v)3.61.4173.31.331.182.71.0042.40.8862.10.7681.80.624

[0062]

图2a展示其中交错是不必要的情况并示出可导致的数据速率损失。两个输出信号均针对1.8v输入电压和3.3v的输出信号进行记录,其中输入数据速率为500mbps。输出信号202由总是应用交错的输出缓冲器产生;输出信号202具有350mbps的输出数据速率。相比之

下,输出信号204由在不需要时关闭交错的输出缓冲器产生。从表2可以确定,对于3.3v的输出电压vout,1.8v的输入电压vin高于vcci触发电压vtrigger的1.3v值,因此在这种情况下关闭交错,且达到最大输出数据速率500mbps。

[0063]

虽然当输入和输出电压相对靠近在一起时输出缓冲器100能够提供最大输出数据速率,但是当电压差最大时输出缓冲器100也能够为两个方向的信号提供干净的信号。图2b和图2c是用具有等于3.6v的第一供应电压vcca和等于0.65v的第二供应电压vccb的电压转换器产生的。输出信号212来自在a到b方向上工作的单个通道,使得输出电压在0.65v域中工作。输出信号214代表来自其余三个通道的三个输出信号,它们都在b到a方向上工作,使得输出信号214在3.6v域中工作。图2b示出这些信号的上升沿且图2c示出相同信号的下降沿。即使具有大电压差,也观察到输出信号212、214的单调行为。图2d描绘在0.65v域中工作的输出信号212的压缩版本。如图2d可见,虽然在此波形中看到一些噪声216,但使用升压器已确保输出信号212上升得足够快,使得在输出高电压(voh)以下没有毛刺并且在输出低电压(vol)以上没有毛刺。

[0064]

图3描绘根据实施例的操作电压电平转换器(即结合输出缓冲器100的电压电平转换器)的方法300。该方法开始于提供305体现在ic芯片上的电压电平转换器。电压电平转换器的输出缓冲器包括被耦合以提供输出信号交错的多个场效应晶体管和多个电阻器。在一个实施例中,多个场效应晶体管包括第一多个pmos晶体管mp1

‑

mpz和第一多个nmos晶体管mn1

‑

mnz,并且多个电阻器包括多个第一电阻器rp1

‑

rpz和多个第二电阻器rn1

‑

rnz。该方法以如下继续:耦合310第一电压域的第一供应电压到第一供应电压引脚并且耦合315第二电压域的第二供应电压到第二供应电压引脚。第一通道的第一数据引脚经耦合320以接收在第一电压域中工作的第一信号并且第一通道的第二数据引脚经耦合325以提供在第二电压域中工作的经转换的第一信号。电压电平转换器经耦合以确定第一供应电压是否大于或等于用于第二供应电压的第一vcci触发电压,并且还经耦合以响应于确定第一供应电压大于或等于第一vcci触发电压而禁用第一通道的第一输出缓冲器中的交错。

[0065]

用于第二通道的第三数据引脚经耦合330以接收在第二电压域中工作的第二信号并且用于第二通道的第四数据引脚经耦合335以提供在第一电压域中工作的经转换的第二信号。电压电平转换器经耦合以确定第二供应电压是否大于或等于用于第一供应电压的第二vcci触发电压并且还经耦合以响应于确定第二供应电压大于或等于第二vcci触发电压而禁用第二通道的第二输出缓冲器中的交错。

[0066]

可以注意到,关于当前输入供应电压vcci与当前输出供应电压vcco的vcci触发电压的比较,当输入供应电压vcci大于输出供应电压vcco时,输入供应电压vcci将始终大于相应的vcci触发电压,因此在从较高电压域转换为较低电压域的通道中始终禁用交错。当输入供应电压vcci和输出供应电压vcco之间存在电压差时,可以在两个转换方向上禁用交错。

[0067]

一些示例提供用于能够处理跨越大范围电压的转换的电压转换器的输出缓冲器。为了最大限度地提高所有电压转换组合下的数据速率,当电压转换从较低电压域到较高电压域并且两个电压域之间的差异很大时应用交错。在较低差异下以及从较高电压域转换到较低电压域时,交错被禁用。当供应域相距很远时,这种安排减少供应噪声的影响并且这样做不会降低数据速率。在彼此更接近的两个电压域之间转换时关闭交错改善了数据速率,

这些较小电压差的传播延迟。还描述用于操作电压转换器的方法。

[0068]

除非另有说明,否则以单数形式提及元素是指“一个或多个”。在权利要求的范围内,在所描述的实施例中的修改是可能的,并且其他实施例也是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1