堆叠式共模滤波器的制作方法

1.本公开涉及一种堆叠式共模滤波器,更具体地,涉及一种在应用了高速信号线的电子装置中使用的堆叠式共模滤波器。

背景技术:

2.通常,移动终端采用移动工业处理器接口(mipi)d-phy标准作为数字数据传输标准。mipi d-phy标准是将移动终端的主电路连接到显示器或相机的数字数据传输标准,是使用两条传输线传输作为差分信号的数据的方法。

3.当移动终端内发送和接收的数据迅速增加时,移动终端需要能够以比mipi d-phy更高的速度来发送和接收数据的传输方法。

4.因此,最近在移动终端产业中,正在进行将mipi c-phy标准应用到移动终端的研究。mipi c-phy标准是通过使用三条传输线从发送侧向每条传输线发送不同的电压、并且在接收侧获取线之间的差值来实现差分输出的方法。

技术实现要素:

5.技术问题

6.本公开是考虑到上述情况而提出的,本公开的目的是提供一种堆叠式共模滤波器,该堆叠式共模滤波器在应用于mipi c-phy标准的共模滤波器中布置有esd吸收层,从而防止滤波器性能的改变并且防止由esd导致的对元件的破坏。

7.问题的解决方案

8.为了实现该目的,根据本公开的示例性实施例的堆叠式共模滤波器包括:滤波器层,滤波器层形成有多个线圈;下磁性层,下磁性层被布置在滤波器层下方;上磁性层,上磁性层被布置在滤波器层上方;以及esd吸收层,esd吸收层被布置在下磁性层和上磁性层中的至少一个磁性层中。

9.esd吸收层可以包括下esd吸收层,下esd吸收层被插入在构成下磁性层的两个磁性板之间。此时,下磁性层包括:第一磁性板,第一磁性板被布置在滤波器层下方;以及第二磁性板,第二磁性板被布置在滤波器层与第一磁性板之间,其中,下esd吸收层被插入在第一磁性板与第二磁性板之间。

10.esd吸收层可以包括上esd吸收层,上esd吸收层被插入在构成上磁性层的两个磁性板之间。此时,上磁性层包括:第三磁性板,第三磁性板被布置在滤波器层上方;以及第四磁性板,第四磁性板被布置在第三磁性板上方,其中,上esd吸收层被插入在第三磁性板与第四磁性板之间。

11.esd吸收层包括:第一esd吸收部;第二esd吸收部,第二esd吸收部与第一esd吸收部间隔开;以及接地部,接地部被插入在第一esd吸收部与第二esd吸收部之间。

12.esd吸收层可以进一步包括:第一输入/输出部,第一输入/输出部被布置在第一esd吸收部与外电极之间,并且电连接到第一esd吸收部和外电极;以及第二输入/输出部,

第二输入/输出部被布置在第二esd吸收部与外电极之间,并且电连接到第二esd吸收部和外电极。

13.同时,esd吸收层也可以被构造成包括:板状导体;第一esd吸收部,第一esd吸收部堆叠在板状导体的上表面上;以及第二esd吸收部,第二esd吸收部堆叠在板状导体的上表面上,并且被布置成与第一esd吸收部间隔开。

14.滤波器层可以具有多个非磁性板,多个非磁性板形成有堆叠在多个非磁性板上的线圈图案,并且滤波器层可以包括:多个非磁性板,多个非磁性板沿堆叠方向堆叠;第一线圈,第一线圈形成在层压部上,多个非磁性板堆叠在层压部中;第二线圈,第二线圈形成在层压部上并且独立于第一线圈;以及第三线圈,第三线圈形成在层压部上并且独立于第一线圈和第二线圈。

15.第一线圈可以包括环路形状的第一线圈图案,第一线圈图案围绕平行于堆叠方向的卷绕轴线卷绕多次,第二线圈可以包括环路形状的第二线圈图案,第二线圈图案围绕卷绕轴线卷绕多次,并且第三线圈包括环路形状的第三线圈图案,第三线圈图案围绕卷绕轴线卷绕多次。

16.在卷绕轴线的一个侧表面的方向上从第二线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分可以被布置在从第一线圈图案的内环周起的第n卷绕部分与第(n+1)卷绕部分之间,n可以为1或大于1的奇数,并且等于或小于第二线圈图案的卷绕数。

17.在卷绕轴线的一个侧表面的方向上从第三线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分可以各自与从第一线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分重叠,在卷绕轴线的另一个侧表面的方向上从第三线圈图案的内环周起的第(m+1)卷绕部分可以各自与从第一线圈图案的内环周起的第m卷绕部分重叠,其中,m可以为1或者大于1,并且等于或小于第三线圈图案的卷绕数。

18.在卷绕轴线的一个侧表面的方向上从第二线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分可以被布置在从第一线圈图案的内环周起的第n卷绕部分与第(n+1)卷绕部分之间,并且在卷绕轴线的另一个侧表面的方向上从第二线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分可以被布置在第(n+1)卷绕部分与第(n+2)卷绕部分之间。此时,从第三线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分可以各自与从第一线圈图案的内环周起的第n卷绕部分和第(n+1)卷绕部分重叠。

19.在卷绕轴线的一个侧表面的方向上的第一线圈图案、第二线圈图案、以及第三线圈图案可以被布置成使得从内环周起的具有相同卷绕数的部分距彼此具有相同的间隔距离。

20.在卷绕轴线的另一侧的方向上从第二线圈图案的内环周起的第x卷绕部分、从第一线圈图案的内环周起的第x卷绕部分、以及从第三线圈图案的内环周起的第(x+1)卷绕部分距彼此可以具有相同的间隔距离,其中,x可以为1或者大于1,并且等于或小于第二线圈图案的卷绕数。

21.在卷绕轴线的另一个侧表面的方向上从第二线圈图案的内环周起的第x卷绕部分、从第一线圈图案的内环周起的第(x+1)卷绕部分、以及从第三线圈图案的内环周起的第(x+1)卷绕部分距彼此具有相同的间隔距离,并且其中,x可以为1或者大于1,并且等于或小于第二线圈图案的卷绕数。

22.在卷绕轴线的另一个侧表面的方向上的第一线圈图案、第二线圈图案、以及第三线圈图案可以被布置成使得从内环周起的具有相同卷绕数的部分距彼此具有相同的间隔距离。

23.发明的有益效果

24.根据本公开,堆叠式共模滤波器可以在磁性层上形成esd吸收层,磁性层被布置在滤波器层上方或被布置在滤波器层下方,从而防止由在衬底中瞬时产生的esd导致的故障和缺陷。

25.此外,堆叠式共模滤波器可以在磁性层上形成esd吸收层,磁性层被布置在滤波器层上方或被布置在滤波器层下方,从而防止由在衬底中瞬时产生的esd导致的故障和缺陷,并且使esd吸收性能和滤波器的特征的改变最小化。

26.此外,堆叠式共模滤波器可以在磁性层上形成esd吸收层,磁性层被布置在滤波器层上方或被布置在滤波器层下方,使得即使一个esd吸收层被破坏,仍使另一个esd吸收层起作用,从而防止由esd导致的故障和缺陷。

27.此外,堆叠式共模滤波器可以相等地形成构成第一线圈至第三线圈的线圈图案之间的间隔距离(间距),从而改进第一线圈至第三线圈之间的磁性耦合(即电磁耦合)的平衡,并且使差分信号的劣化最小化。

附图说明

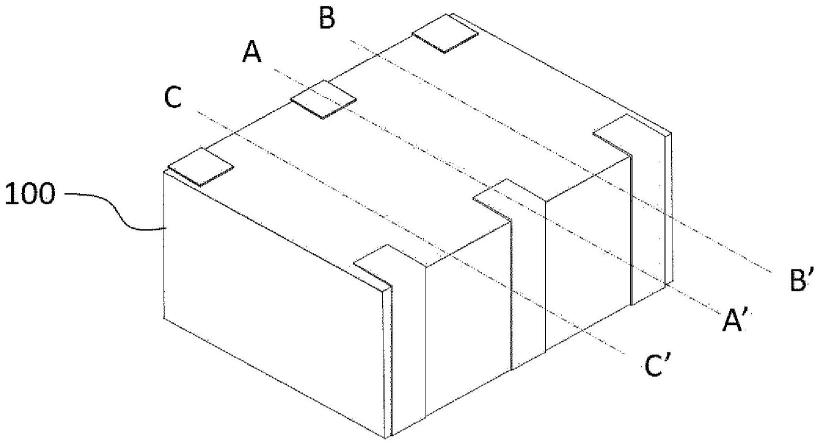

28.图1和图2是用于说明根据本公开的示例性实施例的堆叠式共模滤波器的示意图。

29.图3至图9是用于说明图2的滤波器层的示意图。

30.图10是用于说明图2的下磁性层的示意图。

31.图11是用于说明图2的上磁性层的示意图。

32.图12至图15是用于说明包括在图2的滤波器层中的线圈图案的示意图。

33.图16至图18是用于说明根据本公开的示例性实施例的堆叠式共模滤波器的修改的示例的示意图。

34.图19和图20是用于说明esd吸收层的构造的示意图。

具体实施方式

35.在下文中,为了具体地描述示例性实施例,将参考附图描述本公开的最优选的示例性实施例,使得本公开所属领域的技术人员可以容易地实现本公开的技术精神。首先,在给每个附图的部件添加附图标记时,应当注意,即使相同的部件在不同的附图中示出,相同的部件也尽可能具有相同的附图标记。此外,在描述本公开时,当确定相关的已知的构造或功能的详细描述可能使本公开的主旨不清楚时,将省略对已知的构造或功能的详细描述。

36.参照图1和图2,根据本公开的第一示例性实施例的堆叠式共模滤波器(100)包括滤波器层(200)、下磁性层(300)、上磁性层(400)以及多个外电极。

37.滤波器层(200)是形成有多个线圈的非磁性层压部。滤波器层(200)通过使多个非磁性板进行堆叠来进行构造,线圈图案形成在多个非磁性板上,并且非磁性板形成有堆叠在非磁性板上的具有线圈图案的多个线圈。

38.此时,线圈图案可以形成并且布置成具有相同的线宽、线间距以及层间距。例如,

线圈图案可以形成为具有约10μ0至122例如的线宽、约10宽、的线间距和约10.5和约的层间距。

39.参照图3,滤波器层(200)包括多个非磁性板和多个线圈图案,多个线圈图案各自形成在多个非磁性板上。多个非磁性板中的每一个具有上表面和下表面。

40.在下文中,将作为示例描述堆叠式共模滤波器(100),该堆叠式共模滤波器包括多个非磁性板和多个线圈图案,多个非磁性板包括第一非磁性板(211)、第二非磁性板(212)、第三非磁性板(213)、第四非磁性板(214)、第五非磁性板(215)以及第六非磁性板(216),多个线圈图案包括第一线圈图案(221)、第二线圈图案(222)、第三线圈图案(223)、第四线圈图案(224)、第五线圈图案(225)以及第六线圈图案(226)。

41.多个非磁性板沿堆叠方向(即,从底部到顶部)相继地堆叠,以构成非磁性层压部。换言之,第二非磁性板(212)堆叠在第一非磁性板(211)的上表面上,第三非磁性板(213)堆叠在第二非磁性板(212)的上表面上。第四非磁性板(214)堆叠在第三非磁性板(213)的上表面上。第五非磁性板(215)堆叠在第四非磁性板(214)的上表面上。第五非磁性板(215)堆叠在第四非磁性板(214)的上表面上。第六非磁性板(216)堆叠在第四非磁性板(214)的上表面上。因此,构造了非磁性层压部,第一非磁性板(211)和第二非磁性板(212)沿堆叠方向相继地堆叠在非磁性层压部中。

42.例如,多个非磁性板是低温煅烧陶瓷(ltcc)板,该低温煅烧陶瓷板是包括氧化硅的绝缘的非磁性材料。此时,多个非磁性板可以具有相同的厚度t1。

43.多个线圈图案各自形成在多个非磁性板上。换言之,第一线圈图案(221)形成在第一非磁性板(211)的上表面上。第二线圈图案(222)形成在第二非磁性板(212)的上表面上。第三线圈图案(223)形成在第三非磁性板(213)的上表面上。第四线圈图案(224)形成在第四非磁性板(214)的上表面上。第五线圈图案(225)形成在第五非磁性板(215)的上表面上。第六线圈图案(226)形成在第六非磁性板(216)的上表面上。

44.多个线圈图案中的两个线圈图案配对以形成一个线圈。换言之,第一线圈图案(221)和第四线圈图案(224)形成第一线圈。第二线圈图案(222)和第五线圈图案(225)形成第二线圈。第三线圈图案(223)和第六线圈图案(226)形成第三线圈。

45.配对的线圈图案通过通孔电连接,通孔被形成为穿透至少一个非磁性板。换言之,第一线圈图案(221)和第四线圈图案(224)通过第一通孔(610)电连接,第一通孔形成为穿透第二非磁性板(212)至第四非磁性板(214)。第二线圈图案(222)和第五线圈图案(225)通过第二通孔(620)电连接,第二通孔形成为穿透第三非磁性板(213)至第五非磁性板(215)。第三线圈图案(223)和第六线圈图案(226)通过第三通孔(630)电连接,第三通孔形成为穿透第四非磁性板(214)至第六非磁性板(216)。

46.多个线圈图案可以通过在非磁性板的上表面上以螺旋形形状电镀或印刷导电材料(例如银)来形成。

47.多个线圈图案具有卷绕虚拟的卷绕轴线一次或多次的环路形状,虚拟的卷绕轴线与非磁性板的中心点垂直地相交。多个线圈图案具有圆角矩形的环路,在该环路中,长侧和短侧重复。

48.例如,当非磁性板具有矩形形状(第一侧和第二侧彼此平行,第三侧和第四侧彼此平行,并且第三侧的端部和第四侧的端部各自连接到第一侧的端部和第二侧的端部)时,水

平方向是平行于第一侧和第二侧的方向,竖直方向是平行于第三侧和第四侧的方向。

49.在下文中,将参照附图来描述第一线圈图案(221)至第六线圈图案(226)的形状。

50.参照图4,第一线圈图案(221)具有多次卷绕该卷绕轴线的环路形状。第一线圈图案(221)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架有具有长侧和短侧的圆角矩形形状。第一线圈图案(221)的一个端部连接到布置在框架的内环周上的第一内环周端子图案(231)。第一线圈图案(221)的另一个端部连接到布置在框架的外环周上的第一外环周端子图案(241)。

51.参照图5,第二线圈图案(222)具有多次卷绕该卷绕轴线的环路形状。第二线圈图案(222)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架为具有长侧和短侧的圆角矩形形状。第二线圈图案(222)的一个端部连接到布置在框架的内环周上的第二内环周端子图案(232)。第二线圈图案(222)的另一个端部连接到布置在框架的外环周上的第二外环周端子图案(242)。

52.参照图6,第三线圈图案(223)具有多次卷绕该卷绕轴线的环路形状。第三线圈图案(223)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架为具有长侧和短侧的圆角矩形形状。第三线圈图案(223)的一个端部连接到布置在框架的内环周上的第三内环周端子图案(233)。第三线圈图案(223)的另一个端部连接到布置在框架的外环周上的第三外环周端子图案(243)。

53.参照图7,第四线圈图案(224)具有多次卷绕该卷绕轴线的环路形状。第四线圈图案(224)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架为具有长侧和短侧的圆角矩形形状。第四线圈图案(224)的一个端部连接到布置在框架的内环周上的第四内环周端子图案(234)。第四线圈图案(224)的另一个端部连接到布置在框架的外环周上的第四外环周端子图案(244)。

54.参照图8,第五线圈图案(225)具有多次卷绕该卷绕轴线的环路形状。第五线圈图案(225)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架为具有长侧和短侧的圆角矩形形状。第五线圈图案(225)的一个端部连接到布置在框架的内环周上的第五内环周端子图案(235)。第五线圈图案(225)的另一个端部连接到布置在框架的外环周上的第五外环周端子图案(245)。

55.参照图9,第六线圈图案(226)具有多次卷绕该卷绕轴线的环路形状。第六线圈图案(226)具有环路形状,在该环路形状中,长侧和短侧在框架中围绕卷绕轴线连续地卷绕,框架为具有长侧和短侧的圆角矩形形状。第六线圈图案(226)的一个端部连接到布置在框架的内环周上的第六内环周端子图案(236)。第六线圈图案(226)的另一个端部连接到布置在框架的外环周上的第六外环周端子图案(246)。

56.第一内环周端子图案(231)和第二外环周端子图案(242)通过第二非磁性板(212)至第四非磁性板(214)而彼此隔开,并且被布置成至少部分地彼此重叠。第一外环周端子图案(241)和第三内环周端子图案(233)通过第三非磁性板(213)至第五非磁性板(215)而彼此隔开,并且被布置成至少部分地彼此重叠。第二内环周端子图案(232)和第三外环周端子图案(243)通过第四非磁性板(214)至第六非磁性板(216)而彼此隔开,并且被布置成至少部分地彼此重叠。

57.第一外环周端子图案(241)、第二外环周端子图案(242)以及第三外环周端子图案

(243)被布置成与非磁性板的两个长侧中的一个长侧接触,第四外环周端子图案(244)、第五外环周端子图案(245)以及第六外环周端子图案(246)被布置成与非磁性板的两个长侧中的另一个长侧接触。

58.第一外环周端子图案(241)、第二外环周端子图案(242)以及第三外环周端子图案(243)各自被布置成面向第四外环周端子图案(244)、第五外环周端子图案(245)以及第六外环周端子图案(246)。换言之,第一外环周端子图案(241)被布置成相对于虚拟的直线面向第四外环周端子图案(244),该虚拟的直线穿过非磁性板的中心点并且平行于非磁性板的两个长侧。第二外环周端子图案(242)被布置成相对于虚拟的直线面向第五外环周端子图案(245),该虚拟的直线穿过非磁性板的中心点并且平行于非磁性板的两个长侧。第三外环周端子图案(243)被布置成相对于虚拟的直线面向第六外环周端子图案(246),该虚拟的直线穿过非磁性板的中心点并且平行于非磁性板的两个长侧。

59.当第一非磁性板(211)至第六非磁性板(216)被相继地堆叠时,第一线圈图案(221)至第六线圈图案(226)从底部到顶部相继地布置。

60.因此,形成第二线圈的第二线圈图案(222)和形成第三线圈的第三线圈图案(223)被布置在形成第一线圈的第一线圈图案(221)和第四线圈图案(224)之间,形成第三线圈的第三线圈图案(223)和形成第一线圈的第四线圈图案(224)被布置在形成第二线圈的第二线圈图案(222)和第五线圈图案(225)之间,并且形成第一线圈的第四线圈图案(224)和形成第二线圈的第五线圈图案(225)被布置在形成第三线圈的第三线圈图案(223)和第六线圈图案之间。

61.构成该线圈(即,第一线圈至第三线圈中的一个线圈)的两个线圈图案之间布置有构成其他线圈(即,第一线圈至第三线圈中的其余线圈)的两个线圈图案中的一个线圈图案。换言之,构成该线圈的两个线圈图案之间布置有构成其他线圈的两个线圈图案。

62.下磁性层(300)被布置在滤波器层(200)下方。换言之,下磁性层(300)堆叠在滤波器层(200)下方并且被布置在堆叠式共模滤波器(100)的最下部处。下磁性层(300)包括多个磁性板和多个非磁性板。多个磁性板和多个非磁性板交替地堆叠。

63.例如,参照图10,下磁性层(300)具有从底部到顶部相继地堆叠的第七非磁性板(310)、第一磁性板(320)、第八非磁性板(330)以及第二磁性板(340)。换言之,第七非磁性板(310)被布置在下磁性层(300)的最下部。第一磁性板(320)堆叠在第七非磁性板(310)的上表面上。第八非磁性板(330)堆叠在第一磁性板(320)的上表面上。第二磁性板(340)堆叠在第八非磁性板(330)的上表面上。此时,由于下磁性层(300)被布置在滤波器层(200)下方,所以第一非磁性板(211)堆叠在第二磁性板(340)的上表面上。

64.上磁性层(400)被布置在滤波器层(200)上方。换言之,上磁性层(400)堆叠在滤波器层(200)上方并且被布置在堆叠式共模滤波器(100)的最上部。上磁性层(400)包括多个磁性板和多个非磁性板。多个磁性板和多个非磁性板交替地堆叠。

65.例如,参照图11,上磁性层(400)具有从底部到顶部相继地堆叠的第三磁性板(420)、第九非磁性板(410)、第四磁性板(440)以及第十非磁性板(430)。换言之,第三磁性板(420)被布置在上磁性层(400)的最下部。第九非磁性板(410)堆叠在第三磁性板(420)的上表面上。第四磁性板(440)堆叠在第九非磁性板(410)的上表面上。第十非磁性板(430)堆叠在第四磁性板(440)的上表面上。此时,由于上磁性层(400)被布置在滤波器层(200)上

方,所以第三磁性板(420)堆叠在第六非磁性板(216)的上表面上。

66.多个外电极被布置在层压部的上表面、下表面以及一个侧表面上,滤波器层(200)、下磁性层(300)以及上磁性层(400)堆叠在该层压部中。

67.例如,多个外电极包括电连接到第一线圈的第一外电极(510)和第二外电极(520)、电连接到第二线圈的第三外电极(530)和第四外电极(540)、以及电连接到第三线圈的第五外电极(550)和第六外电极(560)。

68.第一外电极(510)通过第一外环周端子图案(241)电连接到第一线圈图案(221),第一外环周端子图案形成在第一非磁性板(211)上,第二外电极(520)通过第八端子图案电连接到第四线圈图案(224),第八端子图案形成在第四非磁性板(214)上。此时,第一线圈图案(221)和第四线圈图案(224)通过第一通孔(610)而彼此电连接以形成第一线圈,因此,第一外电极(510)电连接到第一线圈的一个端部,第二外电极(520)电连接到第一线圈的另一个端部。

69.第三外电极(530)通过第二外环周端子图案(242)电连接到第二线圈图案(222),第二外环周端子图案形成在第二非磁性板(212)上。第四外电极(540)通过第十端子图案电连接到第五线圈图案(225),第十端子图案形成在第五非磁性板(215)上。此时,第二线圈图案(222)和第五线圈图案(225)通过第二通孔(620)电连接以形成第二线圈,因此,第三外电极(530)电连接到第二线圈的一个端部,第四外电极(540)电连接到第二线圈的另一个端部。

70.第五外电极(550)通过第三外环周端子图案(243)电连接到第三线圈图案(223),第三外环周端子图案形成在第三非磁性板(213)上,第六外电极(560)通过第十二端子图案电连接到第六线圈图案(226),第十二端子图案形成在第六非磁性板(216)上。此时,第三线圈图案(223)和第六线圈图案(226)通过第三通孔(630)电连接以形成第三线圈,因此,第五外电极(550)电连接到第三线圈的一个端部,第六外电极(560)电连接到第三线圈的另一个端部。

71.参照图12至图14,第一线圈图案(221)和第四线圈图案(224)通过第一通孔(610)电连接以形成第一线圈。第二线圈图案(222)和第五线圈图案(225)通过第二通孔(620)电连接以形成第二线圈。第三线圈图案(223)和第六线圈图案(226)通过第三通孔(630)电连接以形成第三线圈。

72.此外,第一线圈图案(221)和第三线圈图案(223)被布置成沿水平方向(即左右方向)移动,水平方向垂直于第二线圈图案(222)和非磁性板的堆叠方向。第四线圈图案(224)和第六线圈图案(226)被布置成沿水平方向(即左右方向)移动,水平方向垂直于第五线圈图案(225)和非磁性板的堆叠方向。

73.参照图12,在卷绕轴线的一个侧表面的方向上,第二线圈图案(222)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分被布置在从第一线圈图案(221)的内环周起的第n卷绕部分与第(n+1)卷绕部分之间。在此,n为1或大于1的奇数,并且等于或小于第二线圈图案(222)的卷绕数。

74.在卷绕轴线的一个侧表面的方向上,第三线圈图案(223)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分各自与从第一线圈图案(221)的内环周起的第n卷绕部分和第(n+1)卷绕部分重叠。在卷绕轴线的另一个侧表面的

方向上,第三线圈图案(223)具有从内环周起的第(m+1)卷绕部分,第(m+1)卷绕部分各自与从第一线圈图案(221)的内环周起的第m卷绕部分重叠。在此,m为1或者大于1,并且等于或小于第三线圈图案(223)的卷绕数。

75.参照图13,在卷绕轴线的一个侧表面的方向上,第二线圈图案(222)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分被布置在从第一线圈图案(221)的内环周起的第n卷绕部分与第(n+1)卷绕部分之间。在卷绕轴线的另一个侧表面的方向上,第二线圈图案(222)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分被布置在从第二线圈图案(222)的内环周起的第(n+1)卷绕部分与第(n+2)卷绕部分之间。第三线圈图案(223)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分各自与从第一线圈图案(221)的内环周起的第n卷绕部分和第(n+1)卷绕部分重叠。

76.参照图14,在卷绕轴线的两个侧表面的方向上,第二线圈图案(222)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分被布置在从第一线圈图案(221)的内环周起的第n卷绕部分与第(n+1)卷绕部分之间。第三线圈图案(223)具有从内环周起的第n卷绕部分和第(n+1)卷绕部分,该第n卷绕部分和第(n+1)卷绕部分各自与从第一线圈图案(221)的内环周起的第n卷绕部分和第(n+1)卷绕部分重叠。

77.参照图15,第一线圈图案(221)与第二线圈图案(222)之间的最短长度、第一线圈图案(221)与第三线圈图案(223)之间的最短长度、以及第二线圈图案(222)与第三线圈图案(223)之间的最短长度相对于堆叠式共模滤波器(100)的横截面都具有相同的长度。第四线圈图案(224)与第五线圈图案(225)之间的最短长度、第四线圈图案(224)与第六线圈图案(226)之间的最短长度、以及第五线圈图案(225)与第六线圈图案(226)之间的最短长度相对于堆叠式共模滤波器(100)的横截面都具有相同的长度。此时,第三线圈图案(223)与第四线圈图案(224)之间的最短长度也具有相同的长度。在此,最短长度表示线圈图案之间的间隔距离。

78.如上所述,第一线圈图案(221)、第二线圈图案(222)以及第三线圈图案(223)被布置成使得:在卷绕轴线的一个侧表面的方向上从内环周起具有相同卷绕数的部分距彼此具有相同的间隔距离。

79.第一线圈图案(221)、第二线圈图案(222)以及第三线圈图案(223)被布置成使得:在卷绕轴线的另一个侧表面的方向上从内环周起具有相同卷绕数的部分距彼此具有相同的间隔距离。

80.例如,第二线圈图案(222)被布置成使得:在卷绕轴线的另一个侧表面中从内环周起的第x卷绕部分距从第一线圈图案(221)的内环周起的第x卷绕部分和从第三线圈图案(223)的内环周起的第(x+1)卷绕部分具有相同的间隔距离。此时,x为1或者大于1,并且等于或小于第二线圈图案(222)的卷绕数。

81.作为另一个示例,第二线圈图案(222)被布置成使得:在卷绕轴线的另一个侧表面的方向上从内环周起的第x卷绕部分距从第一线圈图案(221)的内环周起的第(x+1)卷绕部分和从第三线圈图案(223)的内环周起的第(x+1)卷绕部分具有相同的间隔距离。

82.因此,堆叠式共模滤波器(100)可以改进第一线圈至第三线圈之间的磁性耦合(即,电磁耦合)的平衡,并且使差分信号的劣化最小化。

83.同时,由于在衬底上瞬时产生的静电放电(esd),堆叠式共模滤波器(100)可能有缺陷或出现故障。因此,根据本公开的示例性实施例,为上磁性层(400)和下磁性层(300)中的至少一个增加esd防护功能,从而防止由esd导致的缺陷和故障。

84.例如,参照图16,堆叠式共模滤波器(100)包括形成在下磁性层(300)上的下esd吸收层(710),以防护静电放电(esd)。

85.当安装堆叠式共模滤波器(100)时,下esd吸收层(710)形成在面向衬底的下磁性层(300)上。下esd吸收层(710)插入在构成下磁性层(300)的磁性板之间。下esd吸收层(710)插入在下磁性层(300)的第一磁性板(320)和第二磁性板(340)之间。

86.下esd吸收层(710)电连接到多个外电极。当在衬底上产生的esd通过外电极被施加时,下esd吸收层(710)使被施加的esd流到接地部,从而防止esd传递到滤波器层(200)。

87.参照图17,堆叠式共模滤波器(100)包括形成在上磁性层(400)上的上esd吸收层,以防护静电放电(esd)。

88.当安装堆叠式共模滤波器(100)时,上esd吸收层形成在面向衬底的上磁性层(400)上。上esd吸收层插入在构成上磁性层(400)的磁性板之间。上esd吸收层插入在上磁性层(400)的第三磁性板(420)和第四磁性板(440)之间。

89.上esd吸收层电连接到多个外电极。当在衬底上产生的esd通过外电极被施加时,上esd吸收层使被施加的esd流到接地部,从而防止esd传递到滤波器层(200)。

90.同时,堆叠式共模滤波器(100)仅包括下esd吸收层(710)和上esd吸收层中的一个esd吸收层,并且当倒置地安装的并且没有布置esd吸收层的磁性层面向衬底时,esd吸收性能可能降低,从而导致由esd导致的缺陷或故障。

91.此外,堆叠式共模滤波器(100)仅包括下esd吸收层(710)和上esd吸收层中的一个esd吸收层,并且当倒置地安装的并且没有布置esd吸收层的磁性层面向衬底时,可能导致滤波器层(200)的特征的改变。

92.因此,堆叠式共模滤波器(100)可以包括下esd吸收层(710)和上esd吸收层,以防止esd吸收性能和滤波器特征的改变。换言之,参照图18,堆叠式共模滤波器(100)包括插入在下磁性层(300)中的下esd吸收层(710)和插入在上磁性层(400)中的上esd吸收层。此时,下esd吸收层(710)和上esd吸收层电连接到多个外电极。

93.因此,堆叠式共模滤波器(100)使esd吸收性能和滤波器特征的改变最小化。即使下esd吸收层(710)和上esd吸收层中的一个esd吸收层被esd破坏,堆叠式共模滤波器(100)也可以使另一个esd吸收层起作用以保护滤波器层(200)免受esd的影响。

94.参照图19,esd吸收层(即,下esd吸收层(710)和上esd吸收层)被构造成包括第一输入/输出部(730)、第二输入/输出部(740)、接地部(750)、第一esd吸收部(760)和第二esd吸收部(770)。

95.接地部(750)被布置在第一esd吸收部(760)与第二esd吸收部(770)之间。第一输入/输出部(730)被布置在第一esd吸收部(760)与外电极(即,第一外电极(510)、第三外电极(530)以及第五外电极(550))之间。第二输入/输出部(740)被布置在第二esd吸收部(770)与外电极(即,第二外电极(520)、第四外电极(540)以及第六外电极(560))之间。

96.当esd输入到第一输入/输出部(730)时,第一esd吸收部(760)使输入的esd流向接地部(750),以阻止esd被施加到滤波器层(200)。当esd输入到第二输入/输出部(740)时,第

二esd吸收部(770)使输入的esd流向接地部(750),以阻止esd被施加到滤波器层(200)。

97.参照图20,esd吸收层可以将第一输入/输出部(730)、第二输入/输出部(740)以及接地部(750)构造成单个板状导体,并且还可以被构造成将第一esd吸收部(760)和第二esd吸收部(770)堆叠在板状导体的表面上。

98.尽管上文已经描述了本公开的优选示例性实施例,但是应当理解,本公开可以以各种形式修改,并且本领域技术人员可以在不背离本公开的权利要求的范围的情况下实施各种修改的示例和改变的示例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1