宽频带注入锁定分频器

本发明属于电子电路技术领域,具体涉及一种宽频带注入锁定分频器,可用于计算机、无线通信、雷达、智慧家居的射频收发芯片中。

背景技术:

随着多标准多波段通信系统的兴起,宽带收发机芯片引起了人们的极大关注。锁相环是现代无线通信系统中最重要的部分之一,而分频器则是锁相环中必不可少的模块,所以研究出宽锁定范围lr、低功耗和小尺寸的分频器,具有十分重要的意义。基于交叉耦合振荡器拓扑结构的lc注入锁定分频器由于易于实现,功耗低而得到了广泛的研究,然而,这种注入锁定分频器通常具有较窄的锁定范围lr,为了满足多波段应用、增强鲁棒性,人们急于探索出具有足够宽锁定范围、低功耗、小尺寸的毫米波分频器。

复旦大学在其申请的专利文献“一种注入锁定分频器”(申请号cn200910045161.1,公开号cn101777871a,公开日2010.07.13)中公开了一种注入锁定分频器。它由电感电容振荡器、调谐电路、信号注入电路和电流源偏置电路组成,如图1所示,其中调谐电路包括数字控制电容阵列调谐和变容管调谐。调谐电路通过改变振荡器谐振腔的负载电容实现对自激振荡频率的调谐,信号注入电路通过将输入信号注入到振荡器的谐振腔从而实现对振荡器自激频率的牵引和锁定,从而实现较宽频带的二分频功能。但是,该注入锁定分频器由于其输出端有较大的寄生电容,限制了分频器的锁定范围,同时由于该注入锁定分频器需要较大的电流源来为电路提供直流偏置,增加了整体电路的功耗。

王洁夫在其发表的论文“用于ka波段锁相环的宽带注入锁定分频器”(华东师范大学微电子电路与系统研究所,微电子学,2018年,第48卷,第6期)中公开了一种采用0.13μmcmos工艺设计的注入锁定分频器,该注入锁定分频器采用2位可变电容阵列和差分信号互补谐振腔直接注入方法,实现了宽带的注入锁定分频。当注入信号幅度vp为0.6v时,该注入锁定分频器最终可实现在24.1~35.6ghz频率范围,锁定范围为38.5%。该电路虽然可通过可变电容阵列扩大自谐振频率范围,但是又由于其采用了传统的交叉耦合振荡器结构和多个可变电容,需要较大的直流电流来维持电路振荡,增加了直流功耗。

技术实现要素:

本发明的目的在于针对上述现有技术的不足,提出一种宽频带注入锁定分频器,以在减小电路面积的同时,扩大锁定范围,减小直流功耗。

实现本发明目的思路是:使用colpitts振荡器、开关电流源和衬底偏置电路。利用colpitts振荡器中的比例电容产生正反馈以保持振荡,并提供比普通交叉耦合mos管振荡器更小的输出电容值,从而增大频率锁定范围;利用开关电流源将尾电流值减小为原来的一半,同时,利用衬底偏置电路为晶体管提供正向衬底偏置,降低阈值电压,获取更小的工作电压,从而极大地降低电路功耗。

根据上述思路,本发明的宽频带注入锁定分频器,包括注入晶体管mi、电感电容谐振腔、振荡器和电流源,注入晶体管mi连接在振荡器的正、负信号输出端之间,电感电容谐振腔连接在电源电压vdd与振荡器信号输出端之间,其特征在于:

所述振荡器,采用colpitts结构,其包括第一nmos晶体管m1、第二nmos晶体管m2及外围元件;这两个晶体管m1和m2的栅端均连接到第三偏置电压vb3;且第一晶体管m1的源端与漏端之间连接有第一电容c1,第二晶体管m2的源端与漏端之间连接有第二电容c2,第一晶体管m1的源端与第二晶体管m2的源端之间连接有第三电容c3,这三个电容形成电容正反馈结构,用于降低振荡器起振条件;第一晶体管m1的漏端与其正信号输出端v1之间连接有第一阻隔电感l1,第二晶体管m2的漏端与其负信号输出端v2之间连接有第二阻隔电感l2,这两个电感用于实现正反馈结构与信号输出端之间的隔离,扩展分频器的锁定范围;

所述电流源,采用开关电流源,其包括第三nmos晶体管m3和第四nmos晶体管m4,这两个晶体管的源端均连接电源地gnd;该第三晶体管m3,其栅端与第四晶体管m4的漏端连接,其漏端与colpitts振荡器中第一晶体管m1的源端连接;该第四晶体管m4,其栅端第三晶体管m3的漏端连接,其源端与colpitts振荡器中第二晶体管m2的源端连接,形成交叉耦合的尾电流源,为振荡器提供交替导通的尾电流;

上述四个晶体管m1、m2、m3、m4的体端均连接有衬底偏置电路,用于减小晶体管阈值电压,降低电路的直流功耗。

进一步,所述注入晶体管mi,其源端与振荡器的正信号输出端v1连接,其漏端与振荡器的负信号输出端v2连接,其栅端与直流电压vdc和注入信号vi连接,用于实现注入信号vi与colpitts振荡器的振荡信号的混频,在振荡器的信号输出端产生分频信号。

进一步,所述衬底偏置电路,包括第一偏置电阻r1和第二偏置电阻r2,第一偏置电压vb1通过第一偏置电阻r1连接colpitts振荡器中两个晶体管m1、m2的体端,第二偏置电压vb2通过第二偏置电阻r2连接开关电流源中两个晶体管m3、m4的体端,用于实现晶体管的正向衬底偏置。

进一步,所述电感电容谐振腔,包括第三电感l3和第四电感l4,该第三电感l3连接在电源电压vdd与振荡器的正信号输出端v1之间,该第四电感l4连接电源电压vdd在振荡器的负信号输出端v2之间,这两个电感取值相同。

本发明与现有技术相比,具有如下优点:

第一,本发明由于在colpitts振荡器中采用三个电容c1、c2、c3组成的电容正反馈结构,降低了振荡器稳定振荡所需的负载电容值,且通过colpitts振荡器中的第一阻隔电感l1和第二阻隔电感l2,进一步将电容正反馈结构与信号输出端隔离,避免了大输出电容对注入锁定分频器锁定范围lr的限制,从而极大地扩展了注入锁定分频器的带宽。

第二,本发明由于在开关电流源中采用由第三晶体管m3和第四晶体管m4组成的交叉耦合尾电流源,为colpitts振荡器提供两路交替导通的直流电流,使得colpitts振荡器的两个晶体管只在饱和状态时流通大电流,减小了分频器的直流偏置电流。

第三,本发明由于通过衬底偏置电路为colpitts振荡器和开关电流源中的nmos晶体管提供正向衬底偏置,可减小晶体管的阈值电压,在导通电流不变的条件下降低晶体管的过驱动电压,从而降低电路的电源电压和直流功耗。

附图说明

图1是现有注入锁定分频器的电原理图;

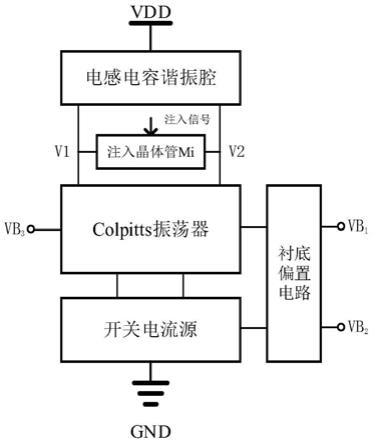

图2是本发明的结构框图;

图3是本发明的电原理图;

图4是本发明的输入功率灵敏度仿真结果图;

图5是本发明的瞬态信号波形仿真结果图。

具体实施方式:

下面结合附图,对本发明的实施例和效果做进一步详细描述。

参照图2,本发明包括注入晶体管mi、电感电容谐振腔、colpitts振荡器、开关电流源和衬底偏置电路;注入晶体管mi连接在colpitts振荡器的正、负信号输出端之间,电感电容谐振腔连接在电源电压vdd与colpitts振荡器信号输出端之间,colpitts振荡器和电源地gnd之间连接有开关电流源,以产生交替导通的尾电流,colpitts振荡器和开关电流源均连接有衬底偏置电路,用于减小晶体管阈值电压,降低电路的直流功耗。

参照图3,本实例各模块的电路结构如下:

所述colpitts振荡器,其包括第一nmos晶体管m1、第二nmos晶体管m2及三个电容与两个电感。这两个晶体管m1和m2的栅端均连接到第三偏置电压vb3;第一电容c1连接在第一晶体管m1的源端与漏端之间,第二电容c2连接在第二晶体管m2的源端与漏端之间,第三电容c3连接在第一晶体管m1的源端与第二晶体管m2的源端之间,这三个电容形成电容正反馈结构,用于降低振荡器起振条件。第一阻隔电感l1连接在第一晶体管m1的漏端与其正信号输出端v1之间,第二阻隔电感l2连接在第二晶体管m2的漏端与其负信号输出端v2之间,这两个电感用于实现正反馈结构与信号输出端之间的隔离,扩展分频器的锁定范围。

所述开关电流源,其包括第三nmos晶体管m3和第四nmos晶体管m4,这两个晶体管的源端均连接电源地gnd;该第三晶体管m3的栅端与第四晶体管m4的漏端连接,其漏端与colpitts振荡器中第一晶体管m1的源端连接;该第四晶体管m4的栅端与第三晶体管m3的漏端连接,其源端与colpitts振荡器中第二晶体管m2的源端连接,形成交叉耦合的尾电流源,为振荡器提供交替导通的尾电流。

上述四个晶体管m1、m2、m3、m4的体端均连接有衬底偏置电路,用于减小晶体管阈值电压,降低电路的直流功耗。

所述注入晶体管mi,其源端与振荡器的正信号输出端v1连接,其漏端与振荡器的负信号输出端v2连接,其栅端与直流电压vdc和注入信号vi连接,用于实现注入信号vi与colpitts振荡器的振荡信号的混频,在振荡器的信号输出端产生分频信号。

所述电感电容谐振腔,包括第三电感l3和第四电感l4,该第三电感l3连接在电源电压vdd与振荡器的正信号输出端v1之间,该第四电感l4连接在振荡器的负信号输出端v2之间,这两个电感取值相同。

所述衬底偏置电路,包括第一偏置电阻r1和第二偏置电阻r2,第一偏置电压vb1通过第一偏置电阻r1连接到colpitts振荡器中两个晶体管m1、m2的体端,第二偏置电压vb2通过第二偏置电阻r2连接带开关电流源中两个晶体管m3、m4的体端,用于实现晶体管的正向衬底偏置。

所述colpitts结构振荡器中的二个阻隔电感l1和l2的取值相同,且小于电感电容谐振腔中两个电感l3和l4的取值。

所述衬底偏置电路中第一偏置电阻r1和第二偏置电阻r2的取值在5kω-10kω范围内调节,以确保偏置电压的无损传输。

本实施例注入锁定分频器功能的实现是以colpitts振荡器为基础的,即用colpitts振荡器作为输出信号的发生器,在其输出端产生振荡信号,其工作原理如下:

在满足稳定振荡的工作条件下,振荡信号与通过信号注入晶体管直接注入的信号进行混频,当注入信号的频率与振荡器自由振荡频率的n倍接近时,注入信号与自由振荡信号的各次谐波进行混频,得到频率为finj-(n-1)fosc的混频信号,其中,finj为注入信号的频率,fosc为振荡器的振荡频率,n为振荡器的谐波次数。由于电感电容谐振腔的滤波作用,频率满足finj-(n-1)fosc=fosc的混频信号被保留下来,从而得到fosc=finj/n,实现了输出振荡频率fosc对注入信号频率finj的n分频。

colpitts振荡器通过正反馈电容结构和两个阻隔电感l1、l2,拓宽了分频器的注入锁定范围lr。通过小信号简化分析,可得本发明注入锁定分频器的锁定范围lr为:

其中gm、reff分别表示分频器信号输出端的等效跨导和等效阻抗,gmax是信号注入晶体管mi的等效跨导,c1为第一电容c1的电容值,c2为第一电容c2的电容值,l1是第一电感l1的电感值,l=l3+l4,其中l3和l4分别是第三电感l3和第四电感l4的电感值。通过对本发明的电感值进行合理的设计,使得1/(1-l1/l)>1,即可获得更大的频率锁定范围,同时避免了调谐电路的使用,减小了芯片面积。

开关电流源通过在振荡器的两侧切换相同的电流源来复用尾电流,即通过这一对晶体管m3、m4将电流从colpitts振荡器一边切换到另一边,这种开关动作将减少几乎一半的电流,降低了分频器的直流功耗。

衬底偏置电路的原理可以用电路的直流电流id来描述:

其中,w为第三晶体管m3和第四晶体管m4的沟道宽度,l为第三晶体管m3和第四晶体管m4的沟道长度,μn为第三晶体管m3和第四晶体管m4的电子迁移率,cox为第三晶体管m3和第四晶体管m4的栅氧化物电容,vgs为第三晶体管m3和第四晶体管m4栅源电压,

从上式可以得出结论,当衬底正向偏置时,vbs增大,vth减小,则在直流电流id不变的条件下,可以通过降低栅源偏置电压vgs和电路的电源电压vdd,进一步降低电路功耗。

下面结合仿真实验对本发明的效果作进一步的描述。

1.仿真实验条件:

本发明仿真实验的硬件平台为:处理器为intel(r)pentium(r)cpu,主频为3ghz,内存为4gb。

本发明仿真实验的软件平台为:linux操作系统和ic617。

仿真软件为spectrerf,仿真采用smic55nmcmos工艺,给定电源电压vdd为0.6v,第一偏置电压vb1和第二偏置电压vb2为550mv,第三偏置电压vb3为1.8v,工作温度为26℃,注入锁定分频器的自由振荡频率为4.07ghz。

2.仿真内容及其结果分析:

仿真实验1,设置输入信号频率的扫描范围为4ghz-13ghz,对本实例的输入功率灵敏度进行仿真,结果如图4所示。图4中的横坐标表示输出信号的频率,单位为ghz,纵坐标表示输入信号的功率,单位为dbm,图4中的曲线是仿真得到的注入锁定分频器的最小输入功率,即输入功率灵敏度。从图4的结果可以看出,本实例的锁定范围可达94.3%,相较现有结构有了很大提升。

仿真实验2,设置注入信号的频率为8ghz,对本实例的交流注入信号和交流输出信号进行瞬态仿真,结果如图5所示。图5的横坐标表示时间变量,单位为ns,纵坐标表示信号电压幅度值,单位为v,图5中的虚曲线代表仿真得到的交流注入信号的瞬态波形,图5中的实曲线代表仿真得到的交流输出信号的瞬态波形。由图5可以看出,本实例的交流输出信号频率为交流注入信号频率的一半,实现了二分频功能。

上述的理论分析和仿真结果表明,本发明的宽频带注入锁定分频器,在实现正常分频功能的同时,具有更宽的注入频率锁定范围和更低的直流功耗。

以上描述仅为本发明的一个具体事例,并未构成对本发明的任何限制,显然对于本领域的专业人员来说,在了解了本发明内容和原理后,都可能在不背离本发明原理、结构的情况下,对其进行形式和细节上的各种修改和改变。但是这些基于本发明思想的修正和改变仍在本发明的权利要求保护范围之内。

- 还没有人留言评论。精彩留言会获得点赞!