晶体振荡器起振电路、功能模块以及电子设备的制作方法

文档序号:30085778发布日期:2022-05-18 05:38阅读:222来源:国知局

导航: X技术> 最新专利>电子电路装置的制造及其应用技术

1.本发明实施例涉及振荡技术领域,尤其涉及一种晶体振荡器起振电路、功能模块以及电子设备。

背景技术:

2.晶体振荡器技术己经日渐成熟,晶振作为一种高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。

3.现有的晶体振荡器的起振时间通常都在毫秒级,在需要频繁启停并且只需要短时工作的系统中,晶体振荡器从起振到稳定所占据的时间在整个系统工作时间段中占据了很大的比例,因此起振能耗所占的比例较大。由此可知晶体振荡电路中起振功耗取决于晶振的起振时间,快速起振的晶振电路可以降低起振功耗。目前晶振电路使用的晶体振荡器起振电路,只能在谐振频率上提供固定的环路增益,因此晶振电路的起振速度受到限制。

4.现有的晶体振荡器存在的起振时间过长的问题,成为业内亟待解决的问题。

技术实现要素:

5.本发明实施例提供一种晶体振荡器起振电路、功能模块以及电子设备,以解决晶体振荡器存在的起振时间过长的问题,提高晶体振荡器的起振速度。

6.第一方面,本发明实施例提供了一种晶体振荡器起振电路,其包括:

7.振荡模块,振荡模块用于生成振荡信号;

8.起振控制模块,振荡模块与起振控制模块连接;起振控制模块用于根据振荡信号调节振荡模块的反馈系数,以缩短振荡模块的起振时间。

9.可选地,振荡模块包括:放大单元和反馈单元;

10.放大单元的第一输入端用于输入电源信号,放大单元的输出端分别与反馈单元的输入端和起振控制模块的输入端连接,反馈单元的输出端与放大单元的第二输入端连接,起振控制模块的输出端与反馈单元的控制端连接;

11.放大单元用于放大放大单元的第二输入端的输入信号,并生成振荡信号;反馈单元用于接收振荡信号,并将振荡信号反馈给放大单元的第二输入端。

12.可选地,起振控制模块包括:

13.状态识别单元,状态识别单元的第一端作为起振控制模块的输入端,状态识别单元的第二端与反馈单元的控制端连接;

14.状态识别单元用于根据振荡模块输出的振荡信号,生成第一控制信号或第二控制信号;

15.第一控制信号和第二控制信号用于调节振荡模块的反馈系数,以缩短振荡模块的起振时间。

16.可选地,状态识别单元包括:

17.比较器,比较器的第一端作为状态识别单元的第一端,比较器的第二端与基准电源连接,比较器的第三端作为状态识别单元的第二端;

18.比较器用于将振荡信号与基准电源输入的基准电压进行比较,并根据比较结果生成第一控制信号或第二控制信号。

19.可选地,起振控制模块还包括:

20.延时器,延时器的第一端与比较器的第三端连接,延时器的第二端作为起振控制模块的输出端;延时器用于将第一控制信号或第二控制信号延迟预设时间后传输给反馈单元的控制端。

21.可选地,放大单元包括:

22.第一开关管、第二开关管以及第一电阻;

23.第一开关管的控制端、第一电阻的第一端以及第二开关管的控制端连接,并作为放大单元的第二输入端;第一开关管的第一端作为放大单元的第一输入端,并与外部电源连接;第一开关管的第二端、第一电阻的第二端以及第二开关管的第一端连接,并作为放大单元的输出端,第二开关管的第三端接地。

24.可选地,反馈单元包括晶体、第一电容、第二电容、第二电阻以及第三开关管;

25.晶体的第一端和第一电容的第一端连接,并作为反馈单元的输出端;第一电容的第二端接地,晶体的第二端、第二电容的第一端以及第二电阻的第一端连接,第二电阻的第二端作为反馈单元的输入端;第二电容的第二端与第三开关管的第一端连接,第三开关管的第二端接地,第三开关管的控制端作为反馈单元的控制端;

26.第三开关管用于根据第一控制信号关断,调节反馈单元的反馈系数为第一反馈系数;或者,第三开关管根据第二控制信号导通,调节反馈单元的反馈系数为第二反馈系数。

27.可选地,第一反馈系数f1通过如下公式计算:

[0028][0029]

第二反馈系数f2通过如下公式计算:

[0030][0031]

其中,zy为晶体的阻抗,zc1为第一电容的阻抗,zc2为第二电容的阻抗,r2为第二电阻的电阻。

[0032]

可选地,反馈单元还包括第三电容;

[0033]

第三电容的第一端与晶体的第二端、第二电容的第一端以及第二电阻的第一端连接,第三电容的第二端接地。

[0034]

第二方面,本发明实施例还提供了一种功能模块,其包括如第一方面中任一项的晶体振荡器起振电路。

[0035]

第三方面,本发明实施例还提供了一种电子设备,其包括如第一方面中任一项的晶体振荡器起振电路,或者,包括如第二方面中的功能模块。

[0036]

本发明实施例提供的技术方案通过振荡模块生成振荡信号,并将所述振荡信号传输至起振控制模块;起振控制模块根据接收到的振荡信号调节振荡模块的反馈系数提高,缩短了振荡模块的起振时间,从而使振荡模块更快地达到稳定振荡,可以更有效的避免振

荡器不能启振的发生,进而降低晶体振荡器的起振功耗。

附图说明

[0037]

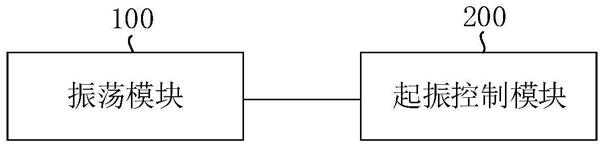

图1为本发明实施例提供的一种晶体振荡器起振电路的结构示意图;

[0038]

图2为本发明实施例提供的一种振荡模块的结构示意图;

[0039]

图3为本发明实施例提供的另一种晶体振荡器起振电路的结构示意图;

[0040]

图4为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图;

[0041]

图5为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图;

[0042]

图6为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图;

[0043]

图7为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图;

[0044]

图8为本发明实施例提供的一种振荡模块等效电路的结构示意图;

[0045]

图9为本发明实施例提供的另一种晶体振荡器起振电路的结构示意图。

[0046]

图10为本发明实施例提供的一种功能模块的结构示意图;

[0047]

图11为本发明实施例提供的一种电子设备的结构示意图;

[0048]

图12为本发明实施例提供的另一种电子设备的结构示意图。

具体实施方式

[0049]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0050]

本发明实施例提供了一种晶体振荡器起振电路,图1为本发明实施例提供的一种晶体振荡器起振电路的结构示意图。如图1所示,晶体振荡器起振电路包括:振荡模块100,振荡模块100用于生成振荡信号;起振控制模块200,振荡模块100与起振控制模块200连接;起振控制模块200用于根据振荡信号调节振荡模块100的反馈系数,以缩短振荡模块100的起振时间。

[0051]

具体地,振荡模块100主要由放大单元110和反馈单元120组成,振荡模块100能够振荡起来,并维持稳定的振荡,可以从环路形成正反馈的角度分析。图2为本发明实施例提供的一种振荡模块的结构示意图,如图2所示,振荡模块100由放大单元110和反馈单元120组成。放大单元110将输入信号ui放大,其放大系数为ai,反馈单元120将放大单元110输出的信号uo按照反馈系数fi,反馈给放大单元110的输入。输入信号ui经过放大单元110后,相位移动180度,经过反馈单元120后,会再次产生180度的相位移动,由此反馈单元120实现了对放大单元110的正反馈调节。如果整个呈闭环连接结构的振荡模块100的增益aifi大于1,那该振荡模块100会将其本身的噪声不断放大,从而形成自激振荡。而振荡模块100的增益aifi越大,振荡模块100形成稳定的自激振荡的时间越短。由此,可以通过调节振荡模块100的增益aifi,从而调节振荡模块100形成稳定的自激振荡的时间。

[0052]

根据上述分析,本方案可以通过对晶体振荡器的增益进行调节,从而可以缩短晶体振荡器形成稳定的自激振荡的时间。由于晶体振荡器的起振速度是由晶体振荡器的增益所决定的,而晶体振荡器的放大系数是由振荡模块100里的放大器件的本身特性所决定的,

也就是晶体振荡器的放大系数是固定的。由此起振控制模块200可以通过调节振荡模块100的反馈系数,对晶体振荡器的增益进行调节。例如,在振荡模块100的起振阶段,起振控制模块200可以通过调节振荡模块100的反馈系数增大,从而使晶体振荡器的增益增大,以缩短振荡模块100的起振时间;在振荡模块100起振后,起振控制模块200可以通过调节振荡模块100的反馈系数减小,从而使振荡模块100的振荡频率达到预设的频率精度。

[0053]

具体地,振荡模块100为晶体振荡器起振电路产生振荡信号的部分,起振控制模块200为晶体振荡器起振电路调节振荡模块100起振速度的部分。振荡模块100与起振控制模块200连接,振荡模块100可以将生成的振荡信号传输给起振控制模块200,起振控制模块200可以根据振荡信号调节振荡模块100的反馈系数增大,以缩短振荡模块100的起振时间。

[0054]

本实施例提供的技术方案通过振荡模块生成振荡信号,并传输给起振控制模块;起振控制模块根据接收到的振荡信号调节振荡模块的反馈系数,若振荡模块的反馈系数增大,可以使晶体振荡器的增益增大,从而缩短振荡模块的起振时间,使振荡模块更快地达到稳定振荡,可以更有效的避免振荡器不能启振的发生,进而降低晶体振荡器的起振功耗。

[0055]

图3为本发明实施例提供的另一种晶体振荡器起振电路的结构示意图。如图3所示,振荡模块100可以包括:放大单元110和反馈单元120;放大单元110的第一输入端用于输入电源信号,放大单元110的输出端分别与反馈单元120的输入端和起振控制模块200的输入端连接,反馈单元120的输出端与放大单元110的第二输入端连接,起振控制模块200的输出端与反馈单元120的控制端连接;放大单元110用于放大放大单元110的第二输入端的输入信号,并生成振荡信号;反馈单元120用于接收振荡信号,并将振荡信号反馈给放大单元110的第二输入端。

[0056]

具体的,放大单元110具有放大的作用,反馈单元120用于将放大单元110输出的信号再反馈给放大单元110的第二输入端,需要注意的是反馈单元120对放大单元110所起的作用是正反馈。

[0057]

放大单元110的第一输入端与外部电源300连接,外部电源300可以给振荡电路提供电源信号,使放大单元110可以正常工作。放大单元110的输出端与反馈单元120的输入端连接,反馈单元120的输出端与放大单元110的第二输入端连接。反馈单元120与放大单元110形成闭环连接,反馈单元120可以将放大单元110所生成的振荡信号传输到放大单元110的第二输入端,放大单元110会对其第二输入端的输入信号不断地进行放大。

[0058]

放大单元110的第二输入端的输入信号包括放大单元110内部器件产生的噪声信号和放大单元110每次放大产生的振荡信号。放大单元110的输出端还与起振控制模块200的输入端连接,基于反馈单元120对放大单元110的正反馈作用,使得放大单元110输出的振荡信号的振荡幅度呈逐渐变大的趋势,由此起振控制模块200可以接收到放大单元110产生的振动幅值不断变大的振荡信号。起振控制模块200的输出端与反馈单元120的控制端连接,起振控制模块200可以根据具体接收到的振荡信号,控制反馈单元120的反馈系数大小,进而缩短振荡模块100的起振时间。

[0059]

图4为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图。如图4所示,起振控制模块200包括:状态识别单元210,状态识别单元210的第一端作为起振控制模块200的输入端,状态识别单元210的第二端与反馈单元120的控制端连接;状态识别单元210用于根据振荡模块100输出的振荡信号,生成第一控制信号或第二控制信号;第一控制

信号和第二控制信号用于调节振荡模块100的反馈系数,以缩短振荡模块100的起振时间。

[0060]

具体地,状态识别单元210的第一端作为起振控制模块200的输入端,也就是状态识别单元210的第一端与放大单元110的输出端连接,状态识别单元210可以识别放大单元110输出的振荡信号的振荡幅值大小,并根据振荡信号的振荡幅值大小生成第一控制信号或第二控制信号。

[0061]

示例性的,若状态识别单元210识别到放大单元110输出的振荡信号的振荡幅值小于状态识别单元210的预设幅值,状态识别单元210则产生第一控制信号;若状态识别单元210识别到放大单元110输出的振荡信号的振荡幅值大于状态识别单元210的预设幅值,状态识别单元210则产生第二控制信号。

[0062]

状态识别单元210的第二端与反馈单元120的控制端连接,状态识别单元210可以输出其根据振荡信号生成的第一控制信号或第二控制信号,从而使得反馈单元120根据第一控制信号或第二控制信号调节振荡模块100的反馈系数,实现调节振荡模块100的起振时间。

[0063]

图5为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图。如图5所示,状态识别单元210可以包括:比较器211,比较器211的第一端作为状态识别单元210的第一端,比较器211的第二端与基准电源400连接,比较器211的第三端作为状态识别单元210的第二端;比较器211用于将振荡信号与基准电源400输入的基准电压进行比较,并根据比较结果生成第一控制信号或第二控制信号。

[0064]

具体地,比较器211具有两个信号输入端,其可以对两个信号输入端输入的信号进行比较,并根据比较结果输出不同的信号。比较器211的第一端作为状态识别单元210的第一端,也就是比较器211的第一端与放大单元110的输出端连接,由此比较器211的第一端可以接收到放大单元110产生的振荡信号。比较器211的第二端与基准电源400连接,由此比较器211的第二端可以接收到基准电源400产生的基准电压。

[0065]

比较器211第一端接收到振荡信号后,会将振荡信号的幅值与其第二端接收到的基准电压进行比较,并根据比较结果生成第一控制信号或第二控制信号。例如,振荡信号的幅值小于基准电压,比较器211第三端输出第一控制信号;振荡信号的幅值大于基准电压,比较器211第三端输出第二控制信号。比较器211的第三端作为状态识别单元210的第二端,也就是比较器211的第三端与反馈单元120的控制端连接,从而使得反馈单元120可以根据第一控制信号和第二控制信号调节振荡模块100的反馈系数,可以缩短振荡模块100的起振时间。

[0066]

图6为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图。如图6所示,起振控制模块200还可以包括:延时器220,延时器220的第一端与比较器211的第三端连接,延时器220的第二端作为起振控制模块200的输出端;延时器220用于将第一控制信号或第二控制信号延迟预设时间后传输给反馈单元120的控制端。

[0067]

具体地,延时器具有延时的作用。延时器220的第一端与比较器211的第三端连接,延时器220的第二端作为起振控制模块200的输出端,也就是延时器的第二端与反馈单元120的控制端连接,延时电路可以将接收到的比较器211输出的第一控制信号或第二控制信号延迟预设时间后传输给反馈单元120,可以确保比较器211输出的第一控制信号或第二控制信号的准确性。

[0068]

示例性地,延迟器可以采用计数延时器,计数延时器可以通过采集比较器211输出的第一控制信号或第二控制信号的输出时间,当计数延时器采集到第一控制信号或第二控制信号的时长达到预设时长时,计数延时器将第一控制信号或第二控制信号传输给反馈单元120。

[0069]

图7为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图。如图7所示,放大单元110包括:第一开关管p1、第二开关管p2以及第一电阻r1;第一开关管p1的控制端、第一电阻r1的第一端以及第二开关管p2的控制端连接,并作为放大单元110的第二输入端;第一开关管p1的第一端作为放大单元110的第一输入端,并与外部电源300连接;第一开关管p1的第二端、第一电阻r1的第二端以及第二开关管p2的第一端连接,并作为放大单元110的输出端,第二开关管p2的第三端接地。

[0070]

具体地,第一开关管p1的控制端、第一电阻r1的第一端以及第二开关管p2的控制端连接,并作为放大单元110的第二输入端,也就是第一开关管p1的控制端、第一电阻r1的第一端以及第二开关管p2的控制端均与反馈单元120的输出端连接。第一开关管p1的第一端作为放大单元110的第一输入端,并与外部电源300连接,可以输入电源信号,以保证放大单元110的正常工作。第一开关管p1的第二端、第一电阻r1的第二端以及第二开关管p2的第一端连接,并作为放大单元110的输出端,也就是分别与反馈单元120的输入端和起振控制模块200的输入端连接。

[0071]

可选地,继续参考图7,反馈单元120包括晶体y、第一电容c1、第二电容c2、第二电阻r2以及第三开关管p3;晶体y的第一端和第一电容c1的第一端连接,并作为反馈单元120的输出端;第一电容c1的第二端接地,晶体y的第二端、第二电容c2的第一端以及第二电阻r2的第一端连接,第二电阻r2的第二端作为反馈单元120的输入端;第二电容c2的第二端与第三开关管p3的第一端连接,第三开关管p3的第二端接地,第三开关管p3的控制端作为反馈单元120的控制端;第三开关管p3用于根据第一控制信号关断,调节反馈单元120的反馈系数为第一反馈系数;或者,第三开关管p3根据第二控制信号导通,调节反馈单元120的反馈系数为第二反馈系数。

[0072]

具体地,晶体y的第一端和第一电容c1的第一端连接,并作为反馈单元120的输出端,与放大单元110的第二输入端连接。第一电容c1的第二端接地,晶体y的第二端、第二电容c2的第一端以及第二电阻r2的第一端连接,第二电阻r2的第二端作为反馈单元120的输入端,与放大单元110的输出端连接。第二电容c2的第二端与第三开关管p3的第一端连接,第三开关管p3的第二端接地。第三开关管p3的控制端作为反馈单元120的控制端,与起振控制模块200的输出端连接。当第三开关管p3接收到第一控制信号时,第三开关管p3的控制端会根据第一控制信号断开第三开关管p3的第一端和第二端的连接,从而使反馈单元120中第二电容c2的阻抗值为零,进而实现调节反馈单元120的反馈系数为第一反馈系数。当第三开关管p3接收到第二控制信号时,第三开关管p3的控制端会根据第二控制信号导通第三开关管p3的第一端和第二端的连接,从而使反馈单元120中第二电容c2的阻抗值不为零,进而实现调节反馈单元120的反馈系数为第二反馈系数。

[0073]

可选地,继续参考图7,第一反馈系数f1通过如下公式计算:

[0074]

[0075]

第二反馈系数f2通过如下公式计算:

[0076][0077]

其中,zy为晶体y的阻抗,zc1为第一电容c1的阻抗,zc2为第二电容c2的阻抗,r2为第二电阻r2的电阻。

[0078]

具体的,第一开关管p1、第二开关管p2以及第一电阻r1组成的放大单元110在正常工作时等效为负阻,放大单元110的等效负阻可以抵消晶体y等效内阻的功耗损耗,从而维持整个晶体振荡器的稳定振荡。第二电阻r2为限制电阻,可以防止放大单元110驱动晶体y的功率过大,对晶体y造成损坏。

[0079]

图8为本发明实施例提供的一种振荡模块等效电路的结构示意图。如图7-图8所示,其中zy为晶体y在振荡模块振荡时的等效阻抗,zc1和zc2为第一电容c1和第二电容c2在振荡模块振荡时的等效阻抗。其中,由第一开关管p1,第二开关管p2和第一电阻r1组成的放大单元110的增益为a1。

[0080]

当第三开关管p3关断时,晶体y、第一电容c1、以及第二电阻r2组成的反馈单元120的第一反馈系数f1为:

[0081][0082]

经分析可知,当第一电容c1的阻抗值zc1和第二电容c2的阻抗值zc2都为零时,反馈单元120的反馈系数可取得最大值,但此时反馈单元120环路相位移动达不到正反馈的要求,由此第一电容c1和第二电容c2不能同时为零。当第二电容c2取零,第一电容c1取晶体y匹配的负载电容值时,反馈单元120可取得较优的反馈系数,并且反馈单元120相位移动可以达到正反馈的要求。由此,我们通过控制第三开关管p3关断,使第三开关管p3的第一端和第二端断开,使第二电容c2的阻抗值zc2为0,可以得到反馈单元120的较优的反馈系数,从而使振荡模块起振的时间大大缩短,避免振荡模块不能起振。

[0083]

当第三开关管p3导通时,晶体y、第一电容c1、第二电容c2以及第二电阻r2组成的反馈网络的反馈系数为:

[0084][0085]

在振荡模块启振成功后,第二电容c2作为振荡器的负载电容不能为零,需要将第二电容c2重新连接入反馈单元120中,从而使振荡模块的振荡频率达到预设的频率精度。

[0086]

图9为本发明实施例提供的又一种晶体振荡器起振电路的结构示意图。如图9所示,反馈单元120还包括第三电容c3;第三电容c3的第一端与晶体y的第二端、第二电容c2的第一端以及第二电阻r2的第一端连接,第三电容c3的第二端接地。

[0087]

其中,可以通过第三开关管p3关闭使一部分负载电容失效(第二电容c2),剩余一部分的负载电容(第三电容c3),从而使振荡模块的环路增益得到提高,从而使振荡模块达到稳定振荡的时间更短,并且更有效的避免振荡模块不能启振。

[0088]

图10为本发明实施例提供的一种功能模块的结构示意图,如图10所示,该功能模块002包括上述实施例中任一项的晶体振荡器起振电路001。本发明实施例提供的功能模块002包括本发明上述任意实施例提供的晶体振荡器起振电路001,因此具有本发明实施例提

供的晶体振荡器起振电路001的有益效果,此处不再赘述。

[0089]

图11为本发明实施例提供的一种电子设备的结构示意图,图12为本发明实施例提供的另一种电子设备的结构示意图,如图11-图12所示,该电子设备003包括上述任意实施例中提出的晶体振荡器起振电路001,或者,包括上述任意实施例中提出的功能模块002。本实施例提供的电子设备003包括本发明任意实施例提供的晶体振荡器起振电路001或功能模块002,因此具有本发明实施例提供的晶体振荡器起振电路001的有益效果,此处不再赘述。

[0090]

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:林武

- 技术所有人:深圳市英特瑞半导体科技有限公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、田老师:1: 建筑节能 绿色建筑能耗的模拟与检测(EnergyPlus);建筑碳排放和生命周期评价;城市微气候、建筑能耗与太阳能技术的相互影响;地理信息系统(GIS)和空间回归方法用于城市建筑能耗分析;不确定性、敏感性分析和机器学习方法应用于建筑能耗分析(R);贝叶斯方法用于城市和单体建筑能源分析 2: 过

- 2、孙老师:1.振动信号时频分析理论与测试系统设计 2.汽车检测系统设计 3.汽车电子控制系统设计

- 3、毕老师:机构动力学与控制

- 4、王老师:1.计算机网络安全 2.计算机仿真技术

- 5、周老师:1.智能机器人技术 2.智能检测与控制技术 3.机构运动学与动力学 4.机电一体化技术

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....