一种噪声信号处理装置和处理方法与流程

[0001]

本申请涉及无线通信领域,尤其是涉及一种噪声信号处理装置和处理方法。

背景技术:

[0002]

数字用户线(digital subscriber line,dsl)是在一对双绞线上进行数据传输的技术, 具体地,它包括:非对称数字用户线路(asymmetric digital subscriber line,adsl)、adsl2+、 超高速数字用户线路(very high speed dsl,vdsl)2、g.fast和v35b等技术。

[0003]

参见图1,表示应用dsl技术进行数据传输的示意图。它包含由局端设备和用户端设备 组成的通信系统;其中,局端设备和用户端设备之间通过双绞线相连接,并且采用dsl协议 在该双绞线进行数据传输。进一步地,在局端设备和用户端设备中都包括以下单元模块:数 字前端(digital front end,dfe)、模拟前端(analog front end,afe)、线路驱动器(line driver,ld)和混合(hybrid,h)电路等。

[0004]

局端设备和用户端设备之间可以互相双向传输数据,应用dsl技术传输数据时,需要采 用频分复用(frequency division duplex,fdd)方式对上行、下行频带进行划分。一般地, 局端设备向用户端设备传输数据称为下行传输,局端设备向用户端设备发送的信号称为下行 信号,下行传输使用的频率范围可称为下行频带;相反地,用户端设备向局端设备传输数据 称为上行传输,用户终端设备向局端设备发送的信号称为上行信号,上行传输使用的频率范 围可称为上行频带。

[0005]

例如,在v35b技术中应用的上行、下行频带划分如图2所示,分别包括三个上行频带和 三个下行频带。其中,上行频带用于传输上行数据流(up stream,us),对应的频带表示为 us0、us1和us2;下行频带用于传输下行数据流(down stream,ds),对应的频带表示为ds1、 ds2和ds3。上行、下行频带的信号可以同时进行数据传输,上行与下行频带之间又相互交叉, 当用户端设备在us0、us1或us2上发送上行信号时,由于用户端设备中的afe的发射通路和 ld特性的非理想环境,会产生一系列噪声,比如量化噪声、热噪、非线性噪声等,这些噪声 会经过hybrid电路回到用户端设备afe的接收侧,从而影响下行频带ds1、ds2和ds3的接 收性能。

[0006]

同理地,由于adsl、adsl2+、vdsl2和v35b等技术中对上行、下行频带的划分方式基本 兼容,所以adsl2+技术中,上行频带包括us0,频率范围是25khz~138khz,下行频带只有ds1 频率范围是138khz~2.2mhz。同样当用户端设备在us0发送上行信号时,afe和ld会在us0 以上频带产生带外噪声,该噪声经过hybrid电路后回到接收侧,与ds1的信号同频带,影响 ds1的性能。对于vdsl2技术,当双绞线环路距离较长时,由于线缆的衰减特性,只有us0 和ds1频带可用时,也存在带外噪声,与adsl2+中的问题相同。

技术实现要素:

[0007]

本申请实施例的技术方案,用于消除在频带us0以上的带外噪声。为了解决该技术

问题, 本申请实施例提供了如下技术方案:

[0008]

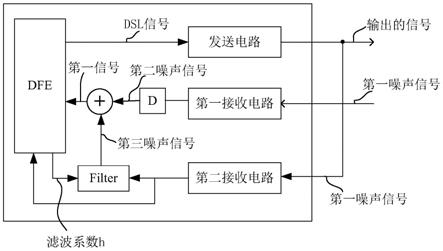

第一方面,本申请实施例提供了一种噪声信号处理装置,该装置包括数字前端dfe、发 送电路和第一接收电路,其中所述发送电路用于接收来自所述dfe的信号,并对所述信号进 行处理和放大后输出,所述输出的信号中包括第一噪声信号,且所述第一噪声信号流入至所 述第一接收电路;

[0009]

另外,该装置还包括第二接收电路、滤波模块、加法器模块和延迟模块;进一步地,所 述第一接收电路依次通过所述延迟模块和所述加法器模块,与所述dfe相连接,且所述第一 噪声信号经过所述第一接收电路和所述延迟模块处理后得到第二噪声信号;所述第二接收电 路与所述发送电路的输出端相连接,用于接收所述发送电路输出的所述第一噪声信号,以及 将所述第一噪声信号发送至所述滤波模块;所述滤波模块与所述dfe和所述第二接收电路相 连接,用于接收所述dfe发送的滤波系数,以及利用所述滤波系数对所述第二接收电路接收 的所述第一噪声信号进行滤波处理,得到第三噪声信号;所述加法器模块分别与所述延迟模 块和所述滤波模块相连接,用于对接收的所述第二噪声信号和所述第三噪声信号做相加处理 得到第一信号,并将所述第一信号发送给所述dfe。

[0010]

本方面提供的装置,通过增加第二接收电路来采集从发送电路泄漏的噪声信号,并通过 滤波模块按照滤波系数对该噪声信号进行滤波处理,与加法器模块中第一接收电路所采集的 噪声进行相加,从而抵消第一接收电路中的噪声,避免了带外噪声影响下行传输性能,本实 施例中利用回波来抵消噪声的方法,提升了下行业务速率。

[0011]

结合第一方面,在第一方面的一种可能的实现方式中,所述发送电路包括:数模转换器 dac、可编程增益放大器pga和线路驱动器ld,从所述dfe输出的所述dsl信号依次经过所 述pga和所述ld后,生成所述第一噪声信号。

[0012]

结合第一方面,在第一方面的另一种可能的实现方式中,所述装置还包括:第一高通滤 波器hpf1、第二高通滤波器hpf2和混合电路h;所述混合电路h设置在所述ld与所述hpf1 之间,用于将所述ld输出的所述第一噪声信号发送至所述hpf1;所述hpf1的输入端与所述 混合电路h相连接,输出端与所述第一接收电路相连接;所述hpf2的输入端与所述ld相连 接,输出端与所述第二接收电路相连接。本实现方式中,通过设置hpf1来滤波压制us0传输 的信号,使得在ds1频带内的噪声采集更为准确。

[0013]

结合第一方面,在第一方面的又一种可能的实现方式中,所述dfe根据所述第一接收电 路输出的信号和所述第二接收电路输出的信号确定滤波系数,并将所述滤波信息发送给所述 滤波模块。其中,所述滤波信息中包括所述滤波系数,本实现方式中,数字前端dfe通过第 一接收电路和第二接收电路发送的信号来确定滤波系数,从而为抵消第一噪声信号做准备。

[0014]

结合第一方面,在第一方面的又一种可能的实现方式中,所述第二噪声信号表示为s

n2

, 所述第三噪声信号表示为s

n3

,且s

n3

=s*h

_filter

,所述第一噪声信号s

n1

经过所述第二接收电 路处理后得到的信号表示为s,所述滤波系数表示为h

_filter

;所述加法器模块输出的所述第一 信号表示为y,具体地,y=s

n2

+s

n3

=s

n2

+s*h

_filter

=0。

[0015]

结合第一方面,在第一方面的又一种可能的实现方式中,所述装置还包括:变压器tf和 切换模块,所述tf的一端与所述混合电路h相连接;所述切换模块连接在所述hpf2和所述 第二接收电路之间,用于切换所述ld输出的所述第一噪声信号,和,通过所述tf采集

的双 绞线上的共模噪声。

[0016]

本实现方式中,在第二接收电路rx2通路中增加切换模块,比如开关选择电路,从而实 现了在adsl模式或vd长距模式下,开关切换到采集ld输出信号,训练滤波系数,抵消ld 输出噪声对rx性能影响;当在其他模式时,通过将开关选择电路切换到另一通路来采集变压 器初级的共模信号,从而抵消线缆上的共模噪声对接收电路rx性能的影响。

[0017]

第二方面,本实施例还提供了一种噪声信号处理方法,该方法可应用于噪声信号处理装 置,所述装置包括:数字前端dfe、发送电路和第一接收电路,其中所述发送电路用于接收 来自所述dfe的信号,并对所述信号进行处理和放大后输出,所述输出的信号中包括第一噪 声信号,且所述第一噪声信号流入至所述第一接收电路,所述装置还包括第二接收电路,

[0018]

具体地,所述方法包括:所述第一接收电路接收所述第一噪声信号,并将所述第一噪声 信号通过延迟处理后生成第二噪声信号;所述第二接收电路接收所述发送电路输出的所述第 一噪声信号,将所述第一噪声信号进行滤波处理得到第三噪声信号,其中所述滤波处理所使 用的滤波系数是所述dfe发送的;对所述第二噪声信号和所述第三噪声信号做相加处理得到 第一信号,并将所述第一信号发送给所述dfe。

[0019]

结合第二方面,在第二方面的一种可能的实现方式中,所述噪声信号处理装置还包括: 数模转换器dac、可编程增益放大器pga和线路驱动器ld,所述方法还包括;所述ld接收所 述pga输出的信号,并对所述信号进行放大生成所述第一噪声信号,其中所述pga输出的信 号是依次经过所述dac和所述pga处理之后输出的。

[0020]

结合第二方面,在第二方面的另一种可能的实现方式中,所述装置还包括:第一高通滤 波器hpf1、第二高通滤波器hpf2和混合电路h,所述方法还包括:所述混合电路h将所述 ld输出的所述第一噪声信号发送至所述hpf1,所述hpf1对所述第一噪声信号进行高通滤波 之后,输出至所述第一接收电路;所述hpf2接收所述第一噪声信号,并对所述第一噪声信号 进行高通滤波之后,输出至所述第二接收电路。

[0021]

结合第二方面,在第二方面的又一种可能的实现方式中,所述方法还包括:所述dfe根 据所述第一接收电路输出的信号和所述第二接收电路输出的信号确定滤波系数,以及发送所 述滤波系数。

[0022]

可选的,所述dfe将所述滤波系数发送给过滤模块。

[0023]

结合第二方面,在第二方面的又一种可能的实现方式中,所述得到第一信号包括:通过 以下表达式对所述第二噪声信号和所述第三噪声信号做相加处理得到所述第一信号:

[0024]

y=s

n2

+s

n3

=s

n2

+s*h

_filter

=0,

[0025]

其中,所述第一信号表示为y,所述第二噪声信号表示为s

n2

,所述第三噪声信号表示为 s

n3

,且s

n3

=s*h

_filter

,所述第一噪声信号s

n1

经过所述第二接收电路处理后得到的信号表示 为s,所述滤波系数表示为h

_filter

。

[0026]

结合第二方面,在第二方面的又一种可能的实现方式中,所述装置还包括:变压器tf和 切换模块,所述tf的一端与所述混合电路h相连接;所述方法还包括:所述切换模块切换所 述ld输出的所述第一噪声信号,和,通过所述tf采集的双绞线上的共模噪声。

[0027]

第三方面,本申请实施例还提供一种通信装置,包括处理器,所述处理器与存储器

耦合, 所述存储器用于存储指令;所述处理器用于执行所述存储器中的指令,使得所述通信装置执 行前述第二方面以及第二方面各种实现方式所述的方法。

[0028]

可选的,所述通信装置为前述第一方面或第一方面的各种实现方式中的所述噪声信号处 理装置。

[0029]

可选的,所述通信装置为一种端设备,进一步地,所述端设备包括局端设备和用户端设 备。

[0030]

可选的,所述通信装置为一种芯片或芯片系统,对于芯片来说,该芯片包括上述第一方 面以及第一方面的各种实现方式中的数字前端dfe、发送电路和第一接收电路,还包括第二 接收电路、滤波模块、加法器模块和延迟模块,用于实现前述的噪声信号处理方法。

[0031]

另外,所述芯片中包括存储单元,该存储单元中可用于存储计算机程序指令,并在执行 所述程序指令时,能够实现前述第一方面及第一方面的各种实现方式中的噪声信号处理方法。

[0032]

第四方面,本申请实施例还提供了一种通信系统,该系统包括至少一个局端设备,每个 局端设备和至少一个用户端设备之间通过双绞线连接,其中,所述局端设备或用户端设备为 前述第一方面或第一方面各种实现方式中的噪声信号处理装置。

[0033]

可选的,所述通信系统包括但不限于以下:千兆级别家庭网络g.hn系统、电力线载波通 信plc系统和有线电缆数据服务接口规范docsis系统。

[0034]

本申请实施例提供的装置,通过增加第二接收电路来采集从发送电路泄漏的噪声信号, 并通过滤波模块按照滤波系数对该噪声信号进行滤波处理,与加法器模块中第一接收电路所 采集的噪声进行相加,从而抵消第一接收电路中的噪声,避免了带外噪声影响下行传输性能, 本实施例中利用回波来抵消噪声的方法,提升了下行业务速率。

附图说明

[0035]

图1为本申请提供的一种应用dsl技术进行数据传输的示意图;

[0036]

图2为本申请提供的一种上行、下行频带划分的示意图;

[0037]

图3为本申请实施例提供的一种噪声信号处理装置的结构示意图;

[0038]

图4为本申请实施例提供的另一种噪声信号处理装置的结构示意图;

[0039]

图5为本申请实施例提供的又一种噪声信号处理装置的结构示意图;

[0040]

图6为本申请实施例提供的又一种噪声信号处理装置的结构示意图;

[0041]

图7为本申请实施例提供的一种通信装置的结构示意图。

具体实施方式

[0042]

为了使本技术领域的人员更好地理解本申请实施例中的技术方案,并使本申请实施例的 上述目的、特征和优点能够更加明显易懂,下面结合附图对本申请实施例中的技术方案作进 一步详细的说明。

[0043]

在对本申请实施例的技术方案说明之前,首先结合附图对本申请实施例的应用场景进行 说明。

[0044]

本申请的技术方案可应用于至少一个局端设备和至少一个用户端设备组成的通信系统, 比如,dsl系统,千兆级别家庭网络(gigabit-level home networking,g.hn)系

统,电力线 载波通信(power line communication,plc)系统,有线电缆数据服务接口规范(data over cable service interface specifications,docsis)系统等,只要在线路间存在串扰产生的 噪声,都可以应用本技术方案进行处理。

[0045]

进一步地,在dsl系统中,包括至少一个局端设备,每个局端设备和至少一个用户端设 备之间通过双绞线连接。对应的,g.hn系统、plc系统和docsis系统中,所述局端设备与用 户端设备之间分别用以太网、电力线、同轴电缆等传输介质连接。

[0046]

下面具体以dsl系统为例进行介绍,局端设备可以是数字用户线接入复接器(digital subscriber line access multiplexer,dslam),也可是集成了dsl接入业务功能单元的其他 设备。用户端设备可以是dsl调制解调器(modem),也可以是集成了dsl modem功能的路由 器或机顶盒等位于用户侧的设备。

[0047]

在实现本发明方式的所涉及结构和工作原理上,局端设备和用户端设备是对等的,即都 要进行相同的处理。具体地,如图3所示,表示一种端设备的结构示意图,该端设备可以是 局端设备,也可以是用户端设备,进一步地,该端设备包括:数字前端(digital front end, dfe)和模拟前端(analog front end,afe),另外,如图4所示,还可以包括线路驱动器(line driver,ld)、混合(hybrid,h)电路和变压器(transformer,tf)等。

[0048]

其中,在信号发送方向上,所述dfe用于实现数字用户线(digital subscriber line, dsl)信号调制解调和编解码功能。所述afe包括发送电路和第一接收电路rx1,进一步地, 所述发送电路中可以包括数模转换器(digital-analog converter,dac)和可编程增益放大 器(programable gain amplifier,pga),所述dac从所述dfe接收到信号(比如dsl信号 或xdsl信号)后,对该信号进行数模转换,然后将转换后的信号传输至pga进行增益放大, 最后将放大后信号传输至ld。

[0049]

ld主要用于将所述发送电路产生的模拟信号先放大,然后再驱动到线路上去以准备传输。

[0050]

hybrid电路,简称h电路,连接在所述发送电路的pga和第一接收电路rx1之间,用于 实现二四线转换功能,即对发送信号和接收信号进行隔离,具体主要用于实现以下功能:

[0051]

1、将ld输出的发送信号传输到线路上,以便能够通过双绞线进行传输;

[0052]

2、接收线路对端设备传输过来的信号,并将该接收信号发送给所述第一接收电路rx1;

[0053]

3、抑制ld的发送信号传到第一接收电路的lna。

[0054]

其中,所述第一接收电路rx1中可以包括lna和adc。

[0055]

变压器tf用于实现共模抑制、高通滤波器以及防护等功能。

[0056]

在信号接收方向上,第一接收电路rx1包括低噪声放大器(low noise amplifier,lna) 和模数转换器(analog-digital converter,adc),进一步地,lna用于接收来自对端的经 过hybrid电路的信号,然后将该信号传输至adc;adc用于对接收的信号进行模数转换,再 输出至dfe。可选的,所述lna中一般还集成增益可配置功能。

[0057]

本实施例提供的方法,用于消除在频带us0以上的带外噪声,该噪声主要包括以下两部 分组成:一部分是在所述发送电路中,数字用户线dsl信号从dac到pga后输出的噪声;另 一部分噪声是ld产生的噪声。需要说明的是,本申请实施例中所述的噪声泛指这两部分

噪声 的总和,并且在下面的实施例中,对噪声的抑制和消除,如果未特别说明,均指对从ld输出 的总的噪声(即上述两部分的噪声和),本实施例称之为第一噪声信号,可表示为s

n1

。

[0058]

下面对本申请的技术方案进行详细说明。

[0059]

本申请提供的技术方案,在各个端设备的基础上增加一个接收电路,比如第二接收电路 rx2,该第二接收电路rx2用于接收来自ld输出的发射(简称tx)信号,并将该tx信号经 过高通滤波器(high pass filter,hpf)滤波压制us0传输的信号,使得在ds1频带内的噪 声采集更为准确。

[0060]

dfe根据采集噪声数据和接收信号,计算滤波系数,使得采集的噪声经过滤波模块 (filter)处理后与原接收通路内的噪声互相抵消,从而消除带外噪声,提升接收链路性能。

[0061]

如图3所示,本实施例提供了一种噪声信号处理装置的结构示意图,该装置可以是局端 设备,也可以是用户端设备,本实施例对此不进行限制。

[0062]

具体地,该装置包括:dfe、发送电路和第一接收电路rx1,另外,还包括第二接收电路 rx2、滤波模块filter、加法器模块“+”和延迟模块(delay,d)等。

[0063]

其中,所述发送电路,用于接收来自所述dfe的信号,并对所述信号进行处理和放大后 输出,所述输出的信号中包括第一噪声信号,且所述第一噪声信号流入至所述第一接收电路。 可选的,所述来自dfe的信号为dsl信号。

[0064]

所述第一接收电路接收该第一噪声信号之后,对第一噪声信号进行处理,然后依次通过 所述延迟模块和所述加法器模块,最后流入所述dfe。其中,所述第一噪声信号经过所述第 一接收电路和所述延迟模块处理后得到第二噪声信号。

[0065]

所述第二接收电路与所述发送电路的输出端相连接,用于接收所述发送电路输出的所述 第一噪声信号,以及将所述第一噪声信号发送至所述滤波模块。

[0066]

所述滤波模块与所述dfe和所述第二接收电路相连接,用于接收所述dfe发送的滤波系 数,以及利用所述滤波系数对所述第二接收电路接收的所述第一噪声信号进行滤波处理,得 到第三噪声信号。

[0067]

所述加法器模块分别与所述延迟模块和所述滤波模块相连接,用于对接收的所述第二噪 声信号和所述第三噪声信号做相加处理得到第一信号,并将所述第一信号发送给所述dfe。

[0068]

可选的,如图4所示,所述发送电路包括:数模转换器dac、可编程增益放大器pga和 线路驱动器ld,从所述dfe输出的dsl信号或xdsl信号依次经过所述pga和所述ld后,生 成输出信号,该输出信号中有一部分通过混合电路流入到第一接收电路中,该流入到所述第 一接收电路的信号称为第一噪声信号。

[0069]

进一步地,如图5所示,该装置还包括第一高通滤波器hpf1和第二高通滤波器hpf2。 所述混合电路h设置在所述ld与所述hpf1之间,用于将所述ld输出的所述第一噪声信号发 送至所述hpf1;所述hpf1的输入端与所述混合电路h相连接,输出端与所述第一接收电路 的lna1相连接,即该hpf1设置在第一接收电路rx1和所述混合电路h之间,用于对所述混 合电路h输出的第一噪声信号进行滤波处理,并输入至所述第一接收电路rx1。

[0070]

本实施例中通过设置hpf1来滤波压制us0传输的信号,使得在ds1频带内的噪声采集更 为准确。

[0071]

另外,所述装置还包括衰减网络,所述衰减网络的设置在所述ld的输出端和第二

接收电 路的输入端之间,可选的,在所述衰减网络和所述第二接收电路之间还包括hpf2,该hpf2 用于过滤泄漏到ds1频带的噪声,使得采集的输入至第二接收电路rx2的噪声更准确。

[0072]

进一步地,如图5所示,所述第一噪声信号表示为s

n1

,所述第二噪声信号表示为s

n2

, 所述第三噪声信号表示为s

n3

,且s

n3

=s*h

_filter

,所述第一噪声信号s

n1

经过所述第二接收电 路处理后得到的信号表示为s,所述滤波系数表示为h

_filter

,所述加法器模块输出的所述第一 信号表示为y,其中,y=s

n2

+s

n3

=s

n2

+s*h

_filter

=0,并且“*”从时域看表示卷积运算, 从频域看表示乘法运算。一般地,本申请实施例中均表示时域上的卷积运算。

[0073]

另外,所述dfe用于根据所述第一接收电路rx1输出的第二噪声信号s

n2

,和,所述第一 噪声信号经过所述第二接收电路rx2处理后的信号s,确定滤波系数h

_filter

,并将该滤波系数 h

_filter

输入至所述滤波模块;所述滤波模块用于根据所述滤波系数h

_filter

对经过所述第二接收 电路rx2的信号s进行滤波处理生成第三噪声信号s

n3

,并该第三噪声信号s

n3

输出至所述加 法器模块。其中,s

n3

=s*h

_filter

。

[0074]

dfe通过第二接收电路rx2通路采集的tx输出噪声,以及通过rx1采集到tx经过hybrid 电路泄漏到正常接收通路(第一接收电路rx1)的噪声,经过计算可以得到一组滤波器系数 h

_filter

,并分配给过滤模块,以及将延时参数分配给delay模块,使得rx2电路采集的噪声经 过过滤模块后与经过hybrid电路泄漏到rx1电路的噪声幅度相等、相位相反,最后经过加法 器模块后抵消掉rx1电路中的tx泄露噪声,从而提升接收性能。

[0075]

其中,延迟模块用于匹配正常接收通路rx1和采集通路rx2的延时关系,使得在加法器 位置两者噪声信号相位相反,即s

n2

=-s

n3

。

[0076]

可选的,第一接收电路rx1中包括第一模数转换器adc1和第一低噪声放大器lna1;所 述第二接收电路rx2中包括第二模数转换器adc2和第二低噪声放大器lna2。此外,所述rx1 和rx2中还可以包括其他更多或更少的功能单元/模块,本实施例对此不进行限制。

[0077]

本实施例提供的装置,通过增加第二接收电路来采集从ld通路泄漏的噪声信号,并通过 滤波模块按照滤波系数对该噪声信号进行滤波处理,与加法器模块中第一接收电路所采集的 噪声进行相加,从而抵消第一接收电路中的噪声,避免了带外噪声影响下行传输性能,本实 施例中利用回波来抵消噪声的方法,提升了下行业务速率。

[0078]

下面根据图4或图5所示的结构示意图,对信号流的传输过程进行说明。

[0079]

以图5为例,上行传输信号流的走向为:dfe

→

dac

→

fga

→

ld

→

;其中,ld通路输出噪 声信号x中包括噪声,该噪声为带外噪声,由两部分组成,参见上述带外噪声的描述,此处 不再赘述。

[0080]

下行传输中,经过ld输出的信号和噪声通过h电路后产生第一噪声信号,并将该第一噪 声信号输入至第一接收电路rx1,信号流或称第一通路的信号流的走向为:

[0081]

(1)ld

→

h电路

→

hpf1

→

lna1

→

adc1

→

d

→

加法器模块

→

dfe。

[0082]

本实施例,新增的第二接收电路rx2所对应的下行信号流或称第二通路的信号流走向为:

[0083]

(2)ld

→

衰减网络

→

hpf2

→

lna2

→

adc2

→

filter

→

加法器模块

→

dfe。

[0084]

第一、对于第一通路的信号流(1)的处理过程:

[0085]

假设ld通路输出信号和噪声为x,混合电路hybrid的回波抑制特性为h-hybird

,hpf1

的 滤波特征为h-hpf1

,lna1的特征为h-lna1

,adc1的特征为h-adc1

,则存在以下关系:

[0086]

噪声信号x输入至h电路后,经过hybrid电路的回波抑制特性,输入信号为第一噪声信 号s

n1

=x*h

_hybird

,该信号第一噪声信号经过hpf1后输出为x*h-hybird

*h-hpf1

,再依次经过lna1 噪声放大和adc1,将模拟信号转换为数字信号处理后,输出第二噪声信号s

n2

,其中,关系 式为s

n2

=x*h-hybird

*h-hpf1

*h-lna1

*h-adc1

。

[0087]

所述第二噪声信号s

n2

经过delay模块后输入至加法器模块;并且,在滤波模块未配置滤 波系数时,所述第二噪声信号s

n2

直接输入给dfe,即dfe可以直接获得该噪声。

[0088]

第二、对于第二通路的信号流(2)的处理过程:

[0089]

ld通路输出的信号和噪声为x,衰减网络的衰减特性为h-atte

,hpf2的滤波特征为h-hpf2

, lna2的特征为h-lna2

,adc2的特征为h-adc2

,则存在以下关系:

[0090]

输出信号和噪声x输入至衰减网络后,经过衰减特性h-atte

处理后输出信号为x*h-atte

,该 信号经过hpf2后输出为x*h-atte

*h-hpf2

,然后再依次经过lna2噪声放大和adc2模数转换后 输出,该输出的信号为s,其中,s=x*h-atte

*h-hpf2

*h-lna2

*h-adc2

。

[0091]

adc2将该输出信号s传输至dfe,dfe接收信号s,并根据上述获得的第二噪声信号s

n2

计 算可以得到一组滤波系数h

_filter

,然后将该滤波系数h

_filter

发送给滤波模块。

[0092]

所述滤波模块的第一输入端接收adc2输出的信号s,其第二输入端接收dfe发送的滤波 系数h

_filter

,然后利用该滤波系数对该信号s做滤波处理,生成第三噪声信号s

n3

,关系式为, s

n3

=s*h

_filter

,即s

n3

=s*h

_filter

=(x*h-atte

*h-hpf2

*h-lna2

*h-adc2

)*h

_filter

。

[0093]

第三、滤波模块和加法器模块的处理过程:

[0094]

在滤波模块中,将经过滤波系数h

_filter

处理后生成的第三噪声信号s

n3

与第一通路信号流 的第二噪声信号s

n2

相叠加可以互相抵消,具体地,信号叠加处理过程包括:

[0095]

y=s

n2

+s

n3

=s

n2

+s*h

_filter

=0,为了使输出第一信号y趋近于0,配置滤波系数h

_filter

时 期望达到,s

n2

=-s

n3

,

[0096]

即x*h-hybird

*h-hpf1

*h-lna1

*h-adc1

=-(x*h-atte

*h-hpf2

*h-lna2

*h-adc2

)*h

_filter

,

[0097]

变形后得到滤波系数:

[0098][0099]

由于在实际配置中,系统的各个模块的特性比较复杂,无法整除得到一个滤波系数使得 h

_filter

完全等于所以一般地,采用最小二乘法使得滤波系 数逼近于目标值,即从而使得经过加法器模块后 的输出信号y接近于0,进而达到抵消第一噪声信号的效果。

[0100]

其中,延迟模块(delay)用于同步所述第二噪声信号s

n2

和经滤波处理后的第三噪声信 号s

n3

,进而保证加法器模块确定输出信号时,同时获取所述经过滤波模块处理的第二噪声信 号s

n3

和第二噪声信号s

n2

。

[0101]

可选的,在本实施例的另一种可能实现中,如图6所示,所述装置还包括:变压器 (transformer,tf)和切换模块,所述tf的一端与混合电路h相连接,tf用于接收对端发 送

的信号/数据,以及该信号或数据传输至混合电路h。

[0102]

所述切换模块包括至少两个端口(或称接入点),本实施例中假设切换模块包括两个端口, 分别是第一端口和第二端口,其中,所述切换模块的第一端口与ld的输出端相连接;进一步 地,ld输出的信号经过衰减网络和hpf2后,通过所述第一端口输入至lna2。

[0103]

所述切换模块的第二端口与tf的另一端相连接,所述tf的另一端接收双绞线上的共模 噪声;所述切换模块的输出端与第二接收电路rx2的输入端相连接。所述切换模块用于切换 所述ld输出的所述第一噪声信号,和,通过所述tf采集的双绞线上的共模噪声。

[0104]

可选的,所述切换模块为开关选择电路,所述第一端口为a,第二端口为b,当所述开关 选择电路的第一端口a连通时,lna2用于接收并处理来自ld通路输出的噪声信号,以及减 小带外噪声。具体的,信号流的走向以及对噪声的处理过程,参见上述实施例描述,此处不 再赘述。

[0105]

当开关选择电路的第二端口b连通时,lna2用于接收并处理来自变压器tf的共模信号, 从而抵消线缆上产生的共模噪声,避免该共模噪声影响下行数据传输。更进一步地,这种情 况下,信号流的走向为:tf

→

lna2

→

adc2

→

filter

→

加法器模块

→

dfe。

[0106]

本实现方式中,在第二接收电路rx2通路中增加切换模块,比如开关选择电路,从而实 现了在adsl模式或vd长距模式下,开关切换到采集ld输出信号,训练滤波系数,抵消ld 输出噪声对rx性能影响;当在其他模式时,通过将开关选择电路切换到另一通路来采集变压 器初级的共模信号,从而抵消线缆上的共模噪声对rx性能的影响。

[0107]

另外,本申请实施例还提供了一种噪声信号处理方法,所述方法应用于上述噪声信号处 理装置,所述装置包括:dfe、发送电路和第一接收电路,还包括第二接收电路、滤波模块、 加法器模块和延迟模块,所述方法包括:

[0108]

步骤1:发送电路接收来自所述dfe的数字用户线dsl信号,并对所述dsl信号进行处 理和放大后输出,所述输出的信号中包括第一噪声信号,且所述第一噪声信号流入至所述第 一接收电路;

[0109]

步骤2:第一接收电路接收所述第一噪声信号,并将所述第一噪声信号通过所述延迟模 块做延迟处理后生成第二噪声信号;

[0110]

步骤3:第二接收电路接收所述发送电路输出的所述第一噪声信号,将所述第一噪声信 号发送至所述滤波模块;

[0111]

步骤4:滤波模块接收所述dfe发送的滤波系数,和所述第二接收电路发送的所述第一 噪声信号,利用所述滤波系数对所述第一噪声信号进行滤波处理得到第三噪声信号,将所述 第三噪声信号发送至所述加法器模块;

[0112]

步骤5:加法器模块分别接收所述第二噪声信号和所述第三噪声信号,对所述第二噪声 信号和所述第三噪声信号做相加处理得到第一信号,并将所述第一信号发送给所述dfe。

[0113]

可选的,在本实施例的一种具体的实现方式中,所述噪声信号处理装置还包括:数模转 换器dac、可编程增益放大器pga和线路驱动器ld,所述方法还包括;所述ld接收所述pga 输出的信号,并对所述信号进行放大生成所述第一噪声信号,其中所述pga输出的信号是依 次经过所述dac和所述pga处理之后输出的。

[0114]

可选的,在本实施例的另一种具体的实现方式中,所述装置还包括:第一高通滤波

器hpf1、 第二高通滤波器hpf2和混合电路h;所述方法还包括:所述混合电路h将所述ld输出的所 述第一噪声信号发送至所述hpf1,所述hpf1对所述第一噪声信号进行高通滤波之后,输出 至所述第一接收电路;所述hpf2接收所述第一噪声信号,并对所述第一噪声信号进行高通滤 波之后,输出至所述第二接收电路。

[0115]

可选的,在本实施例的又一种具体的实现方式中,还包括:所述dfe根据所述第一接收 电路输出的信号和所述第二接收电路输出的信号确定滤波系数,以及发送给所述滤波系数。

[0116]

可选的,在上述步骤5中得到的第一信号的过程包括:加法器模块通过以下表达式对所 述第二噪声信号和所述第三噪声信号做相加处理得到所述第一信号:

[0117]

y=s

n2

+s

n3

=s

n2

+s*h

_filter

=0,

[0118]

其中,所述第一信号表示为y,所述第二噪声信号表示为s

n2

,所述第三噪声信号表示为 s

n3

,且s

n3

=s*h

_filter

,所述第一噪声信号s

n1

经过所述第二接收电路处理后得到的信号表示 为s,所述滤波系数表示为h

_filter

。

[0119]

可选的,在本实施例的又一种具体的实现方式中,所述装置还包括:变压器tf和切换模 块,所述tf的一端与所述混合电路h相连接;所述方法还包括:切换模块切换所述ld输出 的所述第一噪声信号,和,通过所述tf采集的双绞线上的共模噪声。

[0120]

本实施例提供的方法,通过增加第二接收电路来采集从ld通路泄漏的噪声信号,并通过 滤波模块按照滤波系数对该噪声信号进行滤波处理,与加法器模块中第一接收电路所采集的 噪声进行相加,从而抵消第一接收电路中的噪声,避免了带外噪声影响下行传输性能,本实 施例中利用回波来抵消噪声的方法,提升了下行业务速率。

[0121]

进一步地,在具体硬件实现层面上,本申请实施例还提供了一种通信装置,用于实现前 述实施例所述的方法的部分或全部步骤。本实施例所述的通信装置可以是前述实施例的局端 设备,或者还可以是用户端设备。

[0122]

参见图7所示,该通信装置包括:收发器701、处理器702和存储器703,此外,该通信 装置还可以包括更多或更少的部件,或者组合某些部件,或者不同的部件布置,比如通信接 口、传输总线等,本申请对此不进行限定。

[0123]

具体地,收发器701用于建立通信信道,使通信装置能够通过该通信信道连接至dsl系 统,从而实现端到端设备之间的通信传输。进一步地,收发器701可以包括接收机、发射机 与天线等部件,或者还可以包括接收机和发射机等射频部件,进一步地,所述射频部件可以 包括无线局域网(wireless local area network,wlan)模块、蓝牙模块、基带(base band) 模块等至少部分通信模块,以及所述通信模块对应的射频(radio frequency,rf)电路,用 于进行无线局域网络通信、蓝牙通信、红外线通信及/或蜂窝式通信系统通信,例如宽带码分 多重接入(wideband code division multiple access,wcdma)及/或高速下行封包存取(high speed downlink packet access,hsdpa)。此外,收发器701还用于控制通信装置中的各组 件间的通信,并且可以支持直接内存存取(direct memory access)。

[0124]

处理器702为通信装置的控制中心,利用各种接口和线路连接整个硬件设备的各个部分, 通过运行或执行存储在存储器703内的软件程序和/或模块,以及调用存储在存储器内的数 据,以执行所述终端设备的各种功能。

[0125]

进一步地,处理器702可以包括一个或多个集成电路(integrated circuit,ic)或芯 片,例如可以包括单颗封装的ic,也可以包括连接多颗相同功能或不同功能的封装ic。举例 来说,处理器可以仅包括cpu,也可以是进一步包括gpu、数字信号处理器(digital signal processor,dsp)、及收发模块中的控制芯片的组合。

[0126]

存储器703用于存储执行本申请技术方案的计算机程序代码,并由处理器702来控制执 行。进一步地,处理器702用于执行存储器703中存储的计算机程序代码,实现上述实施例 中的方法。

[0127]

进一步地,存储器703可以是只读存储器(read-only memory,rom)或可存储静态信息 和指令的其他类型的静态存储设备,随机存取存储器(random access memory,ram)或者可 存储信息和指令的其他类型的动态存储设备,也可以是电可擦可编程只读存储器 (electrically erasable programmable read-only memory,eeprom)、只读光盘(compact disc read-only memory,cd-rom)或其他光盘存储、光碟存储(包括压缩光碟、激光碟、光 碟、数字通用光碟、蓝光光碟等)、磁盘存储介质或者其他磁存储设备、或者能够用于携带或 存储具有指令或数据结构形式的期望的程序代码并能够由计算机存取的任何其他介质,但不 限于此。存储器可以是独立存在,也可以和处理器集成在一起。

[0128]

可选的,所述通信装置可以是一种芯片或芯片系统,对于芯片来说,该芯片包括上述实 施例中的数字前端dfe、发送电路和第一接收电路,还包括第二接收电路、滤波模块、加法 器模块和延迟模块,并且各个模块之间的连接关系参见上述图3至图6所示的结构,用于实 现上述实施例中的噪声信号处理方法。

[0129]

本申请的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似 的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可 以互换,以便这里描述的实施例能够以除了在这里图示或描述的内容以外的顺序实施。此外, 术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了 一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元, 而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

[0130]

本领域的技术人员可以清楚地了解到本申请实施例中的技术可借助软件加必需的通用硬 件平台的方式来实现。基于这样的理解,本申请实施例中的技术方案本质上或者说对现有技 术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品可以存储在存储介质 中,如rom/ram、磁碟、光盘等,包括若干指令用以使得一台计算机设备(可以是个人计算 机,服务器,或者网络设备等)执行本发明各个实施例或者实施例的某些部分所述的方法。

[0131]

本说明书中各个实施例之间相同相似的部分互相参见即可。尤其,对于终端设备而言, 由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例中的说明即 可。

[0132]

以上所述的本申请实施方式并不构成对本申请保护范围的限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1