同步方法、装置、设备及存储介质与流程

1.本技术涉及通信领域,尤其涉及同步方法、装置、设备及存储介质。

背景技术:

2.随着传统时分复用(timedivision multiplex,tdm)系统与信息包技术的融合,固定比特率(constant bit rate,cbr)服务在分组包交换网络中的传输需要考虑其应用的同步需求。对此,g.8260标准和g.8261标准给出了分组包交换网络中同步和定时相关的定义和术语,它介绍了一种通过信息包到达客户端的时戳值来恢复tdm时钟和/或时间的方式,称为自适应时钟恢复(adaptive clock recovery,acr)和/或自适应时间恢复(adaptive time recovery,atr)。

3.然而,由于中间网络存在交换设备、业务流的动态调度、时延等因素,会引入链路噪声,使得信息包经过中间网络到达客户端的时间发生变化,产生包时延变化量(packetdelay variation,pdv)。与物理层的时钟信号抖动和漂移相比,pdv噪声往往要大得多,因此,若采用acr和/或atr的方式恢复cbr业务时钟和/或时间,对pdv的降噪处理将是时钟和/或时间同步中最重要的环节之一。

技术实现要素:

4.本技术实施例提供了一种同步方法、装置、设备及存储介质,以解决时间和/或时钟同步精度不高的问题,技术方案如下:

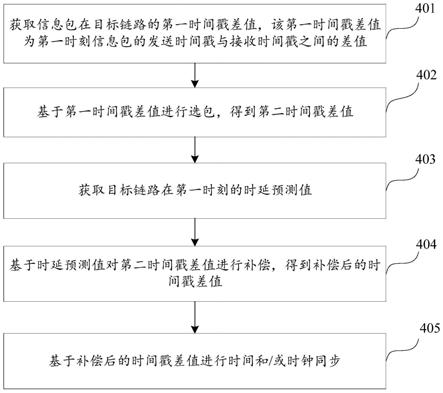

5.一方面,提供了一种同步方法,该方法可应用于网络设备,该方法包括:获取信息包在目标链路的第一时间戳差值,该第一时间戳差值为第一时刻信息包的发送时间戳与接收时间戳之间的差值;基于该第一时间戳差值进行选包,得到第二时间戳差值。之后,获取目标链路在第一时刻的时延预测值,基于该时延预测值对第二时间戳差值进行补偿,得到补偿后的时间戳差值;基于该补偿后的时间戳差值进行时间和/或时钟同步。

6.本技术实施例提供的方法,通过获取目标链路的时延预测值,基于该时延预测值对选包得到的第二时间戳差值进行补偿,也即是对目标链路引入的pdv噪声进行补偿,减少了pdv噪声,使得到的补偿后的时间戳差值更加直接地反映晶振相对于频率基准源的频偏和相偏信息,从而基于该补偿后的时间戳差值进行时间和/或时钟同步之后,同步的精度更高,提高了同步性能。

7.在一种示例性实施例中,获取所述目标链路在所述第一时刻的时延预测值,包括:根据所述目标链路的时延相关数据预测所述目标链路在所述第一时刻的时延预测值,其中,所述时延相关数据包括如下数据中的至少一种:

8.所述目标链路在第二时刻的时延预测值或时间戳差值,所述第二时刻早于所述第一时刻;

9.所述目标链路在所述第一时刻的与时延相关的网络参数数据。

10.在一种示例性实施例中,获取所述目标链路在所述第一时刻的时延预测值,包括:

获取所述目标链路在第一周期内的时延预测值序列,所述时延预测值序列中包括所述目标链路在所述第一时刻的时延预测值。

11.在一种示例性实施例中,所述获取所述目标链路在第一周期内的时延预测值序列,包括:根据所述目标链路在第二周期内的时延预测值序列或时间戳差值序列预测所述目标链路在所述第一周期内的时延预测值序列,所述第二周期是所述第一周期的前一周期。

12.在一种示例性实施例中,所述获取所述目标链路在所述第一时刻的时延预测值,包括:通过预测模型对所述目标链路的时延进行预测,得到所述目标链路在所述第一时刻的时延预测值。

13.在一种示例性实施例中,所述通过预测模型对所述目标链路的时延进行预测之前,还包括:基于所述目标链路获取用于训练所述预测模型的时延相关数据;通过所述时延相关数据进行模型训练,得到所述预测模型。

14.在一种示例性实施例中,所述时延相关数据包括所述目标链路的时间戳差值序列以及与时延相关的网络参数数据中的至少一种数据。

15.在一种示例性实施例中,所述与时延相关的网络参数包括目标网络节点的数量、所述目标网络节点通过所述目标链路传输的流量以及添加时间戳时对应的时间中的至少一种,所述目标网络节点包括所述信息包的发送设备和接收设备,以及所述发送设备和接收设备之间的网络设备。

16.在一种示例性实施例中,所述通过所述时延相关数据进行模型训练,得到所述预测模型,包括:在进行模型训练的过程中,将所述目标链路在第三周期内的时间戳差值序列作为样本,并将所述目标链路在第四周期内的时间戳差值序列作为标签,其中,所述第三周期为所述第四周期的前一周期;或者,

17.在进行模型训练的过程中,将所述目标链路在目标时刻的与时延相关的网络参数作为样本,并将所述目标链路在所述目标时刻的时间戳差值作为标签;或者,

18.在进行模型训练的过程中,将所述目标链路在第三周期内的时间戳差值序列、以及所述目标链路在目标时刻的与时延相关的网络参数作为样本,并将所述目标链路在所述目标时刻的时间戳差值作为标签,其中,所述目标时刻为所述第三周期的下一时刻。

19.在一种示例性实施例中,所述基于所述补偿后的时间戳差值进行时间和/或时钟同步,包括:对所述补偿后的时间戳差值进行环路滤波,得到第二环路滤波结果;对所述第二环路滤波结果进行直接数字频率合成,得到第二频率和/或相位调整值;基于所述第二频率和/或相位调整值进行时间和/或时钟同步。

20.在一种示例性实施例中,以在线方式获取所述时延相关数据时,在获取所述时延相关数据之前,还包括:获取跟踪基准源得到的时间信息,鉴别所述时间信息的相位差,得到相位差鉴别结果;将所述相位差鉴别结果进行环路滤波,得到第一环路滤波结果;对所述第一环路滤波结果进行直接数字式频率合成,得到第一频率和/或相位调整值;基于所述第一频率和/或相位调整值进行时间和/或时钟同步。

21.提供了一种同步装置,所述装置包括:

22.获取模块,用于获取信息包在目标链路的第一时间戳差值,所述第一时间戳差值为第一时刻,所述信息包的发送时间戳与接收时间戳之间的差值;

23.选包模块,用于基于所述第一时间戳差值进行选包,得到第二时间戳差值;

24.补偿模块,用于获取所述目标链路在所述第一时刻的时延预测值,基于所述时延预测值对所述第二时间戳差值进行补偿,得到补偿后的时间戳差值;

25.同步模块,用于基于所述补偿后的时间戳差值进行时间和/或时钟同步。

26.在一种示例性实施例中,所述获取模块,用于获取所述目标链路在第一周期内的时延预测值序列,所述时延预测值序列中包括所述目标链路在所述第一时刻的时延预测值。

27.在一种示例性实施例中,所述获取模块,用于根据所述目标链路在第二周期内的时延预测值序列或时间戳差值序列预测所述目标链路在所述第一周期内的时延预测值序列,所述第二周期是所述第一周期的前一周期。

28.在一种示例性实施例中,所述获取模块,用于通过预测模型对所述目标链路的时延进行预测,得到所述目标链路在所述第一时刻的时延预测值。

29.在一种示例性实施例中,所述装置,还包括:

30.训练模块,用于基于所述目标链路获取用于训练所述预测模型的时延相关数据;通过所述时延相关数据进行模型训练,得到所述预测模型。

31.在一种示例性实施例中,时延相关数据包括所述目标链路的时间戳差值序列以及与时延相关的网络参数数据中的至少一种数据。

32.在一种示例性实施例中,所述与时延相关的网络参数数据包括目标网络节点的数量、所述目标网络节点通过所述目标链路传输的流量以及添加时间戳时对应的时间中的至少一种,所述目标网络节点包括所述信息包的发送设备和接收设备,以及所述发送设备和接收设备之间的网络设备。

33.在一种示例性实施例中,所述训练模块,用于:

34.在进行模型训练的过程中,将所述目标链路在第三周期内的时间戳差值序列作为样本,并将所述目标链路在第四周期内的时间戳差值序列作为标签,其中,所述第三周期为所述第四周期的前一周期;或者,

35.在进行模型训练的过程中,将所述目标链路在目标时刻的与时延相关的网络参数作为样本,并将所述目标链路在所述目标时刻的时间戳差值作为标签;或者,

36.在进行模型训练的过程中,将所述目标链路在第三周期内的时间戳差值序列、以及所述目标链路在目标时刻的与时延相关的网络参数作为样本,并将所述目标链路在所述目标时刻的时间戳差值作为标签,其中,所述目标时刻为所述第三周期的下一时刻。

37.在一种示例性实施例中,所述同步模块,用于对所述补偿之后的时间戳差值进行环路滤波,得到第二环路滤波结果;对所述第二环路滤波结果进行直接数字频率合成,得到第二频率和/或相位调整值;基于所述第二频率和/或相位调整值进行时间和/或时钟同步。

38.在一种示例性实施例中,所述同步模块,还用于获取跟踪基准源得到的时间信息,鉴别所述时间信息的相位差,得到相位差鉴别结果;将所述相位差鉴别结果进行环路滤波,得到第一环路滤波结果;对所述第一环路滤波结果进行直接数字式频率合成,得到第一频率和/或相位调整值;基于所述第一频率和/或相位调整值进行时间和/或时钟同步。

39.还提供一种同步设备,该设备包括:存储器及处理器,所述存储器中存储有至少一条指令,所述至少一条指令由所述处理器加载并执行,以实现上述任一所述的同步方法。

40.还提供了一种计算机可读存储介质,所述存储介质中存储有至少一条指令,所述指令由处理器加载并执行以实现如上任一所述的同步方法。

41.提供了另一种通信装置,该装置包括:收发器、存储器和处理器。其中,该收发器、该存储器和该处理器通过内部连接通路互相通信,该存储器用于存储指令,该处理器用于执行该存储器存储的指令,以控制收发器接收信号,并控制收发器发送信号,并且当该处理器执行该存储器存储的指令时,使得该处理器执行上述任一种可能的实施方式中的方法。

42.作为一种示例性实施例,所述处理器为一个或多个,所述存储器为一个或多个。

43.作为一种示例性实施例,所述存储器可以与所述处理器集成在一起,或者所述存储器与处理器分离设置。

44.在具体实现过程中,存储器可以为非瞬时性(non-transitory)存储器,例如只读存储器(read only memory,rom),其可以与处理器集成在同一块芯片上,也可以分别设置在不同的芯片上,本技术实施例对存储器的类型以及存储器与处理器的设置方式不做限定。

45.提供了一种计算机程序(产品),所述计算机程序(产品)包括:计算机程序代码,当所述计算机程序代码被计算机运行时,使得所述计算机执行上述各方面中的方法。

46.提供了一种芯片,包括处理器,用于从存储器中调用并运行所述存储器中存储的指令,使得安装有所述芯片的通信设备执行上述各方面中的方法。

47.提供另一种芯片,包括:输入接口、输出接口、处理器和存储器,所述输入接口、输出接口、所述处理器以及所述存储器之间通过内部连接通路相连,所述处理器用于执行所述存储器中的代码,当所述代码被执行时,所述处理器用于执行上述各方面中的方法。

附图说明

48.图1为本技术实施例提供的1588时延响应机制过程示意图;

49.图2为本技术实施例提供的apts应用场景结构示意图;

50.图3为本技术实施例提供的pts应用场景结构示意图;

51.图4为本技术实施例提供的同步方法流程图;

52.图5为本技术实施例提供的apts应用场景下的模型训练过程示意图;

53.图6为本技术实施例提供的apts应用场景下的同步过程示意图;

54.图7为本技术实施例提供的pts应用场景下的模型训练过程示意图;

55.图8为本技术实施例提供的pts应用场景下的同步过程示意图;

56.图9为本技术实施例提供的同步装置的结构示意图;

57.图10为本技术实施例提供的同步装置的结构示意图;

58.图11为本技术实施例提供的同步设备的结构示意图。

具体实施方式

59.本技术的实施方式部分使用的术语仅用于对本技术的实施例进行解释,而非旨在限定本技术。

60.随着传统时分复用(timedivision multiplex,tdm)系统与信息包技术的融合,固定比特率(constantbit rate,cbr)服务在分组包交换网络中的传输需要考虑其应用的同

步需求。对此,g.8260标准和g.8261标准给出了分组包交换网络中同步和定时相关的定义和术语,它介绍了一种通过信息包到达客户端的时戳值来恢复tdm时钟的方式,称为自适应时钟恢复(adaptive clock recovery,acr),通过信息包到达客户端的时戳值来恢复tdm时间的方式,称为自适应时间恢复(adaptive time recovery,atr)。

61.然而,由于中间网络存在交换设备、业务流的动态调度、时延等因素,会引入链路噪声,使得信息包经过中间网络到达客户端的时间发生变化,产生pdv。与物理层的时钟信号抖动和漂移相比,pdv噪声往往要大得多,它不仅仅是由网络元器件的噪声导致,还与网络架构和调度方式密切相关,并且可能包含由于网络流量周期变化的极低频噪声。因此,若采用acr和/或atr的方式恢复cbr业务时钟和/或时间,对pdv的降噪处理将是时钟和/或时间同步中最重要的环节之一。

62.例如,在支持带全球定位系统(global positioning system,gps)辅助的时间同步(assisted partial timing support,apts)同步过程中,gps下沉到闭合用户组(closed subscriber group,csg)位置,网络透传1588报文。也就是说,正常情况下,用gps进行时间同步,异常情况采用透传的1588报文争取维护窗口。1588报文是电气和电子工程师协会(institute of electrical and electronics engineers,ieee)1588协议标准报文。其中,ieee 1588协议标准全称是网络测量和控制系统的精密时钟同步协议标准(ieee 1588precision clock synchronization protocol),简称精确定时协议(precision timing protocol,ptp)。ieee1588协议的同步原理,所提出的时延响应机制(delay request-response mechanism)如图1所示。

63.图1中,主时钟与从时钟之间传输的ptp报文包括:(1)同步(sync)报文、(2)跟随(follow_up)报文、(3)时延请求(delay_req)报文和(4)时延响应(delay_resp)报文。时延响应同步机制的报文收发流程包括如下几个步骤:

64.第一步,主时钟周期性的发出sync同步报文,并记录下sync同步报文离开主时钟的精确发送时间戳t1。另外,sync同步报文是周期性发出,可以携带或者不携带发送时间信息。

65.第二步,主时钟将精确的发送时间戳t1封装到follow_up跟随报文中,发送给从时钟。

66.第三步,从时钟记录sync同步报文到达从时钟的精确到达时间戳t2。

67.第四步,从时钟发出delay_req时延请求报文,并且记录下精确发送时间戳t3。

68.第五步,主时钟记录下delay_resp时延响应报文到达主时钟的精确到达时间戳t4。

69.第六步,主时钟发出携带精确时间戳t4的delay_resp报文给从时钟,从时钟由此得到了t1、t2、t3和t4四个精确报文收发时间。

70.基于上述时延响应同步机制虽然能够实现同步,但由于时钟信息穿越第三方或不支持逐点恢复,因而apts在1588透传报文的网络场景具有一定的局限性。又由于中间网络存在交换设备、业务流的动态调度、时延等因素,会引入链路噪声,使得信息包经过中间网络到达路由器等网络设备(client)的时间发生变化,产生pdv,导致acr和/或atr的同步跟踪性能变差。

71.对此,本技术实施例提供了一种同步方法,该方法通过预测出未来时间到达网络

设备可能出现的时延预测值,以该时延预测值来补偿中间网络链路引入的pdv噪声,使补偿后的时间戳差值更加直接的反映晶振相对于频率基准源的频偏和相偏信息。由于补偿了中间网络的部分pdv噪声,在使用锁相环实现同步的情况下,能够使得输入锁相环的输入信号中的pdv噪声减小,从而使同步的精度更高,有效地提高acr和/或atr同步性能。

72.其中,锁相环是指一种电路或者模块,它用于在网络设备的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

73.示例性地,锁相环通常由鉴相器(phase detector,pd)、滤波器(loop filter,lf)和压控振荡器(voltage controlled oscillator,vco)3部分组成前向通路,由分频器组成频率相位的反馈通路。锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路将振荡器输出信号的频率、相位反馈到鉴相器。锁相环在工作过程中,当输出信号的频率成比例地反映输入信号的频率时,输出电压与输入电压保持固定的相位差值,这样输出电压与输入电压的相位就被锁住了。

74.如上所述,鉴相器用来鉴别输入信号与输出信号之间的相位差,并输出误差电压。误差电压中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(vco)的控制电压。该控制电压作用于压控振荡器的结果是将它的输出振荡频率拉向环路输入信号频率,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器提供,因此,鉴相器的两个输入信号间留有一定的相位差。

75.实现同步时,除了上述鉴相器、环路滤波器等,还会使用一种全数字化的频率合成器,如直接数字式频率合成器(direct digital synthesizer,dds)。dds由相位累加器、波形rom、d和/或a转换器和低通滤波器构成。时钟频率给定后,输出信号的频率取决于频率控制器,频率分辨率取决于累加器位数,相位分辨率取决于rom的地址线位数,幅度量化噪声取决于rom的数据位字长和d和/或a转换器位数。

76.在示例性实施例中,本技术实施例提供的方法可应用于图2所示的apts应用场景。如图2所示,在apts应用场景中,基准定时参考时钟(primary reference time clock,prtc)作为信息包的源端提供时间参考信息。电信级主时钟(telecom grandmaster,t-gm)作为主时钟设备,对信息包打上时间戳t1,该t1经t-gm和pts网络到达从时钟设备也即电信级从时钟(telecom time slave clock-assisted,t-tsc-a),其中,a表示其具有本地时间参考源作辅助同步。以1588sync报文传输路径为例,主时钟设备的时间戳t1到达从时钟设备t-tsc-a时,由从时钟设备的rtc计数器记录t1到达时刻作为时间戳t2。之后,基于选包算法对(t2-t1)的时间戳差值进行选包滤波。同理,若采用atr进行时间同步,从时钟设备将依次获得t1、t2、t3和t4等时间戳,并基于选包算法对(t2-t1)、(t4-t3)的时间戳差值进行选包滤波。

77.在示例性实施例中,本技术实施例提供的方法还可应用于图3所示的pts应用场景。如图3所示,在pts应用场景中,prtc作为信息包的源端提供时间参考信息。t-gm作为主

时钟设备,对信息包打上时间戳t1。该t1经t-gm和pts网络到达从时钟设备也即电信级从时钟(telecom time slave clock

–

partial support,t-tsc-p),其中,p表示其存在于局部支持时间同步(pts)网络。由于在pts应用场景中,从端t-tsc-p不具备直接从gnss获取时间信息的能力。因此,1588透传报文为pts应用场景中时钟和/或时间同步的主要方式。若要对pts中间网络中的pdv抓取和测试,可先令主时钟设备与从时钟设备同步于相同的时间参考源。

78.本技术实施例提供了一种同步方法,该方法包括但不限应用于图2或图3所示的应用场景中。以网络设备来执行该方法为例,该网络设备可以是主时钟设备,也可以是从时钟设备,本技术实施例对此不进行限定。如图4所示,本技术实施例提供的同步方法可包括如下几个过程。

79.401,获取信息包在目标链路的第一时间戳差值,该第一时间戳差值为第一时刻信息包的发送时间戳与接收时间戳之间的差值。

80.在本技术实施例提供的方法中,信息包在目标链路上进行传输,该第一时间戳差值可以是第一时刻,信息包到达网络设备的时间戳与发送该信息包的时间戳之间的差值,也即该信息包的发送时间戳与接收时间戳之间的差值。信息包包括但不限于1588报文,还可以携带除1588报文外的其他数据,本技术实施例不对信息包的内容进行限定。

81.如图1所示,以网络设备为从时钟设备为例,该网络设备不仅能够获取到主时钟设备记录的发送时间戳t1,还可以在报文到达时记录下到达时间戳t2,则第一时间戳差值=(t2-t1)或(t1-t2)。示例性地,又由于该网络设备除了获取到t1和t2外,还可以获取到t3和t4,因而第一时间戳差值还可以为(t4-t3)或(t3-t4)。

82.402,基于第一时间戳差值进行选包,得到第二时间戳差值。

83.无论该第一时间戳差值是(t2-t1)或(t1-t2),还是(t4-t3)或(t3-t4),得到第一时间戳差值之后,均可利用选包算法对该第一时间戳差值进行选包,以得到第二时间戳差值。

84.关于采用的选包算法,本技术实施例不进行限定。可以对一段观测时间内的多个第一时间戳差值取平均值,将平均值作为第二时间戳差值,相应地,任一第一时间戳差值对应的时刻均可以视为该第二时间戳差值对应的第一时刻。也可以对第一时间戳差值进行筛选,例如,可以基于g.8261标准的附录中提到的用包选择的方法减小pdv。该方法假设在一段观察时间内,pdv在一个时延基准上缓慢变化。这个时延基准可以是信息包在这条网络路径也即目标链路上传输的最小时延。则在正常情况下,即无特别大的负载拥塞情况下,pdv会有较大概率出现在时延基准附近。因此,当前acr和/或atr的主流选包算法是选出一段观测时间内的最小时间戳差值,将该最小时间戳差值作为第二时间戳差值,相应地,该最小时间戳差值对应的时刻即可视为该第二时间戳差值对应的第一时刻。

85.虽然采用选包算法进行选包也能够对链路噪声有抑制作用,例如可以滤除滤波器带宽以外的高频噪声。但由于pdv与网络流量变化强相关,因而仅采用选包算法对链路噪声的抑制比较有限。例如,当网络流量存在极低频的周期变化时,pdv也呈现着极低频的缓变,无法被滤波器滤除。此外,网络调度机制可能会使pdv以一定概率出现异常下坠点,无法被选包算法排除,使得时钟和/或时间同步性能较差。甚至在某些pdv变化较大的场景下,采用选包算法的时钟和/或时间同步性能无法满足标准要求,导致应用范围也比较局限。

86.因此,本技术实施例提供的方法除了采用选包的方式,还提供了pdv补偿,以进一步降低链路噪声,详见后续步骤。

87.403,获取目标链路在第一时刻的时延预测值。

88.在示例性实施例中,获取目标链路在第一时刻的时延预测值,包括:根据目标链路的时延相关数据预测目标链路在第一时刻的时延预测值,其中,时延相关数据包括如下数据中的至少一种:

89.目标链路在第二时刻的时延预测值或时间戳差值,第二时刻早于第一时刻;

90.目标链路在第一时刻的与时延相关的网络参数数据。

91.在示例性实施例中,获取目标链路在第一时刻的时延预测值,包括:获取目标链路在第一周期内的时延预测值序列,时延预测值序列中包括目标链路在第一时刻的时延预测值。

92.在示例性实施例中,获取目标链路在第一周期内的时延预测值序列,包括:根据目标链路在第二周期内的时延预测值序列或时间戳差值序列预测目标链路在第一周期内的时延预测值序列,第二周期是第一周期的前一周期。

93.在示例性实施例中,获取目标链路在第一时刻的时延预测值,包括但不限于通过预测模型对目标链路的时延进行预测,得到目标链路在第一时刻的时延预测值。例如,可基于机器学习训练预测模型,从而基于该预测模型来预测目标链路在第一时刻的时延预测值。

94.示例性地,通过预测模型对目标链路的时延进行预测之前,还包括:基于目标链路获取用于训练预测模型的时延相关数据;通过时延相关数据进行模型训练,得到预测模型。在本技术实施例提供的方法中,通过机器学习算法训练目标链路的预测模型,基于机器学习训练得到的预测模型进行时延预测的过程分为两个阶段:学习阶段(或训练阶段)和预测阶段。接下来,对这两个阶段分别进行举例说明。

95.阶段一,学习阶段(或训练阶段):通过机器学习算法训练目标链路的预测模型。

96.学习阶段可以是离线学习,或者在线学习。在示例性实施例中,基于目标链路获取用于训练预测模型的时延相关数据,包括:以离线方式获取时延相关数据,或者以在线方式获取时延相关数据,该时延相关数据包括目标链路的时间戳差值序列以及与时延相关的网络参数数据中的至少一种数据。其中,与时延相关的网络参数数据包括但不限于目标网络节点的数量、目标网络节点通过目标链路传输的流量以及添加时间戳时对应的时间中的至少一种,目标网络节点包括信息包的发送设备和接收设备,以及发送设备和接收设备之间的网络设备。

97.以离线学习为例:可提前获取目标链路中的时间戳差值序列(也即pdv样本数据),和/或与时延相关的网络参数数据,该与时延相关的网络参数数据包括但不限于目标网络节点的数量,目标网络节点通过目标链路传输的流量以及打时间戳时对应的时间(年/月/日/时/分/秒)等。由于网络流量受网络设备用户习惯影响,一般在某个特定周期内(如1天)会呈现一定规律的涨落。可将此规律作为时延的主要特征进行学习。

98.通过时延相关数据进行模型训练,得到预测模型,包括但不限于如下几种方式:

99.方式一:在进行模型训练的过程中,将目标链路在第三周期内的时间戳差值序列作为样本,并将目标链路在第四周期内的时间戳差值序列作为标签,其中,第三周期为第四

周期的前一周期。

100.以第四周期为当前周期为例,则在当前周期通过时延相关数据进行模型训练,得到预测模型时,输入数据为当前周期的前一周期(也即第三周期)的时延序列,如t-n,t-n+1,

…

,t-2,t-1时刻的时延,则由t-n,t-n+1,

…

,t-2,t-1时刻的时延学习t,t+1,t+2,

…

,t+k时刻的时延。也即根据前一周期的时延序列学习当前周期的时延序列。其中,n>=1,k>=0。

101.方式二:在进行模型训练的过程中,将目标链路在目标时刻的与时延相关的网络参数作为样本,并将目标链路在目标时刻的时间戳差值作为标签。

102.在示例性实施例中,以目标时刻为t时刻为例,若与时延相关的网络参数数据能获取,那么输入数据也可以为t时刻与时延相关的网络参数数据,通过t时刻与时延相关的网络参数数据来学习t时刻的时延。目标时刻也可以为当前时刻,即根据当前时刻的与时延有关的网络参数数据来学习当前时刻的时延。

103.方式三:在进行模型训练的过程中,将目标链路在第三周期内的时间戳差值序列、以及目标链路在目标时刻的与时延相关的网络参数作为样本,并将目标链路在目标时刻的时间戳差值作为标签,其中,目标时刻为第三周期的下一时刻。

104.该方式三中,同时基于时间戳差值序列和与时延相关的网络参数数据分别来进行学习,以得到该目标链路的预测模型。

105.以在线学习为例:由于是在线学习,需要在时间同步的情况下进行学习。因此,以在线方式获取时延相关数据之前,还包括:获取跟踪基准源得到的时间信息,鉴别该时间信息的相位差,得到相位差鉴别结果;将相位差鉴别结果进行环路滤波,得到第一环路滤波结果;对第一环路滤波结果进行直接数字式频率合成,得到第一频率和/或相位调整值;基于第一频率和/或相位调整值进行时间和/或时钟同步。例如,网络设备跟踪全球导航卫星系统(global navigation satellite system,gnss)或其他频率基准源的时钟时间信息,获取到时间信息,以此得到参考时间信息。

106.之后,可以实时获取网络链路中的时间戳差值序列,以及与时延相关的网络参数数据,该与时延相关的网络参数数据包括但不限于目标网络节点的数量,目标网络节点通过目标链路传输的流量,打时间戳时对应的时间(年/月/日/时/分/秒)等。以时延相关数据为时间戳差值序列为例,输入数据可以为纯时间戳差值序列,由t-n,t-n+1,

…

,t-2,t-1时刻的时延学习t,t+1,t+2,

…

,t+k时刻的时延,可参考上述方式一。其中,n>=1,k>=0。若与时延相关的网络参数数据能获取,那么输入数据也可以为t时刻与时延相关的网络参数数据,来学习t时刻的时延,可参考上述方式二。或者,还可以同时基于时间戳差值序列和与时延相关的网络参数数据来进行学习,以得到该目标链路的预测模型,可参考上述方式三。

107.需要说明的是,无论采用上述离线学习的方式,还是采用上述在线学习的方式,本技术实施例不对获取的预测模型的种类进行限定,能够实现时延预测的机器学习模型都可以作为本技术实施例中的初预测模型。

108.阶段二,预测阶段:基于目标链路的预测模型对目标链路的时延进行预测,得到目标链路在第一时刻的时延预测值。

109.由于阶段一已经训练得到了目标链路的预测模型,因而当网络设备需要用时间戳信息与频率基准源进行时钟和/或时间同步时,向学习阶段训练好的机器学习模型即目标链路的预测模型中输入该目标链路在预测阶段的时延相关数据,即可输出目标链路的时延

locked loop,pll)电路中的重要组成部分,参见上述对锁相环的介绍。在本技术实施例中,环路滤波器可以是具有以下两种作用的低通滤波器:一种是在鉴相器的输出端衰减高频误差分量,以提高抗干扰性能;一种是在环路跳出锁定状态时,提高环路以短期存储,并迅速恢复信号。环路滤波器一般是线性电路,由线性元件电阻,电容及运算放大器组成。环路滤波器用于衰减由输入信号噪声引起的快速变化的相位误差和平滑相位检测器泄露的高频分量,即滤波,以便在其输出端对原始信号进行精确的估计,环路滤波的阶数和噪声带宽决定了环路滤波器对信号的动态响应。

122.本技术实施例提供的方法,通过获取目标链路的时延预测值,基于该时延预测值对选包得到的第二时间戳差值进行补偿,也即是对目标链路引入的pdv噪声进行补偿,减少了pdv噪声,使得到的补偿后的时间戳差值更加直接地反映晶振相对于频率基准源的频偏和相偏信息,从而基于该补偿后的时间戳差值进行时间和/或时钟同步之后,同步的精度更高,提高了同步性能。

123.为了便于对本技术实施例提供的方法进行理解,接下来分别以不同应用场景为例,对本技术实施例提供的方法进行举例说明。

124.应用场景一:apts应用场景。

125.仍以图2所示的apts应用场景为例,图2中,prtc作为信息包的源端提供时间参考信息。t-gm作为主时钟设备,对信息包打上时间戳t1,该t1经t-gm和pts网络到达从时钟设备t-tsc-a。以1588sync报文传输路径上,执行本技术实施例提供的方法的网络设备为从时钟设备t-tsc-a为例进行说明。由于主时钟设备的时间戳t1到达从时钟设备t-tsc-a时,由从时钟设备的实时时钟(real time clock,rtc)计数器记录t1到达时刻作为时间戳t2。之后,基于选包算法对(t2-t1)的时间戳差值进行选包滤波。同理,若采用atr进行时间同步,从时钟设备将依次获得t1、t2、t3和t4等时间戳,并基于选包算法对(t2-t1)、(t4-t3)的时间戳差值进行选包滤波。以该apts应用场景下采用在线学习的方式获取预测模型为例,图5为时延在线学习阶段示意图,图6为时延预测阶段示意图。

126.如图5所示的时延在线学习阶段的实施过程,环路跟踪gnss的时钟时间信息,该gnss的时间信息依次经过鉴相器、环路滤波器、dds,生成相位调整值,使网络设备与gnss时间同步,此时1588acr或atr环路处于开环状态。若网络控制引擎(networkcontrolengine,nce)上的网络参数数据不可获取,那么将时延经过选包(降噪预处理)后送入学习模块也即初始机器学习模型进行学习。若nce上的与时延相关的网络参数数据可获取,那么将与时延相关的网络参数数据送入学习模块进行学习,得到预测模型。其中,nce用于存储网络参数数据。

127.如图6所示的时延预测阶段的实施过程,当gnss丢失时,原来gnss跟踪环路立即断开,并切换到1588acr或atr环路上。此时获取的(t2-t1)或(t4-t3)包含了链路时延噪声和晶振噪声。利用已经训练完成的预测模型,输出链路上的时延预测值,并将该时延预测值补偿到选包输出的(t2-t1)或(t4-t3)上,得到补偿后的时间戳差值。之后,将补偿后的时间戳差值送入环路滤波器进行滤波,滤波结果输入dds进行直接数字式频率合成,产生频率和/或相位调整值。基于该频率和/或相位调整值进行时间和/或时钟同步,使得主时钟设备与从时钟设备的时钟和/或时间同步。

128.综上所述的过程可以看出,由于时间戳差值中的pdv噪声被部分补偿,那么时间戳

差值更多地反映了晶振本身的噪声,从而提高了acr和/或atr的同步精度,以进一步提高同步性能。

129.应用场景二:pts应用场景。

130.仍以图3所示的pts应用场景为例,图3中,prtc作为信息包的源端提供时间参考信息。t-gm作为主时钟设备,对信息包打上时间戳t1。该t1经t-gm和pts网络到达从时钟设备t-tsc-p。由于在pts应用场景中,从端t-tsc-p不具备直接从gnss获取时间信息的能力。因此,1588透传报文为pts应用场景中时钟和/或时间同步的主要方式。以执行本技术实施例提供的方法的网络设备为从时钟设备t-tsc-a为例进行说明,如果要对pts中间网络中的pdv抓取和测试,需要令主时钟设备与从时钟设备同步于相同的时间参考源。以该pts应用场景下采用离线学习的方式获取预测模型为例,图7为时延离线学习阶段示意图,图8为时延预测阶段示意图。其中,图7和图8中的r代表时间或频率参考(time or frequency reference),pt代表数据包时间戳(packet timestamper)。

131.如图7所示的时延离线学习阶段的实施过程,从时钟源设备获得(t2-t1)或(t4-t3)的时间戳差值。由于主时钟源设备和从时钟源设备已经与时间参考源同步,此时的时间戳差值的变化量基本等价于pdv。若nce上的网络参数数据不可获取,那么将时延经过选包(降噪预处理)后送入学习模块进行学习。若nce上的与时延相关的网络参数数据可获取,那么将与时延相关的网络参数数据送入学习模块进行学习,得到预测模型。

132.如图8所示的时延预测阶段的实施过程,从时钟源设备通过acr和/或atr的方式跟踪源端时钟,此时从时钟源设备获得的(t2-t1)或(t4-t3)包含了链路时延噪声和晶振噪声。利用已经训练完成的预测模型,输出链路的时延预测值,并将该时延预测值补偿到选包输出的(t2-t1)或(t4-t3)上,得到补偿后的时间戳差值。之后,将补偿后的时间戳差值依次送入环路滤波器,dds,产生频率和/或相位调整值。基于该频率和/或相位调整值进行时间和/或时钟同步,使得从时钟源设备与主时钟源设备的时钟和/或时间同步。

133.综上的过程可以看出,由于时间戳差值中的pdv噪声被部分补偿,那么时间戳差值更多地反映了晶振本身的噪声,从而提高acr和/或atr的同步精度,以进一步提高同步性能。

134.本技术实施例提供了一种同步装置,该装置可通过如下模块实现上述图4所示的同步方法。

135.参见图9,该装置包括:

136.获取模块901,用于获取信息包在目标链路的第一时间戳差值,第一时间戳差值为第一时刻信息包的发送时间戳与接收时间戳之间的差值。例如,该获取模块901可执行上述图4所示的401中的功能,详见上述401的相关描述,此处不再赘述。

137.选包模块902,用于基于第一时间戳差值进行选包,得到第二时间戳差值。例如,该选包模块902可执行上述图4所示的402中的功能,详见上述402的相关描述,此处不再赘述。

138.补偿模块903,用于获取目标链路在第一时刻的时延预测值,基于时延预测值对第二时间戳差值进行补偿,得到补偿后的时间戳差值。例如,该补偿模块903可执行上述图4所示的403和404中的功能,详见上述403和404的相关描述,此处不再赘述。

139.同步模块904,用于基于补偿后的时间戳差值进行时间和/或时钟同步。例如,该同步模块904可执行上述图4所示的405中的功能,详见上述405的相关描述,此处不再赘述。

140.在示例性实施例中,获取模块901,用于根据目标链路的时延相关数据预测目标链路在第一时刻的时延预测值,其中,时延相关数据包括如下数据中的至少一种:

141.目标链路在第二时刻的时延预测值或时间戳差值,第二时刻早于第一时刻;

142.目标链路在第一时刻的与时延相关的网络参数数据。

143.在示例性实施例中,获取模块901,用于获取目标链路在第一周期内的时延预测值序列,时延预测值序列中包括目标链路在第一时刻的时延预测值。

144.在示例性实施例中,获取模块901,用于根据目标链路在第二周期内的时延预测值序列或时间戳差值序列预测目标链路在第一周期内的时延预测值序列,第二周期是第一周期的前一周期。

145.在示例性实施例中,获取模块901,用于通过预测模型对目标链路的时延进行预测,得到目标链路在第一时刻的时延预测值。

146.在示例性实施例中,该装置,还包括:

147.训练模块905,用于基于目标链路获取用于训练预测模型的时延相关数据;通过时延相关数据进行模型训练,得到预测模型。

148.在示例性实施例中,所述时延相关数据包括目标链路的时间戳差值序列以及与时延相关的网络参数数据中的至少一种数据。

149.在示例性实施例中,与时延相关的网络参数数据包括目标网络节点的数量、目标网络节点通过目标链路传输的流量以及添加时间戳时对应的时间中的至少一种,目标网络节点包括信息包的发送设备和接收设备,以及发送设备和接收设备之间的网络设备。

150.在示例性实施例中,训练模块905,用于:

151.在进行模型训练的过程中,将目标链路在第三周期内的时间戳差值序列作为样本,并将目标链路在第四周期内的时间戳差值序列作为标签,其中,第三周期为第四周期的前一周期;或者,

152.在进行模型训练的过程中,将目标链路在目标时刻的与时延相关的网络参数作为样本,并将目标链路在目标时刻的时间戳差值作为标签;或者,

153.在进行模型训练的过程中,将目标链路在第三周期内的时间戳差值序列、以及目标链路在目标时刻的与时延相关的网络参数作为样本,并将目标链路在目标时刻的时间戳差值作为标签,其中,目标时刻为第三周期的下一时刻。

154.在示例性实施例中,同步模块904,用于对补偿之后的时间戳差值进行环路滤波,得到第二环路滤波结果;对第二环路滤波结果进行直接数字频率合成,得到第二频率和/或相位调整值;基于第二频率和/或相位调整值进行时间和/或时钟同步。

155.在示例性实施例中,同步模块904,还用于获取跟踪基准源得到的时间信息,鉴别时间信息的相位差,得到相位差鉴别结果;将相位差鉴别结果进行环路滤波,得到第一环路滤波结果;对第一环路滤波结果进行直接数字式频率合成,得到第一频率和/或相位调整值;基于第一频率和/或相位调整值进行时间和/或时钟同步。

156.本技术实施例提供的装置,通过获取目标链路的时延预测值,基于该时延预测值对选包得到的第二时间戳差值进行补偿,也即是对目标链路引入的pdv噪声进行补偿,减少了pdv噪声,使得到的补偿后的时间戳差值更加直接地反映晶振相对于频率基准源的频偏和相偏信息,从而基于该补偿后的时间戳差值进行时间和/或时钟同步之后,同步的精度更

高,提高了同步性能。

157.应理解的是,上述图9或图10提供的装置在实现其功能时,仅以上述各功能模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能模块完成,即将设备的内部结构划分成不同的功能模块,以完成以上描述的全部或者部分功能。另外,上述实施例提供的装置与方法实施例属于同一构思,其具体实现过程详见方法实施例,这里不再赘述。

158.图11为本技术实施例的同步设备1100的硬件结构示意图。图11所示的同步设备1100可以执行上述实施例的方法中网络设备执行的相应步骤。

159.如图11所示,同步设备1100包括处理器1101、存储器1102、接口1103和总线1104。其中接口1103可以通过无线或有线的方式实现,具体来讲可以是网卡。上述处理器1101、存储器1102和接口1103通过总线1104连接。

160.接口1103可以包括发送器和接收器,用于同步设备1100接收和发送信息包。处理器1101用于执行上述图3所示实施例中301-305的处理相关步骤。处理器1101和和/或或用于本文所描述的技术的其他过程。存储器1102包括操作系统11021和应用程序11022,用于存储程序、代码或指令,当处理器或硬件设备执行这些程序、代码或指令时可以完成方法实施例中涉及同步设备1100的处理过程。可选的,存储器1102可以包括只读存储器(英文:read-only memory,缩写:rom)和随机存取存储器(英文:random access memory,缩写:ram)。其中,rom包括基本输入和/或输出系统(英文:basic input和/或output system,缩写:bios)或嵌入式系统;ram包括应用程序和操作系统。当需要运行同步设备1100时,通过固化在rom中的bios或者嵌入式系统中的bootloader引导系统进行启动,引导同步设备1100进入正常运行状态。在同步设备1100进入正常运行状态后,运行在ram中的应用程序和操作系统,从而,完成方法实施例中涉及同步设备1100的处理过程。

161.可以理解的是,图11仅仅示出了同步设备1100的简化设计。在实际应用中,同步设备1100可以包含任意数量的接口,处理器或者存储器。

162.应理解的是,上述处理器可以是中央处理器(central processing unit,cpu),还可以是其他通用处理器、数字信号处理器(digital signal processing,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field-programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者是任何常规的处理器等。值得说明的是,处理器可以是支持进阶精简指令集机器(advanced risc machines,arm)架构的处理器。

163.进一步地,在一种可选的实施例中,上述存储器可以包括只读存储器和随机存取存储器,并向处理器提供指令和数据。存储器还可以包括非易失性随机存取存储器。例如,存储器还可以存储设备类型的信息。

164.该存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,rom)、可编程只读存储器(programmable rom,prom)、可擦除可编程只读存储器(erasable prom,eprom)、电可擦除可编程只读存储器(electrically eprom,eeprom)或闪存。易失性存储器可以是随机存取存储器(random access memory,ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用。例如,静态随机存取存储器(static ram,sram)、动态随机

存取存储器(dynamic random access memory,dram)、同步动态随机存取存储器(synchronous dram,sdram)、双倍数据速率同步动态随机存取存储器(double data date sdram,ddr sdram)、增强型同步动态随机存取存储器(enhanced sdram,esdram)、同步连接动态随机存取存储器(synchlink dram,sldram)和直接内存总线随机存取存储器(direct rambus ram,dr ram)。

165.还提供了一种计算机可读存储介质,存储介质中存储有至少一条指令,指令由处理器加载并执行以实现如上任一所述的同步方法。

166.本技术提供了一种计算机程序,当计算机程序被计算机执行时,可以使得处理器或计算机执行上述方法实施例中对应的各个步骤和和/或或流程。

167.提供了一种芯片,包括处理器,用于从存储器中调用并运行所述存储器中存储的指令,使得安装有所述芯片的通信设备执行上述各方面中的方法。

168.提供另一种芯片,包括:输入接口、输出接口、处理器和存储器,所述输入接口、输出接口、所述处理器以及所述存储器之间通过内部连接通路相连,所述处理器用于执行所述存储器中的代码,当所述代码被执行时,所述处理器用于执行上述各方面中的方法。

169.在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本技术所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线)或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,dvd)、或者半导体介质(例如固态硬盘solid state disk)等。

170.以上所述的具体实施方式,对本技术的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本技术的具体实施方式而已,并不用于限定本技术的保护范围,凡在本技术的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1