一种复杂系统智能授时管理方法与流程

:

1.本发明涉及但不限于嵌入式计算机信号处理技术领域,尤指一种复杂系统智能授时管理方法。

背景技术:

:

2.在包含多个不同功能设备的复杂训练系统中,保证各个设备在同一时钟基准下工作至关重要。对于高精度的复杂训练系统,要保证系统运行过程中个设备协同合作的精准性和有效性,以及事后评估分析的真实性,系统内各个设备必须保证时钟同步,必须采用统一的时统源对系统内各设备进行授时。

3.时统的来源有两种方式,一种是采用专门的外部时统基准源设备,另外一种是直接接收卫星导航信号获取卫星时间作为时统源。由于外部时统基准源设备的授时精度更高,通常优先选用外部时统基准源设备作为授时源。然而,外部时统基准源设备可能由于各种原因发生故障,卫星信号可能受到各种外部因素的干扰而失效,如何在卫星信号受到干扰或者外部时统源故障时对复杂训练系统进行精确授时及守时,对于高精度的复杂训练系统具有十分重要意义。

技术实现要素:

:

4.本发明的目的是:本发明实施例提供一种复杂系统智能授时管理方法,以解决由于卫星信号受到干扰或者外部时统源故障时,复杂系统的高精确授时及守时问题。

5.本发明的技术方案是:本发明实施例提供一种复杂系统智能授时管理方法,包括:

6.步骤1,通过2路rs422接口分别接收外部时统源的时码信息和秒脉冲信号作为外部授时信号,通过另1路rs422接口接收内部时统源的信号并将解析获取的时码信息及秒脉冲信号作为内部授时信号;

7.步骤2,外部时统源发送的外部授时信号及内部时统源发送的内部授时信号传输到fpga中进行有效性判定,得到时统源有效性判定结果;

8.其中,初始状态下fpga内部的时统源变量为无效状态(即有效性状态值为0,指:外部和内部时统源均无效);所述fpga执行有效性判定,包括:

9.步骤21,依据fpga的时钟频率进行秒计数以判断外部/内部时统源的有效状态;

10.步骤22,在外部时统源为有效状态时,置时统源变量为有效状态,将外部时统作为授时源,在外部时统源为无效状态时,依据fpga的时钟频率进行秒计数以判断内部时统源的有效状态;

11.步骤23,在内部时统源为有效状态时,置时统源变量为有效状态,将内部时统作为授时源,在内部时统源为无效状态时,将fpga内部配置的rtc时钟模块作为授时源。

12.可选地,如上所述的复杂系统智能授时管理方法中,所述判断外部/内部时统源的有效状态的方式,包括:

13.依据fpga的时钟频率进行秒计数,并检测外部/内部时统源中相邻两个秒脉冲信

号上升沿之间的时间间隔,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差小于1ms,判断出外部/内部时统源为有效状态,且置时统源变量的有效性状态为1。

14.可选地,如上所述的复杂系统智能授时管理方法中,所述fpga执行有效性判定,还包括:

15.在时统源变量为有效状态时,周期性的依据fpga的时钟频率进行秒计数以判断当前作为授时源的时统源的有效状态。

16.可选地,如上所述的复杂系统智能授时管理方法中,所述判断当前作为授时源的时统源的有效状态的方式,包括:

17.在时统源变量为有效状态时,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差大于1ms,或者,由于无法检测到秒脉冲的上升沿跳变而使得fpga的秒计数值大于1.5s,判断出当前作为授时源的时统源变为无效状态,且置时统源变量的有效性状态为0。

18.可选地,如上所述的复杂系统智能授时管理方法中,还包括:

19.步骤3,根据步骤2得到的时统有效性判定结果进行时统输出选通控制,从而对外部n个外部设备进行授时。

20.可选地,如上所述的复杂系统智能授时管理方法中,包括:

21.在所述步骤2中判定出外部时统源有效时,则不进行内部时统源的有效性判定,将外部时统作为授时源,将外部时统源的时码信息和秒脉冲信号分别输出给n个外部设备;

22.在所述步骤2中判定出外部时统源无效时,且内部时统源有效,则将内部时统源作为授时源,将内部时统源的时码信息和秒脉冲信号分别输出给n个外部设备;

23.在所述步骤2中判定出外部时统源和内部时统源均无效时,则将fgpa内部配置的rtc时钟模块作为授时源,将rtc时钟模块的时码信息和秒脉冲信号分别输出给n个外部设备。

24.可选地,如上所述的复杂系统智能授时管理方法中,在确定授时源之后,还包括:

25.步骤4,将授时源中的时码信息经过解析后得到年、月、日、时、分及秒信息,通过授时源中的秒脉冲信号及rtc时钟模块的秒内计数方式生成微秒信息,从而形成高精度时间戳信息。

26.可选地,如上所述的复杂系统智能授时管理方法中,

27.所述rtc时钟模块的秒内计数方式,包括:设置时、分、秒及微秒寄存器,依据fpga系统时钟进行秒内计数,在每个fpga系统时钟上升沿通过d触发器将秒内计数值加1并更新到微秒寄存器,授时源有效时在下一个秒脉冲信号到来时进行秒进位,授时源无效时秒内计数值达到整秒后进行秒进位,进位后秒内计数值清零并重新开始计数。

28.可选地,如上所述的复杂系统智能授时管理方法中,所述rtc时钟模块中配置有校时状态寄存器和时、分、秒配置寄存器,在初始状态或时统源状态发生变化时,rtc时钟模块的时、分、秒配置寄存器的值通过外部时统源或者内部时统源进行时间校准。

29.可选地,如上所述的复杂系统智能授时管理方法中,所述时间校准方法包括:

30.在校时状态寄存器为0情况下,当检测到外部时统源无效而内部时统源有效时,通过fpga读取驱动解析出年、月、日、时、分、秒信息,将解析出的时、分、秒信息写入rtc时钟模

块的时、分、秒配置寄存器,并置校时状态寄存器值为1;

31.在校时状态寄存器为1情况下,当检测到内部时统源和外部时统源从两个均无效状态变为其中一个有效状态,或者,当检测到内部时统源和外部时统源的有效状态发生切换时,置校时状态寄存器值为0,从而在下一个时钟周期触发重新校时。

32.本发明具有的优点是:本发明实施例提供一种复杂系统智能授时管理方法,通过将从外部时统源和内部时统源分别接收的信号送入到fpga进行有效性判定,并基于时统有效性判定结果进行时统输出选通控制,即选择性的将外部时统源、内部时统源或rtc时钟模块作为授时源,并对授时源的时码信息进行解析形成高精度时间戳信息;另外,还可以在初始状态或时统源状态发生变化时,对校时状态进行转换。采用本发明实施例提供的复杂系统智能授时管理方法,能够智能检测多个时统源的有效性,并按照优先级选用时统源,并生成高精度时间戳信息;当卫星信号受到干扰或者外部时统源故障时,能智能进行时统源的切换,并能自主守时。

附图说明:

33.附图用来提供对本发明技术方案的进一步理解,并且构成说明书的一部分,与本申请的实施例一起用于解释本发明的技术方案,并不构成对本发明技术方案的限制。

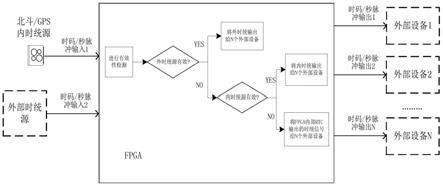

34.图1为本发明实施例提出一种复杂系统智能授时管理方法的实施方式的示意图;

35.图2为本发明实施例中fpga系统中rtc时钟模块执行秒内计数方式的流程图;

36.图3为本发明实施例中rtc时钟模块进行校时状态转换的原理示意图;

37.图4为本发明实施例提供的复杂系统智能授时管理方法的工作原理示意图;

38.图5为用于实现本发明实施例提供的复杂系统智能授时管理方法的功能框图。

具体实施方式:

39.为使本发明的目的、技术方案和优点更加清楚明白,下文中将结合附图对本发明的实施例进行详细说明。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互任意组合。

40.本发明提供以下几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例不再赘述。

41.图1为本发明实施例提出一种复杂系统智能授时管理方法的实施方式的示意图。如图1所示,本发明实施例提出的复杂系统智能授时管理方法包括如下实施步骤:

42.步骤1,通过2路rs422接口分别接收外部时统源的时码信息和秒脉冲信号作为外部授时信号,同时,通过1路rs422接口接收内部时统源的信号并将解析获取时码信息及秒脉冲信息作为内部授时信号,该步,1中,内部时统源信号可以为北斗/gps导航信号;

43.步骤2,基于该复杂系统中的上述外部时统源和内部时统源,该智能授时管理方法中将外部时统源发送的外部授时信号及内部时统源(例如卫星接收芯片)发送的内部授时信号送入到fpga进行有效性判定,并得到时统源有效性判定结果。

44.本发明实施例提供的智能授时管理方法中,上述有效性判定方法如下:初始状态下fpga内部的时统源有效性状态值为0(指:外部和内部时统源无效);fpga执行有效性判定的具体实施过程,可以包括:依据fpga系统时钟频率进行秒计数,并检测外部/内部时统源

中相邻的两个秒脉冲信号上升沿之间的时间间隔,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差小于1ms,则认为外部/内部时统源为有效状态,且置时统源有效性状态为1;当时统源变量为为有效状态时,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差大于1ms,或者,由于无法检测到秒脉冲的上升沿跳变而使得fpga的秒计数值大于1.5s,则判定出当前作为授时源的时统源变为无效状态,此时置时统源有效性状态为0。

45.本发明实施例提供的智能授时管理方法中,在得到时统源的有效性判定结果之后,还可以执行如下步骤:

46.步骤3,依据时统有效性判定结果进行时统输出选通控制,从而实现对外部n个设备授时。实际应用中,本发明实施例中时统输出选通控制的方式包括以下几种情况:

47.情况一:若判定外部时统源有效时,则不管内部时统源的状态,优先将外部时统作为授时源,将外部时统源的时码信息和秒脉冲信号分别输出给n个外部设备;

48.情况二:若判定外部时统源无效时,若内部时统源有效,则将内部时统源作为授时源,将内部时统源的时码信息和秒脉冲信号分别输出给n个外部设备;

49.情况三:若判定外部时统源和内部时统源均无效时,则将fgpa内部配置的rtc时钟模块作为授时源,将rtc时钟模块的时码信息和秒脉冲信号分别输出给n个外部设备。

50.本发明实施例提供的智能授时管理方法,在确定授时源之后,还可以执行如下步骤:

51.步骤4,将授时源中的时码信息经过解析后得到年、月、日、时、分及秒信息,通过授时源中的秒脉冲信号及rtc时钟模块的秒内计数方式生成微秒信息,从而形成高精度时间戳信息。

52.图2为本发明实施例中fpga系统中rtc时钟模块执行秒内计数方式的流程图。如图2所示,实际应用中,rtc时钟模块的秒内计数方式,可以为:设置时、分、秒及微秒寄存器,依据fpga系统时钟进行秒内计数,在每个fpga系统时钟上升沿通过d触发器将秒内计数值加1并更新到微秒寄存器,授时源有效时在下一个秒脉冲信号到来时进行秒进位,授时源无效时计数值达到整秒后进行秒进位,进位后秒内计数值清零并重新开始计数。

53.本发明实施例中rtc时钟模块中配置有校时状态寄存器和时、分、秒配置寄存器,在初始状态或时统源状态发生变化时,rtc时钟模块的时、分、秒配置寄存器的值需要利用外部时统源或者内部时统源进行时间校准,如图3所示,为本发明实施例中rtc时钟模块进行校时状态转换的原理示意图,时间校准方法如下:

54.在校时状态寄存器为0情况下,任意时刻当检测到外部时统源无效而内部时统源有效时,通过fpga读取驱动解析出年、月、日、时、分、秒信息,将解析出的时、分、秒信息写入rtc时钟模块的时、分、秒配置寄存器,同时置校时状态寄存器值为1。

55.在校时状态寄存器为1情况下,任意时刻当检测到内部时统源和外部时统源皆从无效状态变为任意一个有效状态,或者,当检测到内部时统源和外部时统源的发有效状态生切换时,置校时状态寄存器值为0,从而在下一个时钟周期触发重新校时。

56.本发明实施例提供的复杂系统智能授时管理方法,通过将从外部时统源和内部时统源分别接收的信号送入到fpga进行有效性判定,并基于时统有效性判定结果进行时统输出选通控制,即选择性的将外部时统源、内部时统源或rtc时钟模块作为授时源,并对授时

源的时码信息进行解析形成高精度时间戳信息;另外,还可以在初始状态或时统源状态发生变化时,对校时状态进行转换。采用本发明实施例提供的复杂系统智能授时管理方法,能够智能检测多个时统源的有效性,并按照优先级选用时统源,并生成高精度时间戳信息;当卫星信号受到干扰或者外部时统源故障时,能智能进行时统源的切换,并能自主守时。

57.以下通过一个具体实施示例对本发明实施例提供的复杂系统智能授时管理方法的具体实施方式进行详细说明。

58.图4为本发明实施例提供的复杂系统智能授时管理方法的工作原理示意图,图5为用于实现本发明实施例提供的复杂系统智能授时管理方法的功能框图。参考图1到图5所示,本实施示例提供的复杂系统智能授时管理方法已经在某复杂训练系统数据处理设备的授时模块中应用。授时模块由come处理器子卡、授时定位子卡、fpga处理单元及其他功能组件构成;fpga芯片型号例如为altera公司10cl025yu256,系统时钟频率为40mhz。

59.该授时模块通过fpga逻辑和驱动软件合作共同实现智能授时管理方法。fpga完成内部外部时统源切换,串口数据缓存,秒内计数及内部rtc时分秒微秒计时等功能。驱动软件通过对时码解析获取时间信息,进行年月日信息的维护,并通过localbus局部总线完成对fpga内部rtc时分秒信息的校时。

60.该授时模块通过bd/gps卫星接收时码信息和秒脉冲信息,作为内部时统源,同时通过2路rs422总线接收外部时统设备发送过来的时码信息和秒脉冲信息作为外部时统源。fpga处理单元接收外部时统源和内部时统源的信息,将选通时统源信息通过4路rs422接口向外部设备进行授时,并将选通时统源的时码码流传送至come处理器子卡。驱动软件通过对时码解析获取时间信息,通过localbus局部总线完成对fpga内部rtc时分秒信息的校时。fpga内部用秒脉冲对获取的时间报文进行时间对齐、误差计算等后,通过localbus总线以中断的方式提交给come处理器子卡,实现数据包时间戳信息的获取。

61.首先将外部时统源发送的外部授时信号及授时定位子卡发送的内部授时信号进入fpga进行有效性判定,效性判定方法如下:初始状态时统源有效性状态为0;依据fpga系统时钟频率进行秒计数,并检测时统源相邻的两个秒脉冲信号上升沿之间的时间间隔,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差小于1ms,则认为时统源有效,置时统源有效性状态为1;当时统源为有效状态时,若连续3个计数周期秒脉冲信号上升沿之间的时间间隔与秒计数值的误差大于1ms,或者无法检测到秒脉冲的上升沿跳变而fpga的秒计数值大于1.5s,则判定时统源变为无效状态,此时置时统源有效性状态为0。

62.依据时统有效性判定结果进行时统输入选通控制,方法如下:若判定外部时统源有效,则不管内部时统源的状态,优先将外部时统源作为授时源,向外部设备发送时码信息和秒脉冲信息,并对fpga中的rtc时钟进行校时;在外部时统源无效时,若内部时统源有效,则将内部时统源作为授时源,向外部设备发送时码信息和秒脉信息,并对fpga中的rtc时钟进行校时;若内外时统源均无效时,使用在授时模块内配置的rtc时钟进行自主守时,生成时间戳信息。

63.rtc时钟的年、月、日、时、分、秒寄存器值需要用外部时统源或者内部时统源进行校时,校时方法如下:在fpga内设置rtc校时状态寄存器,初始状态寄存器值为0(未校时);在校时状态寄存器为0情况下,任意时刻当检测到外部时统源有效时,通过fpga读取驱动解

析出的年月日时分秒信息,将解析出的时分秒信息写入时、分、秒配置寄存器,同时置校时状态寄存器值为1;在校时状态寄存器为0情况下,任意时刻当检测到外部时统源无效而内部时统源有效时,通过fpga读取驱动解析出的年月日时分秒信息,将解析出的时分秒信息写入时、分、秒配置寄存器,同时置校时状态寄存器值为1;在校时状态寄存器为1情况下,任意时刻当检测到内外时统源皆从无效状态变为任意一个有效或者内外时统有效性发生切换时,置校时状态寄存器值为0,从而在下一个时钟周期触发重新校时。

64.fpga处理单元依据系统时钟进行秒内计数,在每个系统时钟上升沿通过d触发器将秒内计数值加1并更新到微秒寄存器。在内部或者外部时统源有效时,fpga检测到秒脉冲上升沿时,秒内计数值清零,进行秒进位。当外部时统源和内部时统源均无效时,秒内计数值达到整秒后进行秒进位。若当前时分秒寄存器的值为为23时59分59秒,则将跨天状态寄存器置1,并在下一个系统时钟周期恢复为0,产生一个跨天脉冲信号;驱动软件通过中断检测跨天脉冲信号,更新年、月、日信息,并通过localbus局部总线读取时、分、秒及微秒寄存器的值,从而获取精确的时间信息。

65.虽然本发明所揭露的实施方式如上,但所述的内容仅为便于理解本发明而采用的实施方式,并非用以限定本发明。任何本发明所属领域内的技术人员,在不脱离本发明所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本发明的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1