基于空时功率倒置阵的宽带干扰抑制装置及抑制方法

1.本发明涉及信号处理领域技术领域,具体涉及一种基于空时功率倒置阵的宽带干扰抑制装置及抑制方法。

背景技术:

2.无线通信电台广泛应用于野外科考、应急救灾、舰艇飞机通信等军民用领域,具有信号稳定、安全性高等优点,也是保障长距离视距通信的重要设备。然而,在复杂电磁环境下,通信电台易受共平台发射机或敌方干扰机产生的多样式干扰影响,通信鲁棒性较差。特别是在扩频通信体制下,需要对扩频带宽内的宽带干扰信号进行抑制。

3.为解决电台在扩频通信体制下的同频宽带干扰问题,多接收天线技术得到了广泛的应用。由于通信信道通常是衰落的且各向异性,无法采用阵列信号处理中的波束形成技术,而功率倒置算法可利用自适应调零天线接收信号,在强干扰来向形成波束零陷,从而实现空域滤波抑制干扰。功率倒置阵直接将阵列的输出作为误差信号,在保证参考路权系数恒定的前提下,通过自适应算法调整权值路的加权系数,使总的输出功率最小,具有工程实现价值。

4.然而,在实际环境中,信号传播通常具有很强的多径效应,造成信道较强的频率选择性,宽带干扰信号的不同频点对应信道的响应也不同。而目前使用的功率倒置天线阵列在时域上通常只有一个抽头,只能针对单个频点的信道进行干扰抑制,无法覆盖整个宽带信号的带宽,造成传统对消算法性能下降。从方向图角度考虑,基于传统空域功率倒置阵的自适应抗干扰算法只可以在干扰方向形成较深的零陷,进而在空域维度上对干扰进行有效的抑制,但是只能分辨来自不同方向的信号,而无法分辨相同方向不同频率的信号,因此,对多径场景下的宽带干扰,其抑制能力十分有限。

5.中国专利基于波形重构的宽带干扰抑制方法(申请号cn201710277014)、一种盲波束宽带干扰抑制方法及装置(申请号cn201510194436.3)、最低误码率准则的超宽带干扰抑制技术(申请号cn201010510882.8)、一种空频抗干扰方法及装置(申请号cn201611008389.x)等或采用基于时域积累的空时处理手段,或建立非线性模型,利用时域重构完成宽带干扰抑制。均存在算法实时性较差、无法高速流水运行、不利于工程实现等缺点,始终无法克服多径信道下大带宽通信干扰的抑制难题。

技术实现要素:

6.本发明的目的是针对上述技术问题,提供一种具有高速、低延时性能且能够有效抑制宽带干扰的基于空时功率倒置阵的宽带干扰抑制装置及抑制方法。

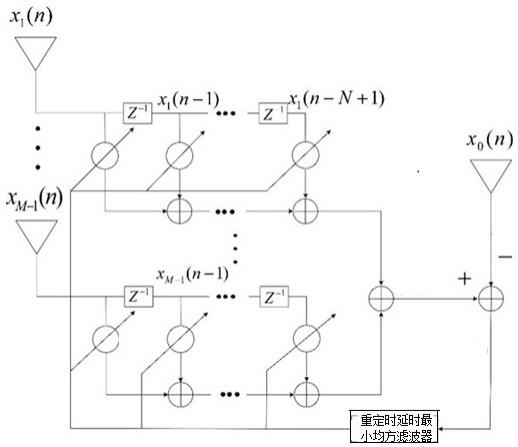

7.为实现上述目的,本发明所设计的基于空时功率倒置阵的宽带干扰抑制装置,包括空时二维功率倒置阵结构及重定时延时最小均方滤波器;所述空时二维功率倒置阵结构由m个阵元组成,设第一个阵元为参考阵元,其他m

‑

1个阵元为权值阵元,每个权值阵元各有n个单位延时器,每个单位延时器都有1个复数权值,使得每个权值阵元构成一个阵元fir滤

波器;重定时延时最小均方滤波器包括m

‑

1组权值处理模块、两个单位延时器、第一加法器、一个单位延时器及第二加法器;两个单位延时器的输入端连接参考阵元接收信号,每个权值处理模块一路输入端一一对应连接权值阵元接收信号、每个权值处理模块另一路输入端一一对应连接一个初始信号,每组权值处理模块一路输出端连接三个单位延时器的输入端、三个单位延时器的输出端连接权值处理模块;所有权值处理模块另一路输出端均连接第二加法器的输入端,第二加法器的输出端和两个单位延时器的输出端均连接第一加法器的输入端,第一加法器的输出端连接一个单位延时器的输入端,一个单位延时器的输入端分别与每个权值处理模块的输入端相连。

8.进一步地,所述参考阵元的权值始终为1,m个阵元的接收信号分别记为x0(n)、x

1 (n)、

……

、x

m

‑1(n),其中,x

0 (n)表示参考阵元接收信号,x1(n) 、

……

、x

m

‑1(n)为权值阵元接收信号,n表示当前时刻;在每个权值阵元后加上n个单位延时器z

‑1,记为x

i (n)、x

i (n

‑

1) 、

……

、x

i (n

‑

n+1),其中,i=0、

……

、m

‑

1,每个单位延时器的复数权值记为w

ij

,i=0、

……

、m

‑

1,j=1、

……

、n,其中i表示阵元序号,j表示延时单元序号。

9.进一步地,每个所述权值阵元接收信号x

i

(n)输送至对应的权值处理模块后经过三个单位延时器形成延时信号x

i

(n

‑

3d)给对应的权值处理模块输出;每个初始信号y

i

(n

‑

1d)输送至对应的权值处理模块后形成延时信号y

i

(n

‑

2d),所有的延时信号y

i

(n

‑

2d)经过第二加法器产生权值合并输出信号y(n

‑

2d),权值合并输出信号y(n

‑

2d)和参考阵元接收信号x0(n)经过第一加法器形成误差信号e(n

‑

2d),误差信号e(n

‑

2d)经过一个单位延时器形成延时误差信号e(n

‑

3d)输送至每个权值处理模块输出。

10.进一步地,每组所述权值处理模块包括四个乘加单元、两个单位延时器、第一加法器及第二加法器,四个乘加单元分别为第一乘加单元、第二乘加单元、第三乘加单元、第四乘加单元;第一乘加单元和第三乘加单元均包括上支路乘法器、下支路乘法器和加法器,上支路乘法器和下支路乘法器的输出端均与加法器的输入端相连;第二乘加单元和第四乘加单元均包括左支路乘法器、右支路乘法器和加法器,左支路乘法器和右支路乘法器的输出端均与加法器的输入端相连。

11.进一步地,每组所述权值处理模块的输入信号为iq信号x

ii

(n)、x

iq

(n),i=1、

……

、m

‑

1,iq信号x

ii

(n)、x

iq

(n)一路经过三个单位延时器形成三个单位延时信号x

ii

(n

‑

3d)、x

iq

(n

‑

3d),三个单位延时信号x

ii

(n

‑

3d)、x

iq

(n

‑

3d)经过两个单位延时器形成五个单位延时信号x

ii

(n

‑

5d)、x

iq

(n

‑

5d)输出;延时信号x

ii

(n

‑

3d)分别连接第一乘加单元的上支路乘法器、第三乘加单元的上支路乘法器,延时信号x

iq

(n

‑

3d)分别连接第一乘加单元的下支路乘法器、第三乘加单元的下支路乘法器,第一乘加单元的加法器输出端依次经过一个单位延时器、上支路移位器、加法器、一个单位延时器与第二乘加单元的左支路乘法器和右支路乘法器输入端均相连,同理,第三乘加单元的加法器输出端依次经过一个单位延时器、下支路移位器、加法器、一个单位延时器与第四乘加单元的左支路乘法器和右支路乘法器输入端均相连;信号x

ii

(n)分别连接第三乘加单元的左支路乘法器和第四乘加单元的左支路乘法器,信号x

iq

(n) 分别连接第三乘加单元的右支路乘法器和第四乘加单元的右支路乘法器;初始信号yii(n

‑

1d)输送至第一加法器的左支路,同时第二乘加单元加法器的输出端经过一个单位延时器输送至第一加法器的右支路,第一加法器左右支路相加后再经过一个单位延时

器形成延时信号yii(n

‑

2d);初始信号yiq(n

‑

1d)输送至第二加法器左支路,同时第四乘加单元加法器的输出端经过一个单位延时器输送至第二加法器右支路,第二加法器左右支路相加后再经过一个单位延时器形成延时信号yiq(n

‑

2d)。

12.进一步地,每组所述权值处理模块的延时信号y

ii

(n

‑

2d)经过第一加法器形成权值合并输出信号y

i

(n

‑

2d),每个权值处理模块的延时信号y

iq

(n

‑

2d)经过第一加法器形成权值合并输出信号y

q

(n

‑

2d)。权值合并输出信号y

i

(n

‑

2d)和参考阵元接收信号x

0i

(n)经过第一加法器形成误差信号e

i

(n

‑

2d),误差信号e

i

(n

‑

2d)经过一个单位延时器形成延时误差信号e

i

(n

‑

3d)输送至每个权值处理模块,延时误差信号e

i

(n

‑

3d)一路分别连接第一乘加单元的上支路乘法器和第三乘加单元的上支持乘法器,延时误差信号e

i

(n

‑

3d)另一路经过权值处理模块中的一个单位延时器形成延时误差信号e

i

(n

‑

4d),延时误差信号e

i

(n

‑

4d)输出;同理,权值合并输出信号y

q

(n

‑

2d)和参考阵元接收信号x

0q

(n)经过第一加法器形成误差信号e

q

(n

‑

2d),误差信号e

q

(n

‑

2d)经过一个单位延时器形成延时误差信号e

q

(n

‑

3d)输送至每个权值处理模块,延时误差信号e

q

(n

‑

3d)一路分别连接第一乘加单元的下支路乘法器和第三乘加单元的下支持乘法器,延时误差信号e

q

(n

‑

3d)另一路经过权值处理模块中的一个单位延时器形成延时误差信号e

q

(n

‑

4d)输出。

13.还提供一种上述所述基于空时功率倒置阵的宽带干扰抑制装置的抑制方法,其特征在于:所述抑制方法如下:s1)初始化空时二维功率倒置阵模型,包括以下子步骤:s11)空时二维功率倒置阵结构由m个阵元组成,设第一个阵元为参考阵元1,其他m

‑

1个阵元为权值阵元,m个阵元的接收信号分别记为x0(n)、x1(n)、

……

、x

m

‑1(n),其中,x0(n)表示参考阵元接收信号,x1(n)、

……

、x

m

‑1(n)为权值阵元接收信号,n表示当前时刻;s12)每个权值阵元各有n个单位延时器,记为x

i

(n)、x

i

(n

‑

1)、

……

、x

i

(n

‑

n+1),其中,i=0、

……

、m

‑

1,每个单位延时器的复数权值记为w

ij

,i=0、

……

、m

‑

1,j=1、

……

、n,其中i表示阵元序号,j表示延时单元序号;s13)初始化参考阵元x0路权值为w

01

=1,w

0j

=0,其中j=2、

……

、n,初始化权值路x1、

……

、x

m

‑1的权值为w

ij

=0,其中i=1、

……

、m

‑

1,j=1、

……

、n记输入信号向量为x(n)=[x1(n)

⋯

x1(n

‑

n+1)

⋯

x

m

‑1(n)

⋯

x

m

‑1(n

‑

n+1)]

t

∈c

(m

‑

1)

×

n

记权向量为w=[w

1,1

w

1,2

⋯

w

1,n

⋯

w

m

‑

1,1

w

m

‑

1,2

⋯

w

m

‑

1,n

]

t

∈c

(m

‑

1)

×

n

初始化当前时刻为n=1;s2)根据多径信道环境计算处理延时量,将参考阵元接收信号进行延时,将x0路信号x0(n)延时2d,得到x0(n

‑

2d),其中2d要大于最大多径传播时延;s3)利用权值处理模块计算输出信号、误差信号以及权向量的更新,具体为:s31)对于n=1,2,3,

……

,利用当前权值w,计算输出信号为y(n)=w

1,1*

x1(n)+w

1,2*

x1(n

‑

1)+

⋯

+w

1,n*

x1(n

‑

n+1)+

⋯

+w

m

‑

1,1*

x

m

‑1(n)+w

m

‑

1,2*

x

m

‑1(n

‑

1)+

⋯

+w

m

‑

1,n*

x

m

‑1(n

‑

n+1)=w

h

x(n)计算期望延时信号为

d(n

‑

2d) =

ꢀ‑

x

0 (n

‑

2d)计算延时误差信号为e(n

‑

2d) = d(n

‑

2d)

‑

y(n

‑

2d)s32)设置步长μ,对于空时二维功率倒置阵,μ由移位器实现,μ为2

‑8~2

‑

12

,并进行权值的更新,权向量更新为:w(n+1) = w(n)+μx(n

‑

2d)e

* (n

‑

2d)s4)令n=n+1,转子步骤s31),直到满足‖w(n+1)

‑

w(n)‖

22

≤ε,其中ε为迭代终止阈值;s5)为实现自适应宽带干扰抑制,对于当前时刻n,输出信号为y ̃

(n)=x0(n)+w

h x(n)。

[0014]

与现有技术相比,本发明具有以下优点:1)有效提高干扰抑制的带宽。在每个天线阵元后加上若干个延迟单元,使得每个阵元后构成一个fir滤波器,从而使得阵列具有一定的频率分辨能力,通过增加fir滤波器阶数,大大提高了功率倒置阵的自由度,从而有效提高了干扰抑制的带宽。

[0015]

2)能够实现多径等复杂信道下的宽带干扰抑制。将时域多抽头的思想引入到空域天线阵列中,综合考虑接收机的工作环境,将时域横向滤波器的总延时时间大于最大的多径传播延时,可实现多径环境下的干扰抑制。

[0016]

3)有效提高干扰抑制速度。相比于传统lms算法,当权系数越多时,系统吞吐能力越低,而本发明提出的tf

‑

rdlms结构,权值是局部更新的,在硬件实现中可采用高度流水的结构,可以通过简单增加权值处理模块来提高空时滤波器的阶数,因此,本发明适合基于fpga的高速低延时硬件实现。

附图说明

[0017]

图1为本发明基于空时功率倒置阵的宽带干扰抑制装置原理图;图2为图1中重定时延时最小均方滤波器原理图;图3为图2中权值处理模块原理图;图4为载频150mhz带宽10mhz宽带干扰信号频谱;图5为传统功率倒置阵干扰抑制效果频谱图;图6为本发明宽带干扰抑制效果频谱图。

具体实施方式

[0018]

下面结合附图和具体实例对本发明作进一步的详细说明。

[0019]

本发明基于空时功率倒置阵的宽带干扰抑制装置,包括空时二维功率倒置阵结构及重定时延时最小均方滤波器(tf

‑

rdlms)。

[0020]

其中,如图1所示空时二维功率倒置阵结构由m个阵元组成,设第一个阵元为参考阵元,其他m

‑

1个阵元为权值阵元,参考阵元的权值始终为1,每个权值阵元各有n个单位延时器,每个单位延时器都有1个复数权值,使得每个权值阵元构成一个阵元fir滤波器。m个阵元的接收信号分别记为x0(n)、x

1 (n)、

……

、x

m

‑1(n),其中,x

0 (n)表示参考阵元接收信号,x1(n) 、

……

、x

m

‑1(n)为权值阵元接收信号,n表示当前时刻;在每个权值阵元后加上n个

单位延时器z

‑1,记为x

i (n)、x

i (n

‑

1) 、

……

、x

i (n

‑

n+1),其中,i=0、

……

、m

‑

1,每个单位延时器的复数权值记为w

ij

,i=0、

……

、m

‑

1,j=1、

……

、n,其中i表示阵元序号,j表示延时单元序号。

[0021]

结合图2所示,重定时延时最小均方滤波器(tf

‑

rdlms)包括m

‑

1组权值处理模块04、两个单位延时器01、第一加法器02、一个单位延时器03及第二加法器06。两个单位延时器01的输入端连接参考阵元接收信号x0(n),每个权值处理模块04一路输入端一一对应连接权值阵元接收信号x

i

(n)、每个权值处理模块04另一路输入端一一对应连接一个初始信号y

i

(n

‑

1d),其中i=1、

……

、m

‑

1,每组权值处理模块04一路输出端连接三个单位延时器05的输入端、三个单位延时器05的输出端连接权值处理模块04;所有权值处理模块04另一路输出端均连接第二加法器06的输入端,第二加法器06的输出端和两个单位延时器01的输出端均连接第一加法器02的输入端,第一加法器02的输出端连接一个单位延时器03的输入端,一个单位延时器03的输入端分别与每个权值处理模块04的输入端相连。每个权值阵元接收信号x

i

(n)输送至对应的权值处理模块04后经过三个单位延时器05形成延时信号x

i

(n

‑

3d)给对应的权值处理模块04输出;每个初始信号y

i

(n

‑

1d)输送至对应的权值处理模块04后形成延时信号y

i

(n

‑

2d),所有的延时信号y

i

(n

‑

2d)经过第二加法器06产生权值合并输出信号y(n

‑

2d),权值合并输出信号y(n

‑

2d)和参考阵元接收信号x0(n)经过第一加法器02形成误差信号e(n

‑

2d),误差信号e(n

‑

2d)经过一个单位延时器03形成延时误差信号e(n

‑

3d)输送至每个权值处理模块04输出。

[0022]

结合图3所示,每组权值处理模块04包括四个乘加单元、两个单位延时器041、第一加法器048及第二加法器049,四个乘加单元分别为第一乘加单元042、第二乘加单元044、第三乘加单元045、第四乘加单元047。第一乘加单元042和第三乘加单元045均包括上支路乘法器、下支路乘法器和加法器,上支路乘法器和下支路乘法器的输出端均与加法器的输入端相连;第二乘加单元044和第四乘加单元047均包括左支路乘法器、右支路乘法器和加法器,左支路乘法器和右支路乘法器的输出端均与加法器的输入端相连。

[0023]

每组权值处理模块04的输入信号为iq信号x

ii

(n)、x

iq

(n)(i=1、

……

、m

‑

1),iq信号x

ii

(n)、x

iq

(n)一路经过三个单位延时器05形成三个单位延时信号x

ii

(n

‑

3d)、x

iq

(n

‑

3d),三个单位延时信号x

ii

(n

‑

3d)、x

iq

(n

‑

3d)经过两个单位延时器041形成五个单位延时信号x

ii

(n

‑

5d)、x

iq

(n

‑

5d)输出;延时信号x

ii

(n

‑

3d)分别连接第一乘加单元042的上支路乘法器、第三乘加单元045的上支路乘法器,延时信号x

iq

(n

‑

3d)分别连接第一乘加单元042的下支路乘法器、第三乘加单元045的下支路乘法器,第一乘加单元042的加法器输出端依次经过一个单位延时器、上支路移位器043、加法器、一个单位延时器与第二乘加单元044的左支路乘法器和右支路乘法器输入端均相连,同理,第三乘加单元045的加法器输出端依次经过一个单位延时器、下支路移位器046、加法器、一个单位延时器与第四乘加单元047的左支路乘法器和右支路乘法器输入端均相连;信号x

ii

(n)分别连接第三乘加单元044的左支路乘法器和第四乘加单元047的左支路乘法器,信号x

iq

(n) 分别连接第三乘加单元044的右支路乘法器和第四乘加单元047的右支路乘法器;初始信号yii(n

‑

1d)输送至第一加法器048的左支路,同时第二乘加单元044加法器的输出端经过一个单位延时器输送至第一加法器048的右支路,第一加法器048左右支路相加后再经过一个单位延时器形成延时信号yii (n

‑

2d);初始信号yiq(n

‑

1d)输送至第二加法器049左支路,同时第四乘加单元047加法器的输出端经过一

个单位延时器输送至第二加法器049右支路,第二加法器049左右支路相加后再经过一个单位延时器形成延时信号yiq(n

‑

2d)。

[0024]

每个权值处理模块04的延时信号y

ii

(n

‑

2d)经过第一加法器02形成权值合并输出信号y

i

(n

‑

2d),每个权值处理模块04的延时信号y

iq

(n

‑

2d)经过第一加法器02形成权值合并输出信号y

q

(n

‑

2d)。权值合并输出信号y

i

(n

‑

2d)和参考阵元接收信号x

0i

(n)经过第一加法器02形成误差信号e

i

(n

‑

2d),误差信号e

i

(n

‑

2d)经过一个单位延时器03形成延时误差信号e

i

(n

‑

3d)输送至每个权值处理模块04,延时误差信号e

i

(n

‑

3d)一路分别连接第一乘加单元042的上支路乘法器和第三乘加单元045的上支持乘法器,延时误差信号e

i

(n

‑

3d)另一路经过权值处理模块04中的一个单位延时器形成延时误差信号e

i

(n

‑

4d),延时误差信号e

i

(n

‑

4d)输出;同理,权值合并输出信号y

q

(n

‑

2d)和参考阵元接收信号x

0q

(n)经过第一加法器02形成误差信号e

q

(n

‑

2d),误差信号e

q

(n

‑

2d)经过一个单位延时器03形成延时误差信号e

q

(n

‑

3d)输送至每个权值处理模块04,延时误差信号e

q

(n

‑

3d)一路分别连接第一乘加单元042的下支路乘法器和第三乘加单元045的下支持乘法器,延时误差信号e

q

(n

‑

3d)另一路经过权值处理模块04中的一个单位延时器形成延时误差信号e

q

(n

‑

4d)输出。

[0025]

基于空时功率倒置阵的宽带干扰抑制方法具体如下:s1)初始化空时二维功率倒置阵模型,包括以下子步骤:s11)空时二维功率倒置阵结构由m个阵元组成,设第一个阵元为参考阵元1,其他m

‑

1个阵元为权值阵元,m个阵元的接收信号分别记为x0(n)、x1(n)、

……

、x

m

‑1(n),其中,x0(n)表示参考阵元接收信号,x1(n)、

……

、x

m

‑1(n)为权值阵元接收信号,n表示当前时刻;s12)每个权值阵元各有n个单位延时器,记为x

i

(n)、x

i

(n

‑

1)、

……

、x

i

(n

‑

n+1),其中,i=0、

……

、m

‑

1,每个单位延时器的复数权值记为w

ij

,i=0、

……

、m

‑

1,j=1、

……

、n,其中i表示阵元序号,j表示延时单元序号;s13)初始化参考阵元x0路权值为w

01

=1,w

0j

=0,其中j=2、

……

、n,初始化权值路x1、

……

、x

m

‑1的权值为w

ij

=0,其中i=1、

……

、m

‑

1,j=1、

……

、n记输入信号向量为x(n)=[x1(n)

⋯

x1(n

‑

n+1)

⋯

x

m

‑1(n)

⋯

x

m

‑1(n

‑

n+1)]

t

∈c

(m

‑

1)

×

n

记权向量为w=[w

1,1

w

1,2

⋯

w

1,n

⋯

w

m

‑

1,1

w

m

‑

1,2

⋯

w

m

‑

1,n

]

t

∈c

(m

‑

1)

×

n

初始化当前时刻为n=1;s2)根据多径信道环境计算处理延时量,将参考阵元接收信号进行延时,将x0路信号x0(n)延时2d,得到x0(n

‑

2d),其中2d要大于最大多径传播时延;s3)利用权值处理模块(04)计算输出信号、误差信号以及权向量的更新,具体为:s31)对于n=1,2,3,

……

,利用当前权值w,计算输出信号为y(n)=w

1,1*

x1(n)+w

1,2*

x1(n

‑

1)+

⋯

+w

1,n*

x1(n

‑

n+1)+

⋯

+w

m

‑

1,1*

x

m

‑1(n)+w

m

‑

1,2*

x

m

‑1(n

‑

1)+

⋯

+w

m

‑

1,n*

x

m

‑1(n

‑

n+1)=w

h

x(n)计算期望延时信号为d(n

‑

2d)=

‑

x0(n

‑

2d)计算延时误差信号为

e(n

‑

2d) = d(n

‑

2d)

‑

y(n

‑

2d)s32)设置步长μ,对于空时二维功率倒置阵,μ由移位器实现,μ为2

‑8~2

‑

12

,并进行权值的更新,权向量更新为:w(n+1) = w(n)+μx(n

‑

2d)e

* (n

‑

2d)s4)令n=n+1,转子步骤s31),直到满足‖w(n+1)

‑

w(n)‖

22

≤ε,其中ε为迭代终止阈值;s5)为实现自适应宽带干扰抑制,对于当前时刻n,输出信号为y ̃

(n)=x0(n)+w

h x(n)。

[0026]

上述中,h表示共轭转置、*表示共轭。

[0027]

图4~6展示了本发明提出的宽带干扰抑制方法在ad9361开发板fpga上实现的效果。为了更好的观察干扰抑制效果,没有加入有用信号分量。其中宽带干扰信号是10mhz带宽的bpsk调制信号,中心频率为150mhz。图4给出了原始10mhz宽带干扰信号频谱,干扰信号在整个带内具有

‑

70dbm的功率谱。当采用传统功率倒置算法时,在干扰中心频点获得了20db的干扰对消效果,而在频谱两侧仅有10db干扰抑制效果,如图5所示。而当采用本发明提出的宽带干扰抑制方法时,整个带内干扰均获得了40db以上的干扰抑制效果,如图6所示。需要注意的是频点1(150.1mhz)为开发板ad9361的本振泄露,实际应用中可以通过设置上下变频频点避开有用信号,例如当有用信号工作在150mhz时将本振设置为151mhz,前端滤波器可以有效滤除本振信号。

[0028]

最后所应该说明的是:以上具体的实施步骤主要是用来说明本发明的具体实现过程,而非限制本发明的技术方案,尽管该部分针对具体的实现实例进行了详细的说明,该领域的技术人员都应该理解:依然可以对本发明进行修改或者等同替换,而不能脱离本发明的精神和范围的任何修改或者局部替换,其均应该涵盖在本发明的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1