一种用于CMOS图像传感器芯片级ADC的双位移位校正系统的制作方法

一种用于cmos图像传感器芯片级adc的双位移位校正系统

技术领域

1.本发明涉及互补型金属-氧化物-半导体(cmos)图像传感器领域和数据转换器领域,具体涉及一种用于cmos图像传感器芯片级adc的双位移位校正系统。

背景技术:

2.芯片级adc具有明显的优势:低功耗、低噪声和高一致性。芯片级adc常采用流水线结构,具有较高的速度和分辨率,流水线adc适用于多种环境应用,常见的流水线adc由采样保持电路(sh),多级量化电路(mdac)和flash adc组成。sh电路常用电荷分享或者电容翻转结构实现,而mdac常用1.5bit、2.5bit、3.5bit结构,包含一个冗余位,其放大倍数分别是2、4、8倍,1.5bit mdac设计难度小但功耗面积较大,3.5bit mdac设计难度大,8倍的闭环增益所需要的带宽和增益是非常难以实现的,通常采用2.5bit mdac是折中的选择,与其他两种结构的mdac一样,2.5bit mdac输出摆幅为-0.5vref~+0.5vref,较高的输出摆幅需要更大的带宽和电源,且其码间校正范围只有0.125vref(3bit),很难直接得到较高的sfdr。

技术实现要素:

3.本发明的目的在于提供一种用于cmos图像传感器芯片级adc的双位移位校正系统,以克服现有技术的不足。

4.为达到上述目的,本发明采用如下技术方案:

5.一种用于cmos图像传感器芯片级adc的双位移位校正系统,包括依次连接的sh电路、多级串联的编码器电路和flash adc电路,sh电路用于电荷分享或者电容翻转结构实现,每级编码器电路输出4位数字码,含两位校正码;多级串联的编码器电路包括一个一级编码器以及多个串联的二级编码器,flash adc输出移位相加后的数字码。

6.进一步的,一级编码器电路结构包括上半部分采样电路、下半部分采样电路、第一增益自举运算放大器和第一编码器,上半部分采样电路和下半部分采样电路分别与第一增益自举运算放大器的反向输入端和同向输入端连接,第一编码器根据接收上半部分采样电路和下半部分采样电路输出的数字码实现余差操作,上半部分采样电路和下半部分采样电路在前一级采样保持输出时闭合,闭环增益为4倍,上半部分采样电路和下半部分采样电路输出到下一级的电压幅值只有mdac电路的一半,上半部分采样电路和下半部分采样电路的开关动作一致。

7.进一步的,上半部分采样电路包括第一flash adc、第一开关电容阵列、第一自举开关、第一开关电容和第一反馈电容,第一flash adc的一端和第一开关电容阵列的一端连接于第一编码器,第一开关电容阵列的另一端连接第一增益自举运算放大器的反向输入端、第一开关电容的一端和第一反馈电容的一端,第一开关电容的另一端连接第一自举开关的一端,第一自举开关的另一端接收输入δvin,第一反馈电容的另一端接第一增益自举运算放大器的电源正极。

8.进一步的,上半部分采样电路和下半部分采样电路结构相同。

9.进一步的,多级串联的编码器电路包括一个一级编码器和四个串联的二级编码器,一级编码器和二级编码器的编码方式不同,四个串联的二级编码器功耗逐级递减,每级均输出4位数字码。

10.进一步的,编码器的输出幅值均为-0.25vref~+0.25vref。

11.进一步的,二级编码器包括第二增益自举运算放大器、第三开关电容阵列和第四开关电容阵列,第三开关电容阵列和第四开关电容阵列结构相同,在前一级采样保持输出时闭合,闭环增益为4倍,第三开关电容阵列和第四开关电容阵列输出到下一级的电压幅值与以及编码器输出电压幅值一致。

12.进一步的,二级编码器还包括第二flash adc、第二编码器、余差开关控制阵列和串联电容开关阵列,第三开关电容阵列接第二增益自举运算放大器的反向输入端,第四开关电容阵列接第二增益自举运算放大器的同向输入端,第三开关电容阵列和第四开关电容阵列均连接一个串联电容开关阵列,第三开关电容阵列与第二增益自举运算放大器的电源正极之间连接第三反馈电容,第四开关电容阵列与第二增益自举运算放大器的电源负极之间连接第四反馈电容,第二编码器连接第二flash adc和余差开关控制阵列,第二flash adc连接第三开关电容阵列和第四开关电容阵列。

13.进一步的,第三开关电容阵列和第四开关电容阵列相同,包括多组并联的开关电容电路,开关电容电路包括串联的自举开关和开关电容。

14.进一步的,第二flash adc由9个动态比较器构成,在stage1输出幅值-0.25vref~+0.25vref内。

15.与现有技术相比,本发明具有以下有益的技术效果:

16.本发明一种用于cmos图像传感器芯片级adc的双位移位校正系统,包括依次连接的sh电路、多级串联的编码器电路和flash adc电路,sh电路用于电荷分享或者电容翻转结构实现,每级编码器电路输出4位数字码,含两位校正码;多级串联的编码器电路包括一个一级编码器以及多个串联的二级编码器,flash adc输出移位相加后的数字码,根据电容的电荷守恒原理,采用电荷分享采样技术,实现了双位移位校正功能,每级4bit输出,两位校正算法,级间闭环增益只有4倍,采用非交叠时钟控制,前级采样,后级放大输出,流水线工作,降低了级间闭环增益,降低了后级量化范围,提升了校正区间,对于adc的整体性能提升具有显著效果。采用多级串联的编码器电路,可有效降低系统功耗、提升量化输入摆幅并极大提升sfdr等关键动态参数,具有很高的实用性。

17.进一步的,采用一级编码器电路结构,其闭环放大倍数只有4倍,输出摆幅只有传统mdac输出值的一半,这就极大降低了对增益和带宽的需求,两位冗余位的引入可以得到更高的线性度。

18.进一步的,采用多级串联的二级编码器,考虑到比较器失调、电容失配等影响,在一级编码器输出幅值超出-0.25vref~+0.25vref时,校正开始介入,校正区间为-0.375vref~-0.25vref和-0.25vref~-0.375vref,超出这一范围就会引入误码,运放功耗降低,电荷分享容值降低。

附图说明

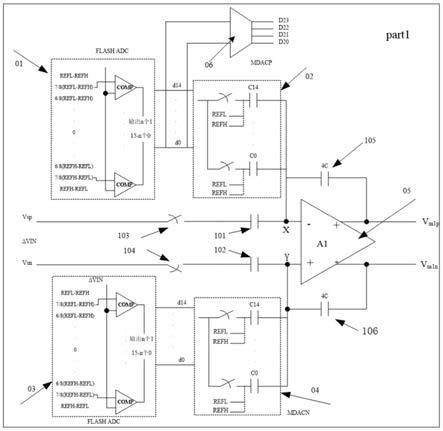

19.图1为本发明实施例中一级编码器电路示意图。

20.图2为本发明实施例中二级编码器电路示意图。

21.图3为本发明实施例中双位校正应与于14bit、200msps adc结构图。

22.图4为本发明实施例中一级编码器输出传函曲线图。

23.图5为本发明实施例中二级编码器输出传函曲线图。

24.图6为本发明实施例中双位移位校正后算法示意图。

具体实施方式

25.下面结合附图对本发明做进一步详细描述:

26.如图3所示,一种用于cmos图像传感器芯片级adc的双位移位校正系统,包括依次连接的sh电路、多级串联的编码器电路和flash adc电路,sh电路用于电荷分享或者电容翻转结构实现,每级编码器电路输出4位数字码,含两位校正码;多级串联的编码器电路包括一个一级编码器以及多个串联的二级编码器。

27.如图1所示,一级编码器(part1)电路结构,包括上半部分采样电路、下半部分采样电路、第一增益自举运算放大器05和第一编码器06,上半部分采样电路和下半部分采样电路分别与第一增益自举运算放大器05的反向输入端和同向输入端连接,第一编码器06根据接收上半部分采样电路和下半部分采样电路输出的数字码实现余差操作,上半部分采样电路和下半部分采样电路在前一级采样保持输出时闭合,闭环增益为4倍,上半部分采样电路和下半部分采样电路输出到下一级的电压幅值只有mdac电路的一半,上半部分采样电路和下半部分采样电路的开关动作一致。

28.具体的,上半部分采样电路包括第一flash adc(快闪式类比数位转换器)01、第一开关电容阵列02、第一自举开关103、第一开关电容101和第一反馈电容105,第一flash adc 01的一端和第一开关电容阵列02的一端连接于第一编码器06,第一开关电容阵列02的另一端连接第一增益自举运算放大器05的反向输入端、第一开关电容101的一端和第一反馈电容105的一端,第一开关电容101的另一端连接第一自举开关103的一端,第一自举开关103的另一端接收输入δvin,第一反馈电容105的另一端接第一增益自举运算放大器05的电源正极;

29.下半部分采样电路包括第二flash adc(快闪式类比数位转换器)03、第二开关电容阵列04、第二自举开关104、第二开关电容102和第二反馈电容106,第二flash adc 03的一端和第二开关电容阵列04的一端连接于第一编码器06,第二开关电容阵列04的另一端连接第一增益自举运算放大器05的同向输入端、第二开关电容104的一端和第二反馈电容106的一端,第二开关电容102的另一端连接第二自举开关104的一端,第二自举开关104的另一端接收输入δvin,第二反馈电容106的另一端接第一增益自举运算放大器05的电源负极;

30.如图1所示,自举开关(103、104)闭合,采样前级采样保持输出的电压值,图1中x和y点由内部复位开关箝位至v

cm

,同时,flash adc(01、03)采集电阻分压的参考信号,开始进行翻转,对输入δvin量化;设定周期后(半个时钟),开关翻转,自举开关(103、104)断开,flash adc(01、03)输出数字码给第一编码器06,同时控制开关电容阵列(02、04)翻转至refh/refl实现余差操作,电荷受电容极板翻转影响,转移到反馈电容(105、106),实现余差的4倍放大,然后在下一个时钟跳变时,复位开关对电容电荷进行复位,重复前一级采样操作,编码器输出的4位码值存于锁存器中,待6个时钟周期后移位相加输出最终码值,一级编

0.25vref~+0.25vref时,校正开始介入,校正区间为-0.375vref~-0.25vref和-0.25vref~-0.375vref,超出这一范围就会引入误码。采用四个二级编码器,stage3~stage5结构与stage2完全一致,运放功耗逐级降低,电荷分享容值降低,stage6为flash adc,采用与stage2相同的电路;系统一共6级,输出码为d23~d0,两位移位校正后,输出最终14bit码值。

42.如图2所示,串联电容开关阵列包括串联的开关和两级电容,电容(122,123)串联,电容122左侧由adc输出高低值控制开关214选择reh或者refl。电容(124,125)串联,电容125左侧接长通控制开关213,选择reh。二级编码器中的自举开关(110、116)与一级编码器中的自举开关(103、104)反向不交叠。余差开关控制阵列15为adc(第二增益自举运算放大器)输出组正反控制信号,控制对应第三开关电容阵列11和第四开关电容阵列12开关电容的关断。

43.开始时,自举开关(110、116)闭合,采样前级stage1余差放大输出的电压值,n和m点由内部复位开关箝位至v

cm

,同时,开关电容阵列(11、12)采集完电阻分压的参考信号,开始进行翻转,对输入δvin量化;半个时钟周期后,开关翻转,自举开关(110、116)断开,第二flash adc 13输出数字码给第二编码器14,同时余差开关控制阵列15控制开关电容阵列(11、12)翻转至refh/refl实现余差操作,串联电容开关(124,125,213)长通至refh,串联电容开关(122,123,241)受采样时钟控制,当stage2采样时,开关214导通至refl,当stage2放大时,开关214导通至refh,电荷受电容极板翻转影响,转移到反馈电容,实现余差的4倍放大,然后在下一个时钟跳变时,复位开关对电容电荷进行复位,重复前一级采样操作,编码器输出的4位码值存于锁存器中,待6个时钟周期后移位相加输出最终码值。stage2的传函曲线由图2结合电荷转移过程计算可得,计算过程与stage1相同,根据电荷守恒定理有:

[0044][0045]

stage2的传函曲线如图5所示,其输出摆幅为

±

0.25v

ref

,编码器14输出4位数字信号d19~d16。

[0046]

stage3~stage5结构与stage2一致,其功耗及电容绝对值逐级递减,对应stage3输出4位数字信号d15~d12,stage4输出4位数字信号d11~d8,stage5输出4位数字信号d7~d4,最后stage6输出4位数字信号d3~d0,stage6不需要余差放大,如果该系统要实现16bit输出码的话,stage6可按照stage5结构,stage7采用flash adc加编码器输出。

[0047]

校准机理六级流水线adc的输出码制有关。因此,本文给出一个芯片级adc的功能框图,如图3所示,第一级为常用的sh电路,中间五级mdac,最后一级flash adc,可实现14bit输出,对输入电压进行粗比较后的判定值,经转换,产生输出到correction的数据《3:0》。图6中的d23~d0为所示adc的输出码校对过程,该级adc的输出值为正常的偏移码格式。

[0048]

该结构的引入降低了下一级的量化范围,增大了级间的校正区间,从而降低了电容面积、功耗并提升了线性度。

[0049]

本发明为一款应用于千万像素级cmos图像传感器的芯片级adc ip,是一款180nm,14bit、200msps的流水线型结构adc,相比于传统1.5bit、2.5bit、3.5bit mdac结构流水线adc,其输入vp-p高达2v,功耗仅为122mw,sfdr高达100db以上,这都是由于两位移位校正算法的使用。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1