一种基于pcie接口的以太网控制器异常处理系统和方法与流程

1.本发明属于计算机网络技术领域,具体属于一种基于pcie接口的以太网控制器异常处理系统和方法。

背景技术:

2.当以太网控制器通过pcie接口将数据上传主机时,其链路异常会引起传输失败;传统的方法是将错误信息以中断的方式告知主机,主机对异常处理后,需要复位操作重启传输;这种处理机制不仅会带来较大的时间开销,也会引起数据帧的传输异常。

技术实现要素:

3.为了解决现有技术中存在的问题,本发明提供一种基于pcie接口的以太网控制器异常处理系统和方法,能够及时的对故障状态进行诊断、现场记录及告知主机;提供的两种处理机制不仅能够避免复位引起的时间开销,同时也能够保证在链路恢复后,数据帧的完整性和正确性。

4.为实现上述目的,本发明提供如下技术方案:

5.一种基于pcie接口的以太网控制器异常处理系统,包括dma控制模块、master接口中断状态控制信息模块、bd控制信息模块、mwr模块和slave接口中断状态控制信息模块;

6.dma控制模块用于发起pcie的master接口传输请求、对pcie内部master接口的中断状态进行查询、发起中断请求给主机、执行重发或者放弃操作;

7.master接口中断状态控制信息模块用于对当前pcie的master接口的错误状态信息进行存储;在放弃状态时,将master接口的状态信息告知bd控制信息模块;

8.bd控制信息模块用于根据错误标志信息,将当前帧返回bd描述符的错误状态标志位进行置位;

9.mwr模块用于发起pcie的slave接口的传输请求、对pcie内部slave接口的中断状态进行查询、发起中断请求给主机、执行重发或者放弃操作;

10.slave接口中断状态控制信息模块用于对当前pcie的slave接口的错误状态信息进行存储;在放弃状态时,将slave接口的状态信息告知bd控制信息模块。

11.优选的,所述中断状态包括发起的传输请求pcie不支持、发起的请求完成、发起的请求完成超时和传输数据有错误。

12.优选的,所述master接口中断状态控制信息模块的错误状态信息包括当前请求的源地址、目的地址、长度信息、读写控制信号、输出中断标志信号和操作恢复标志信号。

13.优选的,所述slave接口中断状态控制信息模块的错误状态信息包括当前请求的源地址、目的地址、长度信息、读写控制信号、输出中断标志信号和操作恢复标志信号。

14.优选的,bd描述符的信息包括当前帧在主机存储空间的地址、长度和当前帧在传输过程中的状态信息。

15.一种基于pcie接口的以太网控制器异常处理方法,包括以下步骤,

16.步骤1,dma控制模块或mwr模块接收pcie的中断状态信息;

17.步骤2,暂停数据传输;

18.步骤3,对pcie的中断状态进行查询,判断是数据完成中断还是错误中断;

19.步骤4,若是错误中断,将本次传输的控制信息写到master接口中断状态控制信息模块或slave接口中断状态控制信息模块,执行步骤;否则,完成本次传输,启动下一次请求;

20.步骤5,若是错误中断,给主机发送中断请求,主机在读取中断状态信息后,对链路的异常进行诊断、恢复,然后根据需求选择重发或者放弃;若重发,dma控制模块或mwr模块会将该次传输再次启动;若放弃,bd控制信息模块会通过返回bd描述符的方式告知主机这帧数据的错误状态,然后启动下一帧数据的传输。

21.优选的,步骤1中,中断状态信息包括发起的传输请求pcie不支持、发起的请求完成、发起的请求完成超时和传输数据有错误。

22.优选的,步骤4中,控制信息包括当前请求的源地址、目的地址、长度信息、读写控制信号、输出中断标志信号和操作恢复标志信号;

23.操作恢复标志信号产生一个周期的脉冲信号,为重传或放弃标志信号,1表示放弃,0表示重新发送;在放弃状态时,将状态信息告知bd控制信息模块。

24.与现有技术相比,本发明具有以下有益的技术效果:

25.本发明的一种基于pcie接口的以太网控制器异常处理系统,能够及时的对pcie的master接口和slave接口的故障状态进行诊断、现场记录及通知主机;给主机提供了放弃和重发两种处理机制,若主机选择放弃,则能够将数据帧的错误状态通过返回bd描述符的方式告知主机;不仅避免了复位引起的时间开销,同时能够保证在链路恢复后数据帧的完整性和正确性。本发明能够及时的对故障状态进行诊断、现场记录及告知主机;提供的两种处理机制不仅避免了复位引起的时间开销,同时能够保证在链路恢复后数据帧的完整性和正确性。

26.通过对该系统进行功能仿真,并与传统的复位方法进行比较。在测试环境中,随机产生1000组报文,其中有200组为异常报文。仿真结果表明,该发明提出的异常处理机制在不用复位的情况下,不仅能够实现数据帧的重发和丢帧两种机制,同时能够将异常数据帧通过返回bd描述符的方式告知主机,主机在对返回bd描述符解析后,能够准确获知当前帧的错误状态,有效提高了以太网控制器应用的可靠性。

附图说明

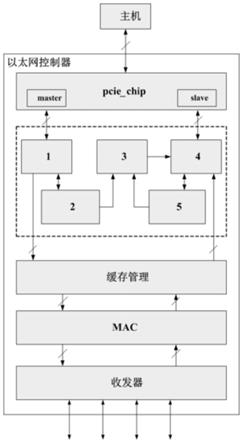

27.图1为对以太网控制器pcie接口的异常处理机制结构框图;

28.附图中:1为dma控制模块;2为master接口中断状态控制信息模块;3为bd控制信息模块;4为mwr模块;5为slave接口中断状态控制信息模块。

具体实施方式

29.下面结合具体的实施例对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

30.本发明的一种基于pcie接口的以太网控制器异常处理方法,在pcie的应用层接口

通过故障状态诊断、现场记录的方法设计了重发和放弃两种控制机制,且将数据帧错误状态通过返回bd描述符的方式告知主机。具体流程为:

①

dma控制模块或mwr模块收到pcie的中断;

②

暂停数据传输;

③

对中断状态进行查询,判断是数据完成中断还是错误中断;

④

若是错误中断,将本次传输的控制信息写到master接口中断状态控制信息模块或slave接口中断状态控制信息模块;否则,完成本次传输,启动下一次请求;

⑤

若是错误中断,给主机发送中断请求。主机在读取中断状态信息后,对链路的异常进行诊断、恢复,然后根据需求选择重发或者放弃;若重发,dma控制模块或mwr模块会将该次传输再次启动;若放弃,控制器会通过返回bd描述符的方式告知主机这帧数据的错误状态,然后启动下一帧数据的传输。

31.如图1所示,本发明一种基于pcie接口的以太网控制器异常处理系统,包括dma控制模块1、master接口中断状态控制信息模块2、bd控制信息模块3、mwr模块4、slave接口中断状态控制信息模块5。

32.dma控制模块1的主要功能是发起pcie的master接口传输请求,首先根据控制器内部的控制及数据信息,发起一次pcie的master接口的访问请求,该请求包括的信息为:从主机搬需要发送的数据到控制器,从主机搬发送bd描述符和接收bd描述符到控制器。当pcie的master接口产生中断时,对pcie内部的中断状态进行查询,主要的中断状态包括unsupported_request(发起的传输请求pcie不支持)、completer_abort(发起的请求完成)、completion_time_out(发起的请求完成超时)和data_poisoning(传输数据有错误);其中,只有completer_abort是传输正确完成中断,另外三种状态为错误状态,也是本发明需要处理的异常错误。如果查询后为completer_abort状态,则直接响应完成控制信号,如果为其它的异常状态,则将本次访问的控制信息存储到master接口中断状态控制信息模块中,然后发起中断请求给主机;主机在读取中断状态信息后,对链路的异常进行诊断、恢复,然后根据需求选择重发或者放弃;若重发,dma控制模块会将该次传输再次启动;若放弃,dma控制模块会通过返回bd描述符的方式告知主机这帧数据的错误状态,然后启动下一帧数据的传输。

33.master接口中断状态控制信息模块2的主要功能是对当前pcie的master接口的错误状态信息进行存储,主要包括当前请求的源地址(位宽可配置)、目的地址(位宽可配置)、长度信息(位宽可配置)、读写控制信号(1位宽)、输出中断标志信号(1位宽)和操作恢复标志信号(1位宽)。其中,操作恢复标志信号产生一个周期的脉冲信号,为重传/放弃标志信号,1表示放弃(产生done信号),0表示重新发送;在放弃状态时,需要将状态信息告知bd控制信息模块。

34.bd控制信息模块3的主要功能是根据master接口中断状态控制信息模块和slave接口中断状态控制信息模块给出的错误标志信息,将当前帧的返回bd描述符的错误状态标志位进行置位,描述符的信息还包括当前帧在主机存储空间的地址、长度和该帧在传输过程中的状态信息,这样主机在对该bd描述符解析时,就能判断出当前帧的错误状态,便于对该帧进行特殊处理。

35.mwr模块4的主要功能是根据接收的数据及返回bd描述符,发起pcie的slave接口的传输访问,功能和dma控制模块类似。首先根据控制器内部的控制及数据信息,发起一次pcie的slave接口的访问请求,该请求包括的信息为:从mac搬接收的数据到主机,从控制器搬返回bd描述符和状态块到主机。当pcie的slave接口产生中断时,对pcie内部的中断状态

进行查询,主要的中断状态包括unsupported_request(发起的传输请求pcie不支持)、completer_abort(发起的请求完成)、completion_time_out(发起的请求完成超时)和data_poisoning(传输数据有错误);其中,只有completer_abort是传输正确完成中断,另外三种状态为错误状态,也是本发明需要处理的异常错误。如果查询后为completer_abort状态,则直接响应完成控制信号,如果为其它的异常状态,则将本次访问的控制信息存储到slave接口中断状态控制信息模块中,然后发起中断请求给主机;主机在读取中断状态信息后,对链路的异常进行诊断、恢复,然后根据需求选择重发或者放弃;若重发,mwr模块会将该次传输再次启动;若放弃,mwr模块会通过返回bd描述符的方式告知主机这帧数据的错误状态,然后启动下一帧数据的传输。

36.slave接口中断状态控制信息模块5的主要功能是对当前pcie的slave接口的错误状态信息进行存储,主要包括当前请求的源地址(位宽可配置)、目的地址(位宽可配置)、长度信息(位宽可配置)、读写控制信号(1位宽)、输出中断标志信号(1位宽)和操作恢复标志信号(1位宽);其中,操作恢复标志信号产生一个周期的脉冲信号,为重传/放弃标志信号,1表示放弃(产生done信号),0表示重新发送;在放弃状态时,需要将状态信息告知bd控制信息模块。

37.本发明是针对以太网控制器pcie接口的异常状态,能够及时的对pcie的master接口和slave接口的故障状态进行诊断、现场记录及通知主机;给主机提供了放弃和重发两种处理机制,若主机选择放弃,则能够将数据帧的错误状态通过返回bd描述符的方式告知主机;不仅避免了复位引起的时间开销,同时能够保证在链路恢复后数据帧的完整性和正确性。

38.实施例

39.其中,实现内部为以太网控制器结构,虚线内部结构为本发明所提出的一种基于pcie接口的以太网控制器异常处理机制的结构,这两种处理机制对pcie的master接口和slave接口都适用,虚线外部为与其连接的其它模块。其中,主机的主要功能包括:将上层协议需要发送的数据帧及描述符发送给以太网控制器,将以太网控制器输出的数据帧及返回的描述符转发给上层协议处理,通过pcie接口对控制电路进行相应配置;pcie模块的主要功能是根据主机和控制电路的请求进行数据帧及描述符的转发,该模块本身不对数据帧内容进行处理;缓存管理模块的主要功能是对收发的数据进行存储管理,采用接收通路和发送通路分离,数据先进先出的原则;mac模块主要实现两个功能:第一、数据的封装与解封,包括寻址、差错校验等;第二、媒体介入控制,包括媒体分配和竞争处理;收发器模块主要功能是把上一层传递过来的数据字节转换成可以通过物理媒介传输的信号,另一方面也负责把来自物理媒介的信号转换成数据链路层传输的数据字节。

40.dma控制模块1主要功能为发起pcie的master接口传输请求、对pcie内部master接口的中断状态进行查询、发起中断请求给主机、重发或者放弃两种机制的执行。

41.master接口中断状态控制信息模块2主要功能是对当前pcie的master接口的错误状态信息进行存储;在放弃状态时,将master接口的状态信息告知bd控制信息模块。

42.bd控制信息模块3主要功能是根据错误标志信息,将当前帧返回bd描述符的错误状态标志位进行置位。

43.mwr模块4主要功能为发起pcie的slave接口的传输请求、对pcie内部slave接口的

中断状态进行查询、发起中断请求给主机、重发或者放弃两种机制的执行。

44.slave接口中断状态控制信息模块5主要功能是对当前pcie的slave接口的错误状态信息进行存储;在放弃状态时,将slave接口的状态信息告知bd控制信息模块。

45.本发明可用于pc机、服务器、测控系统中心机等系统的网卡设备中,特别适用于对网卡的可靠性要求较高的计算机网络系统。

46.采用本发明提出的一种基于pcie接口的以太网控制器异常处理系统,能够及时的对故障状态进行诊断、现场记录及告知主机;提供的两种处理机制不仅避免了复位引起的时间开销,同时能够保证在链路恢复后数据帧的完整性和正确性,有效提升了以太网控制器的可靠性。

47.根据上述方案,用verilog语言对本发明中各个模块的逻辑设计进行描述,并将其与网卡设备中的其它模块集成在一起,进行系统级的验证。验证结果表明,本发明实现了设计功能,且可靠性满足预期。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1