垂直沟道单元阵列晶体管结构和包括其的DRAM器件的制作方法

垂直沟道单元阵列晶体管结构和包括其的dram器件

技术领域

1.本公开涉及一种垂直沟道单元阵列晶体管结构和/或包括其的动态随机存取存储器(dram)器件。

背景技术:

2.动态随机存取存储器(dram)器件中的每个单位器件可以具有包括一个晶体管和一个电容器的1t1c结构。随着器件集成度的不断提高,已经提出用于减小在平面图中每个单位器件的面积的结构。凹陷沟道单元阵列晶体管(rcat)结构最初应用于dram器件,但是现在掩埋沟道单元阵列晶体管(bcat)可购买到。近来已经开发其中晶体管被垂直布置的垂直沟道单元阵列晶体管(vcat)结构以进一步减小单位器件的面积。

技术实现要素:

3.提供垂直沟道单元阵列晶体管结构和/或包括其的动态随机存取存储器(dram)器件。

4.另外的方面将部分地在随后的描述中阐述,并且部分地将从该描述变得明显,或者可以通过实践本公开的所呈现的实施方式而获知。

5.根据一实施方式,一种垂直沟道单元阵列晶体管结构可以包括:半导体基板;多个沟道,在半导体基板上布置成阵列并且每个从半导体基板垂直地延伸;在所述多个沟道上的栅极绝缘层;多条字线,在半导体基板上并在第一方向上延伸;以及二维(2d)材料层,在所述多条字线中的每条的至少一个表面上。

6.在一些实施方式中,所述多条字线中的每条可以对应于所述多个沟道中的在第一方向上排布的沟道。

7.在一些实施方式中,2d材料层可以在所述多条字线的底表面上。2d材料层可以延伸到所述多条字线的侧表面。

8.在一些实施方式中,2d材料层可以在所述多条字线的顶表面上。2d材料层还可以提供在所述多条字线的底表面上。

9.在一些实施方式中,2d材料层可以包括导体、绝缘体和半导体中的至少一种。

10.在一些实施方式中,2d材料层可以包括石墨烯、过渡金属二硫属化物(tmd)、gase、gate2、snse、bi2se3、bi2o2se、六方氮化硼(h-bn)、非晶氮化硼(a-bn)、硅烯、锡烯、碲烯、硼烯和锑烯中的至少一种。

11.在一些实施方式中,石墨烯可以包括具有在从1nm至100nm的范围内的尺寸的晶粒。

12.在一些实施方式中,tmd可以包括mos2、mose2、mote2、ws2、wse2、wte2、zrs2、zrse2、hfs2、hfse2、nbse2、rese2、pts2、ptse2、pdse2、pdte2、vs2、vse2、fese2和fete2中的至少一种。

13.在一些实施方式中,所述多条字线可以包括金属、半导体和合金中的至少一种。

14.在一些实施方式中,所述多条字线的每条可以具有单层结构或者其中堆叠不同材

料的多层结构。

15.在一些实施方式中,半导体基板可以包括多个源极区。所述多个源极区和与其对应的多个漏极区可以分别提供在所述多个沟道当中的每个对应沟道的下部和上部上。

16.在一些实施方式中,垂直沟道单元阵列晶体管结构还可以包括多条位线,每条位线电连接所述多个源极区中的在与第一方向相交的第二方向上排布的源极区。

17.在一些实施方式中,垂直沟道单元阵列晶体管结构还可以包括在所述多条位线之间的多个绝缘材料,并且所述多个绝缘材料可以在第二方向上延伸。

18.根据一实施方式,一种动态随机存取存储器(dram)器件包括垂直沟道单元阵列晶体管结构和在垂直沟道单元阵列晶体管结构上的多个电容器。垂直沟道单元阵列晶体管结构可以包括半导体基板、在半导体基板上布置成阵列并且每个从半导体基板垂直地延伸的多个沟道、在所述多个沟道上的栅极绝缘层、在半导体基板上并在第一方向上延伸的多条字线、以及在所述多条字线中的每条的至少一个表面上的二维(2d)材料层。

19.在一些实施方式中,2d材料层可以在所述多条字线的底表面和所述多条字线的顶表面中的至少一个上。2d材料层可以进一步延伸到所述多条字线的侧表面。

20.在一些实施方式中,半导体基板可以包括多个源极区。所述多个源极区和与其对应的多个漏极区可以分别提供在所述多个沟道当中的每个对应沟道的下部和上部上。

21.在一些实施方式中,垂直沟道单元阵列晶体管结构还可以包括多条位线,每条位线电连接所述多个源极区中的在与第一方向相交的第二方向上排布的源极区。

22.在一些实施方式中,所述多个电容器中的每个可以电连接到所述多个漏极区中的对应一个。

23.根据另一实施方式,一种电子装置包括所述dram器件。

24.根据一实施方式,一种垂直沟道单元阵列晶体管结构可以包括:半导体基板,包括源极区;在源极区上的沟道结构,该沟道结构包括垂直于半导体基板的上表面延伸的沟道和在沟道之上的漏极区;在半导体基板上的字线,该字线在第一方向上延伸;在字线和沟道结构之间的栅极绝缘层,该栅极绝缘层围绕沟道结构;以及直接接触字线的二维(2d)材料层。

25.在一些实施方式中,2d材料层可以包括石墨烯、过渡金属二硫属化物(tmd)、gase、gate2、snse、bi2se3、bi2o2se、六方氮化硼(h-bn)、非晶氮化硼(a-bn)、硅烯、锡烯、碲烯、硼烯和锑烯中的至少一种。

26.在一些实施方式中,2d材料层可以直接接触字线的底表面。

27.在一些实施方式中,2d材料层可以直接接触字线的顶表面。

28.在一些实施方式中,2d材料层可以在字线和栅极绝缘层之间延伸。

附图说明

29.从以下结合附图的描述,本公开的某些实施方式的以上和其它的方面、特征和优点将变得更加明显,附图中:

30.图1是示出根据一实施方式的动态随机存取存储器(dram)器件的平面图;

31.图2是示出图1的dram器件的透视图;

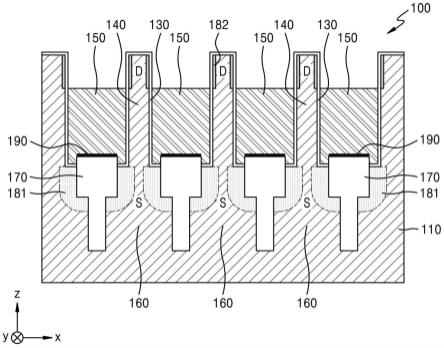

32.图3是示出图1的垂直沟道单元阵列晶体管(vcat)结构的剖视图;

33.图4是示出根据另一实施方式的vcat结构的图;

34.图5是示出根据另一实施方式的vcat结构的图;

35.图6是示出根据另一实施方式的vcat结构的图;

36.图7是示出根据另一实施方式的vcat结构的图;

37.图8是示出根据另一实施方式的vcat结构的图;

38.图9是示出根据另一实施方式的vcat结构的图;

39.图10和图11是示出根据一实施方式的可应用于电子装置的装置架构的概念图;以及

40.图12是根据一实施方式的存储器系统的示意图。

具体实施方式

41.现在将详细参照实施方式,其示例在附图中示出,其中相同的附图标记始终指代相同的元件。在这点上,发明构思的实施方式可以具有不同的形式并且不应被解释为限于这里阐述的描述。因此,下面通过参照附图仅描述了所呈现的实施方式以说明各方面。当在这里使用时,术语“和/或”包括一个或更多个相关列出项目的任何和所有组合。当在一列元件之后时,诸如

“……

中的至少一个”的表述修饰整列元件而不是修饰该列中的个别元件。例如,“a、b和c中的至少一个”和类似的语言(例如,“选自由a、b和c组成的组中的至少一种”)可以被解释为仅a、仅b、仅c、或a、b和c中的两个或更多个的任意组合,诸如例如abc、ab、bc和ac。

42.在下文,将参照附图描述本公开的实施方式。相同的附图标记始终指代相同的元件,并且在附图中,为了清楚和便于说明,元件的尺寸可以被夸大。此外,下面描述的实施方式仅是示例,并且可以从实施方式进行各种修改。

43.当第一元件在第二元件“上”或“之上”时,它可以包括第一元件接触第二元件并直接位于第二元件的顶部、底部、左边或右边的情况,以及第一元件不接触第二元件并位于第二元件的顶部、底部、左边或右边且有第三元件位于它们之间的情况。单数形式“一”、“一个”和“该”旨在也包括复数形式,除非上下文另外清楚地指示。当一部分“包括”一元件时,另外的元件可以被进一步包括,而不是排除另外的元件的存在,除非另外地描述。

44.在描述本公开的上下文中术语“一”和“一个”以及“该”和类似指示语的使用将被解释为涵盖单数和复数两者。这里描述的所有的方法的步骤可以以任何合适的顺序执行,除非这里另外地指示或另外地与上下文明显矛盾,并且不限于所描述的顺序。

45.此外,诸如“单元”或“模块”的术语是指执行至少一种功能或操作的单元,并且所述单元可以被实现为硬件、或软件、或者硬件和软件的组合。

46.此外,连接附图中示出的元件的线或构件仅说明功能连接和/或物理或电路连接。在实际器件中,部件之间的连接可以通过可替换或添加的各种功能连接、物理连接或电路连接来表示。

47.这里提供的任何和所有示例或示例语言的使用仅旨在更好地描述本公开并且不对本公开的范围构成限制,除非另外地声明。

48.图1是示出根据一实施方式的动态随机存取存储器(dram)器件3000的平面图。图2是示出图1的dram器件3000的透视图。

49.参照图1和图2,dram器件3000包括布置成阵列的多个单位器件3100。每个单位器件3100具有包括一个晶体管和一个电容器的1t1c结构。

50.dram器件3000包括垂直沟道单元阵列晶体管(vcat)结构100和提供在vcat结构100上的多个电容器3500。在vcat结构100中,多条字线150和多条位线160被提供为彼此交叉。每条字线150可以在第一方向(例如,x轴方向)上延伸,每条位线160可以在与第一方向相交的第二方向(例如,y轴方向)上延伸。晶体管可以位于所述多条字线150和所述多条位线160之间的交叉点处。

51.图3是示出图1的vcat结构100的剖视图。

52.参照图3,vcat结构100包括半导体基板110和在半导体基板110上布置成阵列的多个沟道140。所述多个沟道140可以在半导体基板110的平面(例如,xy平面)上布置成二维(2d)阵列。

53.半导体基板110可以包括例如硅(si)。作为具体示例,半导体基板110可以是掺有n型杂质的硅基板。然而,这仅是示例,半导体基板110可以包括例如iv族半导体材料(诸如锗(ge)、硅锗(sige)或硅碳化物(sic))、iii-v族半导体材料(诸如镓砷化物(gaas)、铟砷化物(inas)或铟磷化物(inp))、氧化物半导体、氮化物半导体或氮氧化物半导体。然而,本公开不限于此。

54.所述多个沟道140中的每个可以从半导体基板110垂直地延伸。每个沟道140可以从半导体基板110的顶表面垂直地突出。每个沟道140可以与半导体基板110一体地形成并可以包括与半导体基板110的材料相同的半导体材料。

55.源极s和漏极d分别提供在每个沟道140的下部和上部上。源极s电连接到沟道140的下部,漏极d电连接到沟道140的上部。作为重掺杂区的第一掺杂区181和第二掺杂区182分别形成在源极s和漏极d中。图2的电容器3500可以连接到提供在沟道140的上部上的漏极d。在本说明书中,源极s也可以被称为源极区,漏极d也可以被称为漏极区;由漏极d和沟道140形成的结构可以被称为沟道结构。

56.源极s在半导体基板110的顶表面周围提供成阵列以对应于沟道140。多条位线160提供在源极s下面以在第二方向(例如,y轴方向)上延伸。每条位线160可以电连接在第二方向上排布的源极s。所述多条位线160可以形成在半导体基板110中并可以包括与半导体基板110的半导体材料相同的半导体材料。

57.多个绝缘材料170可以在所述多条位线160之间提供在半导体基板110中。所述多个绝缘材料170可以在第二方向上平行于所述多条位线160延伸,以将半导体基板110内部的所述多条位线160分隔开。绝缘材料170可以包括例如硅氧化物、硅氮化物、铝氧化物、铪氧化物或锆氧化物,但是这仅是示例并可以包括各种其它材料。

58.栅极绝缘层130形成在沟道140的表面上。栅极绝缘层130可以包括例如但不限于硅氧化物、硅氮化物、铝氧化物、铪氧化物或锆氧化物。

59.多条字线150提供在半导体基板110上以在第一方向(例如,x轴方向)上延伸。第一方向可以是与第二方向相交的方向。例如,第一方向可以是垂直于第二方向的方向。然而,本公开不限于此。

60.每条字线150可以被提供为对应于在第一方向上排布的沟道140。具体地,每条字线150可以围绕在第一方向上排布的沟道140。字线150可以用作栅电极。

61.所述多条字线150可以被提供为与提供在所述多条字线150下面的所述多个绝缘材料170交叉。绝缘材料170的顶表面可以与字线150的底表面相邻。绝缘材料170的上部可以从字线150的底部突出。然而,本公开不限于此。

62.字线150可以包括导电材料。例如,字线150可以包括金属、半导体和合金中的至少一种。金属的示例可以包括铝(al)、钨(w)、钼(mo)、钛(ti)和钽(ta)。半导体的示例可以包括iv族半导体材料、iii-v族半导体材料、氧化物半导体、氮化物半导体和氮氧化物半导体。本公开不限于此。

63.二维(2d)材料层190提供在字线150的底表面上。具体地,2d材料层190提供在字线150的与绝缘材料170的顶表面接触的底表面上。

64.2d材料层190包括具有2d晶体结构的2d材料。2d材料可以具有单层或多层结构,并且构成2d材料的层中的每个可以具有原子级厚度。

65.2d材料层190可以包括导体、绝缘体或半导体。2d材料层190可以包括石墨烯。石墨烯是指包含布置成2d六边形蜂窝结构的碳原子的材料。石墨烯可以包括具有在从约1nm至约100nm的范围内的尺寸的晶粒。然而,本公开不限于此,石墨烯可以包括具有大于100nm的尺寸的晶粒。

66.2d材料层190可以包括过渡金属二硫属化物(tmd)。tmd是具有半导体特性的二维材料并且是过渡金属和硫属元素的化合物。过渡金属的示例可以包括但不限于钼(mo)、钨(w)、铌(nb)、钒(v)、钽(ta)、钛(ti)、锆(zr)、铪(hf)、钴(co)、锝(tc)和铼(re)。此外,硫属元素的示例可以包括但不限于硫(s)、硒(se)和碲(te)。具体地,tmd可以包括选自由mos2、mose2、mote2、ws2、wse2、wte2、zrs2、zrse2、hfs2、hfse2、nbse2、rese2、pts2、ptse2、pdse2、pdte2、vs2、vse2、fese2和fete2组成的组中的至少一种。

67.2d材料层190可以包括六方氮化硼(h-bn)或非晶氮化硼(a-bn)。2d材料层可以包括各种其它2d材料(诸如gase、gate2、snse、bi2se3、bi2o2se、硅烯、锡烯、碲烯、硼烯或锑烯)中的任一种。

68.在本实施方式中,当形成用作栅电极的字线150时,提供在字线150的底表面上的2d材料层190可以用作用于引导晶粒生长的衬垫。因此,通过使用2d材料层190生长的字线150可以包括具有大尺寸的晶粒以形成低电阻布线。由于字线150的低电阻特性,电阻-电容(rc)延迟也可以被减小。

69.图4示出根据另一实施方式的vcat结构200。下面将集中在与上述实施方式的差异上。

70.参照图4,2d材料层290提供在字线150的底表面上。具体地,2d材料层290提供在字线150的与绝缘材料170的顶表面接触的底表面上和在字线150的位于突出的绝缘材料170的两侧的底表面上。

71.图5示出根据另一实施方式的vcat结构300。

72.参照图5,2d材料层390提供在字线150的底表面上。具体地,2d材料层390提供在字线150的与绝缘材料170的顶表面接触的底表面上和在字线150的与绝缘材料170的突出的侧表面接触的底表面上。

73.图6示出根据另一实施方式的vcat结构400。

74.参照图6,2d材料层490提供在字线150的底表面和侧表面上。具体地,2d材料层490

从字线150的底表面延伸到侧表面。

75.图7示出根据另一实施方式的vcat结构500。

76.参照图7,vcat结构500包括半导体基板110和在半导体基板110上布置成阵列的所述多个沟道140。所述多个沟道140中的每个可以从半导体基板110垂直地延伸。

77.源极s和漏极d分别提供在每个沟道140的下部和上部上。栅极绝缘层130形成在沟道140的表面上。所述多条字线150提供在半导体基板110上以在第一方向(例如,x轴方向)上延伸。字线150被提供为分别对应于在第一方向上排布的沟道140。

78.源极s在半导体基板110的顶表面周围提供成阵列以对应于沟道140,并且所述多条位线160提供在源极s下面以在第二方向(例如,y轴方向)上延伸。每条位线160可以电连接在第二方向上排布的源极s。

79.所述多个绝缘材料170可以在所述多条位线160之间提供在半导体基板110中。所述多条字线150可以位于所述多个绝缘材料170之上。绝缘材料170的上部可以从字线150的底部突出。然而,本公开不限于此。

80.2d材料层590提供在字线150的顶表面上。2d材料层590可以包括导体、绝缘体或半导体。例如,2d材料层590可以包括选自由石墨烯、tmd、h-bn、a-bn、gase、gate2、snse、bi2se3、bi2o2se、硅烯、锡烯、碲烯、硼烯和锑烯组成的组中的至少一种。tmd可以包括选自由mos2、mose2、mote2、ws2、wse2、wte2、zrs2、zrse2、hfs2、hfse2、nbse2、rese2、pts2、ptse2、pdse2、pdte2、vs2、vse2、fese2和fete2组成的组中的至少一种。

81.在本实施方式中,提供在字线150的顶表面上的2d材料层590可以用作用于保护字线150的顶表面的阻挡层。具体地,提供在字线150的顶表面上的2d材料层590可以在通过成角度的离子注入工艺形成漏极d的工艺中防止对字线150的顶表面的损坏,并可以通过字线150的表面散射减少来保持低电阻特性。

82.提供在字线150的顶表面上的2d材料层590可以减少字线150的表面的氧化,并可以减少在后续工艺中对字线150的表面的损坏。

83.提供在字线150的顶表面上的2d材料层590可以通过形成石墨烯/金属结构来调节功函数,因此可以减少栅极感应漏极泄漏(gidl)。

84.表1示出金属的功函数和石墨烯/金属结构的功函数。

85.[表1]

[0086]

金属金属功函数(ev)石墨烯/金属功函数(ev)w4.803.91mo4.613.87ru5.033.90tin3.034.04

[0087]

图8示出根据另一实施方式的vcat结构600。

[0088]

参照图8,vcat结构600包括半导体基板110和在半导体基板110上布置成阵列的所述多个沟道140。所述多个沟道140中的每个可以从半导体基板110垂直地延伸。

[0089]

源极s和漏极d分别提供在每个沟道140的下部和上部上。栅极绝缘层130形成在沟道140的表面上。所述多条字线150提供在半导体基板110上以在第一方向(例如,x轴方向)上延伸。字线150被提供为分别对应于在第一方向上排布的沟道140。

[0090]

源极s在半导体基板110的顶表面附近提供成阵列以对应于沟道140,并且所述多条位线160提供在源极s下面以在第二方向(例如,y轴方向)上延伸。每条位线160可以电连接在第二方向上排布的源极s。

[0091]

所述多个绝缘材料170可以在所述多条位线160之间提供在半导体基板110中。所述多条字线150可以位于所述多个绝缘材料170之上。绝缘材料170的上部可以从字线150的底部突出。然而,本公开不限于此。

[0092]

第一2d材料层691提供在字线150的底表面上,第二2d材料层692提供在字线150的顶表面上。

[0093]

在图8中,第一2d材料层691提供在字线150的与绝缘材料170的顶表面接触的底表面上。然而,本实施方式不限于此,第一2d材料层691可以提供在字线150的与绝缘材料170的顶表面接触的底表面上和在字线150的位于突出的绝缘材料170的两侧的底表面上,如图4所示。第一2d材料层691可以提供在字线150的与绝缘材料170的顶表面接触的底表面上和在字线150的与绝缘材料170的突出的侧表面接触的底表面上,如图5所示。第一2d材料层691可以从字线150的底表面延伸到侧表面,如图6所示。

[0094]

第一2d材料层691和第二2d材料层692中的每个可以包括导体、绝缘体或半导体。例如,第一2d材料层691和第二2d材料层692中的每个可以包括选自由石墨烯、tmd、h-bn、a-bn、gase、gate2、snse、bi2se3、bi2o2se、硅烯、锡烯、碲烯、硼烯和锑烯组成的组中的至少一种。tmd可以包括选自由mos2、mose2、mote2、ws2、wse2、wte2、zrs2、zrse2、hfs2、hfse2、nbse2、rese2、pts2、ptse2、pdse2、pdte2、vs2、vse2、fese2和fete2组成的组中的至少一种。第一2d材料层691和第二2d材料层692可以包括相同的材料。然而,本公开不限于此,第一2d材料层691和第二2d材料层692可以包括不同的材料。

[0095]

如上所述,提供在字线150的底表面上的第一2d材料层691可以用于生长包括大晶粒的字线150,以形成低电阻布线。此外,提供在字线150的顶表面上的第二2d材料层692可以用作用于保护字线150的顶表面的阻挡层。第二2d材料层692可以调节字线150的功函数(即栅极的功函数),因此可以减少gidl。

[0096]

图9示出根据另一实施方式的vcat结构700。

[0097]

在以上实施方式中,字线150具有包括一种材料的单层结构。在本实施方式中,字线750具有其中堆叠不同材料的多层结构。在图9中,依次堆叠包括不同材料的三个层,也就是,第一层m1、第二层m2和第三层m3。第一层m1、第二层m2和第三层m3中的每个可以独立地包括金属、半导体和合金中的至少一种。构成字线750的层的数量可以以各种方式改变。

[0098]

在图9中,2d材料层790仅提供在字线750的底表面上。然而,这仅是示例,2d材料层790可以从字线750的底表面延伸到侧表面。此外,2d材料层790可以提供在字线750的顶表面上,或者可以提供在字线750的顶表面和底表面上。

[0099]

上述dram器件可以用于在各种电子装置中临时存储数据。图10和图11是示出根据实施方式的可应用于电子装置的装置架构的概念图。

[0100]

参照图10,装置架构1000可以包括存储单元1010、算术逻辑单元(alu)1020和控制单元1030。存储单元1010、alu 1020和控制单元1030可以彼此电连接。例如,装置架构1000可以被实现为包括存储单元1010、alu 1020和控制单元1030的一个芯片。具体地,存储单元1010、alu 1020和控制单元1030可以通过芯片上的金属线互连并可以直接相互通信。存储

单元1010、alu 1020和控制单元1030可以单片地集成在一个基板上以形成一个芯片。输入/输出装置2000可以连接到装置架构1000。此外,存储单元1010可以包括主存储器和高速缓冲存储器两者。主存储器可以包括上述dram器件。装置架构1000可以是片上存储器处理单元。

[0101]

参照图11,高速缓冲存储器1510、alu 1520和控制单元1530可以构成中央处理单元(cpu)1500,并且高速缓冲存储器1510可以包括静态随机存取存储器(sram)。除了cpu 1500之外,还可以提供主存储器1600和辅助存储器1700。主存储器1600可以包括上述dram器件。必要时,装置架构可以被实现为使得计算单元器件和存储单元器件在一个芯片中彼此相邻,而不在子单元之间进行区分。输入/输出装置2500(例如,键盘)可以连接到中央处理单元(cpu)1500。

[0102]

图12是根据一实施方式的存储器系统的示意图。

[0103]

参照图12,存储器系统5000可以包括电子装置4000,电子装置4000可以包括中央处理单元1500和用于存储数据的主存储器1600。中央处理单元1500可以响应于主机1800的读取和写入请求从主存储器1600读取数据和将数据写入主存储器1600中。中央处理单元1500可以制作地址映射表,用于将从主机1800(例如,移动装置或计算机系统)提供的地址映射到主存储器1600的物理地址。中央处理单元1500可以用如下实现:处理电路,诸如包括逻辑电路的硬件;硬件/软件组合,诸如执行软件的处理器;或其组合。例如,处理电路更具体地可以包括但不限于中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。主存储器1600可以包括多个存储单元mc。

[0104]

参照图2至图9和图12,每个存储单元mc可以包括连接到晶体管tr的电容器c,并可以具有包括上述vcat结构100、200、300、400、500、600和700中的任一个的特征的结构。图12中的晶体管tr可以提供在图2至图9和图12中的字线150(wl)之一和位线160(bl)之一之间的交叉点处,图12中的电容器c可以包括图2中的电容器3500,该电容器3500连接到图2至图9中的提供在沟道140的上部上的漏极d。

[0105]

根据实施方式,由于2d材料层提供在字线的底表面上使得字线具有大晶粒,所以栅极线可以形成为低电阻布线并且rc延迟可以由于低电阻特性而减小。

[0106]

此外,由于2d材料层提供在字线的顶表面上,所以可以保护字线的顶表面。2d材料层可以在通过成角度的离子注入工艺形成漏极d的工艺中防止对字线的顶表面的损坏。可以减少字线表面的氧化,并且可以减少在后续工艺中对字线表面的损坏。提供在字线的顶表面上的2d材料层可以通过调节字线的功函数来降低gidl。尽管以上已经描述了实施方式,但是这些仅是示例,并且本领域普通技术人员将理解,在不背离本公开的范围的情况下可以在其中进行各种修改。

[0107]

以上公开的元件中的一个或更多个可以包括或被实现为:处理电路,诸如包括逻辑电路的硬件;硬件/软件组合,诸如执行软件的处理器;或其组合。例如,处理电路更具体地可以包括但不限于中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微型计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

[0108]

应当理解,这里描述的实施方式应当仅以描述性的含义来考虑,而不是为了限制

的目的。对每个实施方式内的特征或方面的描述通常应当被认为可用于其它实施方式中的其它类似特征或方面。尽管已经参照附图描述了一个或更多个实施方式,但是本领域普通技术人员将理解,在不背离由所附权利要求限定的精神和范围的情况下,可以在其中进行在形式和细节上的各种改变。

[0109]

本技术基于2021年9月8日在韩国知识产权局提交的韩国专利申请第10-2021-0119860号并要求其优先权,其公开内容通过引用整体地结合于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1