内窥镜系统的制作方法

1.本公开涉及一种内窥镜系统。

背景技术:

2.通常,内窥镜系统由内窥镜装置(镜体)和连接内窥镜装置的处理器构成。例如,近年来,已经开始尝试,按照mipi d-phy信号传输标准,将使用摄像单元(图像传感器)拍摄的内窥镜图像传输到处理器。

3.然而,由于mipi d-phy是针对数10cm的传输距离而确定的标准,因此,并不保证经由内窥镜镜体的插入部从摄像单元到处理器的长传输距离。因此,例如,开发出如专利文献1所公开的技术,其中,在内窥镜装置的插入部或操作部中布置中继基板,将mipi d-phy信号转换成速度更快的信号,以便实现至处理器的长距离信号传输。

4.现有技术文献

5.专利文献

6.专利文献1专利第5861071号公报

技术实现要素:

7.发明所要解决的课题

8.然而,由于内窥镜装置的插入部需要弯曲,因此,在空间上也希望避免配置中继基板。再加上操作部还配置有各种管路等,因此在结构上难以配置中继基板。

9.鉴于这样的限制,最希望的是mipi d-phy信号按原样传输并由处理器处理。在这方面,如上所述,当直接通过mipi d-phy发送信号时,信号由于长距离的传输而衰减,并且处理器不能适当地处理内窥镜图像。

10.有鉴于此,本公开提供了一种技术,能够对按照mipi d-phy标准从摄像单元输出的视频信号(内窥镜图像)不经转换即进行处理。

11.用于解决课题的技术方案

12.内窥镜端连接器部为了解决上述问题,本实施方式提供了一种内窥镜系统,具备:内窥镜装置,其具有内窥镜端连接器部;处理器,其具有处理器端连接器部;以及衰减校正部,其校正配置在内窥镜装置前端部的摄像元件的图像信号的衰减。

13.通过说明书和附图可以看出与本公开内容有关的进一步特征。此外,本公开也是通过要素和各种要素的组合,以及通过详细的后述和所附的权利要求达成和实现的。

14.应当理解的是,本说明书的描述仅是示例性的,并不旨在以任何方式限制权利要求或实施例。

15.发明效果

16.根据本发明,能够对按照mipi d-phy标准从摄像单元输出的视频信号(内窥镜图像)不经转换即进行处理。

附图说明

17.图1是本实施方式的内窥镜系统的整体外观结构示例图。

18.图2是本实施方式的内窥镜系统的内部构成概要示例图。

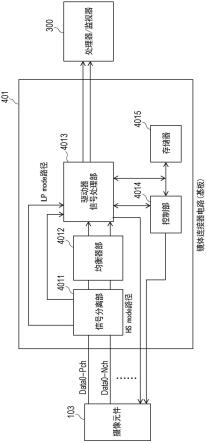

19.图3是具备镜体连接器400的镜体连接器电路401的内部构成示例。

20.图4是镜体连接器电路401处理的信号示例图。图4的a示出了摄像单元103的输出信号(mipi d-phy信号:影像信号)的示例。图4的b示出了通过信号线传输并输入到镜体连接器电路401的信号(分离前)的示例。图4的c示出了分离后的信号(lpmode信号)的示例。图4的d示出了分离后的信号(hsmode信号)经均衡器处理的信号的示例。

21.图5是信号分离部4011的内部构成示例1的图。

22.图6是信号分离部4011的内部构成示例2的图。

23.图7是信号分离部4011的内部构成示例3的图。

24.图8是信号分离部4011的内部构成示例4的图。

25.图9是信号分离部4011的内部构成示例4中,晶体管801和802,以及fet803和804的详细构成图。

具体实施方式

26.下面,将参照附图对本公开的实施方式进行说明。另外,以下,作为本公开的一个实施方式,以内窥镜系统为例进行说明。

27.内窥镜系统的观察对象部位,可以例举出呼吸器官等、消化器官等。呼吸器官等可以例举出肺、支气管和耳鼻喉。消化器官等可以例举大肠、小肠、胃、食道、十二指肠、子宫和膀胱等。在观察如上所述的对象部位时,利用强调特定生物结构的图像更有效。

28.《内窥镜系统的构成》

29.图1是本实施方式的内窥镜系统的整体外观示例图,图2是本实施方式的内窥镜系统的内部构成概略图。内窥镜系统1具备内窥镜装置(电子内镜)100,处理器200与监视器300。内窥镜装置100的处理器端部设有一个内镜连接器(以下简称"连接器")400,它包括与本实施方式的特征有关的连接器电路。

30.内窥镜装置100具备插入受检体内部的细长管状插入部11。内窥镜装置100具备:lcb(light carrying bundle)101,其用于引导来自后述光源201的照射光;配光透镜102,其设于lcb101的输出端;摄像单元103,其通过物镜(未图示)接收来自被照射部分(观察部位)的返回光;驱动摄像单元103的驱动信号处理电路105;以及第1存储器106。

31.来自光源装置201的照射光入射到lcb101内,通过在lcb101内反复进行全反射而传播。在lcb101内传播的照射光从配置在插入部11的前端部12内的lcb101的出射端射出,经由配光透镜102照射观察部位。从被照射部分返回的光经由物镜通过摄像单元103的受光面上的各像素结成光学像。

32.摄像单元103位于插入部11的前端部12内,例如,是一个ccd(电荷耦合器件)图像传感器。摄像单元103将受光面的各像素结成的光学图像(来自活组织的回光)累积为与光强度相对应的电荷,并产生和输出r、g、b图像信号。另外,摄像单元103并不限于ccd图像传感器,还可以替换成cmos(互补性氧化金属半导体)图像传感器或其他类型的摄像装置。从摄像单元103输出的信号由设置在镜体连接器400中的镜体连接器电路401来处理,如下所

述。

33.处理器200是一个一体化装置,具备对来自内窥镜装置100的信号进行处理的信号处理装置,和通过内窥镜装置100照亮自然光无法到达的体腔内部的光源装置。在其他实施方式中,可以分开配置信号处理装置和光源装置。处理器200具备光源装置201、系统控制器202、光学滤波器203、光学滤波器驱动器204、前级信号处理电路205、颜色转换电路206、后级信号处理电路207和第2存储器208。

34.处理器200还可以具备未图示的操作面板。操作面板的构成有各种形态。操作面板的具体构成,可以是例如处理器200的前面所封装的每个功能的硬件键,或触摸板式gui(图形用户界面)、硬件键和gui的组合等。医师能够通过操作面板进行后述的模式切换操作。

35.系统控制器202执行存储在未图示存储器中的各种程序,并且集中控制整个内窥镜系统1。系统控制器202使用控制信号来控制处理器200中各种电路的操作和时间,以便对连接到处理器200的内窥镜装置100进行适当处理。此外,系统控制器202可以连接上述操作面板。系统控制器202根据医师从操作面板输入的指令,改变内窥镜系统1的各项动作和用于各项动作的参数。

36.作为光源装置201,例如,可以使用高强度的灯,如氙气灯、卤素灯、汞灯、金属卤化物灯或led(发光二极管)。来自光源装置201的照射光是具有主要从可见光区扩展到不可见的红外光区(或至少包括可见光区)的光谱的光。来自光源装置201的照射光入射到光学滤波器203上。

37.内窥镜装置100与处理器200之间的数据通信可以使用有线通信方式或光无线通信方式。

38.如图2所示,内窥镜装置100与处理器200经由镜体连接器400连接。连接器400具备:lcb,其属于从处理器200延续到内窥镜装置100的lcb101的一部分,以及一个镜体连接器电路401。镜体连接器电路401分离了从摄像单元103输出的mipi d-phy信号(视频信号)中包含的lp(低功率)模式信号和hs(高速)模式信号,这将在后面详细描述。并校正内窥镜装置100中由电缆传输引起衰减的视频信号(由均衡器放大和传感器特定的噪声校正),再次将lp(低功率)mode信号和校正后的hs(高速)mode信号复用并提供给处理器200。在本实施方式中,镜体连接器电路401被设置在镜体连接器400内,但该电路不一定要位于镜体连接器400内。例如,也可以在处理器200一侧的连接器中或处理器200内设置相当于镜体连接器电路401的电路。

39.《镜体连接器电路401的内部构成示例》

40.图3是镜体连接器400具备的镜体连接器电路401的内部构成示例。图4是镜体连接器电路401处理的信号示例图。图4的a示出了摄像单元103的输出信号(mipi d-phy信号:影像信号)的示例。图4的b示出了通过信号线传输并输入到镜体连接器电路401的信号(分离前)的示例。图4的c示出了分离后的信号(lpmode信号)的示例。图4的d示出了分离后的信号(hsmode信号)经均衡器处理的信号的示例。

41.镜体连接器电路401具备:信号分离器4011,其将从摄像单元103输出并在信号线中传输过来的mipi d-phy信号分离成lpmode信号和hsmode信号;均衡器4012,其放大分离所得的hsmode信号,并校正丢失的增益;驱动器信号处理部4013,例如,由fpga组成,并校正摄像单元103固有的噪声(点损伤),将lpmode信号和校正后的hsmode信号复用,并将它们输

出到处理器200;控制部4014,为摄像单元103进行暂存器等设置(例如,根据插入内镜的体内明暗程度改变快门速度和增益的设置);以及存储器4015,存储摄像单元103的初始设置和驱动信号处理单元4013的配置数据。此外,来自摄像单元103的视频通道数(通道数)由摄像元件的分辨率决定。此外,由控制部4014执行的处理也可以由驱动器信号处理部4013执行。

42.从摄像单元103输出的信号(mipi d-phy信号)例如,是在lpmode(低功率模式)信号之后,再持续hsmode(高速模式)信号的传输形式。如图4的a所示,lpmode(低功率模式)信号具有大大超过hsmode(高速模式)信号的电平(电压振幅)和更慢的传输速率。因为传输速率慢,所以可以说lpmode(低功率模式)信号与hsmode(高速模式)信号相比,电缆传输引起的信号电平劣化较少。

43.当mipi d-phy信号通过内窥镜装置100的信号线传输时(比mipi d-phy标准推荐的距离要长),lpmode(低功率模式)和hsmode(高速模式)信号会反应迟钝,如图4的b所示。关于lpmode(低功率模式)信号,可以看出,即使有些迟钝,也几乎不受电缆传输的影响,因为信号电平很大,因此大于比较器阈值电平(区分和提取lpmode信号的阈值)。另一方面,关于hsmode(高速模式)信号,由于其自身的信号电平较小,所以因电缆传输而变得迟钝,并且在后一级的处理器中难以进行信号处理。因此,在本实施方式中,均衡器4012放大迟钝的hsmode(高速模式)信号,并且执行电平校正以便不影响后级的信号处理。

44.通过设置适当的比较器阈值电平,如图4的c所示,可以将信号分离部4011分离后得到的lpmode(低功率模式)信号提取为干净的矩形波,即便其由于电缆传输多少有些迟钝(图4的b)。

45.经过信号分离部4011的分离后,由均衡器4012校正处理的hsmode(高速模式)信号在电平上得到校正,如图4的d所示,成为一个清晰的差分信号,如同分离前mipi d-phy信号(图4的a)的hsmode信号部分。

46.《信号分离部4011的内部构成示例》

47.从图5到图9是与信号分离部4011的内部构成示例相关的图。

48.(i)构成示例1

49.根据图5所示的内部构成示例,信号分离部4011包括:与每个视频通道(data0-pch,data0-nch,...,datan-pch,datan-nch)串联的多个电阻lp_501及502;多个比较器503及504,提取大于预定比较器阈值电平的信号(大于阈值的信号为1,小于阈值的信号值为0)并输出;多个电阻hs505及507,其与各视频通道并联;以及均衡器506,在电阻hs505和hs507之间与视频通道并联,削减lpmode(低功率模式)信号,校正(放大)因电缆传输而衰减的hsmode(高速模式)信号。

50.电阻lp501及502的电阻值也可以大于电阻hs505及507,例如100ω或更大。通过使lpmode路径的阻抗高于hsmode路径,可以防止hsmode信号传输时的信号质量下降。虽然hs电阻505及507不是必要的构成元件,但其位置可以使均衡器506的输入侧的阻抗与输出侧(驱动器信号处理部(如fpga)4013的输入侧)的阻抗相匹配。

51.比较器503及504的比较器阈值可以根据hsmode的电压振幅来随意(预先)确定。例如,可以是220mv、385mv或550mv。比较器阈值以上的信号作为lpmode信号被提取,如图4的c这样的脉冲信号被提供给驱动器信号处理部4013。

52.(ii)构成示例2

53.根据图6所示的内部构成示例,信号分离部4011具备:比较器503及504,其与每个视频通道(data0-pch,data0-nch,...,datan-pch,datan-nch)串联,并提取高于规定的比较器阈值电平的信号(大于阈值的信号为1,小于阈值的信号值为0)并输出;多个开关601及602,其与每个视频通道串联,由比较器503及504的输出驱动;多个电阻hs505及507,其与开关601及602并联;以及均衡器506,在电阻hs505和hs507之间与视频通道并联,校正(放大)因电缆传输而衰减的hsmode(高速模式)信号。

54.开关601及602被控制成,在比较器503及504完成lpmode信号的提取之后,在图4的c的lpmode信号的下降时开启。当开关601及602处于on状态时,将信号(对应于图4的b中的hsmode信号的部分)提供给均衡器,并且校正(放大)衰减。

55.另外,关于比较器阈值和电阻hs505以及507,如构成示例1所述。

56.(iii)构成示例3

57.根据图7所示的内部构成示例,信号分离部4011具备:多个lpmode用开关sw_lp701及702,其与每个视频通道(data0-pch,data0-nch,...,datan-pch,datan-nch)串联;多个比较器503及504,其提取大于预定比较器阈值电平的信号(大于阈值的信号为1,小于阈值的信号值为0)并输出;hsmode用开关sw_hs703及704,其与各视频通道串联;多个电阻hs505及507,其与sw_hs703及704并联;以及均衡器506,在电阻hs505和hs507之间与视频通道并联,校正(放大)因电缆传输而衰减的hsmode(高速模式)信号。

58.驱动器信号处理部4013(或单独提供的cpu或其他控制单元(未图示))在接收到来自摄像单元103的视频信号时,控制sw_lp701及702为on,sw_hs703及704为off的第一时间(初始运行期),这样所有接收到的视频信号(mipi d-phy信号)都被供应到lp模式路径侧。然后,驱动器信号处理部4013根据在初始运行期获取的视频信号获取lpmode信号的出现时间(出现位置)。由于视频信号(mipi d-phy信号)一个周期的持续时间是预先知道的,因此,在初始运行期之后的运行期,驱动器信号处理部4013控制sw_lp701及702在lp模式信号到达期间为on,sw_hs703及704为off;sw_lp701及702在hs模式信号到达期间为off,sw_hs703及704为on。

59.通过所述开关操作获取的lpmode路径的lpmode信号,由比较器503及504整形,并提供给驱动器信号处理部4013。另一方面,通过所述开关操作获取的hsmode路径的hsmode信号,被均衡器506校正衰减,并被提供给驱动器信号处理部4013。

60.另外,关于比较器阈值和电阻hs505以及507,如构成示例1所述。

61.(iv)构成示例4

62.根据图8所示的内部构成示例,信号分离部4011包括:晶体管801及802(在构成示例3(图7)中用晶体管代替开关sw_lp701和702用于lp模式),其分别与每个视频通道(data0-pch,data0-nch,...,datan-pch,datan-nch)串联;fet803以及804(使用fet代替比较器503及504),其与各晶体管801或802串联;hsmode用开关sw_hs805以及806,其与各视频通道串联;多个电阻hs505以及507,其与sw_hs805以及806并联;以及均衡器506,在电阻hs505和hs507之间与视频通道并联,校正(放大)因电缆传输而衰减的hsmode(高速模式)信号。

63.驱动器信号处理部4013(或单独提供的cpu或其他控制单元(未图示))在收到来自

摄像单元103的视频信号时,在第一时间(初始运行期)将sw_hs805及806控制为off,以便将所有收到的视频信号(mipi d-phy信号)提供给lpmode路径一侧。然后,驱动器信号处理部4013根据在初始运行期获取的视频信号获取lpmode信号的出现时间(出现位置)。由于视频信号(mipi d-phy信号)的一个周期的持续时间是事先知道的,因此,在初始运行期之后的运行期,驱动器信号处理部4013在lp模式信号到达的期间将sw_hs85及806控制为off,在hs模式信号到达的期间将sw_hs805及806控制为on。

64.通过上述开关操作获得的lpmode路径中的lpmode信号由fet803及804整形,并提供给驱动器信号处理部4013。另一方面,通过所述开关操作获取的hsmode路径的hsmode信号,被均衡器506校正衰减,并被提供给驱动器信号处理部4013。

65.另外,关于比较器阈值和电阻hs505以及507,如构成示例1所述。

66.图9显示了构成示例4中晶体管801和802以及fet803和804的详细构成。晶体管801及802与fet803及804的组合能提取lpmode信号(脉冲)。

67.《实施方式的效果》

68.根据本实施方式,在内窥镜装置100的镜体连接器400中提供了一个镜体连接器电路401,以处理来自摄像单元(图像传感器)103的视频信号(基于mipi d-phy标准的信号)。具体来说,镜体连接器电路(衰减校正部)401分离mipi d-phy信号中包含的lpmode和hsmode信号,校正hsmode信号的衰减(由电缆传输引起的衰减),将分离的lpmode信号和带有衰减校正的hsmode信号复用(将信号格式恢复到mipi d-phy标准),并输出到处理器200。通过这种方式,处理器200可以按原样处理mipi d-phy标准信号,而不需要将其转换为其他格式。

69.此外,在本实施方式中,在内窥镜装置(镜体)100的插入部或内窥镜操作部以外的位置,在镜体连接器400内设有衰减校正部(在本实施方式中,设于镜体连接器400中,但也可以设置在其他位置,例如,在处理器侧的连接器中或在处理器200内部),因此,内窥镜装置的插入部或操作部的尺寸不需要增加。

70.《本公开的特定事项》

71.(1)特定事项1

72.一种内窥镜系统,具备:内窥镜装置,其具有内窥镜端连接器部;处理器,其具有处理器端连接器部;以及衰减校正部,其校正来自位于所述内窥镜装置前端部的摄像元件的图像信号的衰减。

73.(2)特定事项2

74.一种内窥镜系统,在特定事项1中,

75.所述衰减校正部设置在所述内窥镜端连接器部内。

76.(3)特定事项3

77.一种内窥镜系统,在特定事项1或2中,

78.所述摄像元件的视频信号包含符合mipi d-phy规格的信号,

79.所述衰减校正部包括:

80.分离部,其将所述视频信号分离成低功率模式信号和高速模式信号;

81.均衡器部,其校正所述高速模式信号的衰减;以及

82.驱动器信号处理部,其将从所述视频信号提取出的低功率模式信号和所述衰减被

校正后的高速模式信号复用而输出到所述处理器。

83.(4)特定事項4

84.一种内窥镜系统,在特定事项3中,

85.所述处理器将所述视频信号处理为mipi d-phy标准信号。

86.(5)特定事项5

87.一种内窥镜系统,在特定事项3或4中,

88.所述分离部包括:第1路径,其处理所述低功率模式信号;以及第2路径,其处理所述高速模式信号,

89.在所述第1路径中,具备:第1种电阻,其与所述摄像元件的信号线串联;以及比较器,其与第1种电阻串联,并从通过第1种电阻的信号中提取预定阈值电平以上的信号,

90.在所述第2路径中,具备均衡器,其与所述摄像元件的信号线并联。

91.(6)特定事项6

92.一种内窥镜系统,在特定事项3或4中,

93.所述分离部包括:第1路径,其处理所述低功率模式信号;以及第2路径,其处理所述高速模式信号,

94.所述第1路径中具备比较器,其与所述摄像元件的信号线串联,从所述视频信号中提取高于预定阈值电平以上的信号,

95.所述第2路径中具备开关,其与所述摄像元件的信号线串联,并在从所述比较器中提取所述低功率模式信号的时点关闭;以及均衡器,其与所述摄像元件的信号线并联。

96.(7)特定事项7

97.一种内窥镜系统,在特定事项3或4中,

98.所述分离部包括:第1路径,其处理所述低功率模式信号;以及第2路径,其处理所述高速模式信号,

99.在所述第1路径中,具备第1种开关,其与所述摄像元件的信号线串联;以及比较器,其与所述摄像元件的信号线串联,从所述视频信号中提取预定阈值电平以上的信号,

100.在所述第2路径中,具备第2种开关,其与所述摄像元件的信号线串联;以及均衡器,其与所述摄像元件的信号线并联,

101.所述驱动器信号处理部控制所述第1种开关为on,所述第2种开关为off,以识别来自所述摄像元件输入的视频信号的所述低功率模式信号的期间和所述高速模式信号的期间,在识别出所述期间后,在所述低功率模式信号期间,所述第1种开关被控制为on,所述第2种开关被控制为off;在所述高速模式信号期间,所述第1种开关被控制为off,所述第2种开关被控制为on。

102.(8)特定事项8

103.一种内窥镜系统,在特定事项3或4中,

104.所述分离部包括:第1路径,其处理所述低功率模式信号;以及第2路径,其处理所述高速模式信号,

105.所述第1路径中具备:晶体,其与所述摄像元件的信号线串联;以及fet,其与所述摄像元件的信号线串联,从所述视频信号中提取预定阈值电平以上的信号,

106.所述第2路径中具备:开关,其与所述摄像元件的信号线串联;以及均衡器,其与所

述摄像元件的信号线并联,

107.所述驱动器信号处理部将所述开关控制在off状态,并从所述摄像元件输入的视频信号中识别出所述低功率模式信号的期间和所述高速模式信号的期间,在识别出所述期间后,所述开关被控制在所述低功率模式信号期间off,在所述高速模式信号期间on。

108.符号说明

[0109]1ꢀꢀꢀꢀ

内窥镜系统

[0110]

100

ꢀꢀ

内窥镜装置

[0111]

110

ꢀꢀ

内窥镜装置的连接器部

[0112]

200

ꢀꢀ

处理器

[0113]

210

ꢀꢀ

处理器的连接器部

[0114]

300

ꢀꢀ

监视器

[0115]

400

ꢀꢀ

镜体连接器

[0116]

401

ꢀꢀ

镜体连接器电路

[0117]

4011 信号分离部

[0118]

4012 均衡器部

[0119]

4013 驱动器信号处理部

[0120]

4014 控制部

[0121]

4015 存储器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1