一种充电桩电磁锁控制电路及方法与流程

1.本发明属于充电桩领域,具体而言,涉及一种充电桩电磁锁控制电路及方法。

背景技术:

2.电磁锁线圈通常采用

±

12v电压来驱动电磁锁的上锁与解锁,如在电磁锁线圈两端el+、el

‑

间施加+12v并保持200ms

‑

500ms以上,电磁锁上锁;施加

‑

12v并保持200ms

‑

500ms以上,电磁锁解锁。另外,一旦电磁锁上锁或解锁成功后希望能够及时移除电磁锁线圈两端施加的+12v或

‑

12v电压,以防止电磁锁线圈过热损坏。

3.目前常用的电磁锁控制电路多采用两个控制信号来驱动el+、el

‑

在+12v和

‑

12v及0v之间切换,如上锁信号触发后将el+、el

‑

被切换到+12v,el

‑

切换到0v,电磁锁上锁,待接收到上锁反馈信号后上锁信号复位,el+被切换到0v,电磁锁进入上锁保持状态。同理接收到解锁信号后el

‑

切换到+12v,电磁锁解锁,待成功接收到解锁反馈信号后el

‑

再次被切到0v实现解锁保持。这种控制方式需要两路控制信号,占用mcu至少2个io口资源。另外这种控制方式也相对复杂:1.每次发出上锁或解锁控制信号后,必须在成功接收到反馈信号状态后将上锁或解锁信号复位,一旦反馈信号异常可能会导致上锁或解锁信号持续存在从而烧坏电磁锁,当然可以通过限制上锁或解锁控制信号的持续时间,但这必然又需要占用cpu资源。2.一旦上锁或解锁过程中程序跑飞,电磁锁驱动信号无法及时移除,存在将电磁锁烧坏风险。3.上锁和解锁信号独立,电磁锁有接收到矛盾指令的风险。

技术实现要素:

4.本技术实施例提供了一种充电桩电磁锁控制电路及方法,将上锁和解锁信号分别用高低电平信号来实现;上锁或解锁驱动信号触发后保持至另一信号触发,而电磁锁线圈驱动电压则持续一段时间后自动解除,无需额外控制。

5.第一方面,本技术实施例提供了一种充电桩电磁锁控制电路,包括:

6.滤波电路、比较器、延迟电路和推挽电路;所述滤波电路与比较器连接,用于将过滤后的控制信号输出给比较器;所述比较器与延迟电路和推挽电路连接,用于将控制信号与参考信号进行比较,根据比较结果,控制输出电压;所述延迟电路用于延迟预设时间后,将输出的电压拉低。

7.其中,所述控制信号为高电平或者低电平。

8.其中,所述滤波电路包括:电阻r2一端为控制信号输入端,电阻r2的另一端与第一比较器的同相输入端连接,电阻r4一端为参考信号输入端,电阻r4的另一端与第一比较器的反向输入端连接;电阻r9一端为控制信号输入端,电阻r9的另一端与第二比较器的反相输入端连接,电阻r7一端为参考信号输入端,电阻r7的另一端与第二比较器的同向输入端连接。

9.其中,所述延迟电路包括:

10.电阻r5的一端与第一比较器的输出端连接,电阻r5的另一端与电容ec1的正极、二

极管d1的阴极连接,电容ec1的负极与信号地连接,二极管d1的阳极与三极管q3的基极连接,三极管q3的发射极与信号地连接,三极管q3的集电极与推挽电路连接;

11.电阻r10的一端与第二比较器的输出端连接,电阻r10的另一端与电容ec2的正极、二极管d2的阴极连接,电容ec2的负极与信号地连接,二极管d2的阳极与三极管q6的基极连接,三极管q6的发射极与信号地连接,三极管q6的集电极与推挽电路连接。

12.其中,所述推挽电路包括:

13.三极管q1的集电极接12v电压,三极管q1的基极与三极管q3的集电极、三极管q2基极连接,三极管q2的集电极与信号地连接,三极管q2的发射极与三极管q1的发射极、输出端a连接;

14.三极管q4的集电极接12v电压,三极管q4的基极与三极管q6的集电极、三极管q5的基极连接,三极管q5的集电极与信号地连接,三极管q4的发射极与三极管q5的发射极、输出端b连接。

15.其中,还包括:电阻r3的一端与三极管q3的集电极、第一比较器的输出端连接。

16.其中,还包括:电阻r8的一端与三极管q6的集电极、第二比较器的输出端连接。

17.其中,还包括:

18.电阻r1的一端接12v电压,电阻r1的另一端与第一比较器的输出端连接;电阻r6的一端接12v电压,电阻r6的另一端与第二比较器的输出端连接。

19.第二方面,本技术提供了一种充电桩电磁锁控制方法,包括:

20.滤波电路对控制信号进行过滤,将过滤后的控制信号输出给比较器;

21.所述比较器将控制信号与参考信号进行比较,根据比较结果,控制输出电压;

22.延迟电路延迟预设时间后,将输出的电压拉低。

23.其中,所述控制信号为高电平或者低电平。。

24.本技术实施例充电桩电磁锁控制电路及方法具有如下有益效果:

25.本技术充电桩电磁锁控制电路包括:滤波电路、比较器、延迟电路和推挽电路;滤波电路与比较器连接,用于将过滤后的控制信号输出给比较器;比较器与延迟电路和推挽电路连接,用于将控制信号与参考信号进行比较,根据比较结果,控制输出电压;延迟电路用于延迟预设时间后,将输出的电压拉低。本发明只采用一个io口即可实现电磁锁的上锁和解锁控制,节省了io口资源,且控制过程中不需要额外的cpu监控,减轻了cpu的负担。io口的输出只有1或0状态,因此电磁锁不会接收到矛盾的控制指令。另外本方案无需增加额外的硬件成本。

附图说明

26.图1为本技术实施例充电桩电磁锁控制电路结构示意图;

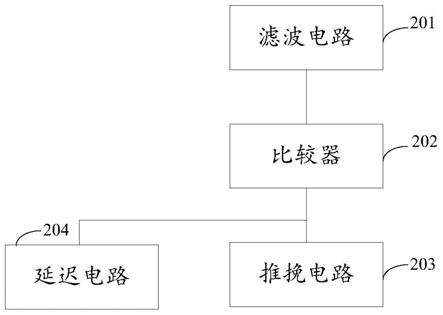

27.图2为本技术实施例充电桩电磁锁控制电路另一种结构示意图。

具体实施方式

28.下面结合附图和实施例对本技术进行进一步的介绍。

29.在下述介绍中,术语“第一”、“第二”仅为用于描述的目的,而不能理解为指示或暗示相对重要性。下述介绍提供了本发明的多个实施例,不同实施例之间可以替换或者合并

组合,因此本技术也可认为包含所记载的相同和/或不同实施例的所有可能组合。因而,如果一个实施例包含特征a、b、c,另一个实施例包含特征b、d,那么本技术也应视为包括含有a、b、c、d的一个或多个所有其他可能的组合的实施例,尽管该实施例可能并未在以下内容中有明确的文字记载。

30.下面的描述提供了示例,并且不对权利要求书中阐述的范围、适用性或示例进行限制。可以在不脱离本技术内容的范围的情况下,对描述的元素的功能和布置做出改变。各个示例可以适当省略、替代或添加各种过程或组件。例如所描述的方法可以以所描述的顺序不同的顺序来执行,并且可以添加、省略或组合各种步骤。此外,可以将关于一些示例描述的特征组合到其他示例中。

31.如图1所示,本技术充电桩电磁锁控制电路包括:滤波电路201、比较器202、延迟电路204和推挽电路203;滤波电路201与比较器202连接,用于将过滤后的控制信号输出给比较器202;比较器202与延迟电路204和推挽电路203连接,用于将控制信号与参考信号进行比较,根据比较结果,控制输出电压;延迟电路204用于延迟预设时间后,将输出的电压拉低。其中,控制信号为高电平或者低电平。

32.电磁锁其实就两种状态:上锁和解锁。因此完全可以用高低电平来控制,如高电平控制上锁,低电平控制解锁,因此只需要一个io口即可实现。比如上锁信号触发,即控制信号为高电平,则驱动控制电路内部比较电路输出高电平并控制a端输出高电平将电磁锁线圈el+端切换到+12v,同时比较电路输出的高电平信号驱动一个延迟的反相电路,待延迟时间到达后将a端电压拉低,线圈el+端再次切换到0v,即电磁锁处于上锁保持状态。反之如果解锁信号触发,则驱动控制电路接收到低电平信号后驱动控制内部的另一比较电路输出高电平控制b端输出高电平将电磁锁线圈el

‑

端切换到+12v,同时该比较电路输出的高电平信号也驱动另外一个延迟的反相电路,待延迟时间到达后将b端拉低,线圈el

‑

切换到0v,即电磁锁处于解锁保持状态。

33.如图2所示,本技术中,滤波电路包括:电阻r2一端为控制信号输入端,电阻r2的另一端与第一比较器的同相输入端连接,电阻r4一端为参考信号输入端,电阻r4的另一端与第一比较器的反向输入端连接;电阻r9一端为控制信号输入端,电阻r9的另一端与第二比较器的反相输入端连接,电阻r7一端为参考信号输入端,电阻r7的另一端与第二比较器的同向输入端连接。r2、r4、r7、r9为滤波电阻,增加了电路的抗干扰能力。

34.延迟电路包括:电阻r5的一端与第一比较器的输出端连接,电阻r5的另一端与电容ec1的正极、二极管d1的阴极连接,电容ec1的负极与信号地连接,二极管d1的阳极与三极管q3的基极连接,三极管q3的发射极与信号地连接,三极管q3的集电极与推挽电路连接;电阻r10的一端与第二比较器的输出端连接,电阻r10的另一端与电容ec2的正极、二极管d2的阴极连接,电容ec2的负极与信号地连接,二极管d2的阳极与三极管q6的基极连接,三极管q6的发射极与信号地连接,三极管q6的集电极与推挽电路连接。

35.推挽电路包括:三极管q1的集电极接12v电压,三极管q1的基极与三极管q3的集电极、三极管q2基极连接,三极管q2的集电极与信号地连接,三极管q2的发射极与三极管q1的发射极、输出端a连接;三极管q4的集电极接12v电压,三极管q4的基极与三极管q6的集电极、三极管q5的基极连接,三极管q5的集电极与信号地连接,三极管q4的发射极与三极管q5的发射极、输出端b连接。

36.如图2所示,本技术充电桩电磁锁控制电路还包括:电阻r3的一端与三极管q3的集电极、第一比较器的输出端连接。电阻r8的一端与三极管q6的集电极、第二比较器的输出端连接。电阻r1的一端接12v电压,电阻r1的另一端与第一比较器的输出端连接;电阻r6的一端接12v电压,电阻r6的另一端与第二比较器的输出端连接。

37.本发明只采用一个io口即可实现电磁锁的上锁和解锁控制,节省了io口资源,且控制过程中不需要额外的cpu监控,减轻了cpu的负担。io口的输出只有1或0状态,因此电磁锁不会接收到矛盾的控制指令。另外本方案无需增加额外的硬件成本。

38.如图2所示,假设control(控制)信号高电平为+12v,低电平为0v,且r5远大于r1,r10远大于r6,vref为5v。

39.当控制电路接收到的control信号为高电平时,u1a输出高电平,对应推挽电路输出也为高电平即a端输出为+12v,此时u1b输出低电平,对应推挽电路输出也为低电平即b端输出为0v。此时施加到电磁锁线圈el+(接a端)、el

‑

(接b端)两端的电压为+12v,电磁锁进入上锁状态。u1a输出的高电平同时经过rc电路后驱动三极管q3,只要合理的选择r5和ec1的参数,从而保证在合理的时间范围内ec1的电压被充到高于二极管d1的钳位电压时q3便导通,从而将三极管q1和q2组成的推挽电路输入拉低,则输出a也同时被拉低。此时电磁锁线圈el+、el

‑

两端的电压为0v。

40.当控制电路接收到的control信号为低电平时,u1b输出高电平,即b端输出+12v,此时u1a输出低电平,a端输出0v,b端输出+12v。这时施加在电磁锁线圈el+、el

‑

两端的电压为

‑

12v,电磁锁进入解锁转态。u1b输出的高电平同时经过rc电路后驱动三极管q6,只要合理的选择r10和ec2的参数,从而保证在合理的时间范围内电容ec2的电压被充到高于二极管d2的钳位电压时三极管q6便导通,则输出b也同时被拉低。此时电磁锁线圈el+、el

‑

两端的电压为0v。

41.比较器将control信号与参考信号vref进行比较,如果control信号大于参考信号vref,u1a输出高,u1b输出低,反之u1a输出低,u1b输出高。

42.本技术还提供了一种充电桩电磁锁控制方法,包括:滤波电路对控制信号进行过滤,将过滤后的控制信号输出给比较器;比较器将控制信号与参考信号进行比较,根据比较结果,控制输出电压;延迟电路延迟预设时间后,将输出的电压拉低。其中,控制信号为高电平或者低电平。

43.本技术中,充电桩电磁锁控制方法实施例与充电桩电磁锁控制电路实施例基本相似,相关之处请参考充电桩电磁锁控制电路实施例的介绍。

44.本技术还提供了一种充电桩电磁锁,包括上述任一种充电桩电磁锁控制电路。

45.本技术还提供了一种充电桩,包括上述任一种充电桩电磁锁控制电路。

46.本领域的技术人员可以清楚地了解到本发明实施例的技术方案可借助软件和/或硬件来实现。本说明书中的“单元”和“模块”是指能够独立完成或与其他部件配合完成特定功能的软件和/或硬件,其中硬件例如可以是fpga(field-programmable gate array,现场可编程门阵列)、ic(integrated circuit,集成电路)等。

47.在本技术所提供的几个实施例中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或

可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的各组成部分相互之间的耦合、或直接耦合、或通信连接可以是通过一些接口,设备或单元的间接耦合或通信连接,可以是电性的、机械的或其它形式的。

48.在本发明各实施例中的各功能单元可以全部集成在一个处理单元中,也可以是各单元分别单独作为一个单元,也可以两个或两个以上单元集成在一个单元中;上述集成的单元既可以采用硬件的形式实现,也可以采用硬件加软件功能单元的形式实现。

49.以上介绍仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1