显示装置和制造显示装置的方法与流程

显示装置和制造显示装置的方法

1.相关申请的交叉引用

2.于2014年8月6日提交的、题为“显示装置与制造显示装置的方法

”ꢀ

的第10

‑

2014

‑

0101136号韩国专利申请通过引用全部并入本文。

技术领域

3.本文中描述的一个或多个实施方式涉及显示装置以及用于制造显示 装置的方法。

背景技术:

4.已经研发出了液晶显示器、有机发光二极管显示器、电泳显示器以 及其他类型的平板显示器。这些显示器具有面板,其中面板具有与数据 线和扫描线耦接的像素。操作中,驱动电路向扫描线供给扫描信号并向 数据线供给数据信号。数据线、扫描线以及像素可设置在显示面板的阵 列衬底上。

5.当制造过程中显示面板被碎片碰撞时,可能在包括阵列衬底的各区 域处形成裂缝。因此,数据线和/或扫描线可能断开,或者数据线和/或扫 描线的电阻可能增加。因此像素可能不准确地发光或者完全不发光。

6.近来,已经研发了柔性显示器。当这种类型的显示器具有微小的裂 缝时,随着显示器被弯曲或者变弯,这些裂缝可能变得更大。通常,这 些微小的裂缝在显示器发放给公众之前未被检测到。因此,像素可能不 发光或者可能不准确地发光。

技术实现要素:

7.根据一个实施方式,显示装置包括:具有与数据线和扫描线的像素 耦接的显示区域;用于接收测试信号的测试焊盘;耦接在显示区域的数 据线与测试焊盘之间的多个第一测试晶体管;以及耦接在第一测试晶体 管中的一个与测试焊盘之间的至少一个轮廓线,该至少一个轮廓线位于 显示区域外部的非显示区域中。该至少一个轮廓线可穿过与显示区域邻 近的路径至少一次。

8.该至少一个轮廓线可通过第一测试晶体管耦接至可与显示区域中 的至少一个绿色像素或绿色子像素耦接的数据线。显示装置可包括电 阻,该电阻位于第一测试晶体管中未与至少一个轮廓线耦接的第一测 试晶体管和测试焊盘之间。电阻可以为电阻器。

9.显示装置可包括:多个数据焊盘;与第一测试晶体管的控制电极耦 接的测试控制焊盘;耦接在显示区域的数据线与数据焊盘之间以接收初 始化信号的多个初始化晶体管;以及与初始化晶体管的控制电极耦接的 多个初始化控制焊盘。测试焊盘、测试控制焊盘、初始化控制焊盘、数 据焊盘、测试晶体管、初始化晶体管以及至少一个轮廓线可位于非显示 区域中。

10.测试控制焊盘可接收测试控制信号,其中该测试控制信号与通过初 始化控制焊盘之一接收的初始化控制信号相反。在测试控制信号被供给 为第一栅极导通电压值的周

期内扫描线可供给有扫描信号,并且扫描信 号可被供给为第二栅极导通电压值。

11.显示装置可包括:与第一测试晶体管的控制电极耦接的多个第一测 试控制焊盘;耦接在显示区域中的数据线与初始化焊盘之间以接收初始 化信号的多个初始化晶体管;与初始化晶体管的控制电极耦接的多个初 始化控制焊盘;耦接在数据线之一与至少一个轮廓线之间的第二测试晶 体管;与第二测试晶体管的控制电极耦接的第二测试控制焊盘;以及与 数据线耦接的多个数据焊盘。

12.第一测试控制焊盘和第二测试控制焊盘可接收测试控制信号,其中 该测试控制信号与通过初始化控制焊盘之一接收的初始化控制信号相 反。在测试控制信号被供给为第一栅极导通电压值的周期内,供给至扫 描线的扫描信号可被供给为第二栅极导通电压值。测试焊盘、第一测试 控制焊盘和第二测试控制焊盘、初始化控制焊盘、数据焊盘、第一测试 晶体管和第二测试晶体管、初始化晶体管以及至少一个轮廓线可位于非 显示区域中。

13.根据另一实施方式,用于制造显示装置的方法包括制造显示装置的 显示面板的阵列衬底;以及检查显示面板的阵列衬底的裂缝。

14.制造操作可包括:在显示面板的阵列衬底上形成数据线;形成与数 据线交叉的扫描线;形成与数据线和扫描线耦接的多个像素;形成测试 焊盘;形成耦接在显示区域的数据线与测试焊盘之间的多个第一测试晶 体管;形成耦接在第一测试晶体管之一与测试焊盘之间的至少一个轮廓 线,该至少一个轮廓线位于非显示区域中;形成与第一测试晶体管的控 制电极耦接的测试控制焊盘;形成数据焊盘;形成耦接在显示区域的数 据线与数据焊盘之间以接收初始化信号的多个初始化晶体管;以及形成 与初始化晶体管的控制电极耦接的多个初始化控制焊盘。

15.检查操作可包括:向测试焊盘供给测试信号,向测试控制焊盘供给 测试控制信号,以及向初始化控制焊盘供给初始化控制信号,其中测试 控制信号与初始化控制信号之一相反。

16.制造操作可包括:在显示面板的阵列衬底上形成多个数据线;形成 与数据线交叉的多个扫描线;形成与数据线和扫描线耦接的多个像素; 形成测试焊盘;形成耦接在显示区域的数据线与测试焊盘之间的多个第 一测试晶体管;形成耦接在第一测试晶体管之一与测试焊盘之间的至少 一个轮廓线,该至少一个轮廓线位于非显示区域中;形成与第一测试晶 体管的控制电极耦接的多个第一测试控制焊盘;形成多个数据焊盘;形 成耦接在显示区域的数据线与数据焊盘之间以接收初始化信号的多个初 始化晶体管;形成与初始化晶体管的控制电极耦接的多个初始化控制焊 盘;形成耦接在数据线与至少一个轮廓线之间的第二测试晶体管;以及 形成与第二测试晶体管的控制电极耦接的第二测试控制焊盘。

17.检查操作可包括:向测试焊盘供给测试信号,向第一测试控制焊盘 和第二测试控制焊盘供给测试控制信号;以及向初始化控制焊盘供给初 始化控制信号,其中测试控制信号与初始化控制信号之一相反。

18.该方法可包括执行模块过程;以及在模块过程之后再检查显示面板 上的裂缝,其中执行模块过程包括附接阵列衬底至显示面板的相反衬底; 附接柔性膜至阵列衬底;附接柔性膜至源极印刷电路板;以及使用柔性 线缆耦接控制印刷电路板与源极印刷电路板。

附图说明

19.通过参照附图对示例性实施方式进行详细描述,对本领域技术人员 而言,各特征将变得清楚,在附图中:

20.图1示出了显示装置的实施方式;

21.图2示出了像素的实施方式;

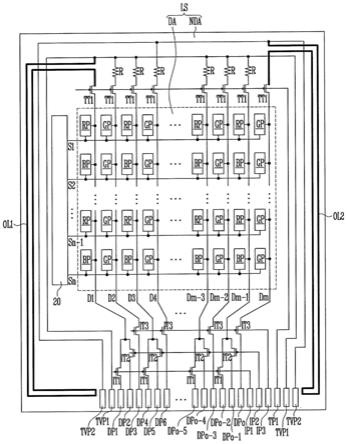

22.图3示出了显示面板的阵列衬底的实施方式;

23.图4示出了用于控制显示面板的信号的示例;

24.图5a

‑

图5c示出了用于控制像素的信号的示例;

25.图6示出了图3中的测试晶体管与轮廓线以及测试晶体管与电阻之 间的耦接结构的实施方式;

26.图7a示出了沿图6中的剖面线i

‑

i’的图,以及图7b示出了沿图6 中的剖面线ii

‑

ii’的图;

27.图8示出了显示面板的阵列衬底的另一实施方式;

28.图9示出了显示面板的阵列衬底的另一实施方式;

29.图10示出了显示面板的下侧的实施方式;

30.图11示出了用于制造显示器的方法的实施方式;以及

31.图12示出了用于制造显示器的方法的另一实施方式。

具体实施方式

32.在下文中将参照附图更充分地描述示例性实施方式;然而,这些示 例性实施方式可以不同的形式实施并且不应解释为受本文中阐述的实施 方式的限制。相反地,提供这些实施方式使得本公开将是详尽且完整的, 并向本领域的技术人员充分地传递示例性实现。

33.为了例示清楚起见,在附图中层和区域的尺寸可能被放大。还应理 解当层或元件被称作在另一层或衬底“上”时,其可直接位于另一层或 衬底上,或者还可存在插入层。此外,应理解当层被称作在另一层“下

”ꢀ

时,其可直接在另一层之下,并且还可存在一个或多个插入层。此外, 还应理解当层被称作在两个层“之间”时,其可以是两个层之间的唯一 层,或者还可存在一个或多个插入层。在整个说明书中相同的附图标记 指代相同的元件。

34.图1示出了包括显示面板10、扫描驱动器20、数据驱动器以及时序 控制器(tc)40的显示装置的实施方式。显示装置可以是有机发光显示 器(oled),或者包括但不限于液晶显示器、场发射显示器或等离子显 示面板的另一类型显示器。

35.数据线d1至dm(m≥2)以及扫描线s1至sn(n≥2)在显示面板 10处相互交叉。布置在矩阵中的像素p位于数据线d1至dm与扫描线 s1至sn的交叉区域。像素p位于显示面板10的显示区域da中。像素 p可以为像素或子像素。在后一种情况中,子像素可发射不同颜色的光。

36.每个像素p耦接至一个扫描线和一个数据线。当扫描信号供给至相 应的扫描线时,每个像素p通过数据线中对应的一个接收数据信号。每 个像素p通过控制流至有机发光二极管的电流而发射具有预定亮度的光。 电流的幅值基于供给的数据信号的电压值。

37.扫描驱动器20从时序控制器40接收扫描时序控制信号scs。扫描 驱动器20根据扫描时序控制信号scs生成扫描信号。扫描驱动器20将 扫描信号供给至扫描线s1至sn。

38.扫描驱动器20定位成与显示区域da的一个或多个侧部相邻。扫描 驱动器20可使用例如非晶硅tft栅极驱动器(asg)方法或面板中栅极 驱动器(gip)方法与数据线d1至dm、扫描线s1至sn以及像素p同 时形成。可替代地,扫描驱动器20可安装在带载封装或柔性膜ff上。 其上安装有扫描驱动器20的带载封装或柔性膜ff可通过带式自动结合 (tab)过程附接至显示面板10的阵列衬底。扫描驱动器20可耦接至 栅极焊盘,栅极焊盘与扫描线s1至sn相耦接。

39.数据驱动器包括至少一个源极驱动ic 30。源极驱动ic 30从时序控 制器40接收数字视频数据信号以及源极时序控制信号。源极驱动ic 30 通过响应于源极时序控制信号而将数字视频数据信号转换成数据信号。 源极驱动ic 30通过与扫描信号中的每个同步而将数据信号供给至数据 线d1至dm。因此,数据信号供给至供给有扫描信号的像素p。

40.源极驱动ic 30可安装在柔性膜ff上,并可附接至显示面板10的阵 列衬底和源极印刷电路板sp。源极驱动ic 30可耦接至与数据线d1至dm耦接的数据焊盘。可替代地,源极驱动ic 30可使用玻璃上芯片过程 或塑料上芯片过程而耦接至数据焊盘并附接至显示面板10的阵列衬底。

41.时序控制器40接收数字视频数据和时序信号。时序信号可包括竖直 同步信号、水平同步信号、数据使能信号、点时钟和/或其他信号。时序 控制器40基于时序信号生成时序控制信号,其中该时序控制信号用于控 制数据驱动器和扫描驱动器20的操作时序。时序控制信号可包括扫描时 序控制信号和数据时序控制信号,其中扫描时序控制信号用于控制扫描 驱动器20的操作时序以及数据时序控制信号用于控制数据驱动器的操作 时序。时序控制器40向扫描驱动器20输出扫描时序控制信号并向数据 驱动器输出数据时序控制信号和数字视频数据。

42.时序控制器40可安装在控制印刷电路板cp上。控制印刷电路板cp 和源极印刷电路板sp可通过柔性线缆fc(如柔性平线缆ffc或柔性印 刷电路fpc)彼此耦接。

43.电力供给源不仅可向扫描驱动器20、数据驱动器以及时序控制器40 供给驱动信号,而且可通过第一电力电压线供给第一电力信号以及通过 第二电力电压线供给第二电力信号。第一电力信号可通过与像素p耦接 的第一电力电压线供给至像素p。第二电力信号可通过与像素p的有机发 光二极管的阴极电极耦接的第二电力电压线供给至像素p。第一电力信号 的电压值可设置为预定(例如,高)电压值并且第二电力信号的电压值 可设置为预定(例如,低)电压值。

44.图2示出了例如可以为图1中的任一像素p的像素的示例。参照图2, 像素p可与第k(1≤k≤n)扫描线sk、第j(1≤j≤m)数据线dj、第 一电力电压线vddl以及第二电力电压线vssl耦接。像素p还可包括 驱动晶体管dt、有机发光二极管oled、扫描晶体管st以及电容器c。

45.驱动晶体管dt位于有机发光二极管oled与第一电力电压线 vddl之间,并控制流至有机发光二极管oled的电流量。因为在驱动 晶体管dt的沟道中流动的电流量可根据供给至驱动晶体管dt的控制电 极的数据信号的电压值而改变,因此可随着供给至驱动晶体管dt的栅极 电极的数据信号的电压值被控制来控制流至有机发光二极管oled的电 流量。

46.驱动晶体管dt的控制电极与扫描晶体管st的第二电极耦接,驱动 晶体管dt的第一电极与第一电力电压线vddl耦接,以及驱动晶体管 dt的第二电极与有机发光二极管

oled的阳极电极耦接。在一个实施方 式中,该控制电极为栅极电极,该第一电极为源极电极或漏极电极,以 及该第二电极为不同于第一电极的电极。例如,当该第一电极为源极电 极时,该第二电极为漏极电极,或者反之亦然。

47.有机发光二极管oled可根据驱动晶体管dt的漏极与源极之间的 电流而发射光。有机发光二极管oled具有与驱动晶体管dt的第二电 极耦接的阳极电极以及与第二电力电压线vssl耦接的阴极电极。

48.扫描晶体管st耦接在驱动晶体管dt的栅极电极与第j数据线dj 之间。扫描晶体管st通过第k扫描线slk的扫描信号而导通,并将第j 数据线dj的数据信号供给至驱动晶体管dt的栅极电极。扫描晶体管st 的栅极电极耦接至第k扫描线slk,扫描晶体管st的第一电极耦接至第 j数据线,以及扫描晶体管st的第二电极耦接至驱动晶体管dt的栅极 电极。

49.电容器c位于驱动晶体管dt的栅极电极与第一电力电压线vddl 之间。电容器c将供给至驱动晶体管dt的栅极电极的数据信号保持一 些时间。

50.驱动晶体管dt和扫描晶体管st的每个半导体层可包括多晶硅、非 晶硅、氧化物半导体或另外的材料。在图3中,驱动晶体管dt和扫描晶 体管st为p型晶体管。在另一实施方式中,可使用n型晶体管。

51.像素p可包括补偿电路,以补偿驱动晶体管dt的阈值电压值。补 偿电路可包括至少一个晶体管,并且可感测驱动晶体管dt的阈值电压值 并将其反映至栅极电极。因此,驱动晶体管dt的漏极与源极之间的电流 ids可以不取决于驱动晶体管dt的阈值电压值vth。在其他实施方式中, 图1中的像素可与图2中的像素具有不同的结构。

52.图3示出了显示面板的阵列衬底的实施方式,该显示面板例如可以 为图1中的显示面板10。参照图3,显示面板10包括阵列衬底ls和相 反的衬底。阵列衬底ls包括显示区域da和非显示区域nda。显示区 域da包括像素rp、gp和bp,其中像素rp、gp和bp用于生成图像 的光。非显示区域nda位于显示区域da外部。

53.阵列衬底ls的显示区域da中的像素rp、gp和bp可在数据线d1 至dm与扫描线s1至sn的交叉区域处布置在矩阵中。像素rp、gp和 bp中的每个与一个扫描线和一个数据线耦接。虽然在图3中红色像素 rp和蓝色像素bp示出为耦接至奇数数据线,以及绿色像素gp示出为 耦接至偶数数据线,但是像素p的耦接布置在其他实施方式中可以不同。

54.数据焊盘dp1至dpo(o>m)、初始化控制焊盘ip1、ip2和ip3、第 一测试控制焊盘tp1、测试焊盘tvp1和tvp2、初始化晶体管it1、it2 和it3、第一测试晶体管tt1、电阻r以及轮廓线ol1和ol2位于阵列 衬底ls的非显示区域nda中。当扫描驱动器20使用asg方法或gip 方法形成时,扫描驱动器20可位于与显示区域da的一侧相邻的非显示 区域中。

55.数据焊盘dp1至dpo通过初始化晶体管it1、it2和it3耦接至数 据线d1至dm。为了检查阵列衬底ls的破裂,初始化信号可供给至数 据焊盘dp1至dpo。源极驱动ic 30可附接至如图1所示的完成的显示 面板10。此处,数据焊盘dp1至dpo可附接至源极驱动ic 30,例如, 随着数据信号供给至数据焊盘dp1至dpo,数据信号可供给至完成的显 示面板10的数据线d1至dm。

56.如图3所示,可包括三组初始化控制焊盘ip1、ip2和ip3。可包括 三组初始化晶体管it1、it2和it3。第一初始化控制焊盘ip1可耦接至 第一初始化晶体管it1的控制电极。第二初始化控制焊盘ip2可耦接至第 二初始化晶体管it2的控制电极。第三初始化控制焊盘

ip3可耦接至第三 初始化晶体管it3的控制电极。第一初始化控制信号可供给至第一初始 化控制焊盘ip1。第二初始化控制信号可供给至第二初始化控制焊盘ip2。 第三初始化控制信号可供给至第三初始化控制焊盘ip3。

57.第一测试控制焊盘tp1可耦接至第一测试晶体管tt1的每个控制电 极。测试控制信号可供给至第一测试控制焊盘tp1。

58.测试焊盘tvp1和tvp2可耦接至第一测试晶体管tt1的第一电极。 测试信号可供给至测试焊盘tvp1和tvp2。测试信号的相同电压值或者 测试信号的不同电压值可供给至第一测试焊盘tvp1和第二测试焊盘tvp2。例如,测试信号的相同电压值可供给至第一测试焊盘tvp1和第 二测试焊盘tvp2。此外,第一测试信号可供给至第一测试焊盘tvp1, 以及第二测试信号可供给至第二测试焊盘tvp2。

59.初始化晶体管it1、it2和it3可耦接在数据线d1至dm与数据焊 盘dp1至dpo之间。第一初始化晶体管it1的控制电极可耦接至第一初 始化控制焊盘ip1。第二初始化晶体管it2的控制电极可耦接至第二初始 化控制焊盘ip2。第三初始化晶体管it3的控制电极可耦接至第三初始化 控制焊盘ip3。

60.第一初始化晶体管it1的每个控制电极可均耦接至第一初始化控制 焊盘ip1。第一初始化晶体管it1的第一电极可耦接至数据线d1至dm 中的任一个。第一初始化晶体管it1的第二电极可耦接至数据焊盘dp1 至dpo中的任一个。第二初始化晶体管it2的每个控制电极可均耦接至 第二初始化控制焊盘ip2。第二初始化晶体管it2的第一电极可耦接至数 据线d1至dm中的任一个。第二初始化晶体管it2的第二电极可耦接至 数据焊盘dp1至dpo中的任一个。第三初始化晶体管it3的每个控制电 极可均耦接至第三初始化控制焊盘ip3。第三初始化晶体管it3的第一电 极可耦接至数据线d1至dm中的任一个。第三初始化晶体管it3的第二 电极可耦接至数据焊盘dp1至dpo中的任一个。

61.耦接至相邻数据焊盘的第一初始化晶体管it1和第二初始化晶体管 it2可耦接至一个数据线。与第一初始化晶体管it1和第二初始化晶体管 it2邻近的第三初始化晶体管it3可耦接至不同的数据线。例如,耦接至 第一数据焊盘dp1的第一初始化晶体管it1和耦接至第二数据焊盘dp2 的第二初始化晶体管it2可耦接至第一数据线d1。耦接至第三数据焊盘 dp3的第三初始化晶体管it3可耦接至第二数据线d2。

62.第一测试晶体管tt1可耦接在数据线d1至dm与测试焊盘tvp1 和tvp2之间。第一测试晶体管tt1的控制电极可耦接至第一测试控制 焊盘tp1。例如,第一测试晶体管tt1的每个控制电极可均耦接至第一 测试控制焊盘tp1。第一测试晶体管tt1的第一电极可耦接至测试焊盘 tvp1和tvp2中的任一个。第一测试晶体管tt1的第二电极可耦接至数 据线d1至dm中的任一个。

63.轮廓线可位于第一测试晶体管tt1的第一电极与测试焊盘之间。例 如,如图3中所示,第一轮廓线ol1可位于与第一数据线d1耦接的第 一测试晶体管tt1的第一电极和第一测试焊盘tvp1之间。第二轮廓线 ol2可位于与第m数据线dm耦接的第一测试晶体管tt1的第一电极和 第二测试焊盘tvp2之间。即,第一轮廓线ol1可耦接在与第一数据线 d1耦接的第一测试晶体管tt1的第一电极和第一测试焊盘tvp1之间。 第二轮廓线ol2可耦接在与第m数据线dm耦接的第一测试晶体管tt1 的第一电极和第二测试焊盘tvp2之间。

64.轮廓线ol1和ol2中的每个可位于显示区域da外部。例如,第一 轮廓线ol1可与显

示区域da的左侧邻近,以及第二轮廓线ol2可与显 示区域da的右侧邻近。此外,当扫描驱动器20位于与显示区域da的 一侧邻近的非显示区域nda中时,轮廓线ol1和ol2可比扫描驱动器 20更靠外部。此外,在阵列衬底ls处形成的结构中,轮廓线ol1和ol2 可位于最外侧,以围绕形成在阵列衬底ls处的结构。此处,阵列衬底 ls处的结构可指代除了焊盘之外的任何结构。

65.具体地,轮廓线ol1和ol2中的每个可与显示区域da的外部邻近 并穿过与显示区域da邻近的路径至少一次,从而至少部分地围绕显示 区域da的外部。例如,第一轮廓线ol1可与显示区域da左侧的外部 邻近并穿过与显示区域da左侧邻近的路径至少一次,从而至少部分地 围绕显示区域da左侧的外部,以及第二轮廓线ol2可与显示区域da 右侧的外部邻近并穿过与显示区域da右侧邻近的路径至少一次,从而 至少部分地围绕显示区域da右侧的外部。

66.由于轮廓线ol1和ol2的导线电阻,(从测试焊盘tvp1和tvp2 经由轮廓线ol1和ol2)供给至第一测试晶体管tt1的测试信号与(从 测试焊盘tvp1和tvp2不经过轮廓线ol1和ol2)供给至第一测试晶 体管tt1的测试信号之间可能出现电压值差异。

67.为了防止电压值差异,电阻r可位于未与轮廓线ol1和ol2耦接的 第一测试晶体管的第一电极与测试焊盘tvp1和tvp2之间。从而,由于 轮廓线的导线电阻所导致的测试信号中的电压值差异可被减小或最小 化。例如,第一轮廓线ol1的电阻值、第二轮廓线ol2的电阻值以及电 阻r的电阻值可设置为基本上相同,以减小由于轮廓线ol1和ol2的每 个导线电阻所导致的测试信号中的电压值差异。

68.在图3的实施方式中的阵列衬底ls中,第一测试晶体管tt1和电 阻r示出在上部非显示区域nda中。数据焊盘dp1至dpo、初始化控 制焊盘ip1、ip2和ip3、第一测试控制焊盘tp1、测试焊盘tvp1和tvp2 以及初始化晶体管it1、it2和it3位于下部非显示区域nda中。但是, 在其他实施方式中,数据焊盘dp1至dpo、初始化控制焊盘ip1、ip2和 ip3、第一测试控制焊盘tp1以及测试焊盘tvp1和tvp2的布置可以不 同。

69.图4示出了用于控制图3中的显示面板的信号的示例。图4中示出 了供给至初始化控制焊盘ip1、ip2和ip3的初始化控制信号is1、is2和 is3、供给至第一测试控制焊盘tp1的测试控制信号ts、供给至数据焊 盘dp1至dpo的初始化信号iv、供给至测试焊盘tvp1和tvp2的测试 信号tv、以及第一至第三扫描信号和第n扫描信号scan1、scan2、 scan3和scann。

70.参照图4,第一帧周期包括多个水平周期,第一水平周期包括第一周 期t1和第二周期t2。第一帧周期为数据信号供给至显示面板10的所有像 素的周期。第一水平周期为数据信号供给至与一个扫描线耦接的像素的 周期。

71.第一初始化控制信号is1在奇数水平周期oh的第一周期t1期间具有 第一栅极导通电压值von1,并且在奇数水平周期oh的第二周期t2和偶 数水平周期eh期间具有第一栅极截止电压值voff1。第二初始化控制信 号is2在偶数水平周期eh的第一周期t1期间具有第一栅极导通电压值 von1,并且在奇数水平周期oh和偶数水平周期eh的第二周期t2期间具 有第一栅极截止电压值voff1。第三初始化控制信号is3在每个水平周期 的第一周期t1期间具有第一栅极导通电压值von1,并且在第二周期t2 期间具有第一栅极截止电压值voff1。

72.测试控制信号ts在每个水平周期的第一周期t1期间具有第一栅极 截止电压值

voff1,并且在第二周期t2期间具有第一栅极导通电压值 von1。当初始化晶体管it1、it2和it3以及第一测试晶体管tt1为如图3中所示的p型晶体管时,第一栅极导通电压值von1低于第一栅极截止 电压值voff1。例如,如图4中所示,测试控制信号ts与第三初始化控 制信号is3相反。

73.初始化信号iv可设置为峰值白色灰度级电压值pwv,并且测试信 号tv可设置为峰值黑色灰度级电压值pbv。当驱动晶体管dt为如图2 中所示的p型晶体管时,如图4中所示,峰值白色灰度级电压值pwv可 低于峰值黑色灰度级电压值pbv。在图4中,示出了初始化信号iv和测 试信号tv的示例。在其他实施方式中,初始化信号iv和测试信号tv 可具有不同的电压值。

74.第一至第三扫描信号和第n扫描信号scan1、scan2、scan3以 及scann在每个水平周期的第一周期t1期间具有第二栅极截止电压值 voff2,并且在第二周期t2期间具有第二栅极导通电压值von2。在图4 中,示出了在每个水平周期的第二周期t2内,在比第二周期t2更短的周 期期间,第一至第三扫描信号和第n扫描信号scan1、scan2、scan3 和scann具有第二栅极导通电压值von2的示例,但本发明并不限于此。 例如,第一至第三扫描信号和第n扫描信号scan1、scan2、scan3 和scann在每个水平周期的第二周期t2期间可具有第二栅极导通电压 值von2。当扫描晶体管st为如图2中所示的p型晶体管时,如图4中 所示,第二栅极导通电压值von2可低于第二栅极截止电压值voff2。

75.当像素rp、gp和bp的扫描晶体管st与第一初始化晶体管至第三 初始化晶体管it1、it2和it3以及第一测试晶体管tt1具有相同的晶体 管特性时,第二栅极导通电压值von2基本上可与第一栅极导通电压值 von1相同,并且第二栅极截止电压值voff2基本上可与第一栅极截止电 压值voff1相同。

76.图3和图4示出了用于检查显示面板破裂的方法的实施方式中的操 作。第一初始化控制信号is1和第三初始化控制信号is3在奇数水平周期 oh的第一周期t1期间具有第一栅极导通电压值von1。第二初始化控制信 号is2和测试控制信号ts在奇数水平周期oh的第一周期t1期间具有第 一栅极截止电压值voff1。因此,第一初始化晶体管it1和第三初始化晶 体管it3导通,并且第二初始化晶体管it2和第一测试晶体管tt1截止。 因此,初始化信号iv可通过第一和第三初始化晶体管it1和it3供给至 第一至第m数据线d1至dm。

77.在奇数水平周期oh的第二周期t2期间,第一至第三初始化控制信号 is1、is2和is3具有第一栅极截止电压值voff1并且测试控制信号ts具 有第一栅极导通电压值von1。因此,第一至第三初始化晶体管it1、it2 和it3截止并且第一测试晶体管tt1导通。因此,测试信号tv可通过 第一测试晶体管tt1供给至第一至第m数据线d1至dm。

78.此外,当第一扫描信号scan1在奇数水平周期oh的第二周期t2内 具有第二栅极导通电压值von2时,第一至第m数据线d1至dm的信号 被供给至与第一扫描线s1耦接的红色像素rp和绿色像素gp。

79.当初始化信号iv的电压值为峰值白色灰度级电压值pwv并且测试 信号tv的电压值为峰值黑色灰度级电压值pbv时,如图5a中所示, 待供给至像素的电压值在第一周期t1期间可减少到峰值白色灰度级电压 值pwv并在第二周期t2期间可增加至峰值黑色灰度级电压值pbv。然 而,如果阵列衬底ls上具有裂缝,则数据线d1至dm或轮廓线ol1和 ol2可能断开,或者数据线d1至dm或轮廓线ol1和ol2的导线电阻 可能增加。

80.例如,当阵列衬底ls上具有一个或多个裂缝并且数据线d1至dm 或轮廓线ol1和ol2被断开时,在第二周期t2期间可能不供给峰值黑 色灰度级电压值pbv。因此,如图5b中所示,待供给至像素的电压值可 在第一周期t1期间减少到峰值白色灰度级电压值pwv,并且峰值白色灰 度级电压值pwv可在第二周期t2期间保持。因为与由于裂缝所导致的 断开的数据线或轮廓线耦接的像素可表示峰值白色灰度级,因此可显示 亮线。

81.此外,当阵列衬底ls上具有一个或多个裂缝并且数据线d1至dm 或轮廓线ol1和ol2的导线电阻增加时,如图5c中所示,即使在第二 周期t2期间供给峰值黑色灰度级电压值pbv,待供给至像素的电压值可 在第一周期t1期间减少到峰值白色灰度级电压值pwv,而不会在第二周 期t2期间增加至峰值黑色灰度级电压值pbv。因此,耦接至数据线的像 素或者由于裂缝导致导线电阻增加的轮廓线将表示灰度变化,并且因此 可显示较不亮的线。

82.如上面所讨论的,根据一个实施方式,初始化信号iv可在每个水平 周期的第一周期t1期间经由初始化晶体管it1、it2和it3供给。测试信 号tv可在第二周期t2期间通过第一测试晶体管tt1供给。因此,基于 数据线d1至dm的断开或导线电阻的变化,或者基于显示区域da外部 轮廓线的断开或导线电阻的变化,可确定阵列衬底ls上是否存在裂缝。 例如,当显示亮线或较不亮的线时,可确定在阵列衬底ls上具有裂缝。

83.图6示出了图3中的测试晶体管与轮廓线以及测试晶体管与电阻之 间的耦接结构的实施方式。图7a为沿图6中的线i

‑

i’的剖视图。图7b 为沿图6中的线ii

‑

ii’的剖视图。下文中参照图6、图7a和图7b描述耦 接至第一数据线d1和第一轮廓线ol1的第一测试晶体管tt1的耦接结 构以及耦接至第二和第三数据线d2和d3以及电阻r的第一测试晶体管 tt1的耦接结构。为了方便起见,图6仅示出第一至第三数据线d1、d2 和d3以及耦接至第一至第三数据线d1、d2和d3的第一测试晶体管 tt1。

84.在图6中,耦接至第一轮廓线ol1的第一晶体管tt1被限定为第 (1

‑

1)测试晶体管tt1

‑

1,并且耦接至电阻r的第一测试晶体管tt1被 限定为第(1

‑

2)测试晶体管tt1

‑

2。

85.参照图6和图7a,第(1

‑

1)测试晶体管tt1

‑

1的控制电极tt_g与 预设区域中的有源层tt_act重叠。第(1

‑

1)测试晶体管tt1

‑

1的有源 层tt_act的一端可通过第一接触孔cnt1耦接至第一数据线d1,并且 有源层tt_act的另一端可通过第二接触孔cnt2耦接至第一轮廓线 ol1的一端。如图3中所示,第一轮廓线ol1可与显示区域da邻近并 且穿过与显示区域da邻近的路径至少一次,从而至少部分地围绕显示 区域da的外部。第一轮廓线ol1的另一端可经由第三接触孔cnt3耦 接至桥式电极be。桥式电极be可通过第四接触孔cnt4耦接至测试电 压线tvl。测试电压线tvl可以为与供给有测试信号tv的测试焊盘 tvp1和tvp2中的任一个耦接的线。

86.第(1

‑

1)测试晶体管tt1

‑

1的控制电极tt_g和桥式电极be可包 括第一金属图案。第(1

‑

1)测试晶体管tt1

‑

1的有源层tt_act可包括 半导体图案。第一数据线d1、第一轮廓线ol1以及测试电压线tvl可 包括第二金属图案。第一金属图案可以为栅极金属图案,以及第二金属 图案可以为源极/漏极金属图案。半导体图案可包括例如多晶硅、单晶硅、 非晶硅或氧化物半导体材料。栅极绝缘体gi可位于第一金属图案与半导 体图案之间,以使第一金属图案和半导体图案绝缘。此外,为了使半导 体图案与第二金属图案绝缘,钝化层pas可位于半导体图案与第二金属 图案之间。

87.参照图6和图7b,第(1

‑

2)测试晶体管tt1

‑

2的控制电极tt_g可 在预设区域中与有

源层tt_act重叠。第(1

‑

2)测试晶体管tt1

‑

2的有 源层tt_act的一端可经由第一接触孔cnt1耦接至第二数据线d2或 第三数据线d3,并且有源层tt_act的另一端可通过第五接触孔cnt5 耦接至桥式电极be。桥式电极be可经由第四接触孔cnt4耦接至测试 电压线tvl。

88.第(1

‑

2)测试晶体管tt1

‑

2的控制电极tt_g和桥式电极be可包 括第一金属图案。第(1

‑

2)测试晶体管tt1

‑

2的有源层tt_act可包括 半导体图案。第二数据线d2和第三数据线d3以及测试电压线tvl可 包括第二金属图案。第一金属图案可以为栅极金属图案,以及第二金属 图案可以为源极/漏极金属图案。半导体图案可包括例如多晶硅、单晶硅、 非晶硅或氧化物半导体材料。栅极绝缘体gi可位于第一金属图案与半导 体图案之间,以使第一金属图案和半导体图案绝缘。此外,为了使半导 体图案与第二金属图案绝缘,钝化层pas可位于半导体图案与第二金属 图案之间。

89.第(1

‑

2)测试晶体管tt1

‑

2的有源层tt_act可长于第(1

‑

1)测 试晶体管tt1

‑

1的有源层tt_act。例如,第(1

‑

2)测试晶体管tt1

‑

2 的有源层tt_act可长于第(1

‑

1)测试晶体管tt1

‑

1的有源层tt_act 并且可用作电阻r。例如,掺杂有杂质的第(1

‑

1)测试晶体管tt1

‑

1的 有源层tt_act可起电阻r的作用。通过将电阻r的电阻值设计为基本 上与第一轮廓线ol1的导线电阻值相同,可使由于第一轮廓线ol1的导 线电阻所导致的测试信号中的电压值差异最小化。

90.图8示出了显示面板10的阵列衬底的另一实施方式。参照图8,显 示面板10包括阵列衬底ls和相反的衬底。阵列衬底ls被划分成包括用 于显示图像的像素p的显示区域da,以及位于显示区域da外部的非显 示区域nda。

91.像素p位于阵列衬底ls的显示区域da中。数据焊盘dp1至dpo、 初始化控制焊盘ip1、ip2和ip3、第一测试控制焊盘tp1、测试焊盘tvp1 和tvp2、初始化晶体管it1、it2和it3、第一测试晶体管tt1、电阻r 以及轮廓线ol1和ol2位于阵列衬底ls的非显示区域nda中。

92.图8中的显示面板10的阵列衬底ls的像素p、数据焊盘dp1至dpo、 初始化控制焊盘ip1、ip2和ip3、第一测试控制焊盘tp1、测试焊盘tvp1 和tvp2、初始化晶体管it1、it2和it3、第一测试晶体管tt1、电阻r 以及轮廓线ol1和ol2可基本上与图3中的相同。

93.显示面板10的阵列衬底ls的轮廓线ol1和ol2通过第一测试晶体 管tt1耦接至与绿色像素gp耦接的数据线d2和dm。例如,与轮廓线 耦接的第一测试晶体管tt1可耦接至与绿色像素gp耦接的数据线。因 为人类对绿色的颜色感知能力比对红色或蓝色的颜色感知能力好,所以 根据图8的实施方式,较不亮的线更容易被察觉,从而可更容易地确定 非显示区域nda中的裂缝。

94.当轮廓线ol1和ol2通过第一测试晶体管tt1耦接至与绿色像素 gp耦接的数据线d2和dm时,电阻r可仅耦接至未与轮廓线ol1和 ol2耦接的第一测试晶体管tt1中的、与耦接至绿色像素gp的数据线 耦接的第一测试晶体管tt1。因此,图8中的实施方式可比图3中的实 施方式减少更多的电阻r。由此,在图8的实施方式中可具有更少的电 路复杂性。

95.图9示出了显示面板10的阵列衬底的另一实施方式。参照图9,显 示面板10包括阵列衬底ls和相反的衬底。阵列衬底ls被划分成包括像 素p以显示图像的显示区域da和位于显示区域da外部的非显示区域 nda。像素p位于阵列衬底ls的显示区域da中。根据图9的实施方式 的显示面板10的阵列衬底ls的像素p可基本上与图3的实施方式相同。

96.数据焊盘dp1至dpm、初始化控制焊盘ip1、ip2和ip3、初始化焊 盘ivp1、ivp2和ivp3、第一测试控制焊盘tp1、测试焊盘tvp1和tvp2、 初始化晶体管it1、it2和it3、第一测试晶体管tt1、电阻r以及轮廓 线ol1和ol2位于阵列衬底ls的非显示区域nda中。此外,当扫描 驱动器20使用asg方法或gip方法形成时,扫描驱动器20可位于显示 区域da外部的非显示区域nda中。

97.数据焊盘dp1至dpm可耦接至数据线d1至dm。当检查阵列衬底 ls的裂缝时,没有信号或电力可供给至数据焊盘dp1至dpm。源极驱 动ic 30可附接至如图1中所示的完成的显示面板10。数据焊盘dp1至 dpm可耦接至源极驱动ic 30。例如,因为源极驱动ic 30向数据焊盘 dp1至dpm供给数据信号,所以源极驱动ic 30可向完成的显示面板10 的数据线d1至dm供给数据信号。

98.初始化焊盘ivp1、ivp2和ivp3通过第一测试晶体管tt1耦接至数 据线d1至dm。初始化信号供给至初始化焊盘ivp1、ivp2和ivp3。初 始化信号的相同或不同的电压值可被供给至初始化焊盘ivp1、ivp2和 ivp3。例如,初始化信号的相同电压值可被供给至第一初始化焊盘至第 三初始化焊盘ivp1、ivp2和ivp3。可替代地,初始化信号的第一电压 值可供给至第一初始化焊盘ivp1,初始化信号的第二电压值可供给至第 二初始化焊盘ivp2,以及初始化信号的第三电压值可供给至第三初始化 焊盘ivp3。

99.如图9中所示,可包括三组初始化控制焊盘ip1、ip2和ip3,并且 可包括三组初始化晶体管it1、it2和it3。第一初始化控制焊盘ip1耦 接至第一初始化晶体管it1的控制电极。第二初始化控制焊盘ip2耦接至 第二初始化晶体管it2的控制电极。第三初始化控制焊盘ip3耦接至第三 初始化晶体管it3的控制电极。第一初始化控制信号供给至第一初始化 控制焊盘ip1,第二初始化控制信号供给至第二初始化控制焊盘ip2,以 及第三初始化控制信号供给至第三初始化控制焊盘ip3。

100.第一测试控制焊盘tp1耦接至第一测试晶体管tt1的每个控制电 极。测试控制信号供给至第一测试控制焊盘tp1。

101.测试焊盘tvp1和tvp2耦接至第一测试晶体管tt1的第一电极。 测试信号供给至测试焊盘tvp1和tvp2。相同或不同的测试信号供给至 第一测试焊盘tvp1和第二测试焊盘tvp2。例如,相同的测试信号可供 给至第一测试焊盘tvp1和第二测试焊盘tvp2。可替代地,第一测试信 号可供给至第一测试焊盘tvp1,以及第二测试信号可供给至第二测试焊 盘tvp2。

102.初始化晶体管it1、it2和it3可耦接在数据线d1至dm与初始化 焊盘ivp1、ivp2和ivp3之间。第一初始化晶体管it1可耦接在数据线 与第一初始化焊盘ivp1之间。第二初始化晶体管it2可耦接在数据线与 第三初始化焊盘ivp3之间。第三初始化晶体管it3可耦接在数据线与第 二初始化焊盘ivp2之间。第一初始化晶体管it1的控制电极可耦接至第 一初始化控制焊盘ip1。第二初始化晶体管it2的控制电极可耦接至第二 初始化控制焊盘ip2。第三初始化晶体管it3的控制电极可耦接至第三初 始化控制焊盘ip3。

103.例如,第一初始化晶体管it1的每个控制电极可均耦接至第一初始 化控制焊盘ip1,第一初始化晶体管it1的第一电极可耦接至数据线d1 至dm中的任一个,以及第一初始化晶体管it1的第二电极可耦接至第 一初始化焊盘ivp1。第二初始化晶体管it2的每个控制电极可均耦接至 第二初始化控制焊盘ip2,第二初始化晶体管it2的第一电极可耦接至

数 据线d1至dm中的任何一个,以及第二初始化晶体管it2的第二电极可 耦接至第三初始化焊盘ivp3。第三初始化晶体管it3的每个控制电极可 均耦接至第三初始化控制焊盘ip3,第三初始化晶体管it3的第一电极可 耦接至数据线d1至dm中的任一个,以及第三初始化晶体管it3的第二 电极可耦接至第二初始化焊盘ivp2。

104.相邻的第一初始化晶体管it1和第二初始化晶体管it2可耦接至一 个数据线。与第一初始化晶体管it1和第二初始化晶体管it2邻近的第 三初始化晶体管it3可耦接至不同的数据线。例如,彼此相邻的第一初 始化晶体管it1和第二初始化晶体管it2可耦接至第一数据线d1。如图 9中所示,与第一初始化晶体管it1和第二初始化晶体管it2邻近的第三 初始化晶体管it3可耦接至第二数据线d2。

105.第一测试晶体管tt1可耦接在数据线d1至dm与测试焊盘tvp1 和tvp2之间。第一测试晶体管tt1的控制电极可耦接至第一测试控制 焊盘tp1。例如,第一测试晶体管tt1的每个控制电极可耦接至第一测 试控制焊盘tp1,第一测试晶体管tt1的第一电极可耦接至测试焊盘 tvp1和tvp2中的任何一个,以及第一测试晶体管tt1的第二电极可耦 接至数据线d1至dm中的任一个。

106.轮廓线可位于第一测试晶体管tt1的第一电极与测试焊盘之间。例 如,如图3中所示,第一轮廓线ol1可位于与第一数据线d1耦接的第 一测试晶体管tt1的第一电极与第一测试焊盘tvp1之间。第二轮廓线 ol2可位于与第m数据线dm耦接的第一测试晶体管tt1的第一电极和 第二测试焊盘tvp2之间。例如,第一轮廓线ol1可耦接在与第一数据 线d1耦接的第一测试晶体管tt1的第一电极和第一测试焊盘tvp1之 间。第二轮廓线ol2可耦接在与第m数据线dm耦接的第一测试晶体管 tt1的第一电极和第二测试焊盘tvp2之间。

107.轮廓线ol1和ol2中的每个可位于显示区域da的外部。例如,第 一轮廓线ol1可位于显示区域da的左侧的外部和上侧的外部。第二轮 廓线ol2可位于显示区域da的右侧的外部和上侧的外部。此外,当扫 描驱动器20位于显示区域da一侧外部的非显示区域nda中时,轮廓 线ol1和ol2可比扫描驱动器20更靠外部。此外,在阵列衬底ls处的 结构之中,轮廓线ol1和ol2可位于最外侧,以围绕形成在阵列衬底 ls处的结构。阵列衬底ls处的结构可以指代除了焊盘之外的任何结构。

108.例如,轮廓线ol1和ol2中的每个可邻近于显示区域da并且穿过 与显示区域da邻近的路径至少一次,从而至少部分地围绕显示区域da 的外部。在一个实施方式中,第一轮廓线ol1可与显示区域da的左侧 和上侧邻近并穿过与显示区域da的左侧和上侧邻近的路径至少一次, 从而至少部分地围绕显示区域da的左侧和上侧,并且第二轮廓线ol2 可与显示区域da右侧和上侧的外部邻近并穿过与显示区域da的右侧 和上侧邻近的路径至少一次,从而至少部分地围绕显示区域da的右侧 和上侧。

109.电压值差异可存在于(从测试焊盘tvp1和tvp2)经由轮廓线ol1 和ol2供给至第一测试晶体管tt1的测试信号与不经过轮廓线ol1和 ol2(从测试焊盘tvp1和tvp2)供给至第一测试晶体管tt1的测试信 号之间。该电压值差异可由于轮廓线ol1与ol2之间的导线电阻的差异 而出现。

110.为了防止出现电压值差异,电阻r可放置在第一测试晶体管tt1(其 未耦接至轮廓线ol1和ol2)的第一电极与测试焊盘tvp1和tvp2之 间。因此,可减小或使由轮廓线ol1和ol2的导线电阻所导致的测试信 号的任何电压值差异最小化。例如,第一轮廓线ol1的电阻

值、第二轮 廓线ol2的电阻值以及电阻r的电阻值可设置为基本上相同,以减小或 使由于轮廓线ol1和ol2的导线电阻导致的测试信号的电压值差异最小 化。电阻r的示例在上文中参照图6、图7a和图7b进行了说明。

111.根据一个实施方式,在显示面板的阵列衬底ls中,初始化晶体管 it1、it2和it3位于上部非显示区域nda中。此外,在该实施方式中, 数据焊盘dp1至dpm、初始化控制焊盘ip1、ip2和ip3、第一测试控制 焊盘tp1、初始化焊盘ivp1、ivp2和ivp3、测试焊盘tvp1和tvp2、 第一测试晶体管tt1以及电阻r位于下部非显示区域nda中。数据焊 盘dp1至dpm、初始化控制焊盘ip1、ip2和ip3、第一测试控制焊盘tp1、 初始化焊盘ivp1、ivp2和ivp3以及测试焊盘tvp1和tvp2的布置在 另一实施方式中可以不同。

112.如上面所讨论的,在图3的实施方式中,使数据线d1至dm初始化 的初始化晶体管耦接至数据焊盘dp1至dpm,而在图9的实施方式中, 使数据线d1至dm初始化的初始化晶体管耦接至初始化焊盘ivp1、ivp2 和ivp3。此外,在图3的实施方式中,第一测试晶体管tt1和电阻r位 于上部非显示区域nda中并且初始化晶体管it1、it2和it3位于下部 非显示区域nda中,而在图9的实施方式中,初始化晶体管it1、it2 和it3位于上部非显示区域nda中并且第一测试晶体管tt1和电阻r 位于下部非显示区域nda中。

113.供给至图9的实施方式中的显示面板的信号可基本上与图4相同。 例如,供给至初始化控制焊盘ip1、ip2和ip3的初始化控制信号is1、is2 和is3、供给至第一测试控制焊盘tp1的测试控制信号ts、供给至初始 化焊盘ivp1、ivp2和ivp3的初始化信号iv、供给至测试焊盘tvp1和 tvp2的测试信号tv以及供给至扫描线s1至s3和sn的扫描信号 scan1、scan2、scan3和scann可基本上与图4相同。在另一实施 方式中,供给至图9的实施方式中的显示面板的信号可不同于图4中的 供给至显示面板的信号。此外,用于检查根据图9的实施方式的显示面 板的裂缝的方法可基本上与图3和图4相同,但是这也不是必须的。

114.图10示出了显示面板10的阵列衬底的另一实施方式。参照图10, 显示面板10包括阵列衬底ls和相反的衬底。阵列衬底ls划分成包括用 于显示图像的像素p的显示区域da以及位于显示区域da外部的非显 示区域nda。

115.像素p位于阵列衬底ls的显示区域da中。数据焊盘dp1至dpm、 初始化控制焊盘ip1、ip2和ip3、初始化焊盘ivp1、ivp2和ivp3、测 试控制焊盘tp1

‑

1、tp1

‑

2、tp2

‑

1和tp2

‑

2、测试焊盘tvp1和tvp2、 初始化晶体管it1、it2和it3、测试晶体管tt1和tt2、电阻r以及轮 廓线ol1和ol2位于阵列衬底ls的非显示区域nda中。图10中的显 示面板10的阵列衬底ls的像素p、数据焊盘dp1至dpm、初始化控制 焊盘ip1、ip2和ip3、初始化焊盘ivp1、ivp2和ivp3、测试焊盘tvp1 和tvp2以及初始化晶体管it1、it2和it3可基本上与图9中的实施方 式相同,但是这并不是必须的。

116.第一测试控制焊盘tp1

‑

1和tp1

‑

2耦接至第一测试晶体管tt1的控 制电极。第(1

‑

1)测试控制焊盘tp1

‑

1耦接至与第一数据线d1耦接的 第一测试晶体管tt1的控制电极和与第m数据线dm耦接的第一测试晶 体管tt1的控制电极。第(1

‑

2)测试控制焊盘tp1

‑

2耦接至与剩余的数 据线d2至dm

‑

1耦接的第一测试晶体管tt1的控制电极。第一测试控制 信号可供给至第一测试控制焊盘tp1

‑

1和tp1

‑

2。

117.图10的实施方式还包括第二测试晶体管tt2以及第二测试控制焊盘 tp2

‑

1和tp2

‑

2。第二测试控制焊盘tp2

‑

1和tp2

‑

2耦接至第二测试晶体 管tt2的控制电极。第(2

‑

1)测试

控制焊盘tp2

‑

1耦接至与第一数据线 d1耦接的第二测试晶体管tt2的控制电极。第(2

‑

2)测试控制焊盘tp2

‑

2 耦接至与第m数据线dm耦接的第二测试晶体管tt2的控制电极。第二 测试控制信号供给至第二测试控制焊盘tp2

‑

1和tp2

‑

2。

118.第一测试晶体管tt1耦接在数据线d1至dm与测试焊盘tvp1和 tvp2之间。第一测试晶体管tt1的控制电极耦接至第一测试控制焊盘tp1

‑

1和tp1

‑

2。例如,第一测试晶体管tt1的每个控制电极耦接至第一 测试控制焊盘tp1

‑

1和tp1

‑

2之一,第一测试晶体管tt1的第一电极耦 接至测试焊盘tvp1和tvp2之一,以及第一测试晶体管tt1的第二电 极耦接至数据线d1至dm之一。

119.第二测试晶体管tt2耦接在数据线d1至dm与轮廓线ol1和ol2 之间。第二测试晶体管tt2的控制电极耦接至第二测试控制焊盘tp2

‑

1 和tp2

‑

2。例如,第二测试晶体管tt2的每个控制电极耦接至第二测试 控制焊盘tp2

‑

1和tp2

‑

2中之一,第二测试晶体管tt2的第一电极耦接 至轮廓线ol1和ol2之一,以及第二测试晶体管tt2的第二电极耦接 至数据线d1至dm之一。

120.轮廓线ol1和ol2耦接在第二测试晶体管tt2与测试焊盘tvp1 和tvp2之间。第一轮廓线ol1耦接在与第一数据线d1耦接的第二测 试晶体管tt2的第一电极和第一测试焊盘tvp1之间。第二轮廓线ol2 耦接在与第m数据线dm耦接的第二测试晶体管tt2的第一电极和第二 测试焊盘tvp2之间。

121.轮廓线ol1和ol2中的每个可位于显示区域da的外部。例如,第 一轮廓线ol1可与显示区域da的左侧和上侧邻近且位于显示区域da 的左侧和上侧外部。第二轮廓线ol2可位于显示区域da的右侧和上侧 外部。此外,当扫描驱动器20位于与显示区域da的一侧邻近的非显示 区域nda中时,轮廓线ol1和ol2可比扫描驱动器20更靠外部。此外, 轮廓线ol1和ol2可位于最外侧,以围绕阵列衬底ls处的结构。这些 结构可以指代除了焊盘之外的任何结构。

122.电压值差异可存在于(从测试焊盘tvp1和tvp2)经由轮廓线ol1 和ol2供给至第二测试晶体管tt2的测试信号与(从测试焊盘tvp1和 tvp2)不经过轮廓线ol1和ol2供给至第一测试晶体管tt1的测试信 号之间。由于轮廓线ol1和ol2的导线电阻的差异而可出现电压值差异。

123.为了防止出现电压值差异,电阻r可放置在未与轮廓线ol1和ol2 耦接的第一测试晶体管tt1的第一电极与测试焊盘tvp1和tvp2之间。 因此,可减小或使由于轮廓线ol1和ol2的导线电阻的电阻值差异所导 致的测试信号的电压值差异最小化。例如,第一轮廓线ol1的电阻值、 第二轮廓线ol2的电阻值以及电阻r的电阻值可基本上相同,以减小或 使由于轮廓线ol1和ol2的导线电阻所导致的测试信号的差异最小化。 电阻r的示例在上文中参照图6、图7a和图7b进行了说明。

124.在图10的实施方式中,在显示面板的阵列衬底ls中,初始化晶体 管it1、it2和it3以及第二测试晶体管tt2位于上部非显示区域nda 中,并且数据焊盘dp1至dpm、初始化控制焊盘ip1、ip2和ip3、测试 控制焊盘tp1

‑

1、tp1

‑

2、tp2

‑

1和tp2

‑

2、初始化焊盘ivp1、ivp2和ivp3、 测试焊盘tvp1和tvp2、第一测试晶体管tt1以及电阻r位于下部非 显示区域nda中。数据焊盘dp1至dpm、初始化控制焊盘ip1、ip2和 ip3、第一测试控制焊盘tp1、初始化焊盘ivp1、ivp2和ivp3以及测试 焊盘tvp1和tvp2的布置在另一实施方式中可以不同。

125.供给至图10的实施方式中的显示面板的信号可基本上与图4相同。 例如,供给至初始化控制焊盘ip1、ip2和ip3的初始化控制信号is1、is2 和is3、供给至测试控制焊盘tp1

‑

1、tp1

‑

2、tp2

‑

1和tp2

‑

2的测试控制 信号ts、供给至初始化焊盘ivp1、ivp2和ivp3的初始化信号iv、供 给至测试焊盘tvp1和tvp2的测试信号tv以及供给至扫描线s1至s3 和sn的扫描信号scan1、scan2、scan3和scann可基本上与图4 相同,但这并不是必须的。此外,用于检查与图10的实施方式相对应的 显示面板的裂缝的方法可基本上与图3和图4中的相同,但是这并不是 必须的。

126.图11示出了用于制造显示装置的方法的实施方式。该方法包括制造 显示面板10的阵列衬底ls(s101)。例如,可根据图3、图8、图9或 图10的实施方式制造显示面板10的阵列衬底ls。

127.接下来,执行检查以确定显示面板10的阵列衬底ls上是否具有裂 缝(s102)。例如,可根据参照图3和图4描述的方法执行对阵列衬底 ls上的裂缝的检查。当确定在显示面板10的阵列衬底ls上存在裂缝时, 阵列衬底ls可被确定为有缺陷的(s103)。

128.当确定显示面板10的阵列衬底ls上没有裂缝时,阵列衬底ls可被 确定为具有良好的品质并且可执行模块过程(s104)。例如,如果阵列衬 底ls被确定为具有良好的品质,则相反的衬底可附接至显示面板10的 阵列衬底ls,安装有源极驱动ic的柔性膜可附接至阵列衬底,该柔性 膜可附接至源极印刷电路板,并且安装有时序控制器的控制印刷电路板 与源极印刷电路板可使用柔性线缆进行耦接。

129.在该实施方式中,可在执行模块过程之前执行检查以确定在阵列衬 底ls上是否已出现了裂缝。当阵列衬底ls被确定为具有裂缝时,阵列 衬底ls被识别为有缺陷的。因此,通过不对有缺陷的显示面板执行模块 过程来防止制造成本的浪费。

130.图12示出了用于制造显示装置的方法的另一实施方式。在该实施方 式中,操作s201至s204可基本上与图11中的操作s101至s104相同。

131.此外,可包括操作205,在操作205中在模块过程完成之后执行再检 查以确定显示面板10的阵列衬底ls上是否具有裂缝。因为由于在模块 过程期间的撞击阵列衬底ls上可能出现裂缝,因此可执行该再检查操 作。通过执行该再检查操作,可减小或使有缺陷的产品的放出最小化。

132.可根据如图3和图4的显示面板的裂缝检查方法来执行阵列衬底ls 上的裂缝的检查。此外或可替代地,可根据图3或图8中的实施方式来 制造显示面板10的阵列衬底ls。

133.当根据图9或图10的实施方式制造阵列衬底ls时,源极驱动ic可 由于模块过程而耦接至与第一测试晶体管tt1的控制电极耦接的测试控 制焊盘。此外,源极驱动ic可向测试控制焊盘供给第一栅极截止电压值 voff1。因此,在模块过程完成之后难以检查显示面板10的阵列衬底ls 上是否出现裂缝。

134.因此,根据本实施方式,在执行模块过程之后,可执行再检查以确 定阵列衬底ls上是否出现了裂缝。如果确定出现了裂缝,那么显示面板 10可被确定为有缺陷的。因此,可防止阵列衬底ls上具有裂缝(例如, 在模块过程之前和模块过程期间出现的)的显示面板的放出。

135.通过总结和回顾,根据一个实施方式,可在第一周期期间经由初始 化晶体管供给初始化信号,并且可在第二周期期间通过第一测试晶体管 供给测试信号。因此,例如,可基

于数据线的断开或数据线的导线电阻 的变化,确定阵列衬底的显示区域中是否已出现了裂缝。

136.根据该实施方式或另一实施方式,轮廓线可位于阵列衬底的非显示 区域(显示区域外部)中。因此,例如,可基于由裂缝引起的轮廓线的 断开或轮廓线的导线电阻的变化,确定阵列衬底的非显示区域中是否已 出现了裂缝。

137.根据该实施方式或另一实施方式,电阻可放置在第一测试晶体管(未 耦接至轮廓线)与供给有测试信号的测试焊盘之间。因此,可减小或使 由于轮廓线的导线电阻的差异所导致的测试信号的电压值差异最小化。

138.根据该实施方式或另一实施方式,轮廓线可通过测试晶体管耦接至 与像素或子像素的预定颜色(例如,绿色)耦接的数据线。因为人类对 绿色的感知能力优于对红色或蓝色的感知能力,因此可以更容易地确定 非显示区域处是否已出现了裂缝。因此,电阻可仅放置在未耦接至轮廓 线的测试晶体管中的、耦接至与绿色像素或子像素耦接的数据线的测试 晶体管处。因此,可减小电阻,并且可减小电路复杂性。在另一实施方 式中,电阻可放置为用于所有颜色像素或子像素或者包括或除去绿色的 颜色像素或子像素的子集。

139.根据该实施方式或另一实施方式,可在执行模块过程之前确定阵列 衬底上是否已出现了裂缝。具有裂缝的阵列衬底可被确定为有缺陷的。 因此,可以不对有缺陷的显示面板执行模块过程,并且由此可以不浪费 制造成本。

140.根据该实施方式或另一实施方式,可在执行了模块过程之后执行再 检查操作,以确定阵列衬底上是否已出现了裂缝。具有裂缝的显示面板 可被确定为有缺陷的。因此,可防止具有在模块过程期间出现在阵列衬 底上的裂缝的显示面板的放出。

141.本文中已经公开了示例性实施方式,并且尽管采用了具体术语,但 是这些术语仅以通用和描述性含义进行使用和解释,而不是用于限制的 目的。除非另有指示,否则在某些情况下正如本领域的普通技术人员将 随着本申请的提交而清楚的,结合特定实施方式而描述的特征、特性和/ 或元件可单独使用或者与结合其他实施方式描述的特征、特性和/或元件 组合使用。相应地,本领域的技术人员应理解,在不背离如所述权利要 求书中阐述的本发明的精神和范围的情况下,可在形式和细节上进行各 种修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1