发光二极管封装件、显示设备以及像素驱动集成电路的制作方法

发光二极管封装件、显示设备以及像素驱动集成电路

1.相关申请的交叉引用

2.本申请要求2020年2月18日提交于韩国知识产权局的韩国专利申请no.10

‑

2020

‑

0019991的优先权,该申请的公开内容以引用方式整体并入本文中。

技术领域

3.本公开的实施例涉及半导体集成电路,更具体地,涉及一种发光二极管(led)封装件和包括其的显示设备。

背景技术:

4.led用作用于照明器材和各种电子产品的光源。具体地,led广泛用作用于各种显示设备(诸如电视(tv)、移动电话、个人计算机(pc)、笔记本pc和个人数字助理(pda))的光源。

5.显示设备可包括液晶显示器(lcd)面板和背光。然而,最近提出了在其中例如三个微型led芯片形成像素的led显示器。与现有lcd显示器相比,led显示器不需要背光,并且因此适合于高度集成并具有优异的光效率。另外,通过改变led芯片的布置方式,可自由地选择屏幕的纵横比并且可提供大型屏幕。

技术实现要素:

6.一个或多个示例实施例提供一种在以低亮度操作时具有提高的可靠性的发光二极管(led)封装件以及使用该led封装件的显示设备。

7.实施例不限于上述那些,本领域技术人员将从下面的描述清楚地理解未提及的发明构思。

8.根据示例实施例的一方面,提供了一种显示设备,该显示设备包括:模块基板;按矩阵布置在模块基板上的多个发光二极管(led)封装件;以及通过模块基板电连接到多个led封装件的控制器,其中,多个led封装件中的每一个包括:封装件基板;位于封装件基板上的像素驱动集成电路;以及位于像素驱动集成电路上的第一led芯片、第二led芯片和第三led芯片,并且其中,像素驱动集成电路被配置为:基于控制器的控制信号,在第一脉冲宽度调制(pwm)模式下控制以第一电流水平施加到第一led芯片、第二led芯片和第三led芯片的电流的脉冲宽度,或者在第二pwm模式下控制以第二电流水平施加到第一led芯片、第二led芯片和第三led芯片的电流的脉冲宽度,第二电流水平不同于第一电流水平。

9.根据示例实施例的一方面,提供了一种发光二极管(led)封装件,该led封装件包括:像素驱动集成电路,其被配置为使用有源矩阵控制像素;以及位于像素驱动集成电路上并且被配置为形成像素的第一led芯片、第二led芯片和第三led芯片,其中,像素驱动集成电路包括:电流调节器,其被配置为基于帧数据输出具有可变的电流水平的第一参考电流、第二参考电流和第三参考电流;以及led驱动器,其被配置为基于第一参考电流、第二参考电流和第三参考电流以及帧数据生成用于驱动第一led芯片的第一驱动电流、用于驱动第

二led芯片的第二驱动电流以及用于驱动第三led芯片的第三驱动电流,并且其中,led驱动器还被配置为基于灰度来控制第一驱动电流、第二驱动电流和第三驱动电流中的每一个的脉冲宽度。

10.根据示例实施例的一方面,提供了一种用于驱动包括发光二极管(led)芯片的像素的像素驱动集成电路,该像素驱动集成电路包括:解串器,其被配置为从外部控制器接收串行数据并从串行数据中提取针对第一像素的帧数据;数据存储部,其被配置为存储由解串器提取的帧数据;电流调节器,其被配置为:在第一模式和第二模式中的一个模式下,基于帧数据输出第一参考电流、第二参考电流和第三参考电流;以及led驱动器,其被配置为基于帧数据以及第一参考电流、第二参考电流和第三参考电流生成用于驱动第一led芯片的第一驱动电流、用于驱动第二led芯片的第二驱动电流以及用于驱动第三led芯片的第三驱动电流,其中,led驱动器还被配置为通过控制第一驱动电流、第二驱动电流和第三驱动电流的脉冲宽度来控制第一led芯片、第二led芯片和第三led芯片的亮度,并且其中,电流调节器还被配置为在第一模式下以第一电流水平输出第一参考电流、第二参考电流和第三参考电流,并且在第二模式下以第二电流水平输出第一参考电流、第二参考电流和第三参考电流,第二电流水平低于第一电流水平。

11.根据示例实施例的一方面,提供了一种发光二极管(led)封装件,该led封装件包括:第一led芯片、第二led芯片和第三led芯片;以及位于第一led芯片、第二led芯片和第三led芯片上方或下方的第一像素驱动集成电路,第一像素驱动集成电路被配置为使用有源矩阵和脉冲宽度调制(pwm)驱动第一led芯片、第二led芯片和第三led芯片,其中,第一像素驱动集成电路还被配置为基于第一led芯片、第二led芯片和第三led芯片的亮度等于或大于阈值,以第一电流水平向第一led芯片、第二led芯片和第三led芯片提供驱动电流,并且被配置为基于第一led芯片、第二led芯片和第三led芯片的亮度小于阈值,以第二电流水平向第一led芯片、第二led芯片和第三led芯片提供驱动电流。

12.根据示例实施例的一方面,提供了一种显示设备,该显示设备包括:模块基板;按矩阵布置在模块基板上的多个发光二极管(led)封装件;以及被配置为控制多个led封装件的控制器,其中,多个led封装件中的每一个包括:封装件基板;位于封装件基板上的像素驱动集成电路;以及位于像素驱动集成电路上的第一led芯片、第二led芯片和第三led芯片,其中,像素驱动集成电路包括:电流调节器,其被配置为生成具有第一电流水平和第二电流水平中的一个的第一参考电流、第二参考电流和第三参考电流;以及led驱动器,其被配置为基于第一参考电流、第二参考电流和第三参考电流生成分别施加到第一led芯片、第二led芯片和第三led芯片并具有可变的脉冲宽度的第一驱动电流、第二驱动电流和第三驱动电流,并且其中,像素驱动集成电路被配置为进行控制以使得第一led芯片、第二led芯片和第三led芯片中的每一个的单位发出时间等于或大于第一led芯片、第二led芯片和第三led芯片的上升时间的80%。

附图说明

13.将从以下结合附图进行的详细描述更清楚地理解示例实施例,在附图中:

14.图1是示出根据示例实施例的发光二极管(led)封装件的示意图;

15.图2是根据示例实施例的led封装件中包括的像素驱动集成电路的电路图;

16.图3a是根据一些示例实施例的电流调节器的框图;

17.图3b是根据一些示例实施例的包括在电流调节器中的控制电压生成器和电压受控电流源的电路图;

18.图4a是根据一些示例实施例的电流调节器的框图;

19.图4b是根据一些示例实施例的包括在电流调节器中的控制电压生成器和电压受控电流源(vccs)的电路图;

20.图5a和图5b是用于描述根据一些示例实施例的像素驱动集成电路的操作的曲线图;

21.图6a、图6b、图6c、图6d、图6e和图6f是用于描述根据一些示例实施例的对驱动电流的控制的曲线图;

22.图7a、图7b、图7c、图7d和图7e是根据一些示例实施例的像素驱动集成电路的电路图;

23.图8a是示出根据一些示例实施例的led封装件的示图,图8b是图8a的led封装件的顶视图;

24.图9a是示出根据一些示例实施例的led封装件的示图,图9b是图9a的led封装件的顶视图;

25.图10是示出根据一些示例实施例的显示设备的示图;

26.图11是图10中的区域a的放大平面图;

27.图12是图10的显示设备的横截面图;

28.图13是根据一些示例实施例的显示设备的电路图;

29.图14是根据一些示例实施例的显示设备的电路图;

30.图15a是根据一些示例实施例的led封装件的平面图;

31.图15b是根据一些示例实施例的像素驱动集成电路的平面图;

32.图15c是根据一些示例实施例的像素驱动集成电路的电路图;

33.图16和图17是根据一些示例实施例的led封装件的平面图。

具体实施方式

34.在下文中,将参照附图详细描述根据本公开的某些实施例。

35.图1是示出根据示例实施例的发光二极管(led)封装件100的示意图。

36.参照图1,led封装件100包括第一led芯片310、第二led芯片320和第三led芯片330以及像素驱动集成电路400。led封装件100还可包括封装件基板200、外部连接端子220(诸如,焊料或凸块)以及密封构件500。尽管图1中示出led封装件100包括三个led芯片,但本公开不限于此。根据一些实施例,led封装件可包括至少四个led芯片。

37.根据一些示例实施例,第一led芯片310、第二led芯片320和第三led芯片330可发出不同颜色的光。例如,第一led芯片310可发出红光,第二led芯片320可发出绿光,第三led芯片330可发出蓝光。在这种情况下,led封装件100可以是红、绿、蓝(rgb)全色封装件。

38.根据一些示例实施例,第一led芯片310、第二led芯片320和第三led芯片330可发出相同颜色的光。例如,第一led芯片310、第二led芯片320和第三led芯片330中的每一个可以是被配置为发出白光的白色led芯片。在这种情况下,led封装件100可以是用于鲜艳颜色

的多白色封装件。

39.根据一些示例实施例,由第一led芯片310、第二led芯片320和第三led芯片330发出的光的颜色可包括各种颜色(诸如,蓝绿色、黄色和品红色)中的至少一种。

40.第一led芯片310、第二led芯片320和第三led芯片330可布置在像素驱动集成电路400的顶表面上,因此,从第一led芯片310、第二led芯片320和第三led芯片330发出的光可不被像素驱动集成电路400遮蔽。

41.像素驱动集成电路400可布置在第一led芯片310、第二led芯片320和第三led芯片330上方或下方,并且可使用有源矩阵来驱动第一led芯片310、第二led芯片320和第三led芯片330。这里,有源矩阵是在平板显示器中使用的一种类型的寻址方案。在使用有源矩阵的显示设备中,像素包括用于驱动像素的存储元件(例如,电容器)以及可根据信号编程的晶体管。可基于外部信号对一条扫描线上的像素进行编程约{(帧时间)

÷

(扫描线的数量)}的周期。像素中的每一个像素的电压由于其电容器得以维持,因此,每一个像素可在帧的剩余时间期间连续地发出光。当运动图像显示在显示器上时,运动按规则的间隔被分割并连续地显示。与一个帧对应的时间周期被称为帧时间。

42.像素驱动集成电路400可使用多模式脉冲宽度调制(pwm)来驱动第一led芯片310、第二led芯片320和第三led芯片330。像素驱动集成电路400可控制单个帧周期中的第一led芯片310、第二led芯片320和第三led芯片330的驱动电流的工作(on

‑

duty)时间,以控制第一led芯片310、第二led芯片320和第三led芯片330的亮度。

43.例如,素驱动集成电路400可在第一led芯片310、第二led芯片320和第三led芯片330显示高灰度(即,高亮度)时增加用于驱动第一led芯片310、第二led芯片320和第三led芯片330的电流的脉冲宽度(即,占空比),并且可在第一led芯片310、第二led芯片320和第三led芯片330显示低灰度(即,第亮度)时减小该电流的脉冲宽度。另一方面,脉冲幅度调制(pam)控制电流脉冲的幅度。与pam不同,pwm可防止电流低于第一led芯片310、第二led芯片320和第三led芯片330在低灰度下的可靠操作所需的水平。

44.根据一些实施例,像素驱动集成电路400可根据灰度(或亮度)使用pwm以另一模式驱动第一led芯片310、第二led芯片320和第三led芯片330。例如,由像素驱动集成电路400接收的帧数据可包括用于选择像素驱动集成电路400的模式的信号。

45.用于选择模式的信号可包括单个比特。在这种情况下,当灰度等于或大于阈值时,单个比特可为“1”,并且像素驱动集成电路400可在以第一电流水平执行pwm的第一模式下驱动第一led芯片310、第二led芯片320和第三led芯片330。当灰度低于阈值时,单个比特可为“0”,并且像素驱动集成电路400可在以低于第一电流水平的第二电流水平执行pwm的第二模式下驱动第一led芯片310、第二led芯片320和第三led芯片330。

46.第一电流水平和第二电流水平指非零的电流的大小。换言之,由像素驱动集成电路400供应给第一led芯片310、第二led芯片320和第三led芯片330的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3(位于图2中)可具有包括0[a]的至少三个水平。

[0047]

根据一些实施例,用于选择模式的信号可包括至少两个比特。因此,像素驱动集成电路400可使用pwm在至少四个模式下驱动第一led芯片310、第二led芯片320和第三led芯片330。例如,当用于选择模式的信号包括两个比特时,像素驱动集成电路400的驱动电流可使用pwm在四个不同的模式下操作。当用于选择模式的信号包括三个比特时,像素驱动集成

电路400的驱动电流可使用pwm在八个不同的模式下操作。

[0048]

像素驱动集成电路400可布置在封装件基板200上。在图1的实施例中,包括硅通孔(tsv)的各种布线结构可形成在像素驱动集成电路400中。像素驱动集成电路400可被配置为通过外部连接端子(诸如,焊料或凸块)电连接到封装件基板200。像素驱动集成电路400可包括用于封装件基板200和像素驱动集成电路400之间的连接的多个焊盘。焊盘可形成在像素驱动集成电路400的底表面上并且在图1中示出。焊盘可包括数据输入焊盘411(位于图2中)、时钟焊盘412(位于图2中)、电力焊盘413(位于图2中)、数据输出焊盘414(位于图2中)、地焊盘415(位于图2中)和辅助电力焊盘。

[0049]

在图1的实施例中,第一led芯片310、第二led芯片320和第三led芯片330可被实施为倒装芯片。详细地,第一led芯片310、第二led芯片320和第三led芯片330可通过至少一个电极连接到像素驱动集成电路400。另外,位于第一led芯片310、第二led芯片320和第三led芯片330上方或下方的像素驱动集成电路400可包括用于电连接到第一led芯片310、第二led芯片320和第三led芯片330的至少一个焊盘。第一led芯片310、第二led芯片320和第三led芯片330可通过导电粘合材料(诸如,共晶金属、糊剂或焊料)电连接到像素驱动集成电路400。

[0050]

封装件基板200可布置在像素驱动集成电路400上方或下方。像素驱动集成电路400和led像素的第一led芯片310、第二led芯片320和第三led芯片330可安装在封装件基板200上,并且可通过封装件基板200和外部印刷电路板(pcb)(图10中的1300)与外部控制器(图10中的1400)通信。

[0051]

封装件基板200可包括用于电连接到像素驱动集成电路400的多个焊盘。封装件基板200的焊盘可包括数据输入焊盘、时钟焊盘、电力焊盘、数据输出焊盘、地焊盘和辅助电力焊盘,并且可布置在封装件基板200和像素驱动集成电路400之间以不被暴露。粘合构件(诸如,环氧树脂、硅树脂、丙烯酸酯和/或糊剂)可位于像素驱动集成电路400和封装件基板200之间以将像素驱动集成电路400和封装件基板200彼此固定。

[0052]

像素驱动集成电路400和led像素的第一led芯片310、第二led芯片320和第三led芯片330可通过透明的密封构件500固定到封装件基板200。密封构件500可包括环氧树脂、硅树脂等。密封构件500还可包括诸如熔融石英或炭黑的填料。

[0053]

根据一些实施例,可通过以下步骤提供图1的led封装件100:准备封装件基板200;使用导电粘合材料和粘合构件将像素驱动集成电路400附接到封装件基板200;使用导电粘合材料将第一led芯片310、第二led芯片320和第三led芯片330接合到像素驱动集成电路400;使用密封构件500将封装件成型;以及锯切或单颗切割成型的封装件。

[0054]

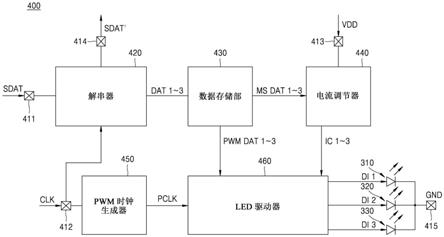

图2是包括在led封装件100中的像素驱动集成电路400的电路图。

[0055]

参照图2,像素驱动集成电路400包括多个焊盘(例如,数据输入焊盘411、时钟焊盘412、电力焊盘413、数据输出焊盘414和地焊盘415)、解串器420、数据存储部430、电流调节器440、pwm时钟生成器450和led驱动器460。

[0056]

解串器420可通过数据输入焊盘411从像素驱动集成电路400外部的控制器1400(位于图10中)接收串行数据sdat,可从串行数据sdat中提取针对第一led芯片310、第二led芯片320和第三led芯片330的帧数据,并且可基于帧数据输出第一驱动数据dat 1、第二驱动数据dat 2和第三驱动数据dat 3。

[0057]

根据一些实施例,帧数据可包括用于控制led驱动器460的第一pwm数据pwm dat 1、第二pwm数据pwm dat 2和第三pwm数据pwm dat 3以及用于选择操作模式的第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat3。根据一些实施例,第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3可包括单个比特。根据一些实施例,第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3可包括至少两个比特。例如,帧数据可包括图像信号的灰度数据,并且还可包括附加灰度数据以对像素的非预期的低效率和波长移位做出反应。

[0058]

除了与像素驱动集成电路400对应的帧数据之外,解串器420可输出而不处理串行数据sdat中的剩余的串行数据sdat’。剩余的串行数据sdat’可通过数据输出焊盘414被输出并被提供给随后的led封装件(例如,随后的扫描线的led封装件)。由于在显示设备1000(位于图10中)中多个led封装件彼此串联连接,所以针对单个帧周期的串行数据sdat可包括多个led封装件的帧数据。

[0059]

例如,第一扫描线的led封装件可仅获取针对自己的帧数据并将剩余的数据输出到第二扫描线的led封装件,并且第二扫描线的led封装件也可仅获取针对自己的帧数据并将剩余的数据输出到第三扫描线的led封装件。这样,第一扫描线至最后扫描线的相应led封装件中的每一个可获取针对自己的帧数据。

[0060]

数据存储部430可存储用于分别驱动第一led芯片310、第二led芯片320和第三led芯片330的第一驱动数据dat 1、第二驱动数据dat 2和第三驱动数据dat 3。在实施例中,数据存储部430可被实施为锁存器、寄存器、缓冲器等,并且可包括选自易失性存储器(诸如,静态随机存取存储器(sram)和动态ram(dram))和/或非易失性存储器(诸如,电可擦除可编程只读存储器(eeprom)、闪速存储器、相变ram(pram)、电阻ram(rram)、纳米浮栅存储器(nfgm)、聚合物ram(poram)、磁性ram(mram)和铁电ram(fram))中的至少一种。

[0061]

电流调节器440可通过电力焊盘413接收电源电压vdd,并且可基于电源电压vdd以及第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3生成第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3。根据一些实施例,电流调节器440可包括电流镜。

[0062]

pwm时钟生成器450可基于通过时钟焊盘412接收的时钟信号clk生成pwm时钟信号pclk。pwm时钟信号pclk的频率可小于时钟信号clk的频率,但不限于此。pwm时钟信号pclk的周期可大于时钟信号clk的周期,但不限于此。

[0063]

根据一些实施例,第一led芯片310、第二led芯片320和第三led芯片330的单位发出时间可以是第一led芯片310、第二led芯片320和第三led芯片330的上升时间的至少80%。根据一些实施例,第一led芯片310、第二led芯片320和第三led芯片330的单位发出时间可大于第一led芯片310、第二led芯片320和第三led芯片330的上升时间。根据一些实施例,单位发出时间可为至少约200ns。根据一些实施例,单位发出时间可为至少约300ns。根据一些实施例,单位发出时间可为至少约500ns。这里,单位发出时间表示第一led芯片310、第二led芯片320和第三led芯片330具有最低亮度的最短“开启”时间周期。上升时间是第一led芯片310、第二led芯片320和第三led芯片330的输出(例如,驱动电流的幅度或亮度)从目标值的10%增加至目标值的90%所花费的时间。

[0064]

根据一些实施例,第一led芯片310、第二led芯片320和第三led芯片330的单位发

出时间可等于或大于pwm时钟信号pclk的周期。根据一些实施例,第一led芯片310、第二led芯片320和第三led芯片330的单位发出时间可以是pwm时钟信号pclk的周期的n倍,其中n是至少为2的整数。

[0065]

led驱动器460可基于pwm时钟信号pclk、从数据存储部430提供的分发的帧数据(例如,第一pwm数据pwm dat 1、第二pwm数据pwm dat 2和第三pwm数据pwm dat 3)以及从电流调节器440提供的第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3生成分别施加到第一led芯片310、第二led芯片320和第三led芯片330的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3。

[0066]

可基于pwm来生成第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3。例如,第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3可具有分别基于第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3确定的电流水平,并且具有分别基于第一pwm数据pwm dat 1、第二pwm数据pwm dat 2和第三pwm数据pwm dat 3确定的脉冲宽度(例如,工作时间)。

[0067]

第一led芯片310、第二led芯片320和第三led芯片330中的每一个可包括从led驱动器460接收第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3中的对应一个的阳极以及连接到提供地电位gnd的地焊盘415的阴极。

[0068]

图3a是根据一些实施例的电流调节器440的框图。图3b是根据一些实施例的包括在电流调节器440中的第一控制电压生成器444和第一电压受控电流源(vccs)447的电路图。

[0069]

参照图3a,电流调节器440可包括第一电压调节器441、第二电压调节器442和第三电压调节器443、第一控制电压生成器444、第二控制电压生成器445和第三控制电压生成器446、第一vccs 447、第二vccs 448和第三vccs 449。

[0070]

第一电压调节器441、第二电压调节器442和第三电压调节器443可分别基于作为数字信号的第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3分别生成第一输入电压vin 1、第二输入电压vin 2和第三输入电压vin 3。第一输入电压vin 1、第二输入电压vin 2和第三输入电压vin 3可具有分别根据第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3的参考电位或设定电压(例如,1[v])。

[0071]

基于第一模式选择数据ms dat 1、第二模式选择数据ms dat2和第三模式选择数据ms dat 3中的每一个的比特数,第一输入电压vin 1、第二输入电压vin 2和第三输入电压vin 3中的每一个可包括分别输出到不同端的多个电压。详细地,当第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3中的每一个中的比特数为“n”时,第一输入电压vin 1、第二输入电压vin 2和第三输入电压vin 3中的每一个可包括分别输出到不同端的“n”个电压值。例如,第一电压调节器441、第二电压调节器442和第三电压调节器443可分别包括被配置为分别基于第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3生成第一输入电压vin 1、第二输入电压vin2和第三输入电压vin 3的串并转换器,其中,第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3中的每一个是串行数字比特流,并且第一输入电压vin 1、第二输入电压vin 2和第三输入电压vin 3中的每一个包括多个并行电压。

[0072]

根据一些实施例,第一电压调节器441、第二电压调节器442和第三电压调节器443中的每一个还可包括被配置为基于第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3(位于图2中)中的对应一个生成第一输入电压vin1、第二输入电压vin 2和第三输入电压vin 3中的对应一个的升压(step

‑

up)电路。例如,升压电路可包括增压转换器。

[0073]

第一控制电压生成器444、第二控制电压生成器445和第三控制电压生成器446可分别基于第一输入电压vin 1、第二输入电压vin2和第三输入电压vin 3生成第一输出电压vout 1、第二输出电压vout 2和第三输出电压vout 3。根据一些实施例,第一控制电压生成器444、第二控制电压生成器445和第三控制电压生成器446中的每一个可包括基于至少一个输入电压生成一个输出电压的放大器电路。

[0074]

第一vccs 447、第二vccs 448和第三vccs 449可分别基于第一输出电压vout 1、第二输出电压vout 2和第三输出电压vout 3输出第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3。第一vccs 447、第二vccs 448和第三vccs 449中的每一个可包括被配置为将在帧周期期间施加的第一输出电压vout 1、第二输出电压vout 2和第三输出电压vout 3中的对应一个维持恒定的电压维持元件(例如,电容器)。第一vccs 447、第二vccs 448和第三vccs 449中的每一个还可包括基于第一输出电压vout 1、第二输出电压vout 2和第三输出电压vout 3中的对应一个来控制第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3中的对应一个的大小的驱动元件(例如,晶体管)。

[0075]

参照图3b,第一控制电压生成器444可以是求和放大器,并且第一vccs 447可包括电容器cap和驱动晶体管dtr。第二控制电压生成器445和第三控制电压生成器446中的每一个可与第一控制电压生成器444基本上相同,第二vccs 448和第三vccs 449中的每一个可与第一vccs 447基本上相同。

[0076]

第一控制电压生成器444可包括分别施加有第一输入电压vin1_1、vin 1_2和vin 1_3的第一输入端ip1、第二输入端ip2和第三输入端ip3、运算放大器op、第一输入电阻器ra、第二输入电阻器rb和第三输入电阻器rc以及反馈电阻器rf。

[0077]

当第一模式选择数据ms dat 1以三比特表示时,第一输入电压vin 1_1、vin 1_2和vin 1_3是分别与三个比特对应的电压值。在下文中,描述第一输入电压vin 1_1、vin 1_2和vin 1_3具有值0[v]或1[v]的示例,但这仅是为了描述方便,而不以任何方式限制本发明构思。第一输入电压vin 1_1、vin 1_2和vin 1_3可具有电压值0[v]和随机非零电压值(例如,5[v])。

[0078]

第一输入电阻器ra、第二输入电阻器rb和第三输入电阻器rc可分别连接在第一输入端ip1、第二输入端ip2和第三输入端ip3与第一节点n1之间。参考电位可被施加到运算放大器op的非反相输入端,并且运算放大器op的反相输入端可连接到第一节点n1。反馈电阻器rf可连接在运算放大器op的反相输入端和输出端之间。

[0079]

运算放大器op的输出端、电容器cap的第一端和驱动晶体管dtr的栅电极可共同连接到一个节点(称为第二节点n2)。电容器cap的第二端和驱动晶体管dtr的源电极可连接到施加有电源电压vdd的第三节点n3。第一参考电流ic 1可根据施加到驱动晶体管dtr的栅电极的电压而具有不同的大小。第一参考电流ic 1可通过驱动晶体管dtr的漏电极输出到输出端opt。

1’、第二输入电压vin 2’和第三输入电压vin 3’中的每一个可具有单个电压电平。

[0094]

第一控制电压生成器444’、第二控制电压生成器445’和第三控制电压生成器446’可分别基于第一输入电压vin 1’、第二输入电压vin 2’和第三输入电压vin 3’生成第一输出电压vout 1、第二输出电压vout 2和第三输出电压vout 3。根据一些实施例,第一控制电压生成器444’、第二控制电压生成器445’和第三控制电压生成器446’中的每一个可包括基于一个输入电压生成一个输出电压的电压受控电压源。

[0095]

第一vccs 447、第二vccs 448和第三vccs 449与参照图3a和图3b描述的那些基本上相同,因此将省略其详细描述。

[0096]

参照图4b,第一控制电压生成器444’可包括输入端ip、分压器vd、第一运算放大器op1和第二运算放大器op2以及求和放大器sap’。

[0097]

分压器vd可包括串联连接在第一节点n1与第四节点n4之间的第一电阻器r1、第二电阻器r2和第三电阻器r3。地电位gnd可被施加到第一节点n1,电源电压vdd可被施加到第四节点n4。第一电阻器r1的第一端可连接到第一节点n1,第一电阻器r1的第二端可在第二节点n2处连接到第二电阻器r2的第一端。第二电阻器r2的第二端可在第三节点n3处连接到第三电阻器r3的第一端。第三电阻器r3的第二端可连接到第四节点n4。

[0098]

第一运算放大器op1和第二运算放大器op2可以是比较器。当输入端ip的第一输入电压vin 1’大于或等于第二节点n2的第二节点电压vn2时,第一运算放大器op1的第一输出电压vo1可等于第一供电电压vs1,并且当输入端ip的第一输入电压vin 1’小于第二节点n2的第二节点电压vn2时,第一运算放大器op1的第一输出电压vo1可等于地电位gnd。当输入端ip的第一输入电压vin 1’大于或等于第三节点n3的第三节点电压vn3时,第二运算放大器op2的第二输出电压vo2可等于第二供电电压vs2,并且当输入端ip的第一输入电压vin 1’小于第三节点n3的第三节点电压vn3时,第二运算放大器op2的第二输出电压vo2可等于地电位gnd。

[0099]

第二节点电压vn2和第三节点电压vn3可被表示为公式3。

[0100]

[公式3]

[0101][0102]

包括电阻器r和第三运算放大器op3的求和放大器sap’的第一输出电压vout 1可被表示为公式4。

[0103]

[公式4]

[0104]

vout1=

‑

vo1

‑

vo2

[0105]

表2示出根据第一输入电压vin 1’的范围的第一运算放大器op1、第二运算放大器op2和第三运算放大器op3的输出值。

[0106]

[表2]

[0107][0108]

在图4b的实施例中,第一输出电压vout 1可具有三个电压电平中的一个,因此,电流调节器440’可向输出端opt输出三个非零水平中的一个的第一参考电流ic 1。根据图4b的实施例,led封装件100(位于图1中)可基于电流的三个不同的水平中的对应一个在第一模式、第二模式和第三模式中的任一个模式下操作。

[0109]

图5a和图5b是用于描述根据一些实施例的像素驱动集成电路400(位于图2中)的操作的曲线图。详细地,图5a是示出在比较例中在使用单个电流水平的pwm期间的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3的曲线图;图5b是示出根据一些实施例的在多模式pwm期间的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3的曲线图。

[0110]

图5a和图5b示出用于在第i帧fr

i

和在第i帧fr

i

之后的第(i+1)帧fr

i+1

中显示相同的图像信息的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3的改变。

[0111]

参照图5a,根据现有技术的pwm方法通过在单个电流水平(即,第一电流水平il 1)下改变脉冲宽度来表示灰度。因此,当灰度分辨率增加时,在pwm控制下,与第一led芯片310、第二led芯片320和第三led芯片330的上升时间相比,第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的单位发出时间变得太短。

[0112]

例如,当关于灰度的数据包括16比特时(即,当灰度分辨率为2

16

时),与led的最小发出时间对应的单位发出时间为{(帧时间)

÷216

}[sec]。假设在使用led的显示设备中由单个控制器控制的线的数量为32并且刷新率为90hz,则帧时间为约0.347ms并且单位发出时间为约5.3ns。

[0113]

另一方面,led芯片的上升时间通常为几百ns,因此,当使用高灰度分辨率时,在根据现有技术的pwm控制下,与led芯片的上升时间相比,单位发出时间太短。因此,led芯片的闪烁的可靠性和操作led封装件的可靠性可能降低。

[0114]

参照图5b,根据示例实施例,当驱动像素时,像素驱动集成电路400使用有源矩阵控制方法和基于多个电流水平(例如,第一电流水平il 1和第二电流水平il 2)的pwm控制方法。当使用有源矩阵时,单位发出时间与受控制器控制的线的数量成正比地增加(例如,在线的数量为32的情况下,32倍)。

[0115]

单个帧中的led的亮度与表示led的电流随时间的曲线图的面积的大小成正比。因此,当表示低灰度时,可基于电流的低水平来调制驱动电流的脉冲宽度,因此,单位发出时间可增加。参照图5b,第二电流水平il 2约为第一电流水平il 1的1/3。当在图5a和图5b之间比较第(i+1)帧fri+1中的第一驱动电流di 1时,图5a中的脉冲宽度约为pwm时钟信号pclk的周期的一半,而图5b中的脉冲宽度约为pwm时钟信号pclk的周期的3/2。换言之,根据

示例实施例,led封装件100(位于图1中)的单位发出时间为约508ns,这比在现有技术中利用使用电流的单个水平的无源矩阵的情况下约5.3ns的单位发出时间大96倍,并且与第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的上升时间相比,led封装件100(位于图1中)的单位发出时间足够长。因此,led封装件100(位于图1中)可以可靠地操作。

[0116]

根据一些实施例,当灰度分辨率为2

n

时,第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的单位发出时间可被表示为公式5和6。

[0117]

[公式5]

[0118][0119]

[公式6]

[0120][0121]

在公式6中,n是至少为2的整数,n是根据电流调节器440(位于图2中)的第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3的电流水平而确定的。

[0122]

根据示例实施例,即使当led封装件100(位于图1中)使用高灰度分辨率并且输出低亮度光时,单位发出时间也足够长,因此,led封装件100(位于图1中)的操作可靠性可提高。

[0123]

图6a、图6b、图6c、图6d、图6e和图6f是用于描述根据一些实施例的驱动电流的控制的曲线图。图6a至图6d示出第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3(位于图2中)包括一比特并且第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3(位于图2中)具有两个电流水平的示例情况。图6e和图6f示出第一模式选择数据ms dat 1、第二模式选择数据ms dat 2和第三模式选择数据ms dat 3(位于图2中)包括两比特并且第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3(图2中)具有四个电流水平的示例情况。

[0124]

参照图6a,第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3(位于图2中)的大小可具有第一电流水平il1或第二电流水平il 2的值。根据一些实施例,当以第二电流水平il 2驱动第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)时第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的亮度ilu 2可以是当以第一电流水平il 1驱动时第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的亮度ilu 1的一半。

[0125]

参照图6b,当以第二电流水平il 2驱动第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)时第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的亮度ilu 2可等于或小于当以第一电流水平il 1驱动时第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的亮度ilu 1的一半。根据一些实施例,当以第二电流水平il 2驱动第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)时第一led芯片310、第二led芯片320和第三led芯片330(图1中)的亮度ilu 2可以是当以第一电流水平il 1驱动时第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)的亮度ilu 1的约30%至约50%。

[0126]

参照图6c,第二电流水平il 2可约为第一电流水平il 1的一半。

[0127]

参照图6d,第二电流水平il 2可等于或小于第一电流水平il 1的约50%。根据一些实施例,第二电流水平il 2可为第一电流水平il 1的约30%至约40%。

[0128]

参照图6e,第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3(位于图2中)的大小可具有第一至第四电流水平il 1、il2、il 3和il 4中的一个的值。根据一些实施例,当以第一至第四电流水平il 1、il 2、il 3和il 4顺序地驱动第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)中的每一个时,第一led芯片310、第二led芯片320和第三led芯片330(位于图1中)中的每一个可顺序地具有第一至第四亮度ilu 1、ilu 2、ilu3和ilu 4。根据一些实施例,第二亮度ilu 2可约为第一亮度ilu 1的一半。根据一些实施例,第三亮度ilu 3可约为第二亮度ilu 2的一半。根据一些实施例,第四亮度ilu 4可约为第三亮度ilu 3的一半。根据一些实施例,当与低灰度对应的电流水平被划分为多个水平时,可更有效地表示灰度。

[0129]

参照图6f,根据一些实施例,第二亮度ilu 2可约为第一亮度ilu 1的3/4,第三亮度ilu 3可约为第一亮度ilu 1的一半。根据一些实施例,第四亮度ilu 4可约为第一亮度ilu 1的1/4。

[0130]

尽管图6a至图6f中示出了控制驱动电流的各种形式,但是应该理解,本公开不限于上述示例。led芯片的驱动电流可具有各种数量和各种大小的电流水平以有效地表示不同的灰度。

[0131]

图7a、图7b、图7c、图7d和图7e是根据一些实施例的像素驱动集成电路400a、400b、400c、400d和400e的电路图。为了描述方便,将省略上面参照图2至图3b给出的冗余描述,并且描述将聚焦于与上述实施例的不同之处。

[0132]

参照图7a,与图2的像素驱动集成电路400相比,像素驱动集成电路400a还可包括静电放电(esd)保护电路445。除了esd保护电路445之外,图7a的像素驱动集成电路400a可与图2的像素驱动集成电路400基本上相同。

[0133]

esd保护电路445可连接到电力焊盘413。当发生esd事件导致大量电荷流入像素驱动集成电路400a中时,esd保护电路445可保护像素驱动集成电路400a内部的元件。esd保护电路445还可连接到地焊盘415。

[0134]

像素驱动集成电路400a还可包括连接到选自数据输入焊盘411、时钟焊盘412和数据输出焊盘414中的至少一个的esd保护电路。

[0135]

参照图7b,与图2的像素驱动集成电路400相比,像素驱动集成电路400b还可包括补偿器470。数据存储部430还可存储关于第一led芯片310、第二led芯片320和第三led芯片330的特性数据cdat。补偿器470可基于特性数据cdat生成选自占空比控制信号dcon和电流水平控制信号clcon中的至少一个以控制第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3。

[0136]

根据一些实施例,补偿器470可包括存储器功能。电流调节器440可基于电流水平控制信号clcon调节第一参考电流ic 1、第二参考电流ic 2和第三参考电流ic 3的大小。因此,可调节分别驱动第一led芯片310、第二led芯片320和第三led芯片330的第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3的大小。led驱动器460可基于占空比控制信号dcon调节第一驱动电流di 1、第二驱动电流di 2和第三驱动电流di 3的占空比以适合于

第一led芯片310、第二led芯片320和第三led芯片330的特性。在实施例中,补偿器470可被包括在数据存储部430中或电流调节器440和led驱动器460中的每一个中。

[0137]

参照图7c,与图2的像素驱动集成电路400相比,像素驱动集成电路400c还可包括检测器480。

[0138]

当在第一led芯片310、第二led芯片320和第三led芯片330中的至少一个中发生电异常时,检测器480可检测电异常并生成故障检测信号fds。例如,电异常可包括第一led芯片310、第二led芯片320和第三led芯片330与像素驱动集成电路400c之间的非预期的短路或开路。

[0139]

根据一些实施例,故障检测信号fds可被反馈给外部控制器(例如,图10中的控制器1400)。在这种情况下,外部控制器可基于故障检测信号fds限制第一led芯片310、第二led芯片320和第三led芯片330的操作。像素驱动集成电路400c还可包括用于将故障检测信号fds提供给外部控制器的反馈焊盘。

[0140]

根据一些实施例,故障检测信号fds可被反馈给数据存储部430,并且数据存储部430可基于故障检测信号fds限制(例如,掩蔽)第一led芯片310、第二led芯片320和第三led芯片330的操作。

[0141]

根据一些实施例,故障检测信号fds可被反馈给led驱动器460,并且led驱动器460可基于故障检测信号fds限制第一led芯片310、第二led芯片320和第三led芯片330的操作。

[0142]

参照图7d,与图2的像素驱动集成电路400不同,像素驱动集成电路400d还可包括振荡器490。因此,像素驱动集成电路400d不包括时钟焊盘412(位于图2中)和pwm时钟生成器450(位于图2中)。

[0143]

由解串器420分发的帧数据还可包括时钟数据clk dat。振荡器490可基于时钟数据clk dat生成时钟信号clk和pwm时钟信号pclk。

[0144]

根据一些实施例,振荡器490可包括环形振荡器、rc振荡器、晶体振荡器或温度补偿晶体振荡器,但不限于此。

[0145]

参照图7e,与图2的像素驱动集成电路400不同,像素驱动集成电路400e还可包括被配置为接收pwm时钟信号pclk的时钟焊盘410。因此,像素驱动集成电路400e不包括pwm时钟生成器450(图2中)。

[0146]

图8a是示出根据一些实施例的led封装件101的示图。图8b是图8a的led封装件101的顶视图。

[0147]

为了描述方便,将省略上面参照图1给出的冗余描述,并且描述将聚焦于与上述实施例的不同之处。

[0148]

参照图8a和图8b,led封装件101可包括封装件基板201、第一led芯片310、第二led芯片320和第三led芯片330、像素驱动集成电路401、密封构件500以及多条接合引线bw1、bw2、bw3、bw4、bw5和bw6。

[0149]

图8a和图8b所示的封装件基板201和像素驱动集成电路401可使用引线接合方法彼此连接。与图1中的封装件基板200不同,封装件基板201可包括多个焊盘211至216,多个焊盘211至216分别电连接到像素驱动集成电路401的多个焊盘411至416并且与像素驱动集成电路401水平分离。封装件基板201的焊盘可包括数据输入焊盘211、时钟焊盘212、电力焊盘213、数据输出焊盘214、地焊盘215和辅助电力焊盘216。

[0150]

与图1中的像素驱动集成电路400不同,像素驱动集成电路401可电连接到封装件基板201,并且可包括位于其顶表面(即,像素驱动集成电路401的与面向封装件基板201的表面相对的表面)上的多个焊盘。例如,像素驱动集成电路401的焊盘可包括数据输入焊盘411、时钟焊盘412、电力焊盘413、数据输出焊盘414、地焊盘415和辅助电力焊盘416。

[0151]

封装件基板201的数据输入焊盘211、时钟焊盘212、电力焊盘213、数据输出焊盘214、地焊盘215和辅助电力焊盘216可分别通过接合引线bw1至bw6分别连接到像素驱动集成电路401的数据输入焊盘411、时钟焊盘412、电力焊盘413、数据输出焊盘414、地焊盘415和辅助电力焊盘416。例如,接合引线bw1可将数据输入焊盘411连接到数据输入焊盘211,接合引线bw2可将时钟焊盘412连接到时钟焊盘212,接合引线bw3可将电力焊盘413连接到电力焊盘213,接合引线bw4可将数据输出焊盘414连接到数据输出焊盘214,接合引线bw5可将地焊盘415连接到地焊盘215,接合引线bw6可将辅助电力焊盘416连接到辅助电力焊盘216。

[0152]

图9a是示出根据一些实施例的led封装件102的示图。图9b是图9a的led封装件102的顶视图。

[0153]

为了描述方便,将省略上面参照图1、图8a和图8b给出的冗余描述,并且描述将聚焦于与上述实施例的不同之处。

[0154]

参照图9a和图9b,led封装件102可包括封装件基板202、第一led芯片311、第二led芯片321和第三led芯片331、像素驱动集成电路402、密封构件500以及多条接合引线bw11、bw12、bw13、bw14、bw15、bw16、bw21、bw22、bw23、bw24和bw25。

[0155]

图9a和图9b所示的封装件基板202和像素驱动集成电路402可使用引线接合方法彼此连接。第一led芯片311、第二led芯片321和第三led芯片331可包括外延向上(epi

‑

up)芯片(即,非倒装芯片),因此可通过引线接合连接到像素驱动集成电路402。

[0156]

封装件基板202可与图8a和图8b中的封装件基板201基本上相同。

[0157]

与图8a和图8b中的像素驱动集成电路401不同,像素驱动集成电路402还可包括分别用于电连接到第一led芯片311、第二led芯片321和第三led芯片331的第一焊盘491、第二焊盘492和第三焊盘493。

[0158]

接合引线bw11、bw12、bw13、bw14、bw15和bw16将封装件基板202电连接到像素驱动集成电路402。接合引线bw21、bw22、bw23、bw24和bw25将第一led芯片311、第二led芯片321和第三led芯片331电连接到像素驱动集成电路402。

[0159]

接合引线bw21可将第一led芯片311连接到第一焊盘491,接合引线bw22可将第二led芯片321连接到第二焊盘492,接合引线bw24可将第三led芯片331连接到第三焊盘493,接合引线bw23和bw25可将第二led芯片321和第三led芯片331连接到地焊盘415。尽管未详细示出,第一led芯片311可通过电极直接连接到地焊盘415。

[0160]

图10是示出根据一些实施例的显示设备1000的示图。图11是图10中的区域a的放大平面图。图12是图10的显示设备1000的横截面图。图13是显示设备1000的电路图。

[0161]

参照图10,显示设备1000包括led模块1200、pcb 1300和控制器1400,led模块1200包括多个led封装件1100。

[0162]

pcb 1300被称为模块基板,并且可包括用于led封装件1100与控制器1400之间连接的复杂内部布线。

[0163]

led封装件1100可布置在pcb 1300的第一表面上,并且可与图1、图8a和图9a分别

所示的led封装件100、101和102中的一个相对应。led封装件1100可分别形成显示设备1000的像素,并且可在pcb 1300上在x轴和y轴方向上按行和列布置。尽管在图10中显示设备1000包括按照15

×

15矩阵布置的led封装件1100,但实施例不限于此。根据要实现的分辨率,显示设备1000可包括随机数量和布置方式(例如,1024

×

768或1920

×

1080)的led封装件。

[0164]

控制器1400布置在与pcb 1300的第一表面相对的第二表面上并且控制led封装件1100的操作。例如,控制器1400可提供用于驱动包括在led封装件1100中的每一个中的像素驱动集成电路的信号和电力。尽管图10中仅示出一个控制器1400,但实施例不限于此,多个控制器可设置在pcb 1300的第二表面上。可基于led封装件1100的总数和可由一个控制器1400驱动的led封装件1100的数量确定控制器的数量。

[0165]

参照图11,显示设备1000还可包括限定pcb 1300上布置led封装件1100的区域的第一屏障结构1210。另外,led封装件1100中的每一个可由第二屏障结构1220包围。led封装件1100可通过第二屏障结构1220彼此电隔离并且作为单独的像素彼此独立地被驱动。根据一些实施例,第一屏障结构1210和第二屏障结构1220可包括黑色矩阵,但不限于此。

[0166]

参照图12,一行或一列中的led封装件1100可通过pcb 1300的引线1310彼此串联连接。因此,led封装件1100中的每一个可在从控制器1400发送的串行数据当中仅获取自己的帧数据并将剩余的串行数据传送至led封装件1100中的随后一个。

[0167]

参照图13,控制器1400可包括输入焊盘c1、c2、c3、c4、...、时钟焊盘clp、电力焊盘vdp、地焊盘gp和辅助电力焊盘vip。

[0168]

输入焊盘c1、c2、c3、c4、...中的每一个可向不同列中的像素驱动集成电路400中的一个的输入焊盘411提供驱动信号。时钟焊盘clp可向像素驱动集成电路400中的每一个的时钟焊盘412提供时钟信号。电力焊盘vdp可向像素驱动集成电路400中的每一个的电力焊盘413提供驱动电流,并且可设置多个电力焊盘vdp以防止电压降。地焊盘gp可向像素驱动集成电路400中的每一个的地焊盘415提供地电位。辅助电力焊盘vip可向像素驱动集成电路400中的每一个的辅助电力焊盘416提供驱动电力,并且可设置多个辅助电力焊盘vip以防止电压降。

[0169]

图14是根据一些实施例的(图10的)显示设备1000的电路图。

[0170]

为了描述方便,将省略上面参照图13给出的冗余描述,并且描述将聚焦于与上述实施例的不同之处。

[0171]

参照图14,控制器1400’可包括输入焊盘c11、c12、c21、c22、c31、c32、c41、c42、...、时钟焊盘clp、电力焊盘vdp、地焊盘gp以及辅助电力焊盘vip。

[0172]

如下所述,像素驱动集成电路403中的每一个可包括多个数据输入焊盘和多个数据输出焊盘。因此,单个像素驱动集成电路可控制两个像素。例如,输入焊盘c11和c12可向第一列中的像素驱动集成电路403提供串行数据,输入焊盘c21和c22可向第二列中的像素驱动集成电路403提供串行数据,输入焊盘c31和c32可向第三列中的像素驱动集成电路403提供串行数据,并且输入焊盘c41和c42可向第四列中的像素驱动集成电路403提供串行数据。

[0173]

图15a是根据一些实施例的led封装件103的平面图。图15b是根据一些实施例的像素驱动集成电路403的平面图,并且示出位于像素驱动集成电路403的背面上的焊盘411至

418。图15c是根据一些实施例的像素驱动集成电路403的电路图。

[0174]

参照图15a,led封装件103可包括封装件基板203和像素驱动集成电路403。封装件基板203可类似于图1中的封装件基板200。下面将参照图15b和图15c描述像素驱动集成电路403。与图1中的led封装件100不同的是,led封装件103可包括六个led芯片,即,第一至第六led芯片310、320、330、340、350和360。图15a的led封装件103可具有包括由一个像素驱动集成电路403驱动的两个像素的二合一结构。

[0175]

参照图15b和图15c,像素驱动集成电路403可类似于图2中的像素驱动集成电路400,并且还可包括数据输入焊盘417和数据输出焊盘418。因此,解串器423可接收第一串行数据sdat 1和第二串行数据sdat 2,提取针对第一至第六led芯片310、320、330、340、350和360的帧数据,并且分发和输出帧数据。

[0176]

数据存储部433可存储分发的帧数据。例如,数据存储部433可存储分发的帧数据当中的分别针对第一至第六led芯片310、320、330、340、350和360的驱动数据dat 1~6。

[0177]

电流调节器473可通过电力焊盘413接收电源电压vdd,并基于电源电压vdd和第一至第六模式选择数据ms dat 1~6生成第一至第六参考电流ic 1~6。根据一些实施例,电流调节器473可包括电流镜。

[0178]

led驱动器463可基于pwm时钟信号pclk、从数据存储部433提供的分发的帧数据(例如,第一至第六pwm数据pwm dat1~6)以及从电流调节器473提供的第一至第六参考电流ic 1~6生成分别施加到第一至第六led芯片310、320、330、340、350和360的第一至第六驱动电流di 1、di 2、di 3、di 4、di 5和di 6。

[0179]

可基于pwm来生成第一至第六驱动电流di 1、di 2、di 3、di4、di 5和di 6。例如,第一至第六驱动电流di 1、di 2、di 3、di 4、di 5和di 6可具有分别基于第一至第六模式选择数据ms dat 1~6确定的第一至第六电流水平,并且具有分别基于第一至第六pwm数据pwm dat 1~6确定的脉冲宽度(例如,工作时间)。

[0180]

第一至第六led芯片310、320、330、340、350和360中的每一个可包括从led驱动器463接收第一至第六驱动电流di 1、di 2、di 3、di 4、di 5和di 6中的对应一个的阳极以及连接到提供地电位gnd的地焊盘415的阴极。第一led芯片310、第二led芯片320和第三led芯片330可形成一个像素,并且第四至第六led芯片340、350和360可形成另一像素。

[0181]

图16和图17是根据一些实施例的led封装件104和105的平面图。

[0182]

为了描述方便,将省略上面参照图1给出的冗余描述,并且描述将聚焦于与上述实施例的不同之处。

[0183]

参照图16,led封装件104可包括封装件基板204、像素驱动集成电路404以及第一led芯片310、第二led芯片320和第三led芯片330。

[0184]

封装件基板204、像素驱动集成电路404以及第一led芯片310、第二led芯片320和第三led芯片330可类似于图1中的封装件基板200、像素驱动集成电路400以及第一led芯片310、第二led芯片320和第三led芯片330。与图1的led封装件100不同的是,图16的led封装件104可包括多个像素驱动集成电路404。像素驱动集成电路404中的每一个可作为单独的像素操作其上的第一led芯片310、第二led芯片320和第三led芯片330。led封装件104可包括两个像素驱动集成电路404,因此,led封装件104可包括两个像素。

[0185]

参照图17,led封装件105可包括封装件基板205、像素驱动集成电路405以及第一

至第六led芯片310、320、330、340、350和360。

[0186]

封装件基板205、像素驱动集成电路405以及第一至第六led芯片310、320、330、340、350和360可类似于图15a中的封装件基板203、像素驱动集成电路403以及第一至第六led芯片310、320、330、340、350和360。与图15a的封装件基板203不同的是,图17的封装件基板205可包括多个(例如,两个)像素驱动集成电路405。因此,led封装件105可包括四个像素。

[0187]

如上面参照图15a至图17描述的,led封装件中可包括不同数量的像素驱动集成电路,并且像素驱动集成电路中的每一个可驱动不同数量的像素(即,至少三个led芯片)。换言之,基于本文的描述,本领域技术人员可实现包括m个像素驱动集成电路(其中m是至少为1的整数)的led封装件,每个像素驱动集成电路驱动n个像素(其中n是至少为1的整数)。

[0188]

尽管已经具体地示出和描述了示例实施例,但是将理解,在不脱离权利要求的精神和范围的情况下,可对示例实施例在形式和细节上进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1