测试结构、测试电路、显示面板及显示装置的制作方法

1.本发明一般涉及显示技术领域,具体涉及一种测试结构、测试电路、显示面板及显示装置。

背景技术:

2.oled(organic light

‑

emitting diode,有机发光二极管)显示产品以其自发光、低功耗、轻薄、色彩绚丽、对比度高、响应速率快等优点,具有广阔的应用前景,而高屏占比逐渐成为oled屏幕的主流发展趋势。

3.为了让屏幕“点亮”,需要将屏幕连接显示驱动ic、fpc排线。目前主流的屏幕的封装工艺主要有三种,分别为cog(chip on glass)、cof(chip on film)、cop(chip on panel),其中cof相比cog可缩减屏幕的“下巴”,cof是cog技术的升级;cop应用于柔性oled,相比cof封装可最大限度缩减屏幕的“下巴”,但是cop的成本高、良品率低,故当前oled屏幕的封装采用cof技术或cop技术。

4.cof技术先进行cof绑定工艺(cof bonding)将固定有ic的柔性线路板连接屏幕,再进行fof绑定工艺(fpc on fpc bonding)将固定有ic的柔性线路板与另一个柔性线路板相连。

5.cop技术先进行cop绑定工艺(cop bonding)将ic连接屏幕,再进行fop绑定工艺(fpc on panel bonding)将fpc连接屏幕。

6.为提升oled产品的良品率,对于cof bonding(或cop bonding)工艺,会通过电阻值来评估cof bonding(或cop bonding)工艺的导通效果,但是目前由于fof bonding电阻(或fop bonding电阻)、fpc线路阻抗、panel线路阻抗等因素的干扰,导致无法准确地监控cof bonding(或cop bonding)工艺的导通效果。

技术实现要素:

7.鉴于现有技术中的上述缺陷或不足,期望提供一种测试结构、测试电路、显示面板及显示装置。

8.第一方面,本发明提供一种测试结构,包括:第一支路,包括依次串联的第一线路、第二线路和第三线路;以及

9.第二支路,包括依次串联的第四线路、第五线路和第六线路;

10.所述第二线路和所述第五线路分别包括至少两个串联的第一绑定电阻,位于所述第二线路两端的第一绑定电阻的其中之一和位于所述第五线路两端的第一绑定电阻的其中之一为同一个电阻,并设定为待测电阻;

11.所述第一线路、所述第三线路、所述第四线路和所述第六线路分别包括一个或多个串联的第二绑定电阻;

12.所述第一支路用于通过所述第一线路远离所述第二线路的端部和所述第三线路远离所述第二线路的端部来耦接恒流源;

13.所述第二支路用于通过所述第四线路远离所述第五线路的端部和所述第六线路远离所述第五线路的端部来耦接电压表。

14.可选地,测试结构还包括:多条第一走线、多条第二走线和多条第三走线,所述第一走线、所述第二走线和所述第三走线互不相连;

15.所述第二线路和所述第一线路之间、所述第二线路和所述第三线路之间、所述第五线路和所述第四线路之间以及所述第五线路和所述第六线路之间分别通过所述第一走线连接,每条所述第一走线的两端分别连接一个所述第一绑定电阻和一个所述第二绑定电阻;

16.串联的两个所述第一绑定电阻之间通过所述第二走线连接;

17.所述第三走线与所述第二绑定电阻相连。

18.进一步地,所述第一绑定电阻为芯片的连接凸块与显示面板的第一连接端子之间的绑定电阻;

19.所述第二绑定电阻为柔性电路板的金手指与显示面板的第二连接端子之间的绑定电阻。

20.进一步地,所述第一走线为面板走线,所述第二走线为ic走线,所述第三走线为fpc走线。

21.进一步地,所述第一绑定电阻为柔性电路板一端的金手指与显示面板的连接端子之间的绑定电阻;

22.所述第二绑定电阻为所述柔性电路板另一端的金手指与另一柔性电路板的金手指之间的绑定电阻。

23.进一步地,所述第一走线为cof走线,所述第二走线为面板走线,所述第三走线为fpc走线。

24.第二方面,本发明提供一种测试电路,包括如第一方面所述的测试结构、恒流源和电压表,所述恒流源的两端分别与所述测试结构的第一线路和所述测试结构的第三线路耦接,所述电压表的两端分别与所述测试结构的第四线路和所述测试结构的第六线路耦接。

25.可选地,所述第一线路和所述第三线路分别通过第三走线耦接所述恒流源,所述第四线路和所述第六线路分别通过第三走线耦接所述电压表。

26.第三方面,本发明提供一种显示面板,包括如第一方面所述的测试结构。

27.第四方面,本发明提供一种显示装置,包括如第三方面所述的显示面板。

28.本发明的实施例提供的技术方案可以包括以下有益效果:

29.本发明实施例提供的测试结构、测试电路、显示面板及显示装置,第一支路用来连接恒流源以测出待测电阻的电流,第二支路用来连接电压表,第二支路并联待测电阻可直接测出待测电阻的电压,排除cof bonding或cop bonding工艺之外的影响因素(fof或fop bonding电阻、fpc线路阻抗、panel线路阻抗),如此可准确测得cof bonding或cop bonding的电阻,从而能准确表征cof bonding或cop bonding的导通效果。

附图说明

30.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

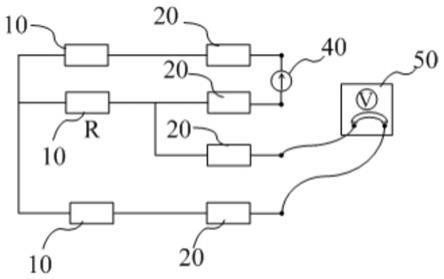

31.图1为现有技术提供的测试电路的结构示意图;

32.图2为本发明实施例提供的一种封装产品的结构示意图;

33.图3为图2所示封装产品的另一视角的结构示意图;

34.图4为本发明实施例提供的一种绑定区的结构示意图;

35.图5为本发明实施例提供的测试结构的结构示意图;

36.图6为本发明实施例提供的另一种封装产品的示意图;

37.图7为图6所示封装产品的另一视角的结构示意图;

38.图8为本发明实施例提供的测试电路的结构示意图。

具体实施方式

39.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的线路。

40.需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本发明。

41.对于cof或cog封装工艺,oled显示面板的绑定区与cof或cog的接线通过各向异性导电胶(anisotropic conductive film,acf胶)电连接。为确保oled产品的良品率,会对绑定区的绑定电阻的阻值进行测试来表征绑定区的导通效果。

42.图1为现有技术提供的测试电路的结构示意图。现有技术通过该测试电路u/i测得的阻值来表征cof bonding(或cog bonding)的电阻r1。

43.参照图2至图4,本发明实施例提供的一种封装产品。该封装产品采用cop技术封装,通过cop bonding工艺将芯片(ic)的金属凸块和面板(panel)的第一连接端子绑定连接,并通过fop bonding工艺将柔性电路板(fpc)的金手指和panel的第二连接端子绑定连接;

44.其中,cop bonding的过程中,通过acf胶将ic的金属凸块与panel的连接端子连接,通过acf中的导电离子将ic和panel导通,ic和panel之间的绑定电阻不大于设定电阻值时,方可确保ic和panel之间的acf胶的导电性能满足需求,从而保证显示产品的绑定良率。

45.结合图2,若图1示意的测试电路应用于cop技术,图1中第一电阻1表示cop bonding的电阻,第二电阻2表示fop bonding的电阻,u/i得到的阻值并不能准确表征cop bonding的导通效果。若该测试电路应用在cof技术中,同样不能准确表征cof bonding的导通效果。

46.故本发明实施例提供一种测试结构,通过该结构测得的阻值能够准确的表征cop bonding或cof bonding的导通效果。

47.如图5所示,本发明实施例提供的测试结构包括:

48.第一支路,包括依次串联的第一线路21、第二线路11和第三线路22;

49.第二支路,包括依次串联的第四线路23、第五线路12和第六线路24,第二线路11和第五线12路分别包括至少两个串联的第一绑定电阻10,第一线路21、第三线路22、第四线路23和第六线路24分别包括一个或多个串联的第二绑定电阻20;

50.位于第二线路11两端的第一绑定电阻的其中之一和位于第五线路两端22的第一

绑定电阻的其中之一为同一个电阻,并设定为待测电阻r;

51.第一支路用于通过第一线路21远离第二线路11的端部和第三线路22远离第二线路11的端部来耦接恒流源;

52.第二支路用于通过第四线路23远离第五线路12的端部和第六线路24远离第五线路12的端部来耦接电压表。

53.该实施例中,“多个”相对于“一个”,“多个”包括两个及两个以上。

54.为了适应各种阻值的待测电阻,恒流源具有多个档位电流,例如10ma、100ma、1a、20a四个切换档位电流;第一支路用于连接恒流源,能够测得流经待测电阻r的电流,第二支路用于连接电压表,实现电压表并联待测电阻r,从而测得电阻r两端的电压,该测试结构能够用来准确测出待测电阻的阻值,即可用来准确表征cop bonding或cof bonding的导通效果。

55.其中,测试结构还包括多条第一走线31、多条第二走线32和多条第三走线33,第一走线31、第二走线32和第三走线33互不相连;

56.第二线路11和第一线路21之间、第二线路11和第三线路22之间、第五线路12和第四线路23之间以及第五线路12和第六线路24之间分别通过第一走线31连接,每条第一走线31的两端分别连接一个第一绑定电阻10和一个第二绑定电阻20;

57.串联的两个第一绑定电阻10之间通过第二走线21连接;

58.第三走线33与第二绑定电阻20相连。

59.由于第一走线、第二走线和第三走线互不相连,故电压表不能直接并联待测电阻,通过第一走线、第二走线和第三走线将第一绑定电阻、第二绑定电阻连接以构成第一支路和第二支路,通过第一支路连接恒流源,通过第二支路连接电压表实现电压表并联待测电阻。

60.如图2至图4所示,本发明实施例提供一种封装产品,该产品为cop产品,芯片(ic)和柔性电路板(fpc)分别绑定面板(panel),cop绑定区与fop绑定区之间通过显示面板的面板走线相连。

61.参照图2至图4,图5中第一绑定电阻10为cop绑定区中芯片的连接凸块与显示面板的第一连接端子之间的绑定电阻;第二绑定电阻20为fop绑定区中柔性电路板的金手指与显示面板的第二连接端子之间的绑定电阻;第一走线31为面板走线,第二走线32为ic走线,第三走线33为fpc走线。

62.该实施例中,优选第二线路11、第五线路12分别包括两个第一绑定电阻10,第二线路11和第五线路12中含有一个共同的电阻,即待测电阻,优选第一线路21、第三线路22、第四线路23和第六线路24分别包括一个第二绑定电阻20。该测试结构中第一绑定电阻和第二绑定电阻的数量最简化,布线简单不冗杂,可用于准确测出cop bonding的导通电阻。

63.如图6和图7所示,本发明实施例提供另一种封装产品,该产品为cof产品,置有ic的fpc绑定panel,且置有ic的fpc还绑定另一fpc。

64.参照图6和图7,图5中第一绑定电阻10为cof bonding中置于芯片的柔性电路板一端的金手指与显示面板的连接端子之间的绑定电阻;

65.第二绑定电阻20为fof bonding中置于芯片的柔性电路板另一端的金手指与另一柔性电路板的金手指之间的绑定电阻;第一走线31为cof走线,第二走线32为面板走线,第

三走线33为fpc走线。

66.本发明实施例还提供一种测试电路,包括上述测试结构、恒流源40和电压表50,恒流源40的两端分别与测试结构的第一线路21和测试结构的第三线路22耦接,电压表50的两端分别与测试结构的第四线路23和测试结构的第六线路24耦接。

67.通过恒流源测得流经待测电阻的电流,通过电压表测得待测电阻两端的电压,如此可直接测得待测电阻的阻值,准确监控cof bonding或cop bonding的导通效果。

68.进一步地,第一线路21和第三线路22分别通过第三走线33耦接恒流源40,第四线路23和第六线路24分别通过第三走线33耦接电压表50。

69.若第一线路或第三走线包括多个第二绑定电阻,则第三走线串联多个第二绑定电阻,且第三走线连接恒流源。

70.若第四线路或第六线路包括多个第二绑定电阻,则第三走线串联多个第二绑定电阻,且第三走线连接电压表。

71.参照图8,该测试电路应用在cop产品中时,fpc作为信号输入端,ic作为信号输出端;该测试电路应用在cof产品中时,置有ic的fpc为信号输出端,与置有ic的fpc相连的另一fpc作为信号输入端。

72.本发明实施例还提供一种显示面板,包括上述测试结构。

73.该实施例中,显示面板适用于采用cof工艺或cop工艺封装制成的oled屏。

74.本发明实施例还提供一种显示装置,包括上述显示面板。

75.本发明对于显示装置的适用不做具体限制,其可以是电视机、笔记本电脑、平板电脑、手机、电子书、可穿戴显示设备、车载显示、广告灯箱等任何具有显示功能的产品或部件。

76.本发明采用第一、第二等来描述各种信息,但这些信息不应局限于这些术语。这些术语仅用来将同一类型的信息彼此区分开。例如在不脱离本发明范围的情况下,第一信息也可以被称为第二信息,类似地,第二信息也可以被称为第一信息。

77.以上描述仅为本发明的较佳实施例以及对所运用技术原理的说明。本领域技术人员应当理解,本发明中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本发明中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1