控制电路及其驱动方法、显示装置与流程

1.本技术属于显示技术领域,尤其涉及一种控制电路及其驱动方法、显示装置。

背景技术:

2.tft

‑

lcd(thin film transistor liquid crystal display,薄膜晶体管液晶显示器)是当前显示面板的主要品种之一,已经成为了现代it、视讯产品中重要的显示平台。

3.tft

‑

lcd中的存储器在烧录时,需要接入电源才能进行工作,但是,一般不知道存储器与tft

‑

lcd中的内部电源是否连接,所以通常会外接一个电源给存储器提供电源。但是,若存储器与内部电源是相连接的,而外部又提供电源时,两电源将处于短接的状态,这样就会产生电流,严重时可能会导致存储器被烧毁。由此,亟待一种电路可以避免上述短接问题。

技术实现要素:

4.本技术实施例提供了一种控制电路及其驱动方法、显示装置,通过在存储器的外围增加开关子电路,开关子电路在第一电压端输入第一电压时断开,而在第一电压端没有输入时导通,使得第二电压端输入第二电压,从而避免第一电压端和第二电压端之间同时提供电压时短接,烧毁存储器的问题。

5.为达到上述目的,本技术采用如下技术方案:

6.第一方面,提供了一种控制电路,包括:具有第一端的存储器、开关子电路,以及第一电压端和第二电压端;所述第一端与所述第一电压端连接,所述开关子电路分别与所述第一端、所述第一电压端和第二电压端均连接;当所述第一电压端提供第一电压时,所述开关子电路断开,所述第一电压输入所述第一端;当所述第一电压端未提供所述第一电压时,所述开关子电路导通,将所述第二电压端提供的第二电压输入所述第一端。

7.本技术实施例提供的控制电路,通过在存储器的外围增加开关子电路,开关子电路在第一电压端输入第一电压时断开,而在第一电压端没有输入时导通,使得第二电压端输入第二电压。由此,通过开关子电路在关闭和导通之间进行切换,可以使得第一电压端和第二电压端分开提供电压给存储器,从而避免第一电压端和第二电压端之间同时提供电压时短接,烧毁存储器的问题。

8.可选地,作为一种可能实现的方式,所述开关子电路包括:第一晶体管和第一电阻;所述第一晶体管的栅极、源极均与所述第一电压端连接,所述第一晶体管的漏极与所述第二电压端连接;所述第一电阻的一端与所述栅极连接,另一端与接地端连接。

9.可选地,作为一种可能实现的方式,所述第一晶体管为p沟道金属氧化物半导体场效应晶体管。

10.第二方面,提供了一种控制电路,包括:具有第一端、第二端和第三端的存储器;所述第一端与第二电压端连接,所述第二端与第一电压端连接,所述第三端与接地子电路连接;所述存储器中还包括开关子电路,所述开关子电路分别与所述第一端、所述第二端和所

述第三端连接;当所述第一电压端提供第一电压时,所述开关子电路断开,所述第一电压输入所述第二端;当所述第一电压端未提供所述第一电压时,所述开关子电路导通,所述第二电压输入所述第一端。

11.本技术实施例提供的控制电路,通过在存储器的内部增加开关子电路,开关子电路在第一电压端输入第一电压时断开,而在第一电压端没有输入时导通,使得第二电压端输入第二电压。由此,通过开关子电路在关闭和导通之间进行切换,可以使得第一电压端和第二电压端分开提供电压给存储器,从而避免第一电压端和第二电压端之间同时提供电压时短接,烧毁存储器的问题。

12.可选地,作为一种可能实现的方式,所述开关子电路包括:第一晶体管;

13.所述第一晶体管的栅极、源极均与所述第一端连接,所述第一晶体管的漏极与所述第二端连接,所述第一晶体管的所述栅极还与所述第三端连接。

14.可选地,作为一种可能实现的方式,所述接地子电路包括:第一电阻,所述第一电阻的一端与所述第三端连接,另一端与接地端连接。

15.可选地,作为一种可能实现的方式,所述第一晶体管为p沟道金属氧化物半导体场效应晶体管。

16.第三方面,提供一种显示装置,包括显示面板和内部电源,还包括第一方面或第一方面的任意可能的实现方式中所述的控制电路;所述内部电源用于为所述第一电压端提供第一电压。

17.第四方面,提供一种显示装置,包括显示面板和内部电源,还包括第二方面或第二方面的任意可能的实现方式中所述的控制电路;所述内部电源用于为所述第一电压端提供第一电压。

18.第五方面,一种如第一方面所述控制电路的驱动方法,包括:当所述第一电压端提供第一电压时,所述开关子电路断开,所述第一电压输入所述第一端;当所述第一电压端未提供所述第一电压时,所述开关子电路导通,将所述第二电压端提供的第二电压输入所述第一端。

19.第六方面,提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序或指令,当计算机读取并执行所述计算机程序或指令时,使得计算机执行如以上第一方面所述的控制电路的驱动方法。

20.第三方面至第六方面的有益效果可参考上述第一方面和/或第二方面的有益效果,在此不再赘述。

附图说明

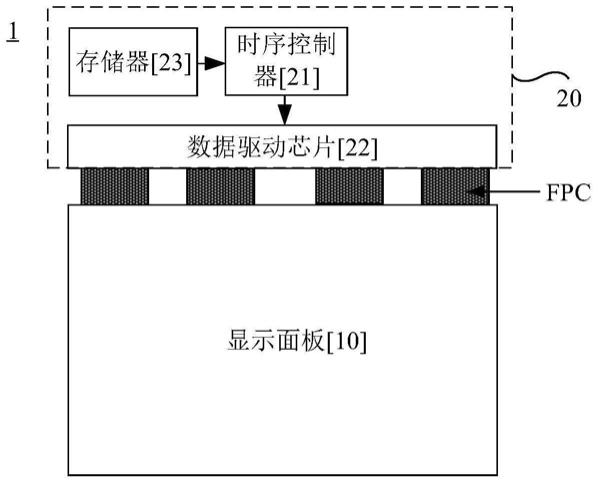

21.图1是本技术实施例一提供的一种显示装置的结构示意图;

22.图2是本技术实施例二提供的第一种存储器的电路示意图;

23.图3是本技术实施例二提供的第二种存储器的电路示意图;

24.图4是本技术实施例三提供的一种存储器的电路示意图。

25.附图标记:

[0026]1‑

显示装置;10

‑

显示面板;20

‑

控制电路板;21

‑

时序控制器;22

‑

数据驱动芯片;23

‑

存储器;30

‑

开关子电路;31

‑

第一晶体管;32

‑

第一电阻;40

‑

接地子电路;in1

‑

第一端;

in2

‑

第二端;vdd

‑

第一电压端;vcc

‑

第二电压端;100

‑

控制电路。

具体实施方式

[0027]

为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

[0028]

在本技术实施例的描述中,除非另有说明,“/”表示或的意思,例如,a/b可以表示a或b;本文中的“和/或”仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。

[0029]

以下,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上。

[0030]“包括”或“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或物件及其等同,而不排除其他元件或物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“左”、“右”、“上”以及“下”等方位术语是相对于附图中的显示组件示意放置的方位来定义的,应当理解到,这些方向性术语是相对的概念,它们用于相对于的描述和澄清,其可以根据显示装置所放置的方位的变化而相应地发生变化。

[0031]

下面结合附图对本技术实施例进行详细说明。

[0032]

实施例一

[0033]

图1为本技术实施例提供的一种显示装置1的结构示意图。如图1所示,该显示装置1包括:显示面板10和控制电路板20。

[0034]

控制电路板20包括:时序控制器(time controller,tcon)21、与时序控制器21连接的数据驱动芯片(source driver ic)22,与时序控制器21连接的存储器23。

[0035]

其中,控制电路板20通过绑定(bonding)技术,利用印刷电路板(fpc)将控制电路板20中的数据驱动芯片22与显示面板10相连接。存储器23与时序控制器21通过集成电路总线(i2c/iic,inter

‑

integrated circuit)相连接。

[0036]

应理解,输入信号输入控制电路板20中,经时序控制器21处理并转换成数据驱动芯片22可以识别的信号格式,然后,经数据驱动芯片22处理再提供给显示面板10进行显示。

[0037]

此处,存储器23用于预先存储编码(code),时序控制器21用于根据需要,通过查询地址从存储器23中读取编码并运行相应设置。其中,存储器23为带电可擦可编程只读存储器23(electrically erasable programmable read only memory,eeprom)或闪存(flash eeprom memory,flash)。当然,存储器23也可以为其他种类的器件,具体可以根据需要进行选择和设置,本技术实施例对此不进行任何限制。

[0038]

需要说明的是,存储器23中存储的编码,是提前通过连接器或者烧录工具,使用软体写入到存储器23中的。但是,在烧录时,存储器23要接入电源才能进行工作。

[0039]

以eeprom为例,第一种:可以利用为显示面板提供电压的tft

‑

lcd中的内部电源,来为eeprom提供工作电压。第二种:可以不使用tft

‑

lcd中的内部电源,直接给eeprom外接

一个外部电源。其中,示例性的,该两种方式为eeprom提供的工作电压为3.3v。

[0040]

如果eeprom上既连接有tft

‑

lcd中的内部电源,又连接有外部电源时,此时两个电源将同时连接至eeprom的第一端,该两个电源处于短接状态。基于此,两个不一致的电压可以会使得eeprom内部产生电流,严重时可能会导致电路以及eeprom被烧毁。

[0041]

为了解决这个问题,本技术提供了一种控制电路,通过在存储器23的第一端外接mos晶体管,或者,通过两个第一端分别与内部电源与外部电源相连接,并通过在两个第一端内部连接mos晶体管,从而可以使控制电路导通,使得仅有一路电源进行供电,从而防止两电源短接在一起,避免出现短路的问题。

[0042]

下面结合图2至图4对本技术实施例提供的控制电路进行详细介绍。

[0043]

实施例二

[0044]

图2至图3分别示出了本技术实施例提供的一种控制电路100的结构示意图。

[0045]

如图2所示,本技术实施例提供一种控制电路100,该控制电路100包括:具有第一端in1的存储器23、开关子电路30,以及第一电压端vdd和第二电压端vcc。

[0046]

该存储器23的第一端in1与第一电压端vdd连接,开关子电路30分别与第一端in1、第一电压端vdd和第二电压端vcc均连接。

[0047]

当第一电压端vdd提供第一电压时,开关子电路30断开,第一电压输入第一端in1。也就是说,此时只有第一电压端vdd给存储器23的第一端in1提供电源,且电源大小为第一电压。

[0048]

当第一电压端vdd未提供第一电压时,开关子电路30导通,将第二电压端vcc提供的第二电压输入第一端in1。也就是说,此时只有第二电压端vcc给存储器23的第一端in1提供电源,且电源大小为第二电压。

[0049]

应理解,第一电压和第二电压的大小可以根据需要进行设置和更改,本技术实施例对此不进行任何限制。

[0050]

其中,第一电压和第二电压的大小可以相同,也可以不相同。例如,第一电压大小为3.3v,第二电压大小也为3.3v。

[0051]

本技术实施例提供了一种控制电路,通过在存储器的外围增加开关子电路,开关子电路在第一电压端输入第一电压时断开,而在第一电压端没有输入时导通,使得第二电压端输入第二电压。由此,通过开关子电路在关闭和导通之间进行切换,可以使得第一电压端和第二电压端分开提供电压给存储器,从而避免第一电压端和第二电压端之间同时提供电压时短接,烧毁存储器的问题。

[0052]

可选地,作为一种可能实现方式,如图3所示,开关子电路30包括:第一晶体管31和第一电阻32。

[0053]

第一晶体管31的栅极、源极均与第一电压端vdd连接,第一晶体管31的漏极与第二电压端vcc连接。

[0054]

第一电阻32的一端与栅极连接,另一端与接地端gnd连接。

[0055]

需要说明的是,开关子电路30还可以包括与第一晶体管31并联的多个开关晶体管,和/或与第一电阻32并联的多个电阻。上述仅仅是对开关子电路30的举例说明,其它与开关子电路30功能相同的结构在此不再一一赘述,但都应当属于本发明的保护范围。

[0056]

可选地,作为一种可能实现方式,第一晶体管31为p沟道金属氧化物半导体场效应

晶体管。

[0057]

基于此结构,当第一电压端vdd提供第一电压时,第一电压端vdd既提供第一电压给存储器23的第一端in1,又提供第一电压给第一晶体管31的栅极,第一晶体管31的栅极为高电平时,此时,第一晶体管31会断开,由此,第二电压端vcc无法提供第二电压给存储器23。

[0058]

而当第一电压端vdd没有提供第一电压时,第一电压端vdd既没有提供第一电压给存储器23的第一端in1,也没有提供第一电压给第一晶体管31的栅极,第一晶体管31的栅极相当于为低电平,此时,第一晶体管31会导通,由此,第二电压端vcc可以提供第二电压给存储器23。

[0059]

应理解,此处,为了保护电路,此处在第一晶体管31的栅极和接地端之间增设了第一电阻32,以在第一电压端vdd提供第一电压时,维持栅极处的高电平状态,使其保持断开。

[0060]

实施例三

[0061]

图4示出了本技术实施例提供的另一种控制电路100的结构示意图。

[0062]

如图4所示,本技术实施例提供一种控制电路100,该控制电路100包括:具有第一端in1、第二端in2和第三端out的存储器23。第一端in1与第二电压端vcc连接,第二端in2与第一电压端vdd连接,第三端out与接地子电路40连接。

[0063]

存储器23中还包括开关子电路30,开关子电路30分别与第一端in1、第二端in2和第三端out连接。

[0064]

当第一电压端vdd提供第一电压时,开关子电路30断开,第一电压输入第二端in2。

[0065]

当第一电压端vdd未提供第一电压时,开关子电路30导通,第二电压端vcc提供的第二电压输入第一端in1。

[0066]

当第一电压端vdd提供第一电压时,开关子电路30断开,第一电压输入第二端in2。也就是说,此时只有第一电压端vdd给存储器23的第二端in2提供电源,且电源大小为第一电压。

[0067]

当第一电压端vdd未提供第一电压时,开关子电路30导通,第二电压端vcc提供的第二电压输入第一端in1。也就是说,此时只有第二电压端vcc给存储器23的第一端in1提供电源,且电源大小为第二电压。

[0068]

应理解,第一电压和第二电压的大小可以根据需要进行设置和更改,本技术实施例对此不进行任何限制。

[0069]

其中,第一电压和第二电压的大小可以相同,也可以不相同。例如,第一电压大小为3.3v,第二电压大小也为3.3v。

[0070]

本技术实施例提供了一种控制电路,通过在存储器的内部增加开关子电路,开关子电路在第一电压端输入第一电压时断开,而在第一电压端没有输入时导通,使得第二电压端输入第二电压。由此,通过开关子电路在关闭和导通之间进行切换,可以使得第一电压端和第二电压端分开提供电压给存储器,从而避免第一电压端和第二电压端之间同时提供电压时短接,烧毁存储器的问题。

[0071]

可选地,作为一种可能实现的方式,开关子电路30包括:第一晶体管31。

[0072]

第一晶体管31的栅极、源极均与第一端in1连接,第一晶体管31的漏极与第二端连接,第一晶体管31的栅极还与第三端连接。

[0073]

可选地,作为一种可能实现的方式,第一晶体管31为p沟道金属氧化物半导体场效应晶体管。

[0074]

需要说明的是,开关子电路30还可以包括与第一晶体管31并联的多个开关晶体管。上述仅仅是对开关子电路30的举例说明,其它与开关子电路30功能相同的结构在此不再一一赘述,但都应当属于本发明的保护范围。

[0075]

可选地,作为一种可能实现的方式,接地子电路40包括:第一电阻32,第一电阻32的一端与第三端连接,另一端与接地端连接。

[0076]

需要说明的是,接地子电路40还可以包括与第一电阻32并联的多个电阻。上述仅仅是对接地子电路40的举例说明,其它与接地子电路40功能相同的结构在此不再一一赘述,但都应当属于本发明的保护范围。

[0077]

实施例四

[0078]

本技术实施例还提供一种显示装置,包括显示面板和内部电源,还包括如图2或图3所示的控制电路100。

[0079]

其中,内部电源用于为第一电压端vdd提供第一电压。此外,外部电源用于为第二电压端提供第二电压。

[0080]

本技术实施例提供的显示装置,在使用i2c为时序控制器21烧录编码的情况下,可以防止显示装置在使用i2c为时序控制器21烧录编码,同时接入外部电源与内部电源时,两电源短接为电路带来烧毁的风险。

[0081]

本技术实施例还提供一种显示装置,包括显示面板和内部电源,还包括如如图4所示的控制电路100。

[0082]

其中,内部电源用于为第一电压端vdd提供第一电压。此外,外部电源用于为第二电压端vcc提供第二电压。

[0083]

本技术实施例提供的显示装置,在使用i2c为时序控制器21烧录编码的情况下,可以防止显示装置在使用i2c为时序控制器21烧录编码,同时接入外部电源与内部电源时,两电源短接为电路带来烧毁的风险。

[0084]

结合图2,本技术实施例还提供一种控制电路的驱动方法,包括:

[0085]

当第一电压端vdd提供第一电压时,开关子电路30断开,第一电压输入第一端in1。

[0086]

当第一电压端vdd未提供第一电压时,开关子电路30导通,将第二电压端vcc提供的第二电压输入第一端in1。

[0087]

本技术实施例提供的控制电路的驱动方法的有益效果与上述控制电路对应的有益效果相同,在此不再赘述。

[0088]

本技术实施例还提供一种计算机可读存储介质,计算机可读存储介质中存储有计算机程序或指令,当计算机读取并执行计算机程序或指令时,使得计算机执行上述控制电路的驱动方法。

[0089]

本技术实施例提供的计算机可读存储介质的有益效果与上述控制电路对应的有益效果相同,在此不再赘述。

[0090]

以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改

或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1