栅极驱动器及包括栅极驱动器的显示装置的制作方法

1.本发明涉及一种栅极驱动器及包括栅极驱动器的显示装置。

背景技术:

2.显示装置包括:具有多个像素的显示面板;用于驱动像素的栅极驱动器和数据驱动器;以及时序控制器。栅极驱动器设置有连接至栅极线的级电路(stage circuit),级电路响应于从时序控制器接收到的控制信号将栅极信号施加给与其连接的栅极线。

技术实现要素:

3.在实施方式中,提供一种栅极驱动器及包括栅极驱动器的显示装置,其中栅极驱动器被配置为使得多个缓存器连接至一个移位寄存器,以便允许栅极信号输出到多条栅极线。

4.此外,在实施方式中,提供一种栅极驱动器及包括栅极驱动器的显示装置,其中栅极驱动器设置有用于对设置在缓存器处的上拉晶体管的栅极电压进行单独充电和放电的晶体管。

5.根据本发明的一个方面,提供一种栅极驱动器,包括:包括多个级电路,其中所述多个级电路的每一个可包括:移位寄存器,所述移位寄存器被配置为控制q节点和qb节点的充电和放电;以及依次连接至所述移位寄存器的多个输出缓存器,其中所述多个输出缓存器的每一个可包括:第一晶体管,所述第一晶体管被配置为向q’节点传输q节点的电压;上拉晶体管,所述上拉晶体管被配置为响应于q’节点的电压向栅极线输出时钟信号;以及下拉晶体管,所述下拉晶体管被配置为响应于qb节点的电压向所述栅极线输出低电位电压。

6.所述多个输出缓存器的每一个还可包括:第二晶体管,所述第二晶体管根据q节点的电压而导通并且被配置为利用高电位电压对q’节点充电。

7.所述第一晶体管的栅极可连接至作为直流电源的高电位电压。

8.所述多个输出缓存器的每一个还可包括:第三晶体管,所述第三晶体管根据qb节点的电压而导通并且被配置为对q’节点放电。

9.所述第一晶体管可以二极管形式连接在q节点与q’节点之间。

10.所述第一晶体管的栅极可被配置为接收从在前级电路输出的进位信号。

11.所述多个输出缓存器的每一个还可包括:第二晶体管,所述第二晶体管根据q节点的电压而导通并且被配置为将高电位电压传输给q’节点;以及第三晶体管,所述第三晶体管根据qb节点的电压而导通并且被配置为将所述低电位电压传输给q’节点。

12.所述第一晶体管的栅极可被配置为接收作为直流电源的高电位电压或者接收从在前级电路输出的进位信号。

13.所述第一晶体管可以二极管形式连接在q节点和q’节点之间。

14.所述第一晶体管和所述第二晶体管可被配置为单独控制所述多个输出缓存器的每个q节点的充电和放电。

15.根据本发明的一个方面,提供一种显示装置,包括:显示面板,所述显示面板被配置为显示图像;数据驱动器,所述数据驱动器被配置为向所述显示面板施加数据信号;以及栅极驱动器,所述栅极驱动器包括多个级电路并且被配置为向所述显示面板施加栅极信号,其中所述多个级电路的每一个可包括:移位寄存器,所述移位寄存器被配置为控制q节点和qb节点的充电和放电;以及依次连接至所述移位寄存器的多个输出缓存器,其中所述多个输出缓存器的每一个可包括:第一晶体管,所述第一晶体管被配置为向q’节点传输q节点的电压;上拉晶体管,所述上拉晶体管被配置为响应于q’节点的电压向栅极线输出时钟信号;以及下拉晶体管,所述下拉晶体管被配置为响应于qb节点的电压向所述栅极线输出低电位电压。

16.根据实施方式,栅极驱动器及包括栅极驱动器的显示装置通过减少移位寄存器的数量来减小栅极驱动器的区域,从而实现具有窄边框的显示装置。

17.此外,根据实施方式,栅极驱动器及包括栅极驱动器的显示装置通过对设置在缓存器处的上拉晶体管的栅极电压充电和放电,能够允许均匀地且稳定地输出栅极信号。

附图说明

18.从结合附图的下文详细描述,将更清楚地理解本发明的上述和其他目的、特征和其他优点。在附图中:

19.图1是图解根据本发明实施方式的显示装置的配置的框图;

20.图2是图解图1所示的像素的实施方式的电路图;

21.图3是示意性图解根据本发明实施方式的栅极驱动器的配置的视图;

22.图4是图解根据本发明第一实施方式的多个缓存器的结构的电路图;

23.图5是图解根据本发明第二实施方式的多个缓存器的结构的电路图;

24.图6是图解根据本发明第三实施方式的多个缓存器的结构的电路图;

25.图7是图解根据本发明第四实施方式的多个缓存器的结构的电路图。

具体实施方式

26.下文中,将参照附图详细描述本发明的实施方式。在本说明书中,将理解,当一个组件(或区域、层、部分)被称为在另一组件“上”或“连接至”或“接合至”另一组件时,其可直接设置在另一个组件上或者直接连接至或接合至另一组件,或者也可存在中间的第三组件。

27.相似的参考标记通篇指代相似的元件。将理解,尽管在此使用诸如“第一”和“第二”之类的术语来描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于将一个组件与其他组件区分开。例如,在不背离所附权利要求书的范围的条件下,在一个实施方式中被称为第一元件的元件可在另一实施方式中称为第二元件。

28.术语“包括”或“包含”的含义指明特性、固定数量、步骤、操作、元素、组件或其组合的存在,但不排除其他特性、固定数量、步骤、操作、元素、组件或其组合的存在或添加。

29.图1是图解根据本发明实施方式的显示装置的配置的框图。

30.参照图1,显示装置1包括时序控制器10、栅极驱动器20、数据驱动器30、电源40和显示面板50。

31.时序控制器10可从外部接收图像信号rgb和控制信号cs。图像信号rgb可包括多个灰度级数据。控制信号cs例如可包括水平同步信号、垂直同步信号和主时钟信号。

32.时序控制器10可处理图像信号rgb和控制信号cs以使得信号适用于显示面板50的操作条件,从而时序控制器10可产生并输出图像数据data、栅极驱动控制信号cont1、数据驱动控制信号cont2以及电源控制信号cont3。

33.栅极驱动器20可基于从时序控制器10输出的栅极驱动控制信号cont1产生栅极信号。栅极驱动器20可经由多条第一栅极线gl11至gl1n向像素px提供所产生的栅极信号。

34.栅极驱动器20可经由多条第二栅极线gl21至gl2n向像素px提供感测信号。可提供感测信号以测量设置在像素px内部的驱动晶体管和/或发光元件的特性。

35.数据驱动器30可基于从时序控制器10输出的图像数据data和数据驱动控制信号cont2产生数据信号。数据驱动器30可经由多条数据线dl1至dlm向像素px提供所产生的数据信号。

36.数据驱动器30可经由多条感测线sl1至slm向像素px提供基准电压(感测电压或初始化电压),或者可基于从像素px反馈的电信号来感测像素px的状态。

37.电源40可基于电源控制信号cont3产生待提供给显示面板50的驱动电压。驱动电压例如可包括高电位驱动电压elvdd和低电位驱动电压elvss。电源40可经由相应的电源线pl1和pl2向像素px提供所产生的驱动电压elvdd和elvss。此外,电源40可向栅极驱动器20和数据驱动器30提供驱动栅极驱动器20和数据驱动器30所需的电压以及产生数据电压所需的电压。

38.在显示面板50中,设置有多个像素px(或称为子像素)。像素px例如可在显示面板50上布置为矩阵形式。像素px可利用与经由第一栅极线gl1至gln和数据线dl1至dlm提供的栅极信号和数据信号对应的亮度来发光。在一个实施方式中,每个像素px可显示红色、绿色、蓝色和白色的任一种,但不限于此。

39.时序控制器10、栅极驱动器20、数据驱动器30和电源40可被配置为分离的集成电路(ic),或者其至少一些集成在一起的ic。例如,数据驱动器30和电源40的至少之一可被配置为与时序控制器10集成在一起的集成电路。

40.此外,在图1中,栅极驱动器20和数据驱动器30被图示为与显示面板50分离的元件,但是栅极驱动器20和数据驱动器30的至少之一可按照与显示面板50一体形成的面板内方式配置。例如,栅极驱动器20可根据面板内栅极(gip)方式形成在显示面板50的边框区域中。

41.图2是图解如图1所示的像素的实施方式的电路图。图2作为示例图解了连接至第i条第一栅极线gl1i和第j条数据线dlj的像素pxij。

42.参照图2,像素px包括开关晶体管st、驱动晶体管dt、感测晶体管sst、存储电容器cst和发光元件ld。

43.开关晶体管st的第一电极连接至第j条数据线dlj,并且开关晶体管st的第二电极连接至第一节点n1。开关晶体管st的栅极连接至第i条第一栅极线gl1i。在栅极导通电平(gate-on level)的栅极信号经由第i条第一栅极线gl1i施加时,开关晶体管st导通,并且将经由第j条数据线dlj施加的数据信号传输给第一节点n1。

44.存储电容器cst的第一电极连接至第一节点n1,存储电容器cst的第二电极可被配

置为接收高电位驱动电压elvdd。利用与施加给第一节点n1的电压和高电位驱动电压elvdd之差对应的电压来对存储电容器cst充电。

45.驱动晶体管dt的第一电极被配置为接收高电位驱动电压elvdd,驱动晶体管dt的第二电极连接至发光元件ld的第一电极(例如,阳极)。驱动晶体管dt的栅极连接至第一节点n1。在栅极导通电平的电压经由第一节点n1施加时,驱动晶体管dt导通,并且可根据提供给栅极的电压,即存储在存储电容器中的电压,控制流入到发光元件ld的驱动电流的量。

46.感测晶体管sst的第一电极连接至第j条感测线slj,并且感测晶体管sst的第二电极连接至发光元件ld的第一电极。感测晶体管sst的栅极连接至第i条第二栅极线gl2i。在栅极导通电平的感测信号经由第i条第二栅极线gl2i施加时,感测晶体管sst导通,并且将经由第j条感测线slj施加的基准电压传输给发光元件ld的第一电极。

47.发光元件ld输出对应于驱动电流的光。发光元件ld可以是具有微米至纳米级别范围尺寸的有机发光二极管(oled)或超小无机发光二极管,但是本发明不限于此。下文,将描述发光元件ld被构建为有机发光二极管的实施方式。

48.在本发明中,像素px的结构不限于图2所示的结构。根据实施方式,像素px可进一步包括用于补偿驱动晶体管dt的阈值电压、或者将驱动晶体管dt的栅极电压和/或发光元件ld的阳极电压初始化的至少一个元件。

49.图2图解了开关晶体管st、驱动晶体管dt和感测晶体管sst是nmos晶体管的示例,但是本发明不限于此。例如,构成每个像素px的晶体管的至少一些或者全部可被构建为pmos晶体管。在各实施方式中,开关晶体管st、驱动晶体管dt和感测晶体管sst的每一个可被实现为低温多晶硅(ltps)薄膜晶体管、氧化物薄膜晶体管或低温多晶硅氧化物(ltpo)薄膜晶体管。

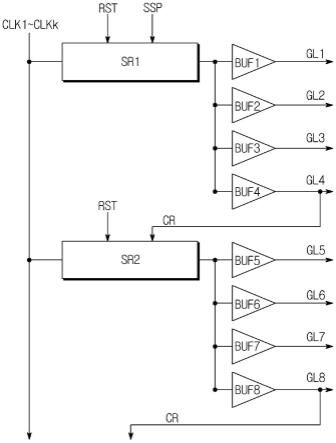

50.图3是示意性图解根据本发明实施方式的栅极驱动器的配置的视图。

51.根据本发明实施方式的栅极驱动器20基于从时序控制器10施加的栅极驱动控制信号cont1产生栅极信号,并将产生的栅极信号依次施加给栅极线gl1至gl8。

52.参照图3,栅极驱动器20可包括多个级电路。级电路可接收至少一个时钟信号clk1至clkk。时钟信号clk1至clkk可以是方波信号,其中用于使构成级电路的晶体管导通的栅极导通电压和用于使构成级电路的晶体管截止的栅极截止电压重复。

53.每个级电路包括:经由进位信号线从属地连接的移位寄存器sr1和sr2;以及分别连接至移位寄存器sr1和sr2的缓存器buf1至buf4以及buf5至buf8。

54.每个级电路的移位寄存器sr1和sr2可接收扫描起始信号ssp或者从在前级电路(previous stage circuit)输出的进位信号cr。例如,第一级电路的第一移位寄存器sr1可接收扫描起始信号ssp,其余级电路的第二移位寄存器sr2可接收从在前级电路输出的进位信号cr。移位寄存器sr1和sr2可响应于扫描起始信号ssp或进位信号cr利用其输出端的节点电压被充电。

55.在一个实施方式中,移位寄存器sr1和sr2可进一步接收从在后级电路(next stage circuit)的移位寄存器输出的进位信号cr。但是,实施方式不限于此。

56.移位寄存器sr1和sr2可进一步接收复位信号rst。移位寄存器sr1和sr2可响应于复位信号rst可对其输出端的节点电压放电。

57.每个级电路的缓存器buf1至buf4以及buf5至buf8可依次连接至移位寄存器sr1和

sr2的输出端。在实施方式中,级电路可具有多重缓存器结构(multi-buffer structure),其中多个缓存器buf1至buf8连接至移位寄存器sr1和sr2的其中之一。例如,第一至第四缓存器buf1至buf4可连接至第一移位寄存器sr1,第五至第八缓存器buf5至buf8可连接至第二移位寄存器sr2。尽管作为示例图3中示出了四个缓存器buf1至buf4、buf5至buf8分别连接至移位寄存器sr1和sr2的其中之一,但是也可以更少或更多数量的缓存器连接至移位寄存器sr1和sr2的其中之一。

58.一般来说,由于移位寄存器sr1和sr2由多个晶体管形成,所以在栅极驱动器20设置在显示面板50上时,栅极驱动器20占据了很大的面积,从而可使边框区域变窄。

59.在实施方式中,级电路被配置为使得移位寄存器sr1和sr2的其中之一向多条栅极线gl1至gl8输出栅极信号。因此,在栅极驱动器20内移位寄存器sr1和sr2的数量减少,并且栅极驱动器20的区域减小,由此能够实现窄边框。

60.每个缓存器buf1至buf4以及buf5至buf8可响应于连接的移位寄存器sr1和sr2的输出端的节点电压来输出时钟信号clk1至clkk。作为栅极信号,输出的时钟信号clk1至clkk被施加给栅极线gl1至gl8。

61.当连接至栅极驱动器20的像素px具有与图2所示的相同结构时,栅极信号可包括第一栅极信号和第二栅极信号。但是,实施方式不限于此。

62.从每个级电路的最后缓存器buf4和buf8输出的栅极信号作为进位信号cr可经由进位信号线施加给在后级电路的移位寄存器。尽管图3示出了移位寄存器sr1和sr2经由进位信号线直接连接至后一级电路的移位寄存器,但是实施方式不限于此。在另一实施方式中,移位寄存器sr1和sr2可经由进位信号线连接至位于相应移位寄存器sr1和sr2之后的任何移位寄存器。

63.下文,将更详细地描述级电路的多重缓存器结构。

64.图4是图解根据本发明第一实施方式的多个缓存器的结构的电路图。

65.参照图4,级电路包括移位寄存器sr和连接至移位寄存器sr的多重缓存器buf1至buf4。

66.移位寄存器sr可响应于输入的信号(扫描起始信号ssp或进位信号cr、复位信号rst)对q节点和qb节点的电压充电和放电(或者简单地说,对q节点和qb节点充电和放电)。例如,移位寄存器sr1和sr2可响应于扫描起始信号ssp或进位信号cr对q节点的电压进行充电,并且可响应于时钟信号clk1至clkk对其输出端的节点进行充电或放电。当q节点的电压被充电时,qb节点的电压可被放电。当q节点的电压被放电时,qb节点的电压可被充电。

67.每个缓存器buf1至buf4可包括连接在q节点与q’节点q’1、q’2、q’3、q’4之间的相应第一晶体管t11、t12、t13、t14。每个第一晶体管t11、t12、t13、t14的栅极连接至高电位电压vdd。高电位电压vdd可以是栅极导通电平的直流电压。第一晶体管t11、t12、t13、t14可在导通状态时将q节点的电压传输给q’节点q’1、q’2、q’3、q’4。

68.每个缓存器buf1至buf4的第一端被配置为分别接收时钟信号clk1至clk4,并且每个缓存器buf1至buf4的第二端连接至栅极线gl1至gl4。此外,缓存器buf1至buf4包括相应的上拉晶体管tu1至tu4,其栅极分别连接至q’节点q’1、q’2、q’3、q’4。上拉晶体管tu1至tu4响应于q’节点q’1、q’2、q’3、q’4的电压而导通,并且将输入的时钟信号clk1至clk4输出到栅极线gl1至gl4。缓存器buf1至buf4可分别进一步包括下拉晶体管td1至td4,其响应于qb

节点的电压而导通并且将低电位电压vss输出到栅极线gl1至gl4。低电位电压vss可以是栅极截止电平(gate-off level)的直流电压。

69.在如上所述的实施方式中,第一晶体管t11、t12、t13和t14在级电路通过作为直流电压的高电位电压vdd驱动的同时保持导通状态。然后,第一晶体管t11、t12、t13和t14可快速劣化,并且其特性可改变。例如,当第一晶体管t11、t12、t13和t14的阈值电压上升时,q’节点的电压可由于上升的阈值电压而降低。因此,位于输出缓存器buf1至buf4处的上拉晶体管tu1至tu4的栅极-源极电压改变,从而输出缓存器buf1至buf4的输出电压降低而变得不均匀。

70.为了避免这个问题,在实施方式中,输出缓存器buf1至buf4进一步包括响应于q节点的电压,分别对q’节点q’1、q’2、q’3、q’4单独充电的第二晶体管t21、t22、t23和t24。第二晶体管t21、t22、t23和t24可分别连接在高电位电压vdd与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可连接至q节点。当q节点被充电时,第二晶体管t21、t22、t23和t24导通,并将高电位电压vdd传输给q’节点q’1、q’2、q’3、q’4,从而q’节点q’1、q’2、q’3、q’4可被有效充电。也就是说,第一晶体管和第二晶体管可被配置为单独控制多个输出缓存器buf1至buf4的每个q节点的充电和放电。

71.在实施方式中,尽管第一晶体管t11、t12、t13和t14劣化,但是q’节点q’1、q’2、q’3、q’4能够经由第二晶体管t21、t22、t23和t24被充电。因此,每个输出缓存器buf1至buf4的上拉晶体管tu1至tu4可被稳定地导通。因此,在实施方式中,可将由于第一晶体管t11、t12、t13和t14的劣化导致的负作用最小化,并且可均匀且稳定地执行栅极导通电压向栅极线的输出。

72.图5是图解根据本发明第二实施方式的多个缓存器的结构的电路图。

73.与图4的实施方式相比,在图5所示的实施方式中,第一晶体管t11’、t12’、t13’和t14’分别以二极管形式连接在q节点与q’节点q’1、q’2、q’3、q’4之间。第一晶体管t11’、t12’、t13’和t14’响应于q节点的电压导通,并将q节点的电压传输给q’节点q’1、q’2、q’3、q’4。第一晶体管t11’、t12’、t13’和t14’以二极管的形式连接,从而可将q节点的电压稳定地传输给q’节点q’1、q’2、q’3、q’4。

74.每个缓存器buf1至buf4可包括:响应于q’节点q’1、q’2、q’3、q’4的电压导通并且向栅极线gl1至gl4输出输入时钟信号clk1至clk4的相应上拉晶体管tu1至tu4;以及响应于qb节点的电压导通并且向栅极线gl1至gl4输出低电位电压vss的相应下拉晶体管td1至td4。

75.在实施方式中,缓存器buf1至buf4进一步包括分别响应于qb节点的电压对q’节点q’1、q’2、q’3、q’4进行单独放电的第三晶体管t31、t32、t33和t34。第三晶体管t31、t32、t33和t34可分别连接在低电位电压vss与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可连接至qb节点。当qb节点被充电时,第三晶体管t31、t32、t33和t34导通,并且将低电位电压vss传输给q’节点q’1、q’2、q’3、q’4,从而q’节点q’1、q’2、q’3、q’4可被有效放电。

76.在实施方式中,尽管第一晶体管t11’、t12’、t13’和t14’劣化,但是q’节点q’1、q’2、q’3、q’4能够经由第三晶体管t31、t32、t33和t34放电。因此,输出缓存器buf1至buf4的上拉晶体管tu1至tu4可稳定地截止。因此,在实施方式中,可将由于第一晶体管t11’、t12’、t13’和t14’的劣化导致的负作用最小化,并且可均匀且稳定地执行栅极截止电压向栅极线

的输出。

77.图6是图解根据本发明第三实施方式的多个缓存器的结构的电路图。

78.与图5中的实施方式相比,在图6所示的实施方式中,第一晶体管t11”、t12”、t13”和t14”分别连接在q节点与q’节点q’1、q’2、q’3、q’4之间,并且其栅极被配置为接收从在前级电路输出的进位信号cr。当从在前级电路施加栅极导通电平的进位信号cr时,第一晶体管t11”、t12”、t13”和t14”可导通,并且可将q节点的电压传输给q’节点q’1、q’2、q’3、q’4。

79.每个缓存器buf1至buf4可包括:响应于q’节点q’1、q’2、q’3、q’4的电压导通并且向栅极线gl1至gl4输出输入时钟信号clk1至clk4的相应上拉晶体管tu1至tu4;以及响应于qb节点的电压导通并且向栅极线gl1至gl4输出低电位电压vss的相应下拉晶体管td1至td4。

80.在实施方式中,缓存器buf1至buf4进一步包括分别响应于qb节点的电压对q’节点q’1、q’2、q’3、q’4进行单独放电的第三晶体管t31、t32、t33和t34。第三晶体管t31、t32、t33和t34可分别连接在低电位电压vss与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可连接至qb节点。当qb节点被充电时,第三晶体管t31、t32、t33和t34导通,并且将低电位电压vss传输给q’节点q’1、q’2、q’3、q’4,从而q’节点q’1、q’2、q’3、q’4可被有效放电。

81.图7是图解根据本发明第四实施方式的多个缓存器的结构的电路图。

82.参照图7,每个缓存器buf1至buf4可包括:分别连接在q节点与q’节点q’1、q’2、q’3、q’4之间的相应第一晶体管t11、t12、t13、t14。每个第一晶体管t11、t12、t13、t14的栅极连接至高电位电压vdd。高电位电压vdd可以是栅极导通电平的直流电压。第一晶体管t11、t12、t13、t14可在导通状态时将q节点的电压传输给q’节点。

83.在实施方式中,每个缓存器buf1至buf4进一步包括响应于q节点的电压,分别对q’节点q’1、q’2、q’3、q’4单独充电的第二晶体管t21、t22、t23和t24。第二晶体管t21、t22、t23和t24可分别连接在高电位电压vdd与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可连接至q节点。当q节点被充电时,第二晶体管t21、t22、t23和t24导通,并将高电位电压vdd传输给q’节点q’1、q’2、q’3、q’4,从而q’节点q’1、q’2、q’3、q’4可被有效充电。

84.此外,在实施方式中,每个缓存器buf1至buf4进一步包括分别响应于qb节点的电压对q’节点q’1、q’2、q’3、q’4进行单独放电的第三晶体管t31、t32、t33和t34。第三晶体管t31、t32、t33和t34可分别连接在低电位电压vss与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可连接至qb节点。当qb节点被充电时,第三晶体管t31、t32、t33和t34导通,并且将低电位电压vss传输给q’节点q’1、q’2、q’3、q’4,从而q’节点q’1、q’2、q’3、q’4可被有效放电。

85.在图7中,示出了每个第一晶体管t11、t12、t13、t14的栅极连接至高电位电压vdd的实施方式。但是,实施方式不限于此。例如,在另一实施方式中,第一晶体管t11’、t12’、t13’、t14’以二极管的形式分别连接在q节点与q’节点q’1、q’2、q’3、q’4之间,如图5示出的实施方式那样。在又一实施方式中,如图6的实施方式那样,第一晶体管t11”、t12”、t13”、t14”可连接在q节点与q’节点q’1、q’2、q’3、q’4之间,并且其栅极可被配置为接收从在前级电路输出的进位信号cr。

86.所属领域的技术人员将理解,在不改变本发明的技术思想或必要特征的条件下,本发明可以以其他具体形式来实现。因此,应理解,上述实施方式在所有方面都是示例性的,而非限制性的。本发明的范围通过所附权利要求书而不是上述的详细描述来限定,其应

当解释为,根据所附权利要求书的含义和范围及其等同物而得到的所有替换或修改都落入本发明的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1