串扰减少的像素电路的制作方法

pixels in organic light-emitting diode displays”,soc.info.display digest,50(s1),paper 3.3(2019)中可以找到这些类型的串扰效应的讨论。

9.通常,微显示器的对角线尺寸小于两英寸,超小显示器的对角线尺寸小于0.25英寸。在大多数情况下,微显示器的分辨率高,并且像素间距通常为5微米至15微米。它们在20世纪90年代末首次商业化,普遍用于背投电视、头戴式显示器(hmd)、平视显示器(hud)、电子取景器(evf)、近眼显示器、增强现实设备、虚拟现实设备、智能手表和其它可穿戴设备以及数码相机。微显示器可以由多种发光技术制成,特别是包括microled(发光二极管)和有机发光二极管(oled)。

10.目前,微led微型显示器基于标准氮化镓(gan)晶片,采用标准led。该方法具有以相对低的价格提供高亮度显示设备而不存在寿命问题的潜力。通常,标准gan晶片被图案化成微led阵列。然后通过集成微led阵列和晶体管来制造微led显示器。然而,这种方法具有若干制造方面的问题,包括晶体管上微led的单片形成、像素间距、颜色产生、以及由于各个微led之间颜色和亮度的变化而导致的空间均匀性。

11.oled技术具有用于微显示器的微led技术的许多有吸引力的特征。其自发射、具有优异的图像质量、有效并且具有超高的色彩还原能力和扩展的色彩空间。此外,在晶体管上形成oled比形成微led容易得多且成本更低,因为oled层可以真空放置或直接涂覆在晶体管背板上。另一方面,oled可以具有有限的亮度和有限的寿命。

12.因此,从成本和可制造性的观点来看,oled微显示器是非常有吸引力的。这种设备通常使用在诸如玻璃的非导电衬底或硅背板上的有源矩阵tft电路来控制各个像素。通常,这些将使用具有由背板中的电路控制的单独控制的电极的oled来制造。就oled而言,它们可以配置成使得每个像素被不同地配置(即,每个单独的像素发射红色(r)、绿色(g)或蓝色(b)的光),或者oled对像所有素共同配置并发射白光,使得当与滤色器阵列(cfa)结合使用时,形成单独的r、g或b像素。其中,所有像素共同配置的oled是优选的,因为它们价格更低、更容易制造。

13.串扰可以由光学和化学/电学机制引起。可以增加串扰程度的一些光学过程包括设备内的波导和光散射。在内部产生光的任何类型的设备中都可能发生光学串扰。对于所有像素具有公共层的oled,可增加串扰的一些化学/电学过程包括相同层内从有源像素区域到相邻无源像素区域的侧向载流子迁移。电荷的这种迁移可以在相邻像素中产生电压和电流,并且导致不期望的和非有意的来自像素的发射。

14.期望所有来源的像素之间的串扰量是像素的总发射量的10%或更少,优选地是3%或更少,并且最优选地是1%或更少。

15.普遍认为,导致串扰的机制有多种。短程模式(0.2μm至0.7μm)可以是侧向电荷载流子和光学机制的结合。中程模式(3μm至7μm)相互作用可以主要由于侧向电荷载流子迁移,但部分由于光学机制导致。长程模式(50μm至200μm)相互作用可以主要由于从有源像素区域到无源区域的光散射。还认为,基于根据像素间距的波导,存在对串扰的更长程的光学贡献。

16.用于最小化由于显示设备内的光学过程而引起的串扰问题的一些有用的方法包括:

[0017]-在像素之间使用像素限定层、散射层或其它类型的光学屏障或结构,有助于将光

传播限制在像素内并使跨越不同像素的光传播最小化。例如,参见us10483310b2、us20170038597a1、us20190056618a1、cn110416247a和cn110429196a。

[0018]-在具有滤色器阵列(cfa)的设备中,优化的滤色器用于减少在空气/玻璃界面和反射阳极之间的光波导,包括使用专门设计成吸收从衬底法线方向以高角度传播的光的光学过滤层。例如,参见us20160065914。

[0019]-通过减少散射位而减少的光散射。特别地,应该最小化底部电极上或底部电极附近的小颗粒碎屑的量。散射也可以由取决于用于沉积的组分和工艺的阴极或阳极的粗糙度而导致(例如,参见shen等人的“efficient upper-excited state fluorescence in an organic hyperbolic metamaterial”,nano lett.,18(3),1693

–

1698(2018)。

[0020]-整个电极表面应该在有源像素区域上以及在像素之间尽可能平坦和平滑。特别地,已知在像素之间形成pdl(像素限定层)并在像素区域内的阳极表面上方延伸的突起、隆起或其它结构对于将光散射回像素区域中并防止其进入相邻(不发光的)像素有帮助。然而,当存在覆盖结构的较厚的oled层时,这种方法不是十分有效的。捕获在较厚层内的光更可能在层内被内部地反射,使得它可以穿过结构到达另一侧。如果电极和oled层是均匀平坦的,则显示器层内的波导光很可能继续不间断地传播,直到被吸收或到达显示器边缘。

[0021]-使用用于波导光的层间吸收剂。

[0022]-通过背板的电介质的光吸收。

[0023]

使oled设备中由于载流子迁移而导致的串扰问题最小化的一些有用方法包括:

[0024]-在像素之间使用像素限定层、沟槽、分离器、分隔器或其它类型的物理屏障或结构,有助于将载流子迁移限制在初始像素内并且最小化任何载流子迁移到不同的像素。例如,参见us 20210151714、us 2020388658、us 2020/0066815、us 20190280062 a1、us 20190006443 a、us 20180180951 a1、cn 110148619 a和cn 110634922 a。

[0025]-在oled的分段阳极下方使用接地面。例如,参见us 10128317。

[0026]-通过改变具有高载流子迁移率的层(例如hil、htl、cgl、etl和eil)的层厚度和组成(以增加“薄层电阻”)来减少侧向电荷载流子迁移。特别地,电荷载流子(空穴或电子)在有源区内产生,并且可以侧向移动越过发光区和非发光区之间的间隙。这个问题可以主要发生在邻近或靠近一个电极的层中。在一些情况下,cgl(电荷产生层)也可以起作用,因为它们具有非常高的载流子迁移率。普遍认为,阳极上的普通hil和htl层可能对此问题贡献最大。可以看到,一旦一个阳极焊盘上的hil的通电区域中产生空穴,它们就可以迁移到相邻的阳极焊盘,并且由于空穴而产生的电压可以超过oled的阈值电压vth,因此(名义上不发光的)像素发光,而不考虑该像素的图像信号。此外,空穴可以作为电子进入导电阳极焊盘,并以非常小的侧向电阻侧向流过阳极。在阳极焊盘的远侧处,电流可以返回到hil(作为空穴),用于跳转到下一个未发光的阳极焊盘。因此,载流子迁移的问题不仅限于相邻阳极焊盘之间较短的距离,而且还可以具有较长距离的分量。为此,应该特别注意两个电极(特别是阳极)的厚度和组成。具有较小载流子迁移率的较薄有机层有助于最小化这些不期望的载流子迁移过程。例如,参见us 20170317308 a1。

[0027]-通过对层进行修改以在电极段之间的区域中具有更高的电阻来减少侧向电荷载流子迁移。例如,参见us 20201772651。

[0028]-选择具有高载流子迁移率的材料用于有机层。特别地,可以选择对最小化串扰有

贡献的材料。在这方面,添加到hil中的p-掺杂剂(例如,f4-tcnq、f6-tcnnq或hat-cn)的类型和水平以及hil或htl中htm(例如,诸如npb或螺旋(spiro)-ttb的芳胺化合物)的选择可能是重要的。仅p掺杂剂或未掺杂的hil也可能是有效的。在一些情况下,可以使用未掺杂的hil和p掺杂的htl。诸如moo3的无机hil材料(其可以与有机材料混合)也可以具有优点。例如,参见us 20170330918 a1、us 20170301864 a1和us 20170301861 a1。

[0029]-在oled中,设计hil和阳极以产生电荷从hil进入阳极的屏障是有利的。

[0030]

还可以通过驱动信号的补偿来减少串扰。可以调整原始图像信号以补偿由于串扰而引起的每个像素的光发射的差异,从而实现期望的发射。然而,这要求每个图像的每个像素中存在的串扰量是可预测的,并且为每个图像帧重新计算图像信号。这极大地增加了对计算以及总计算时间的需求。这增加了设备的成本,而且影响响应时间。在这种方法中,仅依靠这种方法的显示器无法再现高色彩饱和度区域的部分色彩量。

[0031]

一般来说,串扰对于应具有最小光发射或无光发射(“黑色”)或相对低的发射的像素是最明显的并且是最受关注的。这是因为与来自像素的低水平发射或无发射相比,即使很小的由串扰引起的附加的无意的光也会变成总发射的非常大的百分比。对于具有高发射的像素,由串扰引起的少量的光应该不那么明显。

[0032]

在像素与相邻或空间上接近的像素之间发射差异较大的情况下,串扰也更成问题。这可以是亮度低或“黑色”(不发射或最小发射量)的像素邻近于亮度高或处于其最大发射水平的像素。串扰问题也可存在于单色发射像素(例如,红色像素)邻近于发射不同颜色的像素(例如,绿色像素)的情况,即使两者的亮度值相似。此外,如果与相邻发光像素的颜色不同颜色的不发光像素由于串扰而发射不同颜色,则显示器不能实现高饱和度的原色和副色。

[0033]

存在两种常见的具有低水平发射或无发射的像素位于高水平发射像素附近的情况。第一种情况是根据图像。应注意,大多数图像是相关的,即,彼此靠近的像素通常具有相似的发射量,因此串扰程度在该区域内相对较低。例如,在大片黑色区域的中央或大片白色区域的中央将存在少的串扰。只有在图像内的边缘或边界处,像素之间的发射才会有大的差异。因此,由于串扰,相关的发射区域可能不是均匀的,并且在中央与沿着边界是不同的。对于相关的单色像素会出现相同的问题,其中沿着边缘和边界颜色混合将更加显著。

[0034]

第二种情况是其中通过扫描各个像素来产生发射而不是所有像素同时发光的显示器。这种设备的示例包括无源矩阵和有源矩阵显示器。在这种显示器中,像素排列成列和行的矩阵。在有源矩阵显示器中,根据沿着特定行的每个像素的图像,创建对应于所需亮度的数据信号。然后,扫描线允许数据信号传递到沿着该特定行的像素,并且像素按照数据信号产生所需的亮度。然后,生成用于下一行的数据信号,并且激活用于下一行的扫描线,从而下一行中的像素可以产生亮度。重复这种逐行扫描以创建整个图像,并且这种逐行扫描在视觉察觉阈值内发生。然而,串扰会让一些像素在它们应该处于“关断”状态时产生光。

[0035]

因此,期望在像素应处于“关断”或最小发射状态时通过消除或耗散提供给像素的光产生部分的任何电压或电流来防止像素化显示设备中由于串扰而引起的像素的发射。尽管这种解决方案可应用于任何类型的显示器,但是当应用于oled微显示器时尤为合适,甚至更理想地,应用于与cfa组合使用的多模(白色)微腔oled。这是由于多模微腔oled中的常见层允许载流子从一个“导通”的像素迁移到可能是“关断”的另一个相邻像素,从而在相邻

的“关断”的像素中产生足够引起发射的电压,并且由于微腔oled中的层必须厚(为了产生微腔),这促进了侧向载流子迁移,并且对于具有3个或更多发光单元的堆叠的多模oled微显示器是由于驱动这些多叠层oled所需的高电压。这也适用于在指定像素内具有单独设置的r、g和b发射材料的oled微显示器,但是其中所有像素共享至少一个公共oled层。

[0036]

us 20100091001 a1和us 8035580描述了一种用于oled的数字驱动的像素电路。当像素处于“关断”状态时,使用将oled的阳极连接到电压源(其电势可以被设置为小于oled的阴极处的电势)的支路晶体管来防止由于通过驱动晶体管的电流泄漏而引起的像素发射。当该行像素的扫描线被激活时,相同的数据信号被施加到支路晶体管和驱动晶体管的栅极。

[0037]

cn107134257b描述了一种使用将oled的阳极连接到低电压源v

sense

的晶体管来防止由于电荷产生层(cgl)内的载流子迁移而引起的像素发射的像素电路。连接晶体管的栅极由与用于控制驱动晶体管的扫描线分离的扫描线控制。

[0038]

us10665161b2描述了一种用于防止由于通过驱动晶体管的电流泄漏而引起的像素发射的像素电路,其中存在能够使驱动电流绕过发光元件的放电部分。放电部分包括晶体管,该晶体管的栅极由与控制驱动晶体管的扫描信号分离的扫描信号控制。

[0039]

us9324264b2描述了一种用于在像素处于“关断”状态时防止像素发射的像素电路,其使用具有将oled的阳极连接到v

var

(其电势可以被设置为小于oled的阴极处的电势)的支路晶体管的支路单元。在各种实施方式中,支路晶体管的栅极由扫描线或单独的dc电压源控制。

[0040]

us9123294b2描述了一种用于补偿驱动tft的阈值电压的像素电路。作为电路的一部分,存在允许驱动电流绕过oled使得不从像素发射的晶体管。该晶体管的栅极由用于控制驱动晶体管的栅极的相同扫描线或不同的扫描线控制。

[0041]

us20030112205a1描述了一种可以使用放电电路来减少残留图像现象的发生的像素电路,该放电电路对像素上积累的电荷进行放电。该放电电路包括支路晶体管,该支路晶体管的栅极由扫描线控制。

[0042]

us202000066815公开了一种具有泄漏电流接收器(sink)的像素电路以防止像素之间的串扰,其包括位于连接件与地线之间的泄漏电流控制晶体管,该连接件位于串联连接的驱动晶体管和发射晶体管之间。泄漏电流控制晶体管的栅极由v

bias

控制而不是数据信号,v

bias

对于显示器中的所有像素是相同的。

[0043]

us20180180951描述了一种具有像素电路的显示设备,该像素电路具有晶体管,该晶体管的源极连接到驱动晶体管和发光设备的阳极之间的节点,并且该晶体管的漏极连接到电势供应线,该电势供应线可以是地线。该晶体管的栅极由扫描线控制。

[0044]

us20100253666描述了一种具有连接在位于驱动晶体管和像素之间的节点之间的放电晶体管的像素电路,其栅极由扫描信号控制。

[0045]

lin等人的“uhd amoled driving scheme of compensation pixel and gate driver circuits achieving high-speed operation”,j.elec.devices soc.6,26(2017)描述了一种用于补偿vth变化的像素电路。作为电路的一部分,存在与oled和v

ss

电接触的晶体管,其允许驱动电流绕过oled。该支路晶体管的栅极由与用于控制扫描晶体管的扫描线不同的扫描线控制,所述扫描晶体管控制驱动晶体管的栅极。

[0046]

kimura等人的“new pixel driving circuit using self-discharging compensation method for high resolution oled micro displays on a silicon backplane”,j.soc.info.display,25(3),167(2017)公开了用于亮度均匀性的像素电路,其包括在oled的阳极和v

ss

之间的支路电路以改善对比度。该支路电路具有晶体管,该晶体管的栅极由与用于控制扫描晶体管的扫描线不同的扫描线控制,所述扫描晶体管控制驱动晶体管的栅极。

[0047]

kwak等人的“organic light-emitting diode-on-silicon pixel circuit using the source follower structure with active load for microdisplays”,japanese journal of applied physics,50,03cc05(2011)描述了一种用于改善均匀性的像素电路,其包括位于节点和地线之间的支路电路,节点位于发光晶体管和oled的阳极之间。该支路晶体管的栅极连接到节点,使得vg=vs,以限制发射晶体管处的漏极电压。其目的是不超过晶体管的最大允许v

ds

。

[0048]

vogel等人的“oled microdisplays in near-to-eye applications:challenges and solutions”,proc.spie 10335,digital optical technologies,1022502(2017)描述了制造oled微显示器的问题。它指出“高亮度的挑战是向每个oled像素提供和调制在2v到7v(或甚至更高,取决于oled叠层结构)的动态范围电平处的正向电压;这要求集成的驱动晶体管能够承受5v或更高的电压摆动。这对于先进混合信号cmos工艺是高电压

……”

。该参考文献还指出“由于具有约5v的可行电压扫描的不透明cmos背板,只能集成顶部发射的单单元和双单元”。它描述了需要较高工作电压的oled配置,这导致需要额定工作电压高于5v的晶体管以及这种较高电压晶体管会对孔径比和像素尺寸产生影响。

技术实现要素:

[0049]

本发明的一些重要特征包括但不限于:

[0050]

有源矩阵显示器,包括:电源v

dd

(1);由列和行组成的像素阵列,每个用于发光的像素(2)具有单独受控的分段电极(109)和相对电极(125);驱动电路包括沿着列为每个像素(2)提供数据信号(v

data

)的至少一条数据线(3)和针对沿着行的每个像素(2)提供扫描信号(v

scan

)的至少一条扫描线(4),其中,数据信号(v

data

)控制驱动晶体管(t1)的栅极,驱动晶体管(t1)的源极和漏极连接在电源v

dd

(1)和分段电极(109)之间,扫描信号(v

scan

)控制扫描晶体管(t4)的栅极,使数据信号(v

data

)从数据线(3)加载到驱动晶体管(t1)的栅极;以及像素控制电路(5),与分段电极(109)电接触,其中,像素控制电路(5)基于像素(2)的数据信号(v

data

)的值来防止像素(2)的光发射。

[0051]

像素控制电路(5)可以附接到沿着电力线定位在驱动晶体管(t1)与分段电极(109)之间的节点(node1)。像素控制电路(5)通过具有支路晶体管(t3)来防止光发射,支路晶体管(t3)允许分段电极(109)和接收器(6)之间的电连接,每当数据信号(v

data

)指示像素(2)应为非发射或具有低于阈值的发射时,接收器(6)将电压和/或电流降低到低于光发射所需的水平。当像素(2)的数据信号(v

data

)的值指示发射超过阈值时,像素控制电路(5)被禁用。

[0052]

像素控制电路(5)可以包括:判定子单元(9),将数据信号v

data

的电压与参考电压v

ref

进行比较,并基于比较的结果提供输出电压v

output

;以及锁存子单元(10),从判定子单元

(9)接收输出电压v

output

并控制支路晶体管(t3),以基于输出电压v

output

来启用或禁用分段电极(109)与接收器(6)之间的电连接。

[0053]

另外,每当扫描信号(v

scan

)指示扫描晶体管(t4)应防止数据信号(v

data

)加载到驱动晶体管(t1)的栅极并且输出电压v

output

被设置成禁用支路晶体管(t3)时,支路晶体管(t3)允许分段电极(109)和接收器(6)之间的电连接,以将电压和/或电流降低到低于光发射所需的水平。

[0054]

像素控制电路(5)可以包括:判定子单元(9),将数据信号v

data

的电压与参考电压v

ref

进行比较,并且基于比较的结果,提供输出电压v

output

;以及晶体管(tb),晶体管(tb)的栅极由扫描信号v

scan

控制并且串联连接在判定子单元(9)和支路晶体管(t3)的栅极之间,每当扫描信号v

scan

使得晶体管(tb)启用以将输出电压v

output

施加到支路晶体管(t3)的栅极时,基于输出电压v

output

的值启用或禁用分段电极(109)与接收器(6)之间的电连接。

[0055]

对于上述像素控制电路中的任一个,其中,v

ref

和电源v

dd

(1)的电压相同。

[0056]

上述显示器可以是oled微显示器,特别地,其中,用于发光的像素(2)使用具有滤色器阵列(129a,129b,129c)的多模微腔oled形成,可以另外具有三个或更多发光单元(113,117,121)的叠层,或者可以具有5v或更大的阈值电压v

th

。

[0057]

对于上述显示器中的任一个,在驱动晶体管(t1)和分段电极(109)之间串联连接有开关晶体管(t6),使得驱动晶体管(t1)和开关晶体管(t6)串联在电源(1)和分段电极(109)之间。驱动晶体管(t1)和开关晶体管(t6)都可以是p沟道晶体管,并且支路晶体管(t3)可以是n沟道晶体管。

[0058]

上述显示器具有减小的串扰效应。

附图说明

[0059]

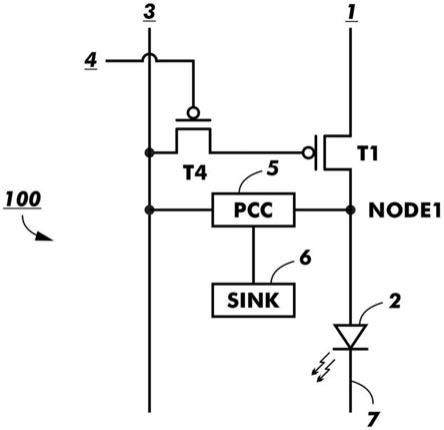

图1示出了用于oled的简单现有技术的控制电路。

[0060]

图2示出了具有基本像素控制电路的本发明的基本像素电路100。

[0061]

图3示出了具有更详细的像素控制电路的本发明的像素电路150。

[0062]

图4示出了使用bjt组件的像素控制电路的判定电路部分的一个实施方式。

[0063]

图5示出了使用bjt组件的像素控制电路的判定电路部分的另一实施方式。

[0064]

图6示出了使用cmos组件的像素控制电路的判定电路部分的另一实施方式。

[0065]

图7示出了具有更详细的像素控制电路的本发明的像素电路200。

[0066]

图8示出了像素电路200的操作流程图。

[0067]

图9a示出了具有像素控制电路的本发明的像素电路250,该像素控制电路添加了具有由扫描线控制的晶体管t5的电路。

[0068]

图9b示出了作为250的变体的本发明的像素电路300。

[0069]

图9c示出了作为250的另一变体的本发明的像素电路350。

[0070]

图10a示出了本发明的像素电路275。

[0071]

图10b示出了275的判定电路9的一个实施方式的细节。

[0072]

图11示出了本发明的像素电路285。

[0073]

图12示出了oled微显示器400的截面,其中oled是多模微腔。

[0074]

图13示出了适于微显示器的本发明的像素电路450。

具体实施方式

[0075]

应注意,除非不相容,否则任何所述特征可以按任何顺序或程度组合而不受限制。

[0076]

出于本公开的目的,术语“之上”或“上方”意指所涉及的结构位于另一结构上方,即,在与衬底相对的一侧上。“顶部”、“最上部”或“上部”意指远离衬底的一侧或表面,而“底部”、“最下部”或“底部”意指最靠近衬底的一侧或表面。除非另外说明,否则“上方”应被解释为两个结构可以直接接触或者在它们之间可以存在中间层。“层”应理解为具有两个侧面或表面(最上和最下),并且可以存在多个层,而不限于单个层。

[0077]

对于发光单元或层,r表示主要发射红光(》600nm,理想地在620nm至660nm的范围内)的层,g表示主要发射绿光(500nm至600nm,理想地在540nm至565nm的范围内)的层,并且b表示主要发射蓝光(《500nm,理想地在440nm至485nm的范围内)的层。重要的是,r、g和b层可以产生一定程度的所示范围外的光,但是产生的量始终小于原色。y(黄色)表示发射大量r光和g光以及少量b光的层。“lel”意指发光层。除非另外说明,否则波长以真空值表示,而非原位值。

[0078]

在显著的光发射开始回到电压轴之后,可以通过i-v曲线的线性外推来估计oled叠层的阈值电压(v

th

)。这种方法不是精确的,因为oled的i-v响应曲线在它们的响应范围内可能不是完全线性的,所以以这种方式计算的值不是精确的。大体范围是+/-10%。

[0079]

有源矩阵显示器通常被理解为具有以正交列和行的二维阵列排列的单独受控的像素的阵列。然而,还应理解,“列”和“行”是主观术语,并不意指任何特定的定向,而是意指仅在单个像素处重叠的两组单独像素。在有源矩阵技术中,“列”通常被描绘为对准在阵列中的垂直方向上,而“行”通常被描绘为对准在阵列中的水平方向上。同样,对于沿着“列”的所有像素,存在通常被称为“数据线”并且被描绘为在垂直方向上的公共电连接,以及对于沿着“行”的所有像素,存在通常被称为“扫描线”或“选择线”并且被描绘为在水平方向上的公共电连接。然而,这些常规术语可以反映或不反映像素的实际物理位置。应理解,发送到像素的“数据信号”控制该像素所需的亮度量,而“扫描或选择信号”控制发送“数据信号”和由像素接收“数据信号”的时序。

[0080]

在有源矩阵显示器中,每个像素必须具有至少一个单独控制的电极,该电极与其它像素的单独控制的电极分开且不同,以便操作。换言之,与在所有像素上是公共的或连续的相比,每个像素的单独控制的电极部分被“分段”或划分成单独控制的部分。通常,像素电路与发光元件的电连接是通过分段电极实现的。应注意,在本说明书的上下文中,“像素”是单独的、一致的和最小的单元,并且不被进一步细分。例如,可以产生白光的彩色像素(即,彩色图像中的离散点)可以由三个分离但空间上相关的“像素”组成,每个像素发射r、g或b光中的一个,它们共同用作彩色像素的子像素。还应注意,像素可以由单个发光元件或一起共同作用的多个共同控制的发光元件组成。

[0081]

在下文中,术语“关断”和“导通”通常用于特定的元件或特征,并且可以根据元件的种类而具有不同的要求。对于像素,“关断”意指没有(或低于阈值的最少量的)光从像素发射,而“导通”意指高于最小水平(高于阈值)的至少一些光被发射。“导通”可以意指完全发射或部分发射,即,高于最小值(理想为零)的一些发射水平。对于像素(即,oled或led)中的发光引擎,“关断”意指在最小亮度以上没有可测量的亮度,而“导通”意指在最小亮度以上有可测量的亮度。对于诸如p沟道和n沟道晶体管的nmos/pmos电路元件,“关断”意指除了

任何泄漏电流之外i

ds

基本上为零;“导通”意指i

ds

非零,并且至少一些电流通过晶体管。这适用于包括扫描晶体管、驱动晶体管、发射晶体管和支路晶体管的所有晶体管,而与晶体管的类型无关。在这种元件中,通过施加到设备栅极的电压来控制“关断”或“导通”。就数据信号或扫描信号而言,“关断”意指施加到像素电路(特别是晶体管的栅极)的数据值使得产生以下描述的任何/所有“关断”条件;同样,“导通”意指施加到像素电路(特别是晶体管的栅极)的数据值使得产生以下描述的任何/所有“导通”条件。

[0082]“关断”的像素的发射量应该不超过最大发射的1%,更优选地不超过最大发射的0.01%。理想地,“关断”的像素应该完全不具有发射。“关断”的像素也可以被称为“暗”或“黑色”像素,它们是等效的。

[0083]

最小发射量可以根据阈值发射值来定义或设置,该阈值发射值将取决于特定显示器的类型和特性。通常,阈值可以是像素能够发射的最大发射的1%或更少,理想地小于最大发射的0.1%,最理想地是零发射。

[0084]

显示器中的数据信号或图像信号由控制电路发送到每个子像素以控制其发射水平。通常,这些图像信号不是连续的,而是被量化为在产生发射的上限或最大电平的信号与不产生发射或产生最少量发射的信号之间的一定数量的等级。这些等级被称为代码值(code value)或cv(以及其它名称)。在显示器中使用的常见系统是cv=0表示没有发射,cv=255表示最大发射,因此在两个极值之间存在254个离散的中间等级。例如,在8位、类srgb颜色编码中,1%强度对应于约cv 26,而0.01%对应于小于一个cv,应注意,使用8位以上或使用不同的非线性编码时,1%或0.01%将对应于不同的cv。理想地,在cv方面,应用pcc电路的发射阈值应《30cv,理想地《5cv,并且最理想地《0cv,或者如果不是8位、类srgb颜色编码,则是等效值。

[0085]

显示器中的数据信号或图像信号由控制电路发送到每个子像素以控制其发射水平。通常,这些图像信号不是连续的,而是被量化为在产生发射的上限或最大电平的信号与不产生发射或产生最少量发射的信号之间的一定数量的等级。这些等级被称为代码值或cv(以及其它名称)。在显示器中使用的常见系统是cv=0表示没有发射,cv=255表示最大发射,因此在两个极值之间存在254个离散的中间等级。因此,在使用介于0和255之间的cv值来控制每个像素单元的亮度的系统中,用于激活该像素单元的pcc的阈值可以是cv=3或更小,并且最理想地是零的cv。

[0086]

上述有源矩阵像素电路的目的是基于来自数据线的信号来接通发光元件(以在某种程度上引起发射)或断开发光元件(无发射或最小发射)。来自扫描线的信号仅控制数据信号被施加到像素的时序。当数据信号的值满足以下标准中的任一个时,将不发生来自像素的发射:

[0087]-其中数据信号的值不足以使像素电路允许该像素的光发射;

[0088]-其中分段电极处的电压小于或等于相对电极处的电压;

[0089]-其中分段电极处的电压减去相对电极处的电压小于发光元件的阈值电压;

[0090]-其中由像素电路根据分段电极处的数据信号提供的电流不足以引起像素的光发射。分段电极处的电流可以小于阳极焊盘的1微安每平方厘米。

[0091]

因此,出于本发明的目的,每当数据信号具有显示控制器预期的使得上述标准中的任一个被满足的值时,像素被认为是“关断”的,并且每当数据信号具有预期的使得上述

标准均不满足的值时,像素被认为是“导通”的。应注意,即使像素根据数据信号的值“关断”,仍然可能存在由于串扰或其它因素(诸如通过晶体管的电流泄漏)引起的一些发射。

[0092]

本发明的像素电路理想地为硅背板的一部分。硅背板来自硅晶片(也称为薄片或衬底)。它们是用于制造集成电路的半导体(诸如晶体硅(c-si))薄片。晶片用作内置在晶片内和晶片上的微电子设备的衬底。其经历许多微制造工艺,诸如掺杂、离子注入、蚀刻、各种材料的薄膜沉积和光刻图案化。最后,各个微电路通过晶片切割而分开并封装为集成电路。晶片由具有规则晶体结构的晶体生长,其中,硅具有金刚石立方结构,金刚石立方结构具有晶格间隔。当切割为晶片时,表面在称为晶体取向的几个相对方向中的一个方向上排列。硅晶片通常不是100%纯硅,而是形成有初始杂质掺杂浓度的硼、磷、砷或锑,其被添加到熔体中并将晶片限定为体n型或p型。

背景技术:

参见“flat panel display manufacturing”souk,l.,ed.,2018的第7章。理想地,硅背板是单晶si晶片。

[0093]

为了提供用于叠层oled的操作的控制电路,在硅晶片的表面上提供薄膜晶体管(tft)以及诸如电容器、电阻器、连接线等的其它组件。例如,参见t.arai的“high performance tft technologies for the am-oled display manufacturing”,thesis,nara institute of science and technology,2016、m.k.han,proc.of asid’06,8-12oct,new delhi、us 9066379和us 10163998。应理解,tft可以包括或不包括作为tft结构的一部分的硅晶片,或者可以由沉积在表面上的单独材料制备。

[0094]

tft可以使用多种半导体材料制成。硅基tft的特性取决于硅的结晶状态,即,半导体层可以是非晶硅、微晶硅或者可以被退火成多晶硅(包括低温多晶硅(ltps)和激光退火)。

[0095]

具有适当控制电路的硅背板的制造是公知的、已知的以及可预测的技术。然而,由于制造工艺和设备的成本和复杂性,建造制造特定背板的设施通常是不实际的。相反,在微电子设备的功能特性已经变得更加标准化的行业中广泛采用代工模式(foundry model)。这种标准化允许设计与制造分开。符合适当设计规则的设计可以由具有兼容的制造方法的不同公司更容易且更廉价地制造。为此,硅背板上的控制电路通常限于从背板制造商提供的一系列选项中选择的标准组件的使用。例如,硅背板的制造商可以提供将诸如1.8v、2.5v、3.3v、5v、8v和12v的晶体管的各种设计结合到客户的设计中的选择,但是将不能够(在不产生大量费用的情况下)提供不包括在所提供的设计中的晶体管。

[0096]

出于本技术的目的,“低电压”(lv)被限定为归类和设计为安全和可靠地在5v或更低电压下工作的模拟微电子组件。“中电压”(mv)微电子设备通常被认为在9v至12v的范围内,而“高电压”(hv)微电子设备通常被认为在18v至25v的范围内。应注意,这些电压额定值由制造商设定,并且制造商不建议超过为每个晶体管设定的最大电压。

[0097]

在电激活时产生光(发光)的有源矩阵显示器沉积或集成到位于硅芯片上的薄膜晶体管(tft)阵列上,其中tft阵列用作一系列开关以控制流到每个单独像素的电流。通常,该连续电流由每个像素处的至少两个tft控制(以触发发光),其中一个tft用于开始和停止存储电容器的充电,第二个tft用于提供为像素产生恒定电流所需的电平的电压源。

[0098]

如图1所示,图1表示现有技术的有源矩阵像素设计的最简单的形式。在有源矩阵显示器中,存在控制每个单独像素并且位于背板的显示区域内的单独像素电路。具有像素存储器的最简单的有源矩阵像素电路使用两个晶体管和一个电容器。电流驱动晶体管mp2

通常从电源电压vdd连接到发光元件的分段电极。如图所示,一个tft(mp2)驱动元件的电流,而另一个tft mp1用作开关以采样并保持存储电容器c1上的电压。存在控制流经驱动晶体管mp2的电流(i

vdd

或i

sd

)的数据线(v

data

)。存在控制扫描(选择)晶体管mp1并因此控制电容器c1的充电的选择线。通常,晶体管具有本征电容,因此根据晶体管的本征电容和通过晶体管的泄漏电流,可能不需要额外的电容。为了清楚起见,在图1之后的附图中,可以从附图中省略任何存在的电容器。

[0099]

图2示出了基本像素电路100,其用于通过确保在像素的分段电极处的电压和/或电流在像素的数据信号使得像素不应发射任何光时总是保持在发射所需的水平以下来控制显示器中的串扰量。如所指出的,各种串扰源可导致在像素的分段电极处出现足够量的电压和/或电流以实现一定程度的发射,而不考虑该像素是否接收到足以导致发射的数据信号。特别地,在由数据信号确定为非发射的像素中,由足以引起发射的串扰产生的电压和/或电流是有问题的。

[0100]

在单个像素的基本像素电路100中,存在连接到驱动晶体管t1的源极的电源1和连接到t1的漏极的发光元件2的分段电极。t1的栅极通过扫描(选择)晶体管t4的源极和漏极连接到数据线3。t4的栅极连接到扫描线4。数据线3提供通常为电压的数据信号v

data

。扫描线4提供通常为电压的扫描信号v

scan

。像素控制电路(pcc)5附接到位于t1的漏极和发光元件2的分段电极之间的node1。pcc 5还连接到数据线3以及接收器6。发光元件2的相对电极连接到第二电源7。在该示例中,t1和t4是p沟道晶体管。

[0101]

node1是沿着电力线定位在驱动晶体管和像素(2)之间的电连接。理想地,在node1和发光元件(2)之间不存在串联连接的其它电学组件。理想地,在node1和电源(1)之间存在至少一个串联的驱动晶体管。

[0102]

在操作方面,每当通过数据线3和选择晶体管t4传递到t1的栅极的数据信号使电流流过t1,电源1将向发光元件2的分段电极提供足够的电力,并且因此,像素将根据数据信号的大小发射。选择晶体管t4由扫描线4控制,以选择单独的像素行。在未选择的像素行中,t4防止来自数据线3的电压流到驱动晶体管t1的栅极,并且因此,t1不能使电流从电源1流动到发光元件2的分段电极,因此,像素不改变其发射直至扫描线将像素重新连接到数据线。

[0103]

pcc 5通过在数据信号不允许电流流过t1(即,不期望来自像素的发射)时将分段电极2处的电压和/或电流维持在引起光发射所需的电压和/或电流以下,来帮助防止像素中来自串扰的发射增加。pcc 5使用数据信号作为输入。每当数据信号不会引起像素发射或使像素仅具有非常低的发射时,pcc 5将分段电极2电连接到接收器6,其将电压和/或电流保持在低于引起像素发射所必需的水平。然而,每当数据信号将引起像素发射时,pcc 5不将分段电极2连接到接收器6。以这种方式,即使由于串扰而在像素处存在足以发射的电压和/或电流,只要数据信号使得该像素应是非发射的,则可以防止该像素具有发射。当像素发射量应高于某个最小量时,pcc 5不涉及像素的驱动。应注意,pcc 5是否将分段电极2连接到接收器6由从数据线3接收的数据信号的值来确定,并且与该行是否通过扫描线4选择无关。

[0104]

pcc 5是像素电路100的组成部分。像素电路的组成部分意指pcc5与驱动晶体管和像素电路的其它组件一起局部地位于背板中、位于像素下方以及有源显示区域内。pcc 5在

帧周期内一次仅控制一个像素,所述控制根据该像素的数据信号。其不控制通常由扫描或选择线选择的沿着同一行的其它像素。

[0105]

pcc 5不是确定和控制数据信号和扫描/选择信号的时序的设备电路(显示控制器)的一部分,所述控制器电路通常位于有源显示区域外部。一般而言,显示(图像)控制器将多个图像信号转换成多个图像数据信号并将其发送到数据驱动器。控制器接收垂直同步信号vsync、水平同步信号hsync和时钟信号,产生用于控制扫描驱动器、发射控制驱动器和数据驱动器的控制信号,并将它们发送到适当的线。此外,控制器产生用于控制电源的电力控制信号,并将其发送到电源。尽管控制器的内部操作可以使用数据信号和扫描信号来导通或关断特定像素,但这与本发明不同,在本发明中,“关断”像素的支路的启用在局部单独像素电路中确定且基于数据信号。

[0106]

接收器6是控制像素的分段电极处的电压的像素电路组件。它可以包括与将电压保持在像素的v

th

以下的电源v

bias

的电连接以防止发射。用于v

bias

的电源布线优选地对于所有像素是公共的,以使背板更简单、更紧凑以及具有更低的成本(更低的掩模级别)。接收器6还可以连接到地线或具有与像素的相对电极125(通常为v

ss

)的电连接。

[0107]

图3示出了与图2中的电路100类似的基本像素电路150。特别地,pcc 5(虚线框内)具有连接在node1和接收器6之间的支路晶体管t3。支路晶体管t3的栅极通过连接到数据线3的判定电路9来控制。当判定电路9确定数据信号的值足以使像素发射高于一些预定量的光时,t3的栅极处的电压被设置成使得t3不会将电流从node1传递到接收器6。然而,当判定电路9确定数据信号使得像素不应发光(或小于一些预定量的发射)时,则t3的栅极处的电压被设置成使得node1和接收器6电接触,并且因此,存在于分段电极处(例如,由于来自任何原因的电学串扰)的任何电压和/或电流将被去除,如此,像素将不具有发射。在本实施方式中,判定电路9仅使用来自数据线3的数据信号作为输入来判断如何设置t3的栅极处的电压。一般来说,支路晶体管t3被控制为通过适当地控制栅极电压而完全“导通”(允许电连接)或完全“关断”(没有电连接)。

[0108]

如所指出的,判定电路9基于像素的数据信号,确定该像素应为“导通”还是“关断”,然后适当地激活t3,以允许或不允许电势从分段电极2传递到接收器6。t3的这种控制可以仅基于数据信号而没有其它输入。这种仅基于数据信号的判定可以以多种方式或方法进行。

[0109]

例如,考虑具有像素电路的显示器的示例,其中,当来自像素的发射应为“关断”时,表示为电压v

data

的数据信号为零,而当来自像素的发射应为“导通”时,数据信号为高(非零)。在这种情况下,可以在不做修改的情况下直接使用v

data

作为如图7中200所示的锁存电路10的输入。锁存电路10的输出v

latch

随后将与v

data

(零或高)相同,尽管在整个帧的其余部分固定为该值直至复位。如果驱动晶体管和扫描晶体管(以及快门晶体管t6(如果存在,参见图11))是p沟道晶体管并且t3是n沟道晶体管,然后如果传输到t3的栅极的输出电压v

latch

为零,则t3将“关断”,但是如果v

latch

为高,则t3将“导通”。然而,在一些驱动方法中,v

data

可能不足以使t3完全“导通”。这是不期望的,因为当像素“关断”时,它将不能使存在的任何电流都绕过像素。在这种情况下,作为判定电路9的一部分,非零v

data

可以激活将t3的栅极与另一电源(例如,电源1的电压v

dd

)连接的开关,该开关具有足够的电平来使t3导通,或者v

data

可以通过包括电压倍增电路而被转换为较高的电压。如果需要,可以另外存在电

压限制器电路(通常包括齐纳二极管)。

[0110]

图3还示出了判定电路9和参考源8之间可以存在电连接。在一个实施方式中,可以通过将数据信号与参考信号进行比较来确定数据信号是否足以引起发射。例如,如果来自数据线3的数据信号是电压信号v

data

且来自参考线8的参考信号是电压v

ref

,则可以使用v

data

和v

ref

之间的差值来设置支路晶体管t3的栅极处的电压,以允许或不允许node1和接收器6之间的电连接。在一些情况下,电源1可以用作参考信号。例如,电源1保持在电压v

dd

,然后v

dd

可以用作参考信号以与v

data

(v

ref

=v

dd

)进行比较。参考信号的值可以高于或低于数据信号。参考信号8对于所有像素是公共的。

[0111]

通常,判定电路9可以包括具有告知输入电压是否高于或低于给定阈值的功能的判定电路。判定电路也可以比较两个电压并提供指示哪个更大的输出结果。判定电路(有时称为比较器或比较器电路)通常用于例如检查输入是否已达到某一预定值。用于oled的比较器电路是公知的。例如,参见us 9786209 b2、us 20060082528 a1、us 20190088205、us 7595596 b2、in等人的“p-8:a novel feedback-type amoleds driving method for large-size panel applications”,society for information display,36(1),252(2005)以及neha等人的“design and analysis of comparators using 180nm cmos technology”,international j.of elec.and comm.tech.,7(2),122(2016)。

[0112]

在图4中示出了需要参考信号的适当判定电路9的一个示例,其中,比较器电路20(其为判定电路的一部分)使用双极结型晶体管(bjt)。在图4中,简单比较器20具有两个工作状态,两个工作状态为bjt q1“导通”以及bjt q2“关断”、或者q1“关断”以及q2“导通”。q1和q2的阈值“导通/关断”电压是那些晶体管的v

be

(基极和发射极之间的v差)“导通”电压。对于q1“导通”以及q2“关断”,v

ref

比v

data

大一定量,使得q1的v

be

比q2的v

be

大。电阻器r3(v

r3

)与q1和q2的发射极的连接处的电压变为等于v

ref-v

be

(q1)。这足以使v

data-v

r3

不足以保持q2“导通”。如果v

data

大于v

ref

,则由于相同的理由,q2“导通”且q1“关断”。q2的“导通”/“关断”状态通过q2的输出与t3的栅极的连接来控制t3的“导通”/“关断”状态。当q2“导通”/“关断”时,t3“导通”/“关断”。v

cc

和v

ee

提供电路组件运行所必需的外部工作电压源。v

cc

应该比可以连接到地线的v

ee

电位更高(more positive)。

[0113]

图5示出了除了r3被r3、r4、z1(齐纳二极管)、q4电路代替之外以与图4相同的方式操作的另一比较器电路21。该电路提供恒定的q4电流(v

z1-v

be

q4-vee)/r4,其确定了在q1和q2切换之前v

ref

必须比v

data

大多少。其应提供比图4的比较器电路更精确的输出。

[0114]

图6示出了基于使用cmos组件的另一比较器电路22的示例。在功能方面,t11和t12取代r1和r2。t13和t14取代q1和q2。t15取代r3、r4、q4和z1。t15设置偏置电流,该偏置电流由等于v

bias-v

ee

的t15的栅极到源极电压(v

gs

)设置。t11和t12提供t13和t14的有源负载电流镜。t12的漏极-源极电流(i

ds

)等于t11的漏极-源极电流。该电流的值由t11的栅极-源极(v

gs

)电压确定。t11的v

gs

等于t13的v

cc-v

drain

。t13和t14将具有两个状态:t13“关断”以及t14“导通”、或者t13“导通”以及t14“关断”。t12和t14的公共漏极连接(n1)驱动支路晶体管t3的栅极。

[0115]

如果连接到t13的栅极的电压v

ref

小于连接到t14的栅极的v

data

,则t13“关断”,t14“导通”,并且n1电位变低,使得t3(支路晶体管)“导通”。其机理是随着v

data

增加至大于v

ref

,n2处的电压变为t14的v

data-v

gs

。t14的v

gs

使得t14的i

ds

=t15的i

ds

(偏置电流)。在该点处,

t13的v

gs

=v

ref-v

n2

小于t13的阈值电压,并且t13“关断”。当t13“关断”时,t13的i

ds

=“关断”,因此t11和t12的i

ds

=“关断”。t14将其i

ds

设置为i

bias

,但t13“关断”,t14的v

drain

降低,以导通t3。

[0116]

如果连接到t13的栅极的电压v

ref

大于连接到t14的栅极的v

data

,则t13“导通”,t14“关断”,并且n1电位将变高,使得t3(支路晶体管)“关断”。该机理现在相反,n2处的电压变为t13的vref-v

gs

,其中t13的v

gs

使得t13的i

ds

=t15的i

ds

(偏置电流)。t11和t12的i

ds

=t13的i

ds

。t14的v

gs

减小,直到其小于t14的阈值电压,并且t14“关断”。t14的漏极电压现在上升,以使t3“关断”。

[0117]

图7示出了类似于图3中的电路150的基本像素电路200。尽管在本实施方式中t1和t4示出为p沟道晶体管,t3示出为n沟道晶体管,但这不是限制性的,并且可以存在其它布置。pcc 5(虚线框内)具有位于判定电路9和支路晶体管t3的栅极之间的锁存电路10。判定电路9的输出信号(例如,电压v

output

)是锁存电路10的输入,并且应该是“导通”或“关断”信号的形式,该信号指示支路晶体管t3允许还是不允许分段电极2和接收器6之间的电连接。锁存电路10的目的是在帧的整个剩余部分将支路晶体管t3的控制锁定到由判定电路9所确定的像素的设置,并且防止在写入后续行的时候由于数据信号的改变而使该设置发生任何进一步改变。锁存电路10也接收来自分路时钟11的输入,该分路时钟11提供锁存的时序。

[0118]

锁存电路(也称为触发电路)的使用和操作是公知的,并且已经在oled中使用。例如,参见us 8068072、us 20090295770以及us 10546541。

[0119]

像素电路200的一般操作顺序在图8的流程图中示出。在第一步骤中,显示控制器电路(其位于显示区域之外)确定合适的数据信号,该信号在单个图像帧期间将从沿着行的每个像素产生所需的光发射。其还将初始化所有像素为接收根据图像信号的数据做准备。该初始化包括复位作为显示控制器的一部分的扫描时钟和分流时钟。

[0120]

在第二步骤中,显示控制器经由扫描线4发送扫描信号,其将扫描晶体管t4设置为“导通”用于整个第一行像素。扫描时钟控制扫描信号激活哪些行的时序。

[0121]

在与第二步骤同时进行的第三步骤中,通过数据线3为沿着该第一行的每个单独的像素发送数据信号。数据信号用作像素电路的两个不同部分的输入。在第一部分中,信号数据通过t4到达驱动晶体管t1的栅极。数据信号控制驱动晶体管t1的栅极,以允许适当量的电力从电源1传递到发光元件2。在第二部分中,数据信号输入到控制支路晶体管t3的栅极的pcc 5。

[0122]

step 4取决于数据信号。如果数据信号使得t1“导通”,并且因此电力可以从电源1流到发光元件2,则像素将发光。同时,pcc 5的判定电路9确定数据信号是否足以使t1“导通”。在像素电路200的情况下,通过将数据信号与参考信号进行比较来进行所述确定操作。如果数据信号和参考信号之间的差值确定数据信号将引起像素发射,则“关断”信号作为判定电路9的输出发送到锁存电路10。锁存电路10然后将输出信号传递到支路晶体管t3的栅极,使得t3“关断”,并且不允许2的分段电极和接收器6之间有电连接。锁存电路10还“锁定”“关断”信号,并在整个帧期间保持该信号,直到在新帧的初始化期间复位。以这种方式,支路晶体管t3的存在对发射像素的操作没有影响,并且显示器以正常方式工作。

[0123]

然而,如果数据信号和参考信号之间的差值确定数据信号将不允许像素发射,则“导通”信号作为判定电路9的输出发送到锁存电路10。然后,锁存电路10“锁定”t3的栅极处

的“导通”信号,并在整个帧期间保持该信号,直到在新帧的初始化期间复位。以这种方式,每当数据信号指示像素不应发光时,支路晶体管t3“导通”,并且因此发光元件2的分段电极处的任何电力将被分流到接收器6,并且将不存在来自像素的任何发射。在这种情况下,保护像素不受由电学串扰以及通过驱动晶体管t1的任何电流泄漏引起的发射的影响。

[0124]

锁存电路10的时序由分路时钟11控制,分路时钟11是显示控制器的一部分,并且在数据和扫描信号针对该像素写入并且由pcc 5进行确定的时间期间激活锁存电路10。分流时钟11针对于行,且锁存电路10防止写入到后续行的数据而不影响写入到先前行的数据。尽管分路时钟11可以与控制发送到t4的栅极的扫描信号的时序以允许该数据信号传递到t1的栅极的扫描时钟不同,但是理想地二者是相同的。其还可以与扫描信号同时启动,并且在扫描信号结束之前结束。

[0125]

重要的是,锁存电路10在图像帧的整个时间内保持t3处的“导通”或“关断”信号直到重新初始化。这是因为数据线一次或另一次为列的每个单独像素提供数据信号。在正常操作中,由于扫描晶体管t4“关断”,因此数据信号不被扫描信号未选择的任何行中的像素接收。然而,在这种情况下,pcc 5将接收用于不同行中的其它像素的数据信号,而不考虑其行是否接收到激活t4的扫描信号。通过在像素正在有效地接收预期数据信号时“锁定”控制t3的信号,用于其它像素的数据信号将不影响支路晶体管对于该单独像素是“导通”还是“关断”。

[0126]

这是仅基于数据信号的值来使用pcc控制支路晶体管而不直接涉及扫描信号的优点之一。作为步骤1的初始化的一部分,可以将表示像素应“关断”的数据信号同时发送给所有像素,使得pcc 5使支路晶体管t3“导通”,并且因此,不存在由于任何原因导致的像素发射。然后,在步骤2至步骤7中,当依次扫描每行时,每个像素中的支路晶体管t3“关断”或“导通”(由数据信号确定)。这意指尚未激活的任何相邻像素行将使支路晶体管“导通”。例如,当第n行被激活并且支路晶体管t3根据该像素是否应该发射的数据信号而“导通”或“关断”时,支路晶体管t3将对于整个第(n+1)、第(n+2)等行“导通”。由于第n行中的一些像素将发射,因此串扰会在第(n+1)、第(n+2)等行中的相邻像素中的分段电极处引起电势,即使它们还没有被激活。然而,由于支路晶体管t3在这些未激活的行中“导通”,因此它们不能发射。以这种方式,可以减少串扰的影响。

[0127]

使用pcc的另一个优点是滚动扫描可以用于串扰最小化,其中,活动(“导通”)显示行以“关断”线为边界。因此,对于行n、(n+1)、(n+2),行(n+1)中的像素将“导通”,而行n和(n+2)将“关断”。以这种方式,也可以减小串扰效应。

[0128]

还可以在扫描并激活行中的每个像素之后,重新发送表示沿着该行的所有像素应“关断”的数据信号。这将要求第二扫描信号激活最近激活的行,以发送“关断”数据信号。例如,扫描信号激活第n行以接收用于该行中的像素的适当的“导通”或“关断”数据信号。然后,当扫描信号沿行向下移动并激活第(n+1)行时,扫描信号重新发送到第n行,但是数据信号指示所有像素应“关断”。然而,这两个扫描信号的时序必须不重叠,使得第n行和第(n+1)行可以各自在正确的时间接收正确的数据信号。例如,可以调整时序,使得显示控制器在激活第(n+1)行之后,但是在激活第(n+2)行之前,发送扫描信号以利用将第n行像素设置为“关断”的数据信号来激活第n行。以这种方式,将防止更多的像素由于串扰而发光。

[0129]

为了使图7中示出的以及图8中描述的电路的操作更具体,一个实施方式可以是其

中驱动方案是模拟的并且信号和电源可以用电压表示,并且驱动晶体管t1和扫描晶体管t4是p沟道晶体管并且支路晶体管t3是n沟道晶体管。应注意,对于n沟道晶体管,高电压施加到栅极(即,vg大于vs)允许晶体管导通,而低电压施加到栅极(即,vgs=0)导通截止。对于p沟道晶体管情况是相反的。在该实施方式中,电源1是电压v

dd

,扫描信号是电压v

scan

,数据信号是电压v

data

,参考信号8是电压v

ref

,判定电路9的输出是电压v

output

,而锁存电路10的输出是电压v

latch

。在这种情况下,当v

data

高(例如等于v

dd

)时,像素应不发射。当v

data

低(例如等于零或为负)时,则像素将以其最大水平发射。当0《v

data

《v

dd

时,发射将处于中间水平。

[0130]

在该实施方式中,图7所示的像素电路的电路操作(参见图8)可以描述为:

[0131]-步骤1:分路时钟11设置为零。初始化包括发送v

data

为高的数据信号,使得pcc 5使t3“导通”,从而绕过发光元件。

[0132]-步骤2和步骤3:扫描信号v

scan

施加到作为p沟道晶体管的t4的栅极,使得数据信号v

data

随后被连接到作为p沟道晶体管的驱动晶体管t1的栅极。同时,v

data

直接从数据线3发送到pcc 5内的判定电路9。

[0133]-步骤4:判定电路然后将v

data

与v

ref

进行比较,以确定v

data

是否大于、等于或小于v

ref

,在这种情况下确定v

data

为低或为零。如果v

data

大于v

ref

(在本实施方式中表示像素不应发射(因为高v

data

将使t1“关断”)),则判定电路9的v

output

处于高电平。如果v

data

小于或等于v

ref

(在本实施方式中表示像素应发射(因为低或零v

data

将使t1导通)),则v

output

将为低或为零。

[0134]

当分路时钟11从零变为高(非零)值时,锁存电路10接收v

output

。然后,锁存电路10的输出v

latch

被设置为与v

output

相同。然后,分流时钟11从高值变回零。这将v

latch“锁定”为与v

output

相同的值,并且如果v

output

随后改变其不再改变。然后v

latch

施加到作为n沟道晶体管的支路晶体管t3的栅极。当v

latch

(当分路时钟11为高值时,v

latch

与

voutput

相同)为低/零时,t3为“关断”,并且像素正常发光。当v

latch

为高(非零)时,t3“导通”,并且像素将不发射,因为任何电流都被分流到接收器6。

[0135]

使用根据信号数据的pcc的优点之一是允许沿着整个列的任何“关断”像素的分段电极处的任何电压和/或电流分流,而不受任何串扰的影响,不管该像素是否在选定行中。根据扫描信号以分流分段电极处的电压和/或电流的现有技术的解决方案仅应用于激活的行。以这种方式,具有串扰保护的可能的“关断”像素的总数将增加,并且串扰的总量将减少。

[0136]

然而,不是所有在帧时间期间可能“关断”的像素将通过使用数据信号来分流分段电极处的任何电压和/或电流以防止发射来恢复。为此,使用数据信号引起分流的方法可以与其中分流基于扫描信号的任何已知方法一起使用。当组合使用时,根据图像将是“关断”的任何像素将被分流,并且将不会发射。

[0137]

图9a和图9b示出像素电路250作为这种组合的示例。除了附加电路将扫描线4连接到与node1连接的t5的栅极之外,图9a与图2类似。在该附加电路中,第二支路晶体管t5将控制分段电极/node1处的任何电压和/或电流是否被分流到电源12,电源12将电压保持在像素的v

th

以下以防止发射。用于12的电源布线优选地对于所有像素是公共的。源12也可以连接到接收器6、直接连接到地线或电连接到像素的相对电极(通常为v

ss

)。然而,晶体管t4和t5不能同时“导通”,尽管二者可以同时“关断”。由于t4和t5都由来自扫描线4的相同信号控

制,所以可能有必要使信号反转,使得晶体管t5“导通”以在t4“关断”时将node1连接到源12。扫描信号的反转方法有多种,例如,可以通过可选的反相器电路18a,或者晶体管t5可以是与扫描晶体管t4不同的类型(例如,t4是p沟道晶体管,而t5是n沟道晶体管)。还可以将允许根据来自扫描线4的扫描信号进行分流的附加电路合并到pcc 5中。

[0138]

图9b示出了作为像素电路250(图9a)的变体的像素电路300。在像素电路300中,第二支路晶体管t5的栅极直接由单独的信号线13控制。在该实施方式中,来自信号线13的信号可以具有与来自扫描线4的扫描信号相同的时序,但是在控制器电平处被反转。或者,来自扫描线13的信号可以具有与来自扫描线4的信号不同的时序。

[0139]

在任何情况下,扫描线4或13的目的是控制第二支路晶体管t5的栅极,以使其在像素发射时“关断”,而在像素不发射时“导通”,而不考虑第一支路晶体管t3是“导通”还是“关断”。最理想的是,当像素不发光且t3“关断”时,t5“导通”。

[0140]

图9c示出了像素电路250和300的另一变体350,其中,附加电路直接并入为pcc 5的一部分,并且在发光元件2不发光时使用单个支路晶体管t3来绕过发光元件2。在这种情况下,支路晶体管t3的栅极可以通过锁存电路10的输出(其仅取决于数据信号)或者通过来自信号线14的信号来控制。来自信号线14的信号可以与扫描线4相同,或者如果需要可以由可选的反相器电路18b(类似于250中的可选的反相器电路18a)进行反相。在这些情况下,扫描线4可以用作信号线14。或者,信号线14可以由显示控制器独立地控制并控制时序,使得其不干扰t3的控制。在这种情况下,期望地每当像素不发射时,t3由锁存电路10或信号线14(而非两者)“导通”。

[0141]

图10a示出了与图3中的电路150类似的基本像素电路275。特别地,pcc 5(虚线框内)中的判定电路9连接到扫描线4而不是数据线3。在该实施方式中,每当扫描信号4使得扫描晶体管t4“关断”且驱动晶体管t1未接收数据信号时,node1和接收器6将(通过支路晶体管t3)电接触。在有源矩阵设备中,通过每个像素的扫描晶体管激活整个像素行,然后允许通过驱动晶体管将数据信号加载到每个像素中。然而,由于该过程是逐行依次执行的,因此存在数据信号尚未被传输到像素的行,并且因此,这些像素不应发射。然而,这种待激活的像素在空间上可能靠近正在发射的像素。通过在t4为“关断”时允许分段电极109和接收器6之间的电连接,可以防止这些尚未被激活的像素中由于串扰或类似问题而导致的潜在发射。

[0142]

然而,这本身并不是完全足够的,因为每当扫描信号4指示扫描晶体管t4“导通”使得驱动晶体管t1根据数据信号3激活,一些像素可能“导通”(具有至少一些发射),而一些像素可能根据数据信号(基于图像)“关断”(无发射)。为了另外防止激活行中的任何“关断”像素的发射,使用指示像素是否应该发射的支路线17。

[0143]

支路线17可以是操作与150(图3)中的参考源8相同的参考源,在这种情况下,在判定电路9和数据线3之间存在单独的电连接(未示出)。在这种情况下,判定电路9将来自数据线的信号与来自参考源8的信号进行比较,以确定数据信号3是否足以引起发射。如果确定像素应发射,则判定电路9将t3设置为“关断”,以允许该像素以预期水平发射。如果确定像素不应发射,则判定电路9将t3设置为“导通”以防止非预期的发射。

[0144]

或者,表示像素是否应发射的来自3的数据信号与参考信号之间的比较不必在pcc 5内进行,而是在电路的不同部分中进行。在这种情况下,判定电路9可以直接使用来自支路

线17的信号。

[0145]

图10示出了用于275的pcc 5(图10a)的一个可能的电路的细节。在pcc 5的该示例中,判定电路9包括串联在支路线17和t3的栅极之间的晶体管tb。在该特定的实施方式中,来自支路线17的信号已经反映了数据信号与参考信号的比较,以确定像素是否应发射。该pcc的操作模式如下:

[0146]-连接到t4的栅极的扫描线4“关断”,并且因此t4“关断”,因此不向t1的栅极提供数据信号,因此t1“关断”。

[0147]-连接到tb的栅极的扫描线4“关断”,并且因此tb“关断”,因此不向t3的栅极提供数据信号,因此t3“关断”。

[0148]-连接到t4的栅极的扫描线4“导通”,并且因此,t4“导通”,因此,数据信号从3提供到t1的栅极。t1根据来自3的数据信号的幅度而“导通”或“关断”。

[0149]-连接到tb的栅极的扫描线4“导通”,并且因此,tb“导通”,因此,信号从支路线17提供到t3的栅极。

[0150]-如果来自3的数据信号的幅度使得t1“关断”(无发射),则来自支路线17的信号将使t3“导通”,因此,像素2的分段电极处的任何电荷将被分流到接收器6,使得像素2不发射光。

[0151]-如果来自3的数据信号的幅度使得t1“导通”(某种程度的光发射),则来自支路线17的信号将使t3“关断”,因此,像素2将根据来自3的数据信号的幅度发射光。

[0152]

在上述两个选项中,判定电路9位于pcc 5内。其基于来自4的扫描信号与来自3的数据信号的某种组合来控制t3的操作。图11示出除了pcc不包括判定电路之外其余与275类似的替代电路285。提供与275中的判定电路9所描述的相同功能的判定电路19位于pcc 24外部。理想地,判定电路19是向t3提供适当的信号的图像控制器的一部分。

[0153]

在275和285两者中,判定电路9将向t3的栅极输出信号,该信号将适当地启用或禁用t3。如果来自3的数据信号的值由于t1未接收到数据信号(t4“关断”)或者由于从3接收到不发射的数据信号使得t1将“关断”(驱动值=0),则来自9的信号将启动t3。如果来自3的数据信号的值使得t1将“导通”,则来自9的信号将禁用t3。理想地,每个像素应具有单独的且独立的支路线17,其通过判定电路来控制t3的栅极。

[0154]

在275和285中,理想地,t1是p沟道晶体管和/或t3是p沟道晶体管。t1和t3也可以是n沟道晶体管,或者t1可以是p沟道晶体管而t3可以是n沟道晶体管。

[0155]

图2、图3、图7以及图9a至图9c示出数据线3直接连接到pcc 5的实施方式。在其它实施方式中,数据信号可以在数据信号经过扫描晶体管t4之后通过pcc 5接收。与pcc 5的连接可以在t4和t1的栅极之间。利用这种类型的连接,pcc 5将只接收沿所选行的该像素的数据信号,而不接收其它的数据信号,因为每当数据信号发送到其它像素行时,t4将“关断”。尽管数据信号可以直接用于控制t3的栅极,但是仅当数据信号的值足以完全“导通”(当像素“关断”)或“关断”(当像素“导通”)t3(诸如使用数字驱动时)时才有效。在诸如模拟驱动的其它驱动方法中,数据信号的值控制像素的亮度的大小,因此,中间数据信号值(完全“关断”的值/像素的值/完全“导通”的值)是常见的。因此,对于这些类型的驱动方法,数据信号不能被用来直接控制t3,因为t3可能不能被完全“导通”或“关断”。如果像素不完全“导通”,则t3将不完全“关断”,而且允许一些电流分流,因此像素将不会发射所需亮度的

光。这是不期望的。在这些实施方式中,pcc 5可以包括开关,该开关将t3的栅极与另一电源(例如,电源1的电压v

dd

)连接,该另一电源具有足够的电平以使t3“导通”。这种开关可以基于数据信号的值进行操作。或者,可通过包括电压倍增器电路或电平移位器电路将v

data

转换为较高电压。如果需要,可以另外设置电压限制器电路(通常包括齐纳二极管)。

[0156]

在一些实施方式中,pcc可能需要电源。pcc电源可以与电源1(即,v

dd

)相同,或者其可以是单独且独立的电源。

[0157]

可以在整个帧时间内激活pcc。在一些情况下,取决于图像要求,可以在多个连续帧内或者在一定数量的帧中的有限数量的帧内激活pcc。例如,可以仅在10个帧中的5个帧内激活pcc,例如,前5个帧激活后5个帧不激活或者在10个帧内以交替方式激活(诸如10个帧交替开启/关断、或者10个帧内2个帧开启/2个帧关断)。在一些情况下,可能期望仅在单个帧的一部分中激活pcc。例如,pcc可以在半帧内激活,而在该帧的剩余部分中关断。

[0158]

尽管上述像素电路可以用于任何类型的显示器,特别是有源矩阵显示器,但是它们特别适用于有源矩阵oled微显示器,甚至更理想地适用于高电压多模(白色)微腔oled。这是由于操作这种oled所必需的高电压以及允许载流子从一个“导通”像素迁移到另一可能“关断”的相邻像素的公共层,因此在相邻的“关断”像素中产生足以引起发射的电压,并且微腔oled中的层需要足够厚(以便产生微腔),这促进了侧向载流子迁移。

[0159]

微显示器需要非常高的亮度以在所有环境条件(诸如阳光强烈的户外)下使用。即使在诸如vr谷歌(googles)的受控环境条件下,也需要非常高的亮度来创建身临其境的视觉体验。显示器的非常高的亮度允许使用更小、更轻、更便宜的低效率光学设备,从而产生更具竞争力的头戴式耳机。

[0160]

目前,现有技术的oled微显示器无法提供所需的亮度。例如,一家串联(tandem)oled微型显示器制造商的新闻稿描述了可能能够提供高达2.5k尼特的全色产品,但是承认5k尼特将是更理想的目标(参见https://www.kopin.com/kopin-to-showcase-latest-advances-in-its-lightning-oled-microdisplay-line-up-at-ces-2020/,2020年1月7日)。一些制造商提出目标应为10k尼特或更高(参见https://hdguru.com/calibration-expert-is-10000-nits-of-brightness-enough/,2018年7月26日)。2020年6月20日的新闻稿(参见https://www.businesswire.com/news/home/20200630005205/en/kopin-announces-breakthrough-colormax%e2%84%a2-technology-unparalleled-color)描述了一种发射》1000尼特的串联(2叠层)oled显示器。其还报道了“通过优化oled沉积条件预期进一步改善亮度(》2000尼特)和色彩保真度。通过结合增强输出耦合效率的结构,可以在几年内将oled微显示器的亮度增加到》5000尼特”。

[0161]

增加从oled设备发射的光的总量的一种解决方案是将多个oled单元彼此堆叠,从而让从叠层发射的光的总量是每个单独的层发射的光的总和。然而,尽管从这种oled叠层发射的光的总量基于单独oled发光单元的总数加和,但是驱动oled叠层所需的电压基于驱动每个独立oled单元的电压加和。例如,如果发光oled单元在给定电流下需要3v来产生250尼特,则两个这样的单元的堆叠将需要6v来在相同电流下产生500尼特,3个单元的堆叠将需要9v来产生750尼特等。

[0162]

这种oled叠层是公知的,例如参见,us 7273663、us 9379346、us 9741957、us 9281487以及us 2020/0013978,其全部描述了具有多个发光oled单元堆叠的oled叠层,其

中,每个发光oled单元堆叠由中间的连接层或电荷产生层间隔开。springer等人,optics express,24(24),28131(2016)报道了具有2个和3个发光单元的oled叠层,其中每个单元具有不同的颜色。已经报道了多达六个发光单元的oled叠层(spindler等人,“high brightness oled lighting”,sid display week 2016,san francisco ca,2016年5月23-27日)。此外,使用串联oled叠层(由一个cgl分隔的两个发光oled单元)来发光的具有低电压5v驱动晶体管的硅背板是可用的。参见,例如,cho等人,journal of information display,20(4),249-255,2019、https://www.ravepubs.com/oled-silicon-come-new-joint-ribture/,2018年出版、以及xiao“recent developments in tandem white organic light-emitting diodes”,molecules,24,151(2019)。

[0163]

然而,这种将需要更高驱动电压的方法难以应用于微显示器应用中。问题在于,微显示器还需要具有高分辨率,要求单个像素的尺寸必须尽可能小,并且微显示器的有源(发光)区域包括尽可能多的像素。这要求背板的控制电路中的晶体管很小,但仍具有足够的尺寸以处理所需的电压和电流而不会永久损坏或产生电流泄漏。此外,使用具有较小、低电压晶体管的电路允许在给定大小的设备内设置较高的像素密度。然而,尽管具有高密度的单独受控的像素对于高分辨率设备是理想的,但是它加重了串扰问题,其中给一个像素供电可能引起相邻像素的光发射。

[0164]

使用具有多个叠层的微腔oled(其具有增加的发射)的另一困难是还需要较高的电压来操作。高电压仅会促进像素内载流子迁移的产生,因此,可以增加向相邻像素的迁移,从而增加串扰,发生非预期的发射。

[0165]

在临时美国申请62/966,757和63/054,387以及非临时美国申请16/695,191中已经描述了合适的多模微腔oled方案。在这些参考文献中描述的任何方案、说明或实施方案可应用于本发明。图12中示出了合适的多模微腔oled微显示器400。

[0166]

图12示出了使用多模(白色)oled微腔的微显示器400,该微腔对于所有像素共用并且具有滤色器阵列(cfa)以产生r、g和b像素。多模oled产生多于一种颜色的光。理想地,多模oled产生具有大致等量的r、g和b光的白光。通常,这对应于cie

x

和ciey的值约为0.33和0.33。然而,根据用于产生rgb像素的滤色器的特性,与这些值的一些偏差仍然是可接受的或者甚至是期望的。微显示器400还包括微腔效应。在该实施方案中,多模oled叠层包括发射不同颜色的光的三个oled发光单元,其中每个单元通过cgl与另一单元垂直间隔开,其中在有效区域中反射表面和顶部电极之间的距离是恒定的。

[0167]

在微显示器400中,硅背板103包括如图2所示的控制电路阵列以及根据输入信号向子像素供电的必要组件。在具有晶体管和控制电路的层103上,可以存在可选的平坦化层105。通过电触点107连接的单独的第一电极段109在层105(如果存在)上,电触点107延伸通过可选的平坦化层,以在单独的底部电极段109和层103中的控制电路之间进行电接触。在该实施方式中,底部电极段109包括更靠近衬底的反射层109b和更靠近oled层的电极层109a。各个底部电极段109彼此侧向电绝缘。非发光oled层111(诸如电子或空穴注入层或电子或空穴传输层)在分段底部电极段109上。红色oled发光单元113位于oled层111上。层115是第一电荷产生层,其位于红色oled发光单元113和绿色oled发光单元117之间并将红色oled发光单元113和绿色oled发光单元117间隔开。第二电荷产生层119位于绿色光产生单元117上,第二电荷产生层119位于绿色oled光产生单元117和蓝色oled光产生单元121之间

并将绿色oled光产生单元117和蓝色oled光产生单元121间隔开。非发光oled层123(诸如电子或空穴传输层或电子或空穴注入层)和半透明顶部电极(相对电极)125在蓝色oled发光单元121上。这形成了oled微腔130,其从反射表面109b的最上表面延伸到半透明顶部电极125的最下表面,该顶部电极也是半反射电极。封装层127保护oled微腔不受环境影响。在此实施方式中,存在具有滤色器129b、129g和129r的滤色器阵列,其过滤由oled微腔130产生的多模发射,使得b、g和r光根据供应到下方电极段的电力发射。

[0168]

在作为采样和保持型显示器的oled微显示器的控制电路中,解决运动模糊问题是重要的(参见https://www.blurbusters.com/faq/oled-motion-blur/、“why do some oleds have motion blur?”,2018年12月28日、以及https://www.soundandvision.com/content/motion-resolution-issue-oled-tvs,“is motion resolution an issue with oled tvs”,2015年1月15日)。

[0169]

减少由采样和保持引起的运动模糊的唯一方法是缩短显示帧的时间。这可以通过使用额外的刷新(较高的hz)或经由刷新之间的黑色周期(闪烁)来实现。对于oled微显示器,最好的解决方案是“关闭(shutter)”显示图像,可以同时关闭整个有效区域或者可以通过“滚蛋”技术来“关闭”显示图像,在“滚动”技术中仅以顺序方式一次关闭显示图像的一部分。“滚动”技术是优选的。为了避免可感知的闪烁,像素被关闭的时间非常短并且远低于人眼的可检测阈值。这在控制电路中通过包括快门晶体管来实现,当快门晶体管通过选择线被激活时防止电流流过oled并且在期望的时间段使oled像素的发射“关断”。换言之,快门晶体管是开关晶体管,因为它只“导通”或“关断”像素,而不调节电压或电流。然而,这种在显示图像(一般称为帧时段)时段中的部分时间关断像素的解决方案仅增加了oled“导通”时对增加亮度的需求,因为其为由眼睛感知到的帧的平均亮度。用于减小运动模糊的这种关闭可以应用于向oled叠层供电的任何方法,例如,电流控制或pwm。

[0170]

为此,微显示器通常具有串联在电源和发光引擎之间的至少两个晶体管。第一(驱动)晶体管将期望的电力(电压和/或电流)传递到发光引擎,并且由扫描线控制,该扫描线“导通”或“关断”该晶体管。第二(开关)晶体管控制发光引擎“关断”的持续时间以控制运动模糊问题。理想地,两个晶体管都是低电压(5v或更低)晶体管。优选地,两个晶体管都是p沟道晶体管。在电源和发光元件之间的路径中具有两个或更多晶体管的电路有时被称为具有“堆叠”晶体管。

[0171]

用于oled微显示器的合适背板是公知的。参见,例如,ali等人的“recent advances in small molecule oled-on-silicon microdisplays”,proc.of spie vol.7415 74150q-1,2006、ying,w.的“silicon backplane design for oled-on-silicon microdisplay”,mse thesis,nanying technology university,2011、jang等人的j.information display,20(1),1-8(2019)、fujii等人的“4032ppi high-resolution oled microdisplay”,sid 2018digest,p.613、us 2019/0259337、prache,display,22(2),49(2001)以及vogel等人的2018 48

th

,european solid-state device research conference,p.90,2018年9月。

[0172]

用于oled微显示器的一些合适的像素电路设计可以参见zeng等人的“anovel pixel circuit with threshold voltage variation compensation in three-dimensional amoled on silicon microdisplays”,p-27,sid 2019digest,p.1313、us 9,

066,379、kimura等人的“new pixel driving circuit using self-discharging compensation method for high-resolution oled microdisplays on a silicon backplane”,28-3,sid 2017digest,p.399、dawson等人的“the impact of the transient response of organic light emitting diodes on the design of active matrix oled displays”,international electronic devices mtg 1998,875-878、kwak等人的“organic light-emitting diode-on-silicon pixel circuit using the source follower structure with active load for microdisplays”,japanese journal of applied physics,50,03cc05(2011)、vogel等人的sid 2017digest,article 77-1,pp 1125-1128、liu等人,j.cent.south univ.,19,1276-1282(2012)、hong等人的sid 2019digest,article 9-4,105(2019)、以及fan等人的international journal of photoenergy,article id 543273(2011)。总体来说,所有这些参考文献描述了使用串联的驱动晶体管和开关晶体管来向oled的阳极输送电力的像素电路。它们还描述了使用p沟道晶体管、以及在某些情况下使用保护电路来防止过电压。这些参考文献都没有处理串扰问题。

[0173]

图13示出了适用于oled微显示器的像素电路450,其中oled是诸如如图10所示的多模微腔oled。除了包括额外的开关晶体管t6(其源极连接到驱动晶体管t1的漏极且其漏极连接到发光元件2)之外,其类似于图3所示的像素电路150。因此,t1和t6串联在电源1和发光元件2之间。t6的栅极连接到不同于扫描线4的扫描线15。开关晶体管t6/扫描线15的增加提供了使运动模糊最小化的快门功能。因此,由扫描线15控制的开关晶体管t6可以在帧期间关断发光元件2一段时间。

[0174]

图13中所示的实施方式示出了node1的优选位置,该node1位于开关晶体管t6的源极或漏极之一与发光元件2之间。然而,在其它实施方式中,其也可位于t1与t6之间,即,t1的源极或漏极与t6的源极或漏极之间。一些像素电路设计包括串联在电源和发光元件之间的电路的驱动部分中的两个以上的晶体管;在这种情况下,node1的理想位置在串联的最后一个晶体管和发光元件之间。

[0175]

在像素电路450中,理想地,t1和t6都是低电压(标称5v或更低)p沟道晶体管。理想地,t1和t6位于浮置n阱中,其中阱电压受控。例如,us 5764077描述了一种低电压输出缓冲器,其使用用于低电压晶体管的浮置n阱来保护电路免受过电压条件的影响。此外,us 9066379和us 7,768,299描述了浮置n阱的使用。在一些情况下,整个像素电路中的任何晶体管可以位于它们各自独立的n阱中。例如,参见shimazaki等人的“ashared-well dual-supply-voltage 64-bit alu”,ieee j.of solid-state circuits,39(3),494(2004)。

[0176]

理想地,像素电路450还包括附加电路(未示出),以保护驱动晶体管和开关晶体管免受瞬时过高电压损坏。例如,参见kwak等人的us 9,066,379和vogel等人的proc.spie 10335,digital optical technologies,1022502(2017)。这种附加的过压保护方法可以结合到pcc中。

[0177]

众所周知,添加(具有相关栅极线、参考电压和电源电压等的)各种类型的补偿电路以校正像素和像素之间的vth的变化、漏电流、老化效应和导致不均匀的其它问题。这种附加的补偿方法可以结合为pcc的一部分。

[0178]

上述本发明的电路也可以应用于操作负载的任何晶体管控制的设备中,其中,有

必要根据传送到控制晶体管的电力量和/或控制晶体管通过单独的控制线被“导通”还是“关断”来减小传送到负载的电压或电流。

[0179]

尽管串扰对于微显示器可能是尤为受关注的,但是其对于诸如移动电话和电视的较大尺寸的显示设备也可能是一个严重的问题,因为较大尺寸的显示设备也需要高分辨率。上述像素电路适于在任何尺寸的显示设备中减少串扰。

[0180]

有源矩阵显示器可以在整个帧周期内以恒定的亮度驱动(通常称为模拟编程)。像素通常在每单个帧周期中被编程一次,且数据由存储电容器保持恒定直到像素数据被刷新的下一帧周期。在大多数有源矩阵设备中,在帧期间,沿着列的每个像素将接收到数据信号。每行将依次接收扫描信号,该扫描信号允许数据信号传递到沿着该行的每个像素中的像素驱动电路。数据信号可以存储在作为像素电路(参见图1)的一部分的电容器中。该数据信号使沿着所选择的行的像素根据数据信号而完全发射、不完全发射或完全不发射。应注意,沿每列提供给各个像素的数据信号针对于该像素,并且确定该像素的理想亮度,因此,数据信号根据选择哪个行而变化。扫描信号是恒定的,并且对于沿着该行的每个像素是相同的。

[0181]

有源矩阵显示器也可以被数字驱动。该方法涉及通过将单个图像帧划分成多个子帧并将各个子帧的发射周期设置为不同来表示由像素提供的总亮度。在该驱动方法中,扫描信号由扫描线提供,因此,根据扫描信号,沿着每行的像素从数据线接收数据信号。由于在该驱动方法中像素的总发射是根据时间而不是数据信号的电平,因此只需要两个数据信号电平。第一数据信号允许像素完全发光,第二数据信号使像素不发光。

[0182]

应注意,像素电路对于模拟和数字方法可以是相同的,并且基于电流的任何驱动方法、驱动发光元件的任何方法都可以用于驱动图2所示的像素电路以及本文中的其它设备。

[0183]

具有本发明像素电路的显示器可以是全色的、双色的或单色的。

[0184]

本领域技术人员应理解,可以调整信号类型和电平以适合所使用的电路类型。特别地,诸如n沟道晶体管和p沟道晶体管的晶体管在本质上表现不同,并且需要不同的信号来按照预期工作。本说明书中的示例可参考特定晶体管来描述特定信号,但不应将此视为限制。已经根据实现所需益处所需的性能描述了示例,导致相同益处的修改也在本领域技术范围内。

[0185]

在以上说明书中,参考了构成说明书一部分的附图,并且在附图中通过说明的方式示出了可以实践的具体实施方式。详细描述这些实施方式以使得本领域的技术人员能够实施本发明,并且应理解,可以利用其它实施方式,并且在不脱离本发明的范围的情况下可以进行结构、逻辑和电气上的改变。因此,对任何示例性实施方式的描述不应被认为是限制性的。尽管出于说明的目的描述了本发明,但是应理解,这样的细节仅出于说明目的,并且在不脱离本发明的精神和范围的情况下,本领域技术人员可以进行修改。

[0186]

部件列表

[0187]

[0188]

[0189]

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1