显示驱动电路和包括该显示驱动电路的显示装置的制作方法

显示驱动电路和包括该显示驱动电路的显示装置

1.相关申请的交叉引用

2.本技术基于并且要求于2021年5月25日在韩国知识产权局提交的专利申请no.10-2021-0066980的优先权,该申请的公开以引用方式全文并入本文中。

技术领域

3.本发明构思涉及一种显示驱动电路以及包括该显示驱动电路的显示装置,更具体地,涉及一种显示驱动电路以及包括该显示驱动电路的显示装置,当识别源沟道的缺陷时,所述显示驱动电路通过利用另一源沟道和伪沟道将数据电压提供至分别对应于源沟道的数据线。

背景技术:

4.显示装置包括用于显示图像的显示面板和用于驱动显示面板的显示驱动电路。显示驱动电路可以通过从外部接收图像数据并将对应于接收的图像数据的图像信号发送至显示面板的数据线来驱动显示面板。

5.显示驱动电路的源沟道可以通过对应于源沟道的数据线将图像信号输出至显示面板。当一些源沟道有缺陷并且通过利用有缺陷的源沟道驱动显示面板时,异常图像信号可输出至显示面板。在一些示例实施例中,在显示面板中可出现垂直故障线。

技术实现要素:

6.本发明构思提供了一种显示驱动电路以及包括该显示驱动电路的显示装置,当检测到源沟道的缺陷时,该显示驱动电路通过利用伪沟道和伪沟道与有缺陷的源沟道之间的源沟道分别将数据电压提供至对应于源沟道的数据线。

7.根据本发明构思的一方面,提供了一种显示驱动电路,该显示驱动电路包括:多个源沟道,其被配置为将数据电压提供至显示面板的多条数据线;伪沟道,其位于多个源沟道中的至少一个的一侧上;以及控制逻辑,其被配置为控制多个源沟道和伪沟道的操作,其中,当确定多个源沟道中的第一源沟道的故障时,控制逻辑通过利用第一源沟道与伪沟道之间的第二源沟道以及伪沟道分别将数据电压提供至与第一源沟道和第二源沟道对应的数据线。

8.根据本发明构思的另一方面,提供了一种显示驱动电路,该显示驱动电路包括:n个组中的多个源沟道,其将被划分为分别包括n个源沟道的源组;n个组中的多个伪沟道,其将被划分为分别包括n个伪沟道的伪组;开关装置,其分别连接在源组的源沟道和与源组的源沟道对应的邻近组的沟道之间;以及控制逻辑,其被配置为当源沟道中的至少一个有缺陷时,通过分别接通连接至第一源组的源沟道的开关装置,通过经过邻近于第一源组的组中的沟道中的至少一些的输出路径将数据电压提供至与分别包括有缺陷的源沟道的第一源组的源沟道对应的数据线。

9.根据本发明构思的另一方面,提供了一种显示装置,该显示装置包括:显示面板;

以及显示驱动电路,其被配置为驱动显示面板在显示面板上显示图像,其中,显示驱动电路包括:多个源沟道,其被配置为将数据电压提供至显示面板的多条数据线;伪沟道,其在多个源沟道中的至少一个的一侧上;以及控制逻辑,其被配置为控制多个源沟道和伪沟道的操作,并且当确定多个源沟道中的第一源沟道的故障时,控制逻辑通过利用第一源沟道与伪沟道之间的第二源沟道和伪沟道将数据电压分别提供至与第一源沟道以及第二源沟道对应的数据线。

附图说明

10.将从下面结合附图的详细描述中更清楚地理解本发明构思的示例实施例,在附图中:

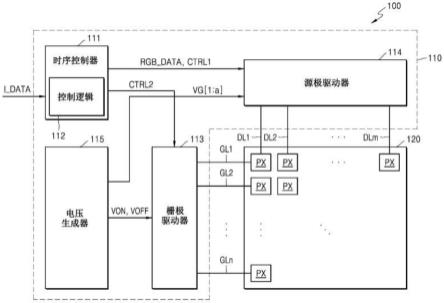

11.图1是示出根据本发明构思的示例实施例的显示装置的框图;

12.图2是示出根据本发明构思的示例实施例的显示驱动电路的配置的示图;

13.图3是用于描述根据示例实施例的源沟道的配置的示图;

14.图4是用于描述根据示例实施例的伪沟道的配置的示图;

15.图5是用于描述根据示例实施例的当源沟道故障出现时提供数据电压的方法的示图;

16.图6是用于描述根据其它示例实施例的当源沟道故障出现时提供数据电压的方法的示图;

17.图7是示出根据示例实施例的源组的示图;

18.图8是示出根据示例实施例的伪组的示图;

19.图9是示出根据示例实施例的包括第一源沟道的第一源组的示图;

20.图10是示出根据示例实施例的源组和伪组的示图;

21.图11是示出根据示例实施例的通过利用伪组提供数据电压的示例的示图;

22.图12是示出根据其它示例实施例的通过利用伪组提供数据电压的示例的示图;

23.图13是示出根据其它示例实施例的通过利用伪组提供数据电压的示例的示图;

24.图14是示出根据本发明构思的示例实施例的显示装置的示例的示图;以及

25.图15是示出根据本发明构思的示例实施例的显示装置的示例的示图。

具体实施方式

26.图1是示出根据本发明构思的示例实施例的显示装置100的框图。

27.参照图1,显示装置100包括显示图像的显示面板120和显示驱动电路110。根据本发明构思的示例实施例的显示装置100可以安装在具有图像显示功能的电子装置上。例如,电子装置可能包括智能手机、平板电脑(pc)、便携式多媒体播放器(pmp)、摄像机、可穿戴装置、电视、数字视频光盘(dvd)播放器、冰箱、空调、空气净化器、机顶盒、机器人、无人机、各种医疗装置、导航装置、全球定位系统(gps)接收器、车辆装置、家具或各种测量装置。

28.显示面板120是在其上实际显示图像的显示单元,并且可以是接收电传输的图像信号并显示二维图像的显示装置中的任何一个,例如,有机发光二极管(oled)显示器、薄膜晶体管液晶显示器(tft-lcd)、场发射显示器、等离子体显示面板(pdp)等。然而,本发明构思不限于此,并且显示面板120可以实现为不同类型的平板显示器或柔性显示面板。

29.显示面板120可包括多条栅极线gl1至gln、在与栅极线gl1至gln交叉的方向上布置的多条数据线dl1至dlm和/或在栅极线gl1至gln与数据线dl1至dlm交叉的区中布置的多个像素px。

30.例如,当显示面板120是tft-lcd时,每个像素px可包括:薄膜晶体管,其栅电极和源电极分别连接至栅极线和数据线;液晶电容器,其连接至薄膜晶体管的漏电极;以及存储电容器。另外,当从栅极线gl1至gln中选择特定栅极线时,连接至选择的栅极线的像素px的薄膜晶体管导通,然后数据电压可通过源极驱动器114分别施加至数据线dl1至dlm。数据电压通过对应的像素px的薄膜晶体管施加至液晶电容器和存储电容器,并且当液晶电容器和存储电容器被驱动时,可显示图像。

31.显示面板120包括多条水平线(或多行),其中一条水平线包括连接至一条栅极线的像素px。例如,连接至第一栅极线gl1的第一行像素px可构成第一水平线,并且连接至第二栅极线gl2的第二行像素px可构成第二水平线。

32.在水平线时间期间,可以驱动一条水平线的像素px,并且在下一水平线时间期间,可以驱动另一条水平线的像素px。例如,在第一水平线时间期间,可以驱动与第一栅极线gl1对应的第一水平线的像素px,然后,在第二水平线时间期间,可以驱动与第二栅极线gl2对应的第二水平线的像素px。就这点而言,在第一水平线时间至第n水平行时间期间,可以驱动显示面板120的像素px。

33.显示驱动电路110可包括时序控制器111、源极驱动器114、栅极驱动器113和/或电压生成器115。显示驱动电路110可以将从外部接收的图像数据i_data转换为用于驱动显示面板120的多个模拟信号(例如,多个数据电压),并且可以将模拟信号供应至显示面板120。

34.源极驱动器114可包括对应于m条数据线dl1至dlm的m个源沟道并且通过m个源沟道输出用于驱动显示面板120的数据电压。数据电压是被提供以驱动显示面板120的一条栅极线的像素px的信号,并且当数据电压分别被输出至m条栅极线gl1至glm时,在显示面板120上实现一帧。源极驱动器114的源沟道可以将从时序控制器111接收的像素数据rgb_data转换为多个图像信号(例如,多个数据电压),并且通过数据线dl1至dlm将数据电压输出至显示面板120。从时序控制器111接收的像素数据rgb_data可包括分别对应于源沟道的像素数据rgb_data。

35.例如,源极驱动器114的源沟道可分别接收对应的像素数据rgb_data。换句话说,源极驱动器114可以以与在显示面板120的一条水平线中包括的多个像素px对应的数据为单位接收像素数据rgb_data。

36.源沟道可基于从电压生成器115接收的多个灰度电压vg[1:a](或者伽马电压)从时序控制器111接收与相应的源沟道对应的像素数据rgb_data,并且将像素数据rgb_data转换为数据电压。

[0037]

源极驱动器114可以通过数据线dl1至dlm以水平线为单位将数据电压输出至显示面板120。例如,源沟道可以输出与在显示面板120的第一水平线中包括的多个像素px对应的多个数据电压,然后输出与在第二水平线中包括的多个像素px对应的多个数据电压。

[0038]

伪沟道(未示出)可以设置在源沟道中的至少一个的一个侧表面上。伪沟道可包括在源极驱动器114中。然而,本发明构思不限于此,并且伪沟道可与源极驱动器114分离地设置在源极驱动器114的一个侧表面上。当源沟道之一有缺陷时,可使用伪沟道替代有缺陷的

源沟道以将数据电压提供至与该源沟道对应的数据线dl1至dlm。与源沟道对应的数据线dl1至dlm可以指连接至该源沟道的数据线。

[0039]

伪沟道可将从时序控制器111接收的像素数据rgb_data转换为图像信号(例如,数据电压),并且经与邻近于该伪沟道的源沟道对应的数据线dl1至dlm将数据电压输出至显示面板120。从时序控制器111接收的像素数据rgb_data可包括对应于伪沟道的伪像素数据。

[0040]

栅极驱动器113连接至显示面板120的多条栅极线gl1至gln,并且可以按次序驱动显示面板120的栅极线gl1至gln。栅极驱动器113可以在时序控制器111的控制下将具有有效电平(例如,逻辑高)的多个栅极导通信号按次序提供至栅极线gl1至gln。因此,可按次序地选择栅极线gl1至gln,并且可通过数据线dl1至dlm将多个数据电压施加至与选择的栅极线对应的水平线的像素px。

[0041]

时序控制器111可以控制显示驱动电路110的整体操作。例如,时序控制器111可以控制显示驱动电路110的组件(例如,源极驱动器114和栅极驱动器113),以在显示面板120上显示从外部接收的图像数据i_data。

[0042]

例如,时序控制器111可以通过将接收的图像数据i_data的格式转换为符合源极驱动器114的接口规范来生成像素数据rgb_data,并且将像素数据rgb_data输出至源极驱动器114。另外,时序控制器111可以生成包括用于控制源极驱动器114和栅极驱动器113的时序的第一控制信号ctrl1和第二控制信号ctrl2的各种控制信号。时序控制器111可以将第一控制信号ctrl1输出至源极驱动器114,并且将第二控制信号ctrl2输出至栅极驱动器113。这里,第一控制信号ctrl1可包括极性控制信号,并且可包括用于控制多个源沟道和多个伪沟道的操作的控制信号。另外,第二控制信号ctrl2可包括栅极时序信号。

[0043]

时序控制器111可包括控制逻辑112。控制逻辑112可以确定源极驱动器114的多个源沟道之一的故障,并且根据确定的结果控制源沟道和多个伪沟道的操作。控制逻辑112可以基于确定的结果生成用于控制源沟道和伪沟道的操作的控制信号,并且将控制信号提供至源极驱动器114作为第一控制信号ctrl1。可基于第一控制信号ctrl1控制源沟道和伪沟道的操作。当伪沟道不包括在源极驱动器114中时,控制逻辑112可以将第一控制信号ctrl1提供至源极驱动器114和伪沟道。

[0044]

当确定源沟道中的第一源沟道的故障时,控制逻辑112可以生成包括用于控制的信号的控制信号,以通过利用第二源沟道和伪沟道将数据电压提供至分别与第一源沟道和第一源沟道与伪沟道之间的第二源沟道对应的数据线。

[0045]

在示例实施例中,当确定第一源沟道的故障时,控制逻辑112可以生成控制信号,以通过经过分别邻近于第一源沟道和第二源沟道的沟道中的至少一些的输出路径将数据电压分别提供至与第一源沟道和第二源沟道对应的数据线。通过经过邻近于第一源沟道的沟道中的至少一些沟道来替代第一源沟道,可将正常数据电压提供至对应于第一源沟道的数据线。

[0046]

虽然图1示出了控制逻辑112设置在时序控制器111内,但是本发明构思不限于此,控制逻辑112可为与时序控制器111分离的电路。这里,控制逻辑112可以将用于控制源极驱动器114的操作的控制信号提供至源极驱动器114,作为与从时序控制器111提供的第一控制信号ctrl1分离的控制信号。根据示例实施例,控制逻辑112可以设置在源极驱动器114

中。

[0047]

电压生成器115可以生成驱动显示装置100所需的各种电压。例如,电压生成器115可从外部接收电源电压。另外,电压生成器115可以生成多个灰度电压vg[1:a]并且将其输出至源极驱动器114。另外,电压生成器115可以生成栅极导通电压von和栅极截止电压voff,并且将其输出至栅极驱动器113。

[0048]

根据本发明构思的显示驱动电路110可包括额外的组件。例如,显示驱动电路110可实施为包括用于逐帧存储接收的图像数据i_data的存储器(未示出)。

[0049]

在本示例实施例中,栅极驱动器113、源极驱动器114和时序控制器111示为彼此不同的功能块。在示例实施例中,例如栅极驱动器113、源极驱动器114和时序控制器111的组件可实施为彼此不同的半导体芯片。在其它示例实施例中,栅极驱动器113、源极驱动器114和时序控制器111中的至少两个可实施为一个半导体芯片。例如,源极驱动器114和时序控制器111可在单个半导体芯片上集成。另外,一些组件可在显示面板120上集成。例如,栅极驱动器113可在显示面板120上集成。

[0050]

图2是示出根据本发明构思的示例实施例的显示驱动电路200的配置的示图。

[0051]

参照图2,显示驱动电路200可包括源极驱动器220和240、伽马沟道230以及/或者伪沟道210和250。图2的显示驱动电路200以及源极驱动器220和240对应于图1的显示驱动电路110和源极驱动器114,并且图2的伪沟道210和250对应于上面参照图1描述的伪沟道。因此,下面将省略与上面给出的那些相同的描述。

[0052]

伪沟道210和250可以布置在源极驱动器220和240的一侧上。伪沟道210和250可以布置在源极驱动器220和240的左侧上、源极驱动器220和240的右侧上、或者源极驱动器220和240的左侧和右侧上。例如,伪沟道210可以设置在源极驱动器220的左侧上,并且伪沟道250可以设置在源极驱动器240的右侧上。在另一示例中,伪沟道210可以设置在源极驱动器220的左侧上,并且伪沟道250可以设置在源极驱动器220的右侧上。

[0053]

伪沟道210和250可以各自包括多个伪沟道。例如,可以在源极驱动器220的左侧上设置五个伪沟道,并且可以在源极驱动器240的右侧上设置其它五个伪沟道。

[0054]

如图2所示,伪沟道210和250可以布置在源极驱动器220和240的一侧上,作为与源极驱动器220和240分离的组件。然而,本发明构思不限于此,并且伪沟道210和250可以布置在源极驱动器220和240中的多个源沟道中的至少一个的一侧上。伪沟道210和250可以布置在多个源沟道的一侧上。源极驱动器220和240可包括多个源沟道,并且可以连续地布置源极驱动器220和240中的每一个中包括的多个源沟道。在示例实施例中,伪沟道210和250可以布置在连续地布置在源极驱动器220和240中的源沟道的一侧上。例如,参照图2,伪沟道250可以设置为邻近于连续地布置的1440个源沟道中的最右侧的源沟道。另外,伪沟道210和250可以布置在源沟道之间。例如,伪沟道250可以设置在源沟道1与源沟道2之间。

[0055]

伽马沟道230可以将由电压生成器生成以驱动源极驱动器的驱动电压发送至源极驱动器220和240。伽马沟道230可以设置在源极驱动器220与源极驱动器240之间。源极驱动器220和源极驱动器240可从伽马沟道230接收相同的驱动电压,并且输出该驱动电压。

[0056]

当多个源沟道中的第一源沟道有缺陷时,可通过利用布置在第一源沟道与伪沟道之间的第二源沟道和伪沟道将数据电压分别提供至与第一源沟道和第二源沟道对应的数据线。例如,参照图2,当从源沟道1至源沟道1440的1440个源沟道在向左的方向上连续地布

置时,伪沟道250设置为邻近于源沟道1,并且源沟道4有缺陷并且对应于第一源沟道,可通过利用伪沟道250、源沟道3、源沟道2和源沟道1将数据电压提供至对应于源沟道1至4的数据线。虽然图2示出了源极驱动器220和240各自包括1440个源沟道,但是源沟道的数量不一定限于此。

[0057]

由于伪沟道210和250布置在多个源沟道的一侧上,并且通过利用第二源沟道以及伪沟道210和250将数据电压提供至数据线,因此连接至与源沟道对应的数据线的输出焊盘的位置可不变。另外,当通过利用第二源沟道和伪沟道将数据电压提供至数据线时,可减小或最小化源沟道与输出焊盘之间的距离的增大。因此,可提供与当多个源沟道中不存在有缺陷的源沟道时提供至数据线的数据电压没有明显不同的数据电压。

[0058]

图3是用于描述根据示例实施例的源沟道的配置的示图。

[0059]

参照图3,显示装置300可包括显示面板310、源极驱动器320和/或时序控制器330。源极驱动器320可包括多个源沟道sc1至scm和移位寄存器。由于图3的源极驱动器320对应于图2的源极驱动器220和240,并且图3的显示装置300、显示面板310和时序控制器330对应于图1的显示装置100、显示面板120和时序控制器111,因此下面将省略与上面给出的那些相同的描述。

[0060]

源极驱动器320可包括移位寄存器。移位寄存器可以将像素数据din1至dinm分别提供至源沟道sc1至scm。移位寄存器可以存储从时序控制器330提供的图像数据data(例如,一条线的像素数据),并且基于垂直同步信号或者基于垂直同步信号生成的时序信号输出一条线的像素数据。移位寄存器可以输出像素数据din1至dinm。移位寄存器可以将与m个源沟道sc1至scm对应的像素数据din1至dinm分别提供至源沟道sc1至scm。例如,移位寄存器可以将与源沟道sc1对应的像素数据din1提供至源沟道sc1。在另一示例中,移位寄存器可以将与源沟道scm对应的像素数据dinm提供至源沟道scm。

[0061]

m个源沟道sc1至scm可以各自包括电平移位器、解码器和/或放大器。例如,源沟道sc1可包括电平移位器ls1、解码器d1和放大器(amp)sa1,并且源沟道sc2可包括电平移位器ls2、解码器d2和放大器sa2。

[0062]

电平移位器可以通过改变像素数据的电压电平提供控制信号。电平移位器可从移位寄存器接收对应于每个源沟道的像素数据,改变接收到的像素数据的电压电平,并且将控制信号提供至每个沟道的解码器。例如,电平移位器ls1可从移位寄存器接收对应于源沟道sc1的像素数据din1,改变像素数据din1的电压电平,并且将控制信号提供至解码器d1。

[0063]

解码器可以基于从电平移位器提供的控制信号选择灰度电压。通过解码器将从电平移位器提供的控制信号转换为灰度电压,因此对应于像素数据的像素信号可提供至放大器。例如,解码器d1可以从多个灰度电压中选择对应于与源沟道sc1对应的像素数据din1的灰度电压,并且输出选择的灰度电压作为像素信号。解码器d1可以将对应于像素数据din1的像素信号提供至放大器sa1。在另一示例中,解码器d2可以从灰度电压中选择对应于与源沟道sc2对应的像素数据din2的灰度电压,并且输出选择的灰度电压作为像素信号。解码器d2可以将对应于像素数据din2的像素信号提供至放大器sa2。

[0064]

放大器可以放大从解码器提供的选择的灰度电压。放大器可以放大从解码器输出的像素信号,并且通过输出焊盘输出数据电压。放大器可被称作沟道放大器或者源极放大器。由于源沟道连接至对应于相应的源沟道的输出焊盘,并且输出焊盘连接至对应于相应

的输出焊盘的数据线,因此放大器可以将数据电压提供至对应于对应的源沟道的数据线。例如,放大器sa1可以放大从解码器d1提供的像素信号,并且通过对应于源沟道sc1的输出焊盘op1输出数据电压,从而将数据电压提供至对应于输出焊盘op1的数据线dl1。

[0065]

在示例实施例中,相应的源沟道sc1至scm的放大器sa1至sam可以将用于确定相应的源沟道sc1至scm是否有缺陷的数据sdata提供至时序控制器330。例如,放大器sa1可以将用于确定源沟道sc1是否有缺陷的数据sdata提供至控制逻辑331。

[0066]

控制逻辑331可以基于放大器的输出确定源沟道sc1至scm中的源沟道sc1是否有缺陷。控制逻辑331可以基于从放大器sa1至sam输出的数据sdata确定相应的源沟道sc1至scm是否有缺陷。用于确定源沟道是否有缺陷的数据sdata可为对应的源沟道的数据电压。

[0067]

控制逻辑331可以通过将数据sdata与预设电压进行比较确定对应于有缺陷的第一源沟道的源沟道。一个源沟道与另一源沟道的预设电压可不同。当从一个源沟道的放大器输出的数据sdata高于预设电压时,控制逻辑331可以确定对应的源沟道有缺陷。例如,当从放大器sa3输出的数据sdata高于预设电压时,控制逻辑331可以将源沟道sc3确定为第一源沟道。然而,本发明构思不限于此。当从一个源沟道的放大器输出的数据sdata低于预设电压时,控制逻辑331也可将对应的源沟道确定为有缺陷。例如,当从放大器sa1输出的数据sdata低于预设电压时,控制逻辑331可以将源沟道sc1确定为第一源沟道。

[0068]

图4是用于描述根据示例实施例的伪沟道的配置的示图。例如,图4是示出其中将伪沟道加至图3的源极驱动器的示例实施例的示图。

[0069]

参照图4,源极驱动器320可包括伪沟道dc1。伪沟道dc1可以设置在源沟道sc1至scm中的至少一个的一侧上。伪沟道dc1可以设置在源沟道sc1至scm的一侧上。例如,伪沟道dc1可以设置为邻近于源沟道sc1。然而,本发明构思不限于此,并且伪沟道dc1可以设置为邻近于源沟道scm。

[0070]

源沟道sc1至scm和伪沟道dc1可以连接至源沟道sc1至scm中的附近源沟道。例如,源沟道sc2可以连接至邻近于源沟道sc2的源沟道sc1和源沟道sc3。在另一示例中,伪沟道dc1可以连接至邻近于伪沟道dc1的源沟道sc1。邻近于源沟道sc1至scm和伪沟道dc1的源沟道可以是从电压生成器接收与源沟道sc1至scm和伪沟道dc1相同的伽马电压的源沟道。邻近于源沟道sc1至scm和伪沟道dc1的源沟道可从电压生成器接收相同的伽马电压。例如,源沟道sc2和邻近于源沟道sc2的源沟道sc3可接收相同的伽马电压。

[0071]

在示例实施例中,源沟道sc1至scm和伪沟道dc1可以分别通过开关装置sw1至swm连接至附近的源沟道。例如,源沟道sc1可以通过开关装置sw2连接至邻近于源沟道sc1的源沟道sc2。在另一示例中,伪沟道dc1可以通过开关装置sw1连接至邻近于伪沟道dc1的源沟道sc1。

[0072]

开关装置sw1至swm的位置可以根据伪沟道dc1的组件而变化。在示例实施例中,当伪沟道dc1包括电平移位器lsd、解码器dd和/或放大器sad时,开关装置sw1至swm可以连接在输出焊盘op1至opm与在邻近于源沟道sc1至scm中的每一个的沟道中包括的放大器sa1至sam和sad的输出端之间。例如,开关装置sw1可以连接在连接至源沟道sc1的输出焊盘op1与在伪沟道dc1中包括的放大器sad的输出端之间。

[0073]

在其它示例实施例中,当伪沟道dc1包括电平移位器lsd和解码器dd作为其组件时,开关装置sw1至swm可以连接在包括在相应的源沟道sc1至scm中的放大器sa1至sam的输

入端与在邻近于相应的源沟道sc1至scm的沟道中包括的解码器d1至dm和dd的输出端之间。

[0074]

另外,开关装置sw1至swm可以根据伪沟道dc1的组件针对源沟道sc1至scm中的每一个布置。在示例实施例中,当伪沟道dc1包括放大器sad作为其组件时,开关装置sw1至swm可包括第一开关装置,其连接在分别连接至源沟道sc1至scm的输出焊盘op1至opm与在邻近于源沟道sc1至scm的沟道中包括的放大器sa1至sam和sad的输出端之间。另外,开关装置sw1至swm可包括第二开关装置,其连接在包括在相应的源沟道sc1至scm中的解码器d1至dm的输出端与在邻近于源沟道sc1至scm的沟道中包括的放大器sa1至sam和sad的输入端之间。

[0075]

移位寄存器可以连接至伪沟道dc1,并且将对应于伪沟道dc1的伪像素数据dind提供至伪沟道dc1。伪像素数据是不会影响数据线dl1至dlm的驱动的任意信号数据。

[0076]

在示例实施例中,伪沟道dc1可包括电平移位器、解码器和/或放大器中的至少一个。例如,伪沟道dc1可包括电平移位器lsd、解码器dd和/或放大器sad。在另一示例中,伪沟道dc1可包括电平移位器lsd和解码器dd。虽然图4仅示出了一个伪沟道dc1,但是可以有多个伪沟道,并且每个伪沟道可包括电平移位器、解码器和放大器中的至少一个。

[0077]

控制逻辑331可以控制源沟道sc1至scm和伪沟道dc1的操作。控制逻辑331可以基于从放大器sa1至sam输出的数据sdata确定源沟道sc1至scm中的第一源沟道的故障,并且基于确定的结果控制源沟道sc1至scm和伪沟道dc1的操作。控制逻辑331可以将包括用于控制源沟道sc1至scm和伪沟道dc1的操作的信号的第一控制信号ctrl1提供至伪沟道dc1和源沟道sc1至scm。

[0078]

当源沟道sc1至scm中不存在有缺陷的第一源沟道时,控制逻辑331可以将数据电压分别提供至与源沟道sc1至scm对应的数据线dl1至dlm,而不使用伪沟道dc1。可通过相应的源沟道sc1至scm的输出路径将像素数据din1至dinm提供至数据线dl1至dlm。换句话说,像素数据din1至dinm可沿着虚线箭头移动。输出路径可以指其中像素数据din1至dinm移动至分别对应于像素数据din1至dinm的输出焊盘op1至opm的路径。可以基于第一控制信号ctrl1控制输出路径。

[0079]

控制逻辑331可以通过利用开关装置sw1至swm控制输出路径。例如,当源沟道sc1至scm中不存在有缺陷的第一源沟道时,控制逻辑331可以控制开关装置sw1至swm保持断开状态,并且控制开关装置swm+1至sw2m保持接通状态。

[0080]

当从源沟道sc1至scm中确定第一源沟道的故障时,可通过利用邻近于第一源沟道的源沟道和伪沟道dc1来替代第一源沟道将数据电压提供至数据线dl1至dlm。将在下面参照图5给出其详细描述。

[0081]

图5是用于描述根据示例实施例的当源沟道故障出现时提供数据电压的方法的示图。

[0082]

图5示出了确定多个源沟道中的第一源沟道的故障的示例实施例。第一源沟道可以指多个源沟道中的有缺陷的源沟道,第二源沟道可以指设置在第一源沟道与伪沟道之间的源沟道。参照图5,控制逻辑331可以基于从放大器sa1至sam输出的数据sdata确定相应的源沟道sc1至scm是否有缺陷。例如,当放大器sa3有缺陷时,控制逻辑331可以基于作为放大器sa3的输出的数据sdata确定源沟道sc3的故障。

[0083]

当通过控制逻辑331确定源沟道sc1至scm中的第一源沟道的故障时,移位寄存器

可以将分别与第一源沟道和第二源沟道对应的像素数据提供至邻近于第一源沟道和第二源沟道的沟道。例如,当控制逻辑331确定源沟道sc3对应于第一源沟道并且有缺陷时,移位寄存器可以将像素数据din3、din2和din1分别提供至在朝着伪沟道dc1的方向上邻近于源沟道sc3、sc2和sc1的沟道。换句话说,移位寄存器可以将像素数据din3提供至源沟道sc2,将像素数据din2提供至源源沟道sc1,并且将像素数据din1提供至伪沟道dc1。

[0084]

当通过控制逻辑331确定源沟道sc1至scm中的第一源沟道的故障时,移位寄存器可以将伪像素数据dind提供至第一源沟道。当伪沟道dc1连接至移位寄存器并且确定第一源沟道的故障时,可以将伪像素数据dind提供至第一源沟道。例如,当控制逻辑331确定源沟道sc3对应于第一源沟道并且有缺陷时,移位寄存器可以将伪像素数据dind提供至源沟道sc3。

[0085]

当确定源沟道sc1至scm中的第一源沟道的故障时,控制逻辑331可以通过利用第二源沟道和伪沟道dc1将数据电压提供至分别与第一源沟道和第一源沟道与伪沟道dc1之间的第二源沟道对应的数据线。当确定源沟道sc3的故障时,控制逻辑331可以通过利用布置在源沟道sc3与伪沟道dc1之间的第二源沟道sc2和sc1以及伪沟道dc1将数据电压提供至分别与作为第一源沟道的源沟道sc3以及第二源沟道sc2和sc1对应的数据线dl3、dl2和dl1。例如,当确定作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以通过利用作为第二源沟道的源沟道sc2将从移位寄存器提供的像素数据din3提供至对应于源沟道sc3的数据线dl3作为数据电压。当确定作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以通过利用作为第二源沟道的源沟道sc1将从移位寄存器提供的像素数据din2提供至对应于源沟道sc2的数据线dl2,作为数据电压。另外,当确定作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以通过利用伪沟道dc1将从移位寄存器提供的像素数据din1提供至对应于作为第二源沟道的源沟道sc1的数据线dl1,作为数据电压。

[0086]

当确定第一源沟道的故障时,控制逻辑331可以通过经过邻近于第一源沟道和第二源沟道的沟道中的至少一些的输出路径将数据电压提供至分别对应于第一源沟道和第二源沟道的数据线。控制逻辑331可以通过利用分别邻近于第一源沟道和第二源沟道的所有或一些沟道提供数据电压。

[0087]

在示例实施例中,当确定多个源沟道中的第一源沟道的故障时,控制逻辑331可以通过利用第二源沟道和伪沟道的电平移位器、解码器和放大器中的至少一个将数据电压提供至分别对应于第一源沟道和第二源沟道的数据线。例如,当确定作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以通过利用作为第二源沟道的源沟道sc2的电平移位器ls2、解码器d2和放大器sa2来生成数据电压,并且通过连接至开关装置sw3的输出焊盘op3输出数据电压,从而将数据电压提供至数据线dl3。控制逻辑331可以通过利用作为第二源沟道的源沟道sc1的电平移位器ls1、解码器d1和放大器sa1来生成数据电压,并且通过连接至开关装置sw2的输出焊盘op2输出数据电压,从而将数据电压提供至数据线dl2。控制逻辑331可以通过利用伪沟道dc1的电平移位器lsd、解码器dd和放大器sad来生成数据电压,并且通过连接至开关装置sw1的输出焊盘op1输出数据电压,从而将数据电压提供至数据线dl1。

[0088]

电平移位器lsd可从移位寄存器接收像素数据din1,转变像素数据din1的电压电平,并且将控制信号提供至解码器dd。解码器dd可以从多个灰度电压中选择对应于像素数

据din1的灰度电压,并且输出选择的灰度电压作为像素信号。放大器sad可以通过放大从解码器dd提供的像素信号生成数据电压,通过连接至开关装置sw1的输出焊盘op1输出数据电压,并且将数据电压提供至数据线dl1。然而,本发明构思不一定限于此,并且控制逻辑331可以使用第二源沟道和伪沟道的电平移位器和解码器,或者可以仅使用其放大器。稍后将参照图6给出其详细描述。

[0089]

当确定第一源沟道的故障时,控制逻辑331可以通过利用开关装置sw1至swm控制输出路径。例如,当确定源沟道sc1至scm中的作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以将开关装置sw1至sw3切换至接通状态,将开关装置swm+1至swm+3切换至断开状态,将开关装置sw4至swm保持在断开状态,并且将开关装置swm+4至sw2m保持在接通状态,从而控制输出路径。

[0090]

图6是用于描述根据其它示例实施例的当源沟道故障出现时提供数据电压的方法的示图。

[0091]

图6示出了提供了与图5的伪沟道dc1不同的组件的示例实施例。参照图6,伪沟道dc1可包括解码器dd和电平移位器lsd。源沟道sc1至scm和伪沟道dc1可以连接至源沟道sc1至scm中的附近的源沟道。

[0092]

源沟道sc1至scm和伪沟道dc1可以通过开关装置sw1至swm连接至附近的源沟道。当伪沟道dc1包括电平移位器lsd和解码器dd作为其组件时,开关装置sw1至swm可以连接在包括在相应的源沟道sc1至scm中的放大器sa1至sam的输入端与在邻近于相应的源沟道sc1至scm的沟道中包括的解码器d1至dm和dd的输出端之间。例如,开关装置sw1可以连接在包括在源沟道sc1中的放大器sa1的输入端与在邻近于源沟道sc1的伪沟道dc1中包括的解码器dd的输出端之间。

[0093]

控制逻辑331可以基于从放大器sa1至sam输出的数据sdata确定相应的源沟道sc1至scm是否有缺陷。例如,当解码器d3有缺陷时,控制逻辑331可以基于作为放大器sa3的输出的数据sdata确定源沟道sc3的故障。

[0094]

当确定多个源沟道中的第一源沟道的故障时,控制逻辑331可以通过利用第二源沟道和伪沟道的电平移位器和解码器中的至少一个将数据电压提供至分别对应于第一源沟道和第二源沟道的数据线。例如,当确定作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以通过利用作为第二源沟道的源沟道sc2的电平移位器ls2和解码器d2生成对应于像素数据din3的像素信号,通过开关装置sw3将生成的像素信号提供至放大器sa3,通过利用作为第二源沟道的源沟道sc1的电平移位器ls1和解码器d1生成对应于像素数据din2的像素信号,通过开关装置sw2将生成的像素信号提供至放大器sa2,通过利用伪沟道dc1的电平移位器lsd和解码器dd生成对应于像素数据din1的像素信号,并且通过开关装置sw1将生成的像素信号提供至放大器sa1。放大器sa1可以通过放大从解码器dd提供的像素信号通过输出焊盘op1输出数据电压,并且将数据电压提供至数据线dl1。

[0095]

当确定第一源沟道的故障时,控制逻辑331可以通过利用开关装置sw1至swm控制输出路径。例如,当确定源沟道sc1至scm中的作为第一源沟道的源沟道sc3的故障时,控制逻辑331可以控制开关装置sw1至sw3和开关装置swm+4至sw2m处于接通状态,并且控制开关装置swm+1至swm+3和开关装置sw4至swm处于断开状态,从而控制输出路径。

[0096]

图7是示出根据示例实施例的源组的示图。

[0097]

参照图7,源极驱动器720可包括多个源组sg1至sg8。虽然图7示出了八个源组sg1至sg8,但是源组的数量可大于或小于八个。由于显示装置700、显示面板710和/或源极驱动器720与上面描述的那些相同,因此下面将省略与上面给出的相同的描述。

[0098]

多个源沟道可被分组成各自包括n(n是正数)个源沟道的源组sg1至sg8。换句话说,一个源组可包括n个源沟道。

[0099]

移位寄存器可以分别将像素数据组ding1至ding8提供至源组sg1至sg8。一个像素数据组可包括与在对应于像素数据组的源组中包括的n个沟道对应的像素数据。例如,移位寄存器可以将像素数据组ding1提供至源组sg1,并且将与源组sg1的n个沟道对应的像素数据分别提供至源组sg1的n个沟道。

[0100]

源组sg1至sg8可以将分别对应于源组sg1至sg8的像素数据组ding1至ding8转换为数据电压,通过分别对应于源组sg1至sg8的输出焊盘组opg1至opg8输出数据电压,并且将数据电压提供至分别对应于输出焊盘组opg1至opg8的数据线组dlg1至dlg8。一个输出焊盘组可包括分别与对应的源组的n个沟道对应的输出焊盘,并且一个数据线组可包括分别与对应的源组的n个沟道对应的数据线。

[0101]

图8是示出根据示例实施例的伪组的示图。例如,图8示出了将伪组加至图7的示例实施例。

[0102]

参照图8,源极驱动器720可包括伪组dg。伪组dg可包括n个伪沟道。伪组dg可以设置在源组sg1至sg8中的至少一个的一侧上。例如,伪组dg可以设置为邻近于源组sg1。然而,本发明构思不一定限于此。伪组dg可以设置为邻近于源组sg8。伪组dg可以设置在源组sg3与源组sg4之间。可替换地,可以有多个伪组dg,并且伪组dg可以布置为邻近于源组sg1和源组sg8。

[0103]

在示例实施例中,源组sg1至sg8和伪组dg可以各自包括四个沟道,并且可包括红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道中的至少一个。例如,源组sg1至sg8和伪组dg可以各自包括红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道。然而,本发明构思不限于以上陈述的类型的沟道。

[0104]

源组sg1至sg8的n个源沟道和伪组dg的伪沟道可以连接至分别邻近于源组sg1至sg8和伪组dg的组中的n个源沟道。例如,源组sg1的n个源沟道可以分别连接至邻近于源组sg1的源组sg2的n个源沟道。在另一示例中,伪组dg的n个伪沟道可以分别连接至邻近于伪组dg的源组sg1的n个源沟道。源组sg1至sg8的n个源沟道和伪组dg的伪沟道可以连接至接收与源组sg1至sg8的n个源沟道和伪组dg的伪沟道相同的伽马电压的邻近于源组sg1至sg8和伪组dg的组中的n个源沟道。例如,源组sg1的源沟道1可以连接至源组sg2的源沟道5,其中源沟道1和源沟道5可接收相同的伽马电压。可以基于一组伽马电压确定在伪组中包括的伪沟道的数量。例如,伪组可包括分别接收四个伽马电压的四个伪沟道。

[0105]

在每个源组和伪组中包括的n个沟道可以彼此对应。例如,在伪组dg中包括的红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道可以分别对应于源组sg1的红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道,并且源组sg1的红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道可以分别对应于源组sg2的红色沟道、蓝色沟道、第一绿色沟道和第二绿色沟道。

[0106]

在示例实施例中,源组sg1至sg8和伪组dg可以通过开关装置组swg1至swg9连接至

邻近的源组。一个开关装置组可包括用于将在源组sg1至sg8中的每一个和伪组dg中包括的n个沟道分别连接至邻近的源组的n个沟道的n个开关装置。例如,在源组sg2中包括的源沟道可以通过开关装置组swg3的n个开关装置连接至与其邻近的源组sg3的源沟道。在另一示例中,在伪组dg中包括的伪沟道可以分别通过开关装置组swg1的n个开关装置连接至与其邻近的源组sg1的源沟道。

[0107]

移位寄存器可以连接至伪组dg,并且可以将对应于伪组dg的伪像素数据组dingd提供至伪组dg。伪像素数据组dingd可包括与包括在对应于伪像素数据组dingd的伪组dg中的n个沟道对应的伪像素数据。例如,移位寄存器可以将对应于伪组dg的n个伪沟道的伪像素数据分别提供至伪组dg的n个伪沟道。

[0108]

控制逻辑(例如,图4的控制逻辑331)可以控制源组sg1至sg8和伪组dg的操作。控制逻辑可以基于从在源组sg1至sg8中包括的源沟道的放大器输出的数据sdata确定源沟道sc1至scm中的第一源沟道的故障,并且基于确定的结果控制源组sg1至sg8和伪组dg的操作。控制逻辑可以将用于控制源组sg1至sg8和伪组dg的操作的信号提供至源组sg1至sg8和伪组dg,作为第一控制信号ctrl1。

[0109]

当在源组sg1至sg8中包括的多个源沟道中不存在有缺陷的第一源沟道时,控制逻辑可以将数据电压提供至分别对应于源组sg1至sg8的数据线组dlg1至dlg8,而不使用伪组dg。

[0110]

控制逻辑可以通过使用开关装置组swg1至swg9控制输出路径。例如,当多个源沟道中不存在有缺陷的第一源沟道时,控制逻辑可以控制在开关装置组swg1至swg9中包括的开关装置保持断开状态并且控制在开关装置组swg10至swg17中包括的开关装置保持接通状态,从而控制输出路径。

[0111]

图9是示出根据示例实施例的包括第一源沟道的第一源组的示图。图9示出了确定在源组sg1至sg8中的第一源组中包括的第一源沟道的故障的示例实施例。

[0112]

参照图9,控制逻辑(例如,图5的控制逻辑331)可以基于从在源组sg1至sg8的源沟道中包括的放大器输出的数据sdata确定每个源沟道是否有缺陷,并且确定第一源组。第一源组可以指包括第一源沟道的源组。例如,当源组sg4包括第一源沟道时,源组sg4可为第一源组。

[0113]

当通过控制逻辑确定多个源沟道中的第一源沟道的故障时,移位寄存器可以将分别与第一源组和布置在第一源组与伪组dg之间的第二源组对应的像素数据组提供至邻近于第一源组和第二源组的组。例如,当通过控制逻辑确定在源组sg4中包括的第一源沟道的故障时,移位寄存器可以将像素数据组ding4、ding3、ding2和ding1分别提供至在朝着伪组dg的方向上邻近于源组sg4、sg3、sg2和sg1的组。换句话说,移位寄存器可以将像素数据组ding4提供至源组sg3,将像素数据组ding3提供至源组sg2,将像素数据组ding2提供至源组sg1,并且将像素数据组ding1提供至伪组dg。

[0114]

当通过控制逻辑确定第一源沟道的故障时,移位寄存器可以将伪像素数据组dingd提供至第一源组。当伪组dg连接至移位寄存器并且确定第一源沟道的故障时,可将伪像素数据组dingd提供至第一源组。例如,移位寄存器可以将伪像素数据组dingd提供至作为第一源组的源组sg4。

[0115]

当确定在源组sg1至sg8中的第一源组中包括的第一源沟道的故障时,控制逻辑可

以通过利用第二源组和伪组将数据电压提供至分别对应于第一源组和第二源组的源沟道的数据线。例如,当确定在作为第一源组的源组sg4中包括的第一源沟道的故障时,控制逻辑可以通过利用源组sg3、sg2和sg1以及伪组dg将数据电压提供至分别对应于源组sg4和作为第二源组的源组sg3、sg2和sg1的源沟道的数据线。

[0116]

当确定第一源沟道的故障时,控制逻辑可以通过经过邻近于第一源组和第二源组的组中的沟道的至少一部分的输出路径将数据电压提供至分别与第一源沟道和第二源组的源沟道对应的数据线。控制逻辑可以通过经过与源组sg4的源沟道分别对应的作为第二源组的源组sg3中包括的沟道的输出路径将数据电压提供至分别与作为第一源组的源组sg4的源沟道对应的数据线。

[0117]

当确定第一源沟道的故障时,控制逻辑331可以通过利用开关装置组swg1至swg9控制输出路径。例如,当确定在作为第一源组的源组sg4中包括的第一源沟道的故障时,控制逻辑可以控制在开关装置组swg1至swg4和开关装置组swg14至swg17中包括的开关装置处于接通状态,并且控制在开关装置组swg10至swg13和开关装置组swg5至swg9中包括的开关装置处于断开状态,从而控制输出路径。

[0118]

图10是示出根据示例实施例的源组和伪组的示图。

[0119]

参照图10,伪组1020可包括多个伪沟道dc1至dc4,第二源组1030可包括多个源沟道sc2877至sc2880,第一源组1040可包括多个源沟道sc2873至sc2876。虽然图10示出了伪组1020、第二源组1030和第一源组1040各自包括四个沟道,但是在每个组中包括的沟道的数量不受限制。

[0120]

伪组1020可以设置在第二源组1030的一侧上。第一源组1040和第二源组1030中的每一个的四个源沟道和伪组1020的四个伪沟道可以各自连接至邻近于第一源组1040、第二源组1030和伪组1020的组中的每一个的四个源沟道。例如,第二源组1030的源沟道sc2877至sc2880可以分别连接至邻近于第二源组1030的第一源组1040的源沟道sc2873至sc2876。源沟道sc2873可以连接至源沟道sc2877,源沟道sc2874可以连接至源沟道sc2878,源沟道sc2875可以连接至源沟道sc2879,并且源沟道sc2876可以连接至源沟道sc2880。在另一示例中,伪组1020的伪沟道dc1至dc4可以分别连接至第二源组1030的源沟道sc2877至sc2880。伪沟道dc1可以连接至源沟道sc2877,伪沟道dc2可以连接至源沟道sc2878,伪沟道dc3可以连接至源沟道sc2879,并且伪沟道dc4可以连接至源沟道sc2880。

[0121]

在示例实施例中,在第一源组1040、第二源组1030和伪组1020中的每一个中包括的沟道可以分别通过开关装置连接至邻近的源组的源沟道。例如,在伪组1020中包括的伪沟道dc1至dc4可以分别通过开关装置sw4、sw3、sw2和sw1连接至第二源组1030的源沟道sc2877至sc2880。四个开关装置sw4、sw3、sw2和sw1可构成开关装置组。

[0122]

在示例实施例中,多个源沟道sc2873至sc2880和伪沟道dc1至dc4可以各自包括电平移位器、解码器和放大器中的至少一个。伪沟道dc1至dc4可以各自包括相同的组件。例如,伪沟道dc1至dc4可以各自包括放大器和解码器。

[0123]

控制逻辑(例如,图5的控制逻辑331)可以基于从在多个源组的源沟道中包括的放大器输出的数据sdata确定多个源沟道之一是否有缺陷。例如,控制逻辑可以确定源沟道sc2873的故障。

[0124]

当通过控制逻辑确定作为第一源沟道的源沟道sc2873的故障时,移位寄存器可以

将分别与第一源组1040和设置在第一源组1040与伪组1020之间的第二源组1030对应的像素数据组提供至邻近于第一源组1040和第二源组1030的组。移位寄存器可以将分别与第一源组1040的源沟道sc2873至sc2876对应的像素数据din2873至din2876在朝着伪组1020的方向上提供至第二源组1030的源沟道sc2877至sc2880。例如,当确定作为第一源沟道的源沟道sc2873的故障时,移位寄存器可以将对应于源沟道sc2873的像素数据din2873提供至源沟道sc2877,将对应于源沟道sc2874的像素数据din2874提供至源沟道sc2878,将对应于源沟道sc2875的像素数据din2875提供至源沟道sc2879,并且将对应于源沟道sc2876的像素数据din2876提供至源沟道sc2880。

[0125]

另外,移位寄存器可以将分别与第二源组1030的源沟道sc2877至sc2880对应的像素数据din2877至din2880在朝着伪组1020的方向上提供至伪组1020的伪沟道dc1至dc4。

[0126]

当伪组1020连接至移位寄存器并且确定第一源沟道的故障时,可以将伪像素数据组提供至第一源组1040。移位寄存器可以将分别对应于伪沟道dc1至dc4的伪像素数据dind1至dind4分别提供至第一源组1040的源沟道sc2873至sc2876。例如,当确定第一源沟道的故障时,移位寄存器可以将对应于伪沟道dc1的伪像素数据din1提供至源沟道sc2873,将对应于伪沟道dc2的伪像素数据din2提供至源沟道sc2874,将对应于伪沟道dc3的伪像素数据din3提供至源沟道sc2875,并且将对应于伪沟道dc4的伪像素数据din4提供至源沟道sc2876。

[0127]

即使当只有第一源组1040的源沟道sc2873有缺陷时,在第一源组1040中包括的所有源沟道sc2873至sc2876也可使用在第二源组1030中包括的源沟道sc2877至sc2880,并且在第二源组1030中包括的所有源沟道sc2877至sc2880也可使用在伪组1020中包括的伪沟道dc1至dc4,以提供与分别对应于第一源组1040和第二源组1030的源沟道的数据线dl2873至dl2880对应的数据电压。

[0128]

控制逻辑可以通过经过邻近于第一源组1040的第二源组1030的源沟道sc2877至sc2880的输出路径将对应于源沟道sc2873至sc2876的像素数据din2873至din2876作为数据电压提供至对应于源沟道sc2873至sc2876的数据线dl2873至dl2876。控制逻辑可以通过经过邻近于第二源组1030的伪组1020的伪沟道dc1至dc4的输出路径将对应于源沟道sc2877至sc2880的像素数据din2877至din2880作为数据电压提供至对应于源沟道sc2877至sc2880的数据线dl2877至dl2880。

[0129]

当确定在第一源组1040中包括的源沟道sc2873的故障时,控制逻辑可以控制开关装置sw1至sw8处于接通状态并且控制开关装置sw9至sw16处于断开状态,从而控制输出路径。

[0130]

图11是示出根据示例实施例的通过利用伪组提供数据电压的示例的示图。

[0131]

参照图11,伪组dg可包括放大器组sagd、解码器组dgd和电平移位器组lsgd,并且源组sg1至sg8可以各自包括放大器组sag1至sag8、解码器组dg1至dg8和电平移位器组lsg1至lsg8。放大器组、解码器组和电平移位器组可以指在包括在源组中的多个源沟道和包括在伪组中的多个伪沟道中包括的多个放大器、多个解码器和多个电平移位器的组。在伪组dg中包括的多个伪沟道和在源组sg1至sg8中的每一个中包括的多个源沟道可以各自包括电平移位器、解码器和放大器,其中在每个沟道中包括的解码器、电平移位器和放大器彼此连接。

[0132]

开关装置组swg1至swg9的位置可根据在伪组dg中包括的伪沟道的组件改变。在示例实施例中,当在伪组dg中包括的伪沟道中的每一个包括电平移位器、解码器和放大器作为其组件时,在开关装置组swg1至swg8中的每一个中包括的开关装置可以连接在分别连接至源组的源沟道的输出焊盘与在邻近于该源组的组的沟道中包括的放大器的输出端之间,所述沟道分别对应于该源组的源沟道。例如,在开关装置组swg2中包括的开关装置可以连接在分别连接至源组sg2的源沟道的输出焊盘和与在源组sg2中包括的源沟道分别对应的源组sg1的沟道中包括的放大器的输出端之间,并且源组sg1可以连接至源组sg2。

[0133]

当源组sg4是第一源组时,控制逻辑可以控制在开关装置组swg1至swg4和开关装置组swg14至swg17中包括的开关装置接通,并且控制在开关装置组swg5至swg9和开关装置组swg10至swg13中包括的开关装置断开。

[0134]

当源组sg4是第一源组时,控制逻辑可以通过经过对应于像素数据的沟道的电平移位器组lsg3的沟道的电平移位器、对应于像素数据的沟道的解码器组dg3的解码器和对应于像素数据的沟道的放大器组sag3的放大器的输出路径,通过发送对应于源组sg4的像素数据组ding4的像素数据,将数据电压提供至输出焊盘组opg4的输出焊盘。控制逻辑可以通过经过源组sg2的源沟道的输出路径将对应于源组sg3的像素数据组ding3的像素数据提供至输出焊盘组opg3的输出焊盘作为数据电压,通过经过源组sg1的源沟道的输出路径将对应于源组sg2的像素数据组ding2的像素数据提供至输出焊盘组opg2的输出焊盘作为数据电压,并且通过经过伪组dg的伪沟道的输出路径将对应于源组sg1的像素数据组ding1的像素数据提供至输出焊盘组opg1的输出焊盘作为数据电压。

[0135]

图12是示出根据其它示例实施例的通过利用伪组提供数据电压的示例的示图。

[0136]

参照图12,伪组dg可包括解码器组dgd和电平移位器组lsgd。在伪组dg中包括的多个伪沟道可以各自包括电平移位器和解码器,其中伪沟道的解码器和电平移位器彼此连接。

[0137]

开关装置组swg1至swg9的位置可以根据在伪组dg中包括的伪沟道的组件改变。在示例实施例中,当在伪组dg中包括的伪沟道中的每一个包括电平移位器和解码器作为其组件时,在开关装置组swg18至swg26中的每一个中包括的开关装置可以连接在包括在源组的源沟道中的放大器的输入端与包括在邻近于该源组的组中的沟道中的解码器的输出端之间,所述沟道分别对应于该源组的源沟道。例如,在开关装置组swg18中包括的开关装置可以连接在源组sg1的源沟道中包括的放大器的输入端和与源组sg1的源沟道分别对应的伪组dg的沟道中包括的解码器的输出端之间,并且源组sg1可以连接至伪组dg。

[0138]

当源组sg4是第一源组时,控制逻辑可以控制在开关装置组swg18至swg21和开关装置组swg31至swg34中包括的开关装置接通,并且控制在开关装置组swg22至swg26和开关装置组swg27至swg30中包括的开关装置断开。

[0139]

当源组sg4是第一源组时,控制逻辑可以通过经过源组sg3的源沟道的解码器和电平移位器的输出路径将对应于源组sg4的像素数据组ding4的像素数据提供至输出焊盘组opg4的输出焊盘作为数据电压,并且通过经过源组sg2的源沟道的解码器和电平移位器的输出路径将对应于源组sg3的像素数据组ding3的像素数据提供至输出焊盘组opg3的输出焊盘作为数据电压。另外,控制逻辑可以通过经过源组sg1的源沟道的解码器和电平移位器的输出路径将对应于源组sg2的像素数据组ding2的像素数据提供至输出焊盘组opg2的输

出焊盘作为数据电压,并且通过经过伪组dg的沟道的解码器和电平移位器的输出路径将对应于源组sg1的像素数据组ding1的像素数据提供至输出焊盘组opg1的输出焊盘作为数据电压。

[0140]

图13是示出根据其它示例实施例的通过利用伪组提供数据电压的示例的示图。

[0141]

参照图13,伪组dg可包括放大器组sagd。在伪组dg中包括的多个伪沟道可包括放大器。

[0142]

开关装置组swg1至swg9和swg35至swg42的位置可根据在伪组dg中包括的伪沟道的组件而改变。在示例实施例中,当在伪组dg中包括的伪沟道中的每一个包括放大器作为其组件时,在开关装置组swg1至swg9和swg35至swg42中的每一个中包括的开关装置可包括第一开关装置,其连接在分别连接至源组的源沟道的输出焊盘与在邻近于该源组的组中的沟道中包括的放大器的输出端之间,所述沟道分别对应于该源组的源沟道。第一开关装置可以分别包括在开关装置组swg1至swg9中。另外,在开关装置组swg1至swg9和swg35至swg42中包括的开关装置可包括第二开关装置,其连接在分别在源组的源沟道中包括的解码器的输出端与邻近于该源组的组中的沟道中的放大器的输入端之间,所述沟道分别对应于该源组的源沟道。第二开关装置可分别包括在开关装置组swg35至swg42中。

[0143]

例如,在开关装置组swg35中包括的第二开关装置可以连接在在源组sg1的源沟道中包括的解码器的输出端和与源组sg1的源沟道分别对应的伪组dg的沟道中包括的放大器的输入端之间。在开关装置组swg1中包括的第一开关装置可以连接在连接至源组sg1的源沟道的输出焊盘和与源组sg1的源沟道分别对应的伪组dg的沟道中包括的放大器的输出端之间。

[0144]

当源组sg4是第一源组时,控制逻辑可以控制在开关装置组swg1至swg4、开关装置组swg14至swg17、开关装置组swg35至swg38和开关装置组swg47至swg50中包括的开关装置接通,并且控制在开关装置组swg5至swg9、开关装置组swg10至swg13、开关装置组swg39至swg42和开关装置组swg43至swg46中包括的开关装置断开。

[0145]

当源组sg4是第一源组时,控制逻辑可以通过经过分别对应于解码器的源组sg3的源沟道的放大器的输出路径将分别从解码器组dg4的解码器输出的灰度电压分别提供至输出焊盘组opg4的输出焊盘作为数据电压。控制逻辑可以通过经过分别对应于解码器的源组sg2的源沟道的放大器的输出路径将分别从解码器组dg3的解码器输出的灰度电压分别提供至输出焊盘组opg3的输出焊盘作为数据电压。另外,控制逻辑可以通过经过分别对应于解码器的源组sg1的源沟道的放大器的输出路径将分别从解码器组dg2的解码器输出的灰度电压分别提供至输出焊盘组opg2的输出焊盘作为数据电压,并且可以通过经过分别对应于解码器的伪组dg的伪沟道的放大器的输出路径将分别从解码器组dg1的解码器输出的灰度电压分别提供至输出焊盘组opg1的输出焊盘作为数据电压。

[0146]

图14是示出根据本发明构思的示例实施例的显示装置的示例的示图。图14的显示装置1400是包括具有中等尺寸或大尺寸显示面板1420的显示装置,并且可应用于例如电视或监视器。

[0147]

参照图14,显示装置1400可包括源极驱动器1411、时序控制器(tcon)1412、栅极驱动器1413和/或显示面板1420。

[0148]

时序控制器1412可包括一个或多个ic或者模块。时序控制器1412可通过一组接口

与多个源极驱动器ic sdic和多个栅极驱动器ic gdic通信。

[0149]

时序控制器1412可以生成用于控制源极驱动器ic sdic和栅极驱动器ic gdic的驱动时序的控制信号,并且将控制信号提供至源极驱动器ic sdic和栅极驱动器ic gdic。

[0150]

源极驱动器1411可包括源极驱动器ic sdic,并且源极驱动器ic sdic可以安装在像磁带载体封装件(tcp)、膜上芯片(cof)和柔性印刷电路(fpc)一样的电路膜上,并且可以通过利用胶带自动粘合(tab)技术附着于显示面板1420,或者可以通过使用玻璃上芯片(cog)技术附着于显示面板1420的非显示区上。

[0151]

栅极驱动器1413可以包括栅极驱动器ic gdic,并且栅极驱动器ic gdic可以安装在电路膜上,并且可以通过使用tab技术附着于显示面板1420,或者可以通过使用cog技术附着于显示面板1420的非显示区上。可替换地,可以通过使用面板内栅极驱动器(gip)技术直接在显示面板1420的下衬底上形成栅极驱动器1413。栅极驱动器1413形成在显示面板1420的其中形成有像素的像素阵列之外的非显示区中,并且可以通过与像素相同的tft工艺形成。

[0152]

如上参照图1至图14描述的,当基于第一控制信号ctrl1确定第一源信道的故障时,源极驱动器1411可以通过利用第二源沟道和伪沟道将数据电压提供至分别对应于第一源沟道和布置在第一源沟道与伪沟道之间的第二源沟道的数据线。因此,即使当多个源沟道中的一个有缺陷时,也可以通过使用邻近于有缺陷的源沟道的沟道来驱动对应于源沟道的数据线,并且因此可以减少或防止显示面板1420中发生的垂直线故障。

[0153]

图15是示出根据本发明构思的示例实施例的显示装置的示例的示图。图15的显示装置1500是包括小尺寸的显示面板1520的显示装置,并且可应用于像智能手机和平板pc一样的移动装置。

[0154]

参照图15,显示装置1500可包括显示驱动电路1510和/或显示面板1520。显示驱动电路1510可包括一个或多个ic,并且可以安装在像tcp、cof和fpc一样的电路膜上,并且可以通过利用tab技术附着于显示面板1520或者可以通过利用cog技术附着于显示面板1520的非显示区(例如,不显示图像的区)上。

[0155]

显示驱动电路1510可包括源极驱动器1511和/或时序控制器1512,并且还可以包括栅极驱动器。在示例实施例中,栅极驱动器可以安装在显示面板1520上。

[0156]

如上参照图1至图15描述的,当基于第一控制信号ctrl1确定第一源沟道的故障时,源极驱动器1511可以通过利用第二源沟道和伪沟道将数据电压提供至分别对应于第一源沟道和布置在第一源沟道与伪沟道之间的第二源沟道的数据线。因此,即使当多个源沟道之一有缺陷时,可通过利用邻近于有缺陷的源沟道的沟道驱动对应于源沟道的数据线,因此可减少或防止显示面板1520中出现的垂直线故障。

[0157]

上面公开的一个或多个元件可以包括或者实现为:控制逻辑,诸如包括逻辑电路的硬件;硬件/软件组合,诸如执行软件的处理器;或者它们的组合。例如,更具体地说,控制逻辑可以包括(但不限于)中央处理单元(cpu)、算术逻辑单元(alu)、数字信号处理器、微计算机、现场可编程门阵列(fpga)、片上系统(soc)、可编程逻辑单元、微处理器、专用集成电路(asic)等。

[0158]

虽然已经参考本发明构思的示例实施例具体地示出和描述了本发明构思,但是应当理解,在不脱离所附权利要求的精神和范围的情况下,可以对其进行形式和细节上的各

种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1