显示驱动芯片的双内存功能切换电路及控制方法与流程

1.本发明涉及电子电路领域,具体而言,涉及一种显示驱动芯片的双内存功能切换电路及控制方法。

背景技术:

2.当前中小型amoled显示屏(主要为手机和平板)在品牌端及高端返修领域,因demura(屏幕缺陷补偿)与cmd mode(指令模式)显示需求,需要两块ram(内存)分别存放demura数据和显示数据,ddic(显示驱动芯片)需要按照dual ram的规格进行设计。但随着amoled panel(有源矩阵有机发光半导体的平板)制程能力的提升及应用范围的拓宽,已越来越多地出现不需要demura或只需要video mode(视频模式)的应用场景。在上述场景下,若ddic重新研发single ram设计,将严重拖累显示模组乃至整机的整体项目进度,若ddic沿用现有dual ram设计则会大幅提升成本压力。

技术实现要素:

3.鉴于上述问题,本发明提供了一种显示驱动芯片的双内存功能切换电路及控制方法,能够有效解决现有dual ram设计成本高的问题。

4.为了实现上述目的,本发明采用如下的技术方案:

5.第一方面,本发明提供了一种显示驱动芯片的双内存功能切换电路,所述双内存功能切换电路包括:

6.显示内存,接收包括显示信号或屏幕缺陷补偿信号的第一输入信号,根据所述第一输入信号产生第一输出信号;

7.屏幕缺陷补偿内存,接收包括所述显示信号或所述屏幕缺陷补偿信号的第二输入信号,根据所述第二输入信号产生第二输出信号;

8.第一数据选择器,连接所述显示内存和所述屏幕缺陷补偿内存,分别接收所述显示内存发送的所述第一输出信号和所述屏幕缺陷补偿内存发送的所述第二输出信号,所述第一数据选择器根据第一切换信号、所述第一输出信号和所述第二输出信号产生显示输出信号;

9.第二数据选择器,连接所述显示内存和所述屏幕缺陷补偿内存,分别接收所述显示内存发送的所述第一输出信号和所述屏幕缺陷补偿内存发送的所述第二输出信号,所述第二数据选择器根据第二切换信号、所述第一输出信号和所述第二输出信号产生屏幕缺陷补偿输出信号;其中,所述第一切换信号和所述第二切换信号为相异。

10.在一实施例中,所述双内存功能切换电路还包括:

11.第三数据选择器,连接于所述显示内存及第一信号组、第二信号组及所述显示内存间,接收所述第一信号组发送的所述显示信号的控制信号、地址总线信号和数据总线信号,并接收所述第二信号组发送的所述屏幕缺陷补偿信号的控制信号、地址总线信号和数据总线信号;所述第三数据选择器根据第三切换信号、所述显示信号及所述屏幕缺陷补偿

信号发送所述第一输入信号至所述显示内存;

12.第四数据选择器,连接于所述屏幕缺陷补偿内存及所述第一信号组、所述第二信号组及所述屏幕缺陷补偿内存间,接收所述第一信号组发送的所述显示信号的控制信号、地址总线信号和数据总线信号,并接收所述第二信号组发送的所述屏幕缺陷补偿信号的控制信号、地址总线信号和数据总线信号;所述第四数据选择器根据第四切换信号、所述显示信号及所述屏幕缺陷补偿信号发送所述第二输入信号至所述屏幕缺陷补偿内存;其中,所述第三切换信号和所述第四切换信号为相异;所述第一切换信号和所述第三切换信号为相同;所述第二切换信号和所述第四切换信号为相同。

13.在一实施例中,所述第一信号组发送的所述显示信号的数据总线信号和地址总线信号的位宽和所述第二信号组发送的所述屏幕缺陷补偿信号的数据总线信号和地址总线信号的位宽为相同。

14.在一实施例中,所述第一信号组发送的所述显示信号的控制信号的高低电平和所述第二信号组发送的所述屏幕缺陷补偿信号的控制信号的高低电平为相同。

15.在一实施例中,所述显示内存和所述屏幕缺陷补偿内存的读写数据位宽为显示子像素数据位宽和屏幕缺陷补偿子像素数据位宽的公倍数。

16.第二方面,本发明提供了一种控制方法,所述控制方法应用于显示驱动芯片的双内存功能切换电路,所述双内存功能切换电路包括显示内存、屏幕缺陷补偿内存、第一数据选择器、第二数据选择器、第三数据选择器和第四数据选择器,所述第一数据选择器连接所述显示内存和所述屏幕缺陷补偿内存,所述第二数据选择器连接所述显示内存和所述屏幕缺陷补偿内存,所述第三数据选择器连接于所述显示内存及第一信号组、第二信号组及所述显示内存间,所述第四数据选择器连接于所述屏幕缺陷补偿内存及所述第一信号组、所述第二信号组及所述屏幕缺陷补偿内存间,所述控制方法包括:

17.所述第三数据选择器接收所述第一信号组发送的所述显示信号的控制信号、地址总线信号和数据总线信号,并接收所述第二信号组发送的所述屏幕缺陷补偿信号的控制信号、地址总线信号和数据总线信号;

18.所述第四数据选择器接收所述第一信号组发送的所述显示信号的控制信号、地址总线信号和数据总线信号,并接收所述第二信号组发送的所述屏幕缺陷补偿信号的控制信号、地址总线信号和数据总线信号

19.所述显示内存接收包括显示信号或屏幕缺陷补偿信号的第一输入信号,根据所述第一输入信号产生第一输出信号;

20.所述屏幕缺陷补偿内存接收包括所述显示信号或所述屏幕缺陷补偿信号的第二输入信号,根据所述第二输入信号产生第二输出信号;

21.所述第一数据选择器分别接收所述显示内存发送的所述第一输出信号和所述屏幕缺陷补偿内存发送的所述第二输出信号,所述第一数据选择器根据第一切换信号、所述第一输出信号和所述第二输出信号产生显示输出信号;

22.所述第二数据选择器分别接收所述显示内存发送的所述第一输出信号和所述屏幕缺陷补偿内存发送的所述第二输出信号,所述第二数据选择器根据第二切换信号、所述第一输出信号和所述第二输出信号产生屏幕缺陷补偿输出信号;其中,所述第一切换信号和所述第二切换信号为相异。

[0023][0024]

所述控制方法还包括:

[0025]

所述第三数据选择器根据第三切换信号、所述显示信号及所述屏幕缺陷补偿信号发送所述第一输入信号至所述显示内存;

[0026]

所述第四数据选择器根据第四切换信号、所述显示信号及所述屏幕缺陷补偿信号发送所述第二输入信号至所述屏幕缺陷补偿内存;其中,所述第三切换信号和所述第四切换信号为相异;所述第一切换信号和所述第三切换信号为相同;所述第二切换信号和所述第四切换信号为相同。

[0027]

根据本发明提供了一种显示驱动芯片的双内存功能切换电路,包括显示内存、屏幕缺陷补偿内存和第一、二、三、四数据选择器。显示内存接收第一输入信号,产生第一输出信号。屏幕缺陷补偿内存接收第二输入信号,产生第二输出信号。第一数据选择器分别接收显示内存发送的第一输出信号和屏幕缺陷补偿内存发送的第二输出信号,根据第一切换信号、第一、二输出信号产生显示输出信号。第二数据选择器分别接收显示内存发送的第一输出信号和屏幕缺陷补偿内存发送的第二输出信号,根据第二切换信号、第一、二输出信号产生屏幕缺陷补偿输出信号。第一切换信号和第二切换信号为相异。本发明提供的双内存功能切换电路,令显示驱动芯片兼容了双内存和两种单内存的应用场景,产品使用范围广。两种单内存(包括显示内存和屏幕缺陷补偿内存)的应用场景下,当使用中的内存损坏,可以用余下的内存进行替换,从而提高半导体芯片的裸片良率,有效降低芯片制程的成本。

[0028]

为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

附图说明

[0029]

为了更清楚地说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对本发明范围的限定。

[0030]

图1是本发明提供的显示驱动芯片的双内存功能切换电路的示意性电路图。

[0031]

图2是本发明提供的控制方法的流程图。

具体实施方式

[0032]

下面详细描述本发明的实施例,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。

[0033]

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0034]

下面将结合本发明实施例中附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0035]

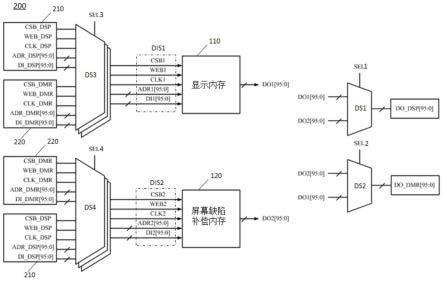

请参阅图1,图1是本发明提供的显示驱动芯片的双内存功能切换电路(以下简称“双内存功能切换电路”)的示意性电路图。双内存功能切换电路200包括显示内存110、屏幕缺陷补偿内存120、第一数据选择器ds1、第二数据选择器ds2、第三数据选择器ds3和第四数据选择器ds4。第三数据选择器ds3连接于显示内存110及第一信号组210、第二信号组220及显示内存110间。第四数据选择器ds4连接于屏幕缺陷补偿内存120及第一信号组210、第二信号组220及屏幕缺陷补偿内存120间。

[0036]

例如,数据选择器(data selector,ds)为根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。屏幕缺陷补偿(demura)为针对amoled生产工艺的外部补偿系统是将存在mura不良的显示屏通过先进的子像素级光学成像技术和软件算法消除mura纹,要求驱动芯片(ic)有一个单独内存(ram)来存储补偿需要的数据。

[0037]

在一实施例中,显示内存110接收包括显示信号或屏幕缺陷补偿信号的第一输入信号dis1。显示内存110根据第一输入信号dis1产生第一输出信号do1[95:0],并将第一输出信号do1[95:0]发送至第一数据选择器ds1及第二数据选择器ds2。屏幕缺陷补偿内存120接收包括显示信号或屏幕缺陷补偿信号的第二输入信号dis2。屏幕缺陷补偿内存120根据第二输入信号dis2产生第二输出信号do2[95:0],并将第二输出信号do2[95:0]发送至第一数据选择器ds1及第二数据选择器ds2。

[0038]

在一实施例中,第一数据选择器ds1连接显示内存110和屏幕缺陷补偿内存120。第一数据选择器ds1分别接收显示内存110发送的第一输出信号do1[95:0]和屏幕缺陷补偿内存120发送的第二输出信号do2[95:0]。第一数据选择器ds1根据第一切换信号sel1、第一输出信号do1[95:0]和第二输出信号do2[95:0]产生显示输出信号do_dsp[95:0]。例如,第一数据选择器ds1根据处理器(图未示)发送的第一切换信号sel1对第一输出信号do1[95:0]和第二输出信号do2[95:0]进行处理后产生显示输出信号do_dsp[95:0]。

[0039]

在一实施例中,第二数据选择器ds2连接显示内存110和屏幕缺陷补偿内存120。第二数据选择器ds2分别接收显示内存110发送的第一输出信号do1[95:0]和屏幕缺陷补偿内存120发送的第二输出信号do2[95:0]。第二数据选择器ds2根据第二切换信号sel2、第一输出信号do1[95:0]和第二输出信号do2[95:0]产生屏幕缺陷补偿输出信号do_dmr[95:0]。第一切换信号sel1和第二切换信号sel2为相异。第一数据选择器ds1和第二数据选择器ds2可以根据处理器发送的第一切换信号sel1和第二切换信号sel2分别对第一输出信号do1[95:0]和第二输出信号do2[95:0]进行处理后产生显示输出信号do_dsp[95:0]及屏幕缺陷补偿输出信号do_dmr[95:0]。换言之,若屏幕缺陷补偿内存120损坏,可以用显示内存110进行替换;若显示内存110损坏,可以屏幕缺陷补偿内存120进行替换,反之亦然。本发明使同一颗ddic在兼容传统的dual ram ddic功能的同时,满足了新型的single ram ddic应用需求,并且可以大大缩短研发周期,节省流片成本,同时在应用于single ram ddic的场景时,在使用的ram损坏时,可以用另一块ram替换损坏的ram,从而提升ic生产良率,降低成本。

[0040]

在一实施例中,第三数据选择器ds3接收第一信号组210发送的显示信号的控制信号(包括csb_dsp、web_dsp、clk_dsp信号)、地址总线信号(adr_dsp[95:0]信号)和数据总线信号(di_dsp[95:0]信号)。例如,csb为1时,代表不生效,csb为0时,代表生效;web为1时,代表读取,web为0时,代表写入。dsp(display)代表显示,clk(clock)代表时钟,adr(address)代表地址,di(data input)代表数据写入。第一信号组210发送的显示信号的数据总线信号和地址总线信号的位宽和第二信号组220发送的屏幕缺陷补偿信号的数据总线信号和地址

总线信号的位宽为相同。第一信号组210发送的显示信号的控制信号的高低电平和第二信号组220发送的屏幕缺陷补偿信号的控制信号的高低电平为相同。显示内存110和屏幕缺陷补偿内存120的读写数据位宽(例如96bit)为显示子像素数据位宽(例如8bit)和屏幕缺陷补偿子像素数据位宽(例如6bit)的公倍数,那么设计两块显示内存110和屏幕缺陷补偿内存120时必须保证控制信号的兼容,在本实施例中,设计成96bit位宽(可表示为上述[95:0])的内存,达成产品通用性以及应用性良好的效果。

[0041]

在一实施例中,第三数据选择器ds3接收第二信号组220发送的屏幕缺陷补偿信号的控制信号(包括csb_dmr、web_dmr、clk_dmr信号)、数据总线信号(di_dmr[95:0]信号)和地址总线信号(adr_dmr[95:0]信号)。第三数据选择器ds3根据第三切换信号sel3、显示信号及屏幕缺陷补偿信号发送第一输入信号dis1(包括csb1、web1、clk1、adr1[95:0]、di1[95:0]信号)至显示内存110。dmr(demure)代表屏幕缺陷补偿。

[0042]

在一实施例中,第四数据选择器ds4接收第一信号组210发送的显示信号的控制信号(包括csb_dsp、web_dsp、clk_dsp信号)、地址总线信号(adr_dsp[95:0])和数据总线信号(di_dsp[95:0]信号)。第四数据选择器ds4接收第二信号组220发送的屏幕缺陷补偿信号的控制信号(包括csb_dmr、web_dmr、clk_dmr信号)、地址总线信号(adr_dmr[95:0]信号)和数据总线信号(di_dmr[95:0]信号)。第四数据选择器ds4根据第四切换信号sel4、显示信号及屏幕缺陷补偿信号发送第二输入信号dis2(包括csb2、web2、clk2、adr2[95:0]、di2[95:0]信号)至屏幕缺陷补偿内存120。控制器发送的第三切换信号sel3和第四切换信号sel4为相异,用于分别控制显示内存110和屏幕缺陷补偿内存120。第一切换信号sel1和第三切换信号sel3为相同。第二切换信号sel2和第四切换信号sel4为相同。本发明针对传统的dual ram ddic做出改进,使其包含的存放显示数据和demura数据的ram可以互相替换使用,增加应用性。相对于当前dual ram规格的ddic直接应用于single ram的场景,本技术将提高6%-8%的die生产良率。相对于重新设计single ram ddic的场景,在目前光罩设计加流片大量耗时的大环境下,至少可以节省半年的研发周期,本发明对一颗ic的研发周期,可以兼容3颗ic(显示驱动芯片兼容了双内存和两种单内存的应用场景),不仅节约研发周期和研发费用,也节省了ic生产前期制作光罩的费用,有效降低成本。

[0043]

请同时参阅图1和图2,图2是本发明提供的控制方法的流程图。一种控制方法,应用于显示驱动芯片的双内存功能切换电路,双内存功能切换电路包括显示内存、屏幕缺陷补偿内存、第一数据选择器、第二数据选择器、第三数据选择器和第四数据选择器,第一数据选择器连接显示内存和所述屏幕缺陷补偿内存,第二数据选择器连接显示内存和屏幕缺陷补偿内存,第三数据选择器连接于显示内存及第一信号组、第二信号组及显示内存间,第四数据选择器连接于屏幕缺陷补偿内存及第一信号组、第二信号组及屏幕缺陷补偿内存间,控制方法包括:

[0044]

s301、第三数据选择器接收第一信号组发送的显示信号的控制信号、数据总线信号和地址总线信号,并接收第二信号组发送的屏幕缺陷补偿信号的控制信号、数据总线信号和地址总线信号;

[0045]

s305、第四数据选择器接收第一信号组发送的显示信号的控制信号、数据总线信号和地址总线信号,并接收第二信号组发送的屏幕缺陷补偿信号的控制信号、数据总线信号和地址总线信号;

[0046]

s310、显示内存接收包括显示信号或屏幕缺陷补偿信号的第一输入信号,根据第一输入信号产生第一输出信号;

[0047]

s320、屏幕缺陷补偿内存接收包括显示信号或屏幕缺陷补偿信号的第二输入信号,根据第二输入信号产生第二输出信号;

[0048]

s330、第一数据选择器分别接收显示内存发送的第一输出信号和屏幕缺陷补偿内存发送的第二输出信号,第一数据选择器根据第一切换信号、第一输出信号和第二输出信号产生显示输出信号;

[0049]

s340、第二数据选择器分别接收显示内存发送的第一输出信号和屏幕缺陷补偿内存发送的第二输出信号,第二数据选择器根据第二切换信号、第一输出信号和第二输出信号产生屏幕缺陷补偿输出信号;其中,第一切换信号和第二切换信号为相异。

[0050]

在一实施例中,控制方法还包括:

[0051]

第三数据选择器根据第三切换信号、显示信号及屏幕缺陷补偿信号发送第一输入信号至显示内存;

[0052]

第四数据选择器根据第四切换信号、显示信号及屏幕缺陷补偿信号发送第二输入信号至屏幕缺陷补偿内存;其中,第三切换信号和第切四换信号为相异;所述第一切换信号和所述第三切换信号为相同;所述第二切换信号和所述第四切换信号为相同。

[0053]

在一实施例中,第一信号组发送的显示信号的数据总线信号和地址总线信号的位宽和第二信号组发送的屏幕缺陷补偿信号的数据总线信号和地址总线信号的位宽为相同。

[0054]

在一实施例中,第一信号组发送的显示信号的控制信号的高低电平和第二信号组发送的屏幕缺陷补偿信号的控制信号的高低电平为相同。

[0055]

在一实施例中,显示内存和屏幕缺陷补偿内存的读写数据位宽为显示子像素数据位宽和屏幕缺陷补偿子像素数据位宽的公倍数。

[0056]

为使本发明实施例的目的、技术方案和优点更加清楚,上面结合本发明实施例中的附图,对本发明实施例中的技术方案进行了清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

[0057]

因此,以上对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1