移位寄存器单元及其驱动方法、栅极驱动电路、显示装置与流程

本技术涉及显示,尤其涉及移位寄存器单元及其驱动方法、栅极驱动电路、显示装置。

背景技术:

1、阵列基板行驱动(gate driver on array,goa)电路通常包括多个级联的goa单元,每个goa单元用于驱动一行像素。由该多个级联的goa单元可以实现对显示装置中各行像素的逐行扫描,以显示图像,goa电路也称栅极驱动电路。

2、在相关技术中,受工艺和材料影响,goa单元的输出电路中晶体管的阈值电压容易发生偏移(如,正偏)。如此,容易导致输出信号异常,影响像素发光,从而造成显示效果较差。

技术实现思路

1、有鉴于此,本技术的目的在于提出一种移位寄存器单元及其驱动方法、栅极驱动电路、显示装置,以提供稳定的移位寄存器单元及栅极驱动电路、显示装置。

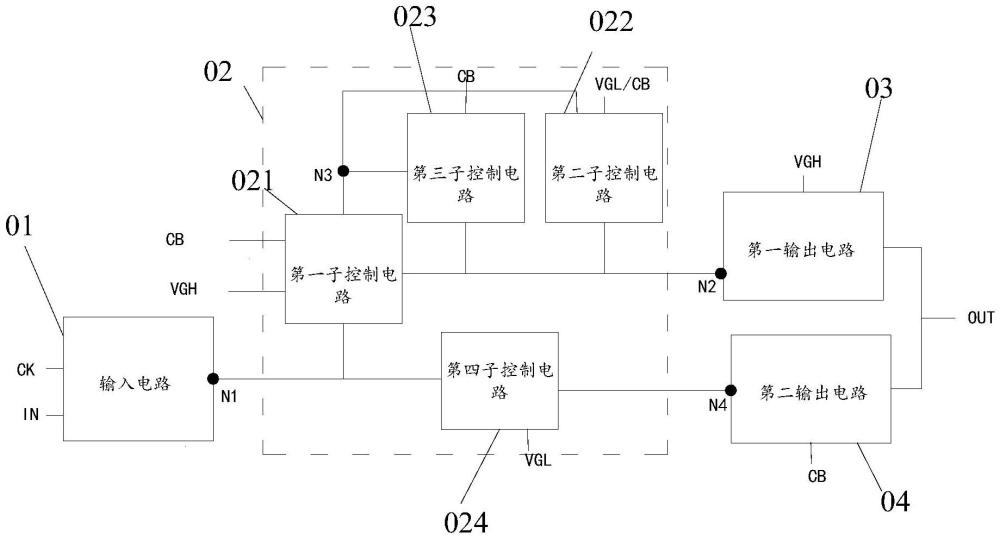

2、基于上述目的,本技术提供了一种移位寄存器单元,包括:输入电路、输出控制电路、第一输出电路和第二输出电路;

3、所述输入电路,分别与第一时钟信号端和输入信号端连接,并被配置为:基于所述第一时钟信号端提供的第一时钟信号和所述输入信号端提供的输入信号,控制所述第一节点的电位;

4、所述输出控制电路,分别与所述第一节点、第二节点、第四节点、第二时钟信号端、第一电源端和第二电源端连接,并被配置为:基于所述第一节点的电位、所述第二时钟信号端提供的第二时钟信号、所述第一电源端提供的第一电源信号和所述第二电源端提供的第二电源信号,控制所述第二节点的电位;基于所述第一节点的电位和所述第二时钟信号提供的第二时钟信号,控制所述第四节点的电位;

5、所述第一输出电路,分别与所述第二节点和所述第一电源端连接,并被配置为:在所述第二节点的电位的控制下,将所述第一电源端提供的第一电源信号输出;

6、所述第二输出电路,分别与所述第四节点和所述第二时钟信号端连接,并被配置为:在所述第四节点的电位控制下,将所述第二时钟信号端提供的第二时钟信号输出;

7、其中,所述输出控制电路包括第一子控制电路和第二子控制电路;

8、所述第一子控制电路,分别与所述第一节点、所述第二节点、第三节点、所述第二时钟信号端和所述第一电源端连接,并被配置为:基于所述第一节点的电位、所述第二时钟信号端提供的第二时钟信号和所述第一电源端提供的第一电源信号,控制所述第二节点的电位和所述第三节点的电位;

9、所述第二子控制电路,分别与所述第二节点和第一控制信号端连接,且与所述第一节点或所述第三节点连接,并被配置为:基于所述第一控制信号端提供的第一控制信号和所述第一节点或所述第三节点的电位,保持所述第二节点的电位。

10、可选地,所述第二子控制电路被配置为基于所述第一控制信号端提供的第一控制信号和所述第三节点,控制所述第二节点和所述第一控制信号端之间导通,保持所述第二节点的电位。

11、可选地,所述第二子控制电路被配置为基于所述第一控制信号端提供的第一控制信号和所述第一节点,控制所述第二节点和所述第一控制信号端之间导通,保持所述第二节点的电位。

12、可选地,所述第一控制信号端包括所述第二时钟信号端或所述第二电源端,所述第一控制信号包括所述第二时钟信号或所述第二电源信号。

13、可选地,所述输出控制电路还包括第三子控制电路和第四子控制电路;

14、所述第三子控制电路分别与所述第三节点、所述第二节点和所述第二时钟信号端连接,基于所述第三节点的电位和所述第二时钟信号端提供的所述第二时钟信号,控制所述第二节点的电位;

15、所述第四子控制电路分别与所述第一节点、所述第二电源端和所述第四节点连接,基于所述第一节点的电位和所述第二电源端提供的第二电源信号,控制所述第四节点的电位。

16、可选地,所述输入电路包括第一晶体管,所述第一晶体管的第一极与输入信号端连接,所述第一晶体管的第二极与所述第一节点连接,所述第一晶体管的控制极与所述第一时钟信号端连接。

17、可选地,所述第一子控制电路包括第二晶体管、第六晶体管、第七晶体管和第九晶体管;

18、所述第九晶体管的第一极与所述第一节点连接,所述第九晶体管的第二极与通过第五节点与所述第六晶体管的第一极连接,所述第九晶体管的控制极与所述第二时钟信号端连接,所述第六晶体管的第二极与所述第二晶体管的第一极连接,所述第六晶体管的第二极与所述第二晶体管的第一极还与所述第一电源端连接,所述第二晶体管的第二极与第二节点连接,所述第二晶体管的控制极与所述第七晶体管的控制极连接,所述第七晶体管的第一极与所述第一电源端连接,所述第七晶体管的第二极与所述第三节点连接。

19、可选地,所述第二子控制电路包括第十晶体管,所述第十晶体管为p型晶体管,所述第十晶体管的第一极与所述第二电源端连接,所述第十晶体管的第二极通过第二节点与所述第一输出电路连接,所述第十晶体管的控制极与所述第三节点连接。

20、可选地,所述第二子控制电路包括第十晶体管,所述第十晶体管为n型晶体管,所述第十晶体管的第一极与第二电源端连接,所述第十晶体管的第二极通过第二节点与所述第一输出电路连接,所述第十晶体管的控制极与所述第一节点连接。

21、可选地,所述第三子控制电路包括第三晶体管和第三电容,第三晶体管,所述第三晶体管的第一极与所述第二时钟信号端连接,所述第三晶体管的第二极与所述第二节点连接,所述第三晶体管的控制极与所述第三节点连接,所述第三电容的第一极与所述第三晶体管的第一极连接,所述第三电容的第二极与所述第三节点连接。

22、可选地,所述第四子控制电路包括第八晶体管,所述第八晶体管的第一极与所述第一节点连接,所述第八晶体管的第二极与所述第四节点连接,所述第八晶体管的控制极与第二电源端连接。

23、可选地,所述第一输出电路包括第四晶体管和第二电容,所述第四晶体管第一极与第一电源端连接,所述第四电容的第二极与输出端连接,所述第四晶体管的控制极与所述第二节点连接;所述第二电容的第一极与所述第四晶体管的第一极连接,所述第二电容的第二极与所述第四晶体管的控制极连接。

24、可选地,所述第二输出电路包括第五晶体管和第一电容,所述第五晶体管的第一极与第二时钟信号端连接,所述第五晶体管的第二极与输出端连接,所述第五晶体管的控制极与所述第四节点连接;所述第二输出电路还包括第一电容,所述第一电容的第一极与所述第五晶体管的第一极连接,所述第一电容的第二极与所述第五晶体管的控制极连接。

25、可选地,所述第一电容的第一极包括相连接的第一连接端和第一增容端,所述第一电容的第二极包括相连接的第二连接端和第二增容端,所述第一连接端和第二连接端与所述第五晶体管的第二极在衬底基板上的正投影部分重叠,所述第一增容端和第二增容端与所述第五晶体管的第二电极在所述衬底基板上的正投影不重叠。

26、基于同一发明构思,本技术还提供了一种移位寄存器单元的驱动方法,应用于上述任一所述的移位寄存器单元,所述方法包括:

27、输入电路在第一时钟信号端提供的第一时钟信号的控制下,将输入信号端提供的输入信号写入所述第一节点;

28、输出控制电路在所述第一节点的电位控制下,将第二时钟信号端提供的第二时钟信号写入第二节点,将第二电源端提供的第二电源信号写入第四节点;

29、第一输出电路在所述第二节点的电位控制下,将第一电源端提供的第一电源信号输出;

30、第二输出电路在所述第四节点的电位控制下,将所述第二时钟信号端提供的第二时钟信号输出;

31、其中,所述输出控制电路包括第一子控制电路和第二子控制电路;

32、所述输出控制电路在所述第一节点的电位控制下,将第二时钟信号端提供的第二时钟信号写入第二节点,将第二电源端提供的第二电源信号写入第四节点进一步包括:

33、所述第一子控制电路基于所述第一节点的电位、所述第二时钟信号端提供的第二时钟信号和所述第一电源端提供的第一电源信号,控制所述第二节点的电位和第三节点的电位;

34、所述第二子控制电路控制所述第二节点和所述第一控制信号之间导通,保持所述第二节点的电位。

35、基于同一发明构思,本技术还提供了一种栅极驱动电路,应用于如上述任一所述的移位寄存器单元,所述栅极驱动电路包括级联的至少两级移位寄存器单元;

36、其中,移位寄存器单元第n级移位寄存器单元的输出端作为第n+1级移位寄存器单元的输入端,第一级移位寄存器单元的输入端连接帧起始信号,n为大于或等于1的整数。

37、基于同一发明构思,本技术还提供了一种显示装置,包括如上述所述的栅极驱动电路。

38、从上面所述可以看出,本技术提供的一种移位寄存器单元及其驱动方法、栅极驱动电路、显示装置,该移位寄存器单元包括输入电路、输出控制电路、第一输出电路和第二输出电路;输入电路能够控制第一节点电位,输出控制电路能够基于第一节点电位控制第二节点和第三节点电位,第一输出电路和第二输出电路能够基于第二节点和第三节点电位向输出端提供输出控制信号;其中,输出控制电路包括第一子控制电路和第二子控制电路;第一子控制电路,分别与第一节点、第二节点、第三节点、第二时钟信号端和第一电源端连接,并被配置为:基于第一节点的电位、第二时钟信号端提供的第二时钟信号和第一电源端提供的第一电源信号,控制第二节点的电位和第三节点的电位;第二子控制电路,分别与第二节点和第一控制信号端连接,且与第一节点或第三节点连接,并被配置为:基于第一控制信号端提供的第一控制信号和第一节点或第三节点的电位,保持第二节点的电位。如此,可以通过第一子控制电路控制第二节点和第三节点的电位,使第一输出电路和第二输出电路能够输出稳定的输出信号,在移位寄存器单元中晶体管的阈值电压发生偏移时,第二节点的电位会被拉低,导致第一输出电路输出异常,因此,可以通过第二子控制电路保持第二节点的电位,使得第一输出电路能够输出有效电位,进而确保可以可靠驱动像素发光,使得显示效果较好。

- 还没有人留言评论。精彩留言会获得点赞!