一种双栅驱动的像素结构及显示面板的制作方法

1.本发明涉及半导体技术领域,特别是涉及一种双栅驱动的像素结构及显示面板。

背景技术:

2.随着半导体技术的提高,要求薄膜晶体管液晶显示器(thin film transistor liquid crystal display,tft

‑

lcd)能够达到高性能以及降低成本,由于z像素结构具备功耗低且充电边界优,不会产生因相反极性导致的摇头纹等特点,因此很多双栅(dual gate)产品都采用z像素结构。

3.但是z像素结构存在面内像素的侧向电容差异,造成不同像素电极之间存在电压差异,会使显示画面产生竖纹,该竖纹正负帧可抵消,即在用户静态正视显示画面时不会产生看到竖纹,但是当用户动态摆头观看显示画面时,则会看到竖纹,称为摇头纹。因此,需要一种能够解决摇头纹问题的像素结构。

技术实现要素:

4.本发明实施例的目的在于提供一种双栅驱动的像素结构及显示面板,用以解决摇头纹的问题。具体技术方案如下:

5.第一方面,本发明实施例提供了一种双栅驱动的像素结构,所述像素结构包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:

6.所述四条栅极线平行设置,所述四条数据线垂直于所述栅极线设置,限定出排列为两行的所述六个像素区,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管;

7.所述两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素至第六像素,第二行包括第七像素至第十二像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线;

8.所述第一像素、第四像素、第六像素、第七像素、第十像素以及第十二像素的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管;

9.所述像素结构包括以下至少一种结构:所述第三像素、所述第五像素以及所述第八像素的电极与薄膜晶体管的源级之间的连接线与其他像素的电极与薄膜晶体管的源级之间的连接线中较长的连接线的长度相等;

10.所述第三像素、所述第五像素以及所述第八像素的电极与位于其下方的栅极线部分交叠;

11.所述第四像素、所述第六像素以及所述第七像素的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离,其中,所述目标像素为电极与栅极线不存在交叠的像素。

12.可选的,所述第三像素的电极、所述第五像素的电极以及所述第八像素的电极与位于其下方的栅极线交叠部分的电容为第一预设电容;

13.其中,所述第一预设电容为所述第二像素的电极与栅极线之间的电容与第一目标电容的差值,所述第一目标电容为未与栅极线交叠状态下的第三像素的电极与栅极线之间的电容。

14.可选的,所述第四像素的电极、所述第六像素的电极以及所述第七像素的电极与位于其下方的栅极线之间的距离使得所述第四像素的电极、所述第六像素的电极以及所述第七像素的电极与栅极线之间的电容为第二预设电容;

15.其中,所述第二预设电容为第二目标电容与所述第二像素的电极与栅极线之间的电容的差值,所述第二目标电容为与栅极线之间的距离与所述第二像素的电极与栅极线之间的距离相同的状态下的第四像素的电极与栅极线之间的电容。

16.可选的,所述第一像素至所述第十二像素的电极与其上方的栅极线之间的距离均相同。

17.第二方面,本发明实施例提供了一种双栅驱动的像素结构,所述像素结构包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:

18.所述四条栅极线平行设置,所述四条数据线垂直于所述栅极线设置,限定出排列为两行的所述六个像素区,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管;

19.所述两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素至第六像素,第二行包括第七像素至第十二像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线;

20.所述第一像素、第四像素、第六像素、第七像素、第十像素以及第十二像素的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管;

21.所述像素结构包括结构:所述第一像素至所述第十二像素的电极与薄膜晶体管的源级之间的连接线的长度均相等;和/或,

22.所述第一像素、所述第二像素、所述第三像素、所述第五像素、所述第八像素、所述第九像素、所述第十像素、所述第十一像素以及所述第十二像素的电极与其连接的薄膜晶体管所在的栅极线部分交叠。

23.可选的,所述第一像素、所述第二像素、所述第三像素、所述第五像素、所述第八像素、所述第九像素、所述第十像素、所述第十一像素以及所述第十二像素的电极与其连接的薄膜晶体管所在的栅极线交叠部分的电容为第三预设电容;

24.其中,所述第三预设电容为所述第四像素的电极与栅极线之间的电容与第三目标电容的差值,所述第三目标电容为未与栅极线交叠状态下的第一像素的电极与栅极线之间的电容。

25.可选的,所述第一像素至所述第十二像素的未与栅极线交叠一侧的电极与其临近的栅极线之间的距离均相同。

26.第三方面,本发明实施例提供了一种双栅驱动的显示面板,所述显示面板包括上

述第一方面任一所述的像素结构。

27.第四方面,本发明实施例提供了一种双栅驱动的显示面板,所述显示面板包括上述第二方面任一所述的像素结构。

28.本发明实施例有益效果:

29.本发明实施例提供的像素结构中,包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:四条栅极线平行设置,四条数据线垂直于所述栅极线设置,限定出排列为两行的六个像素区,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管,两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素至第六像素,第二行包括第七像素至第十二像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线,第一像素、第四像素、第六像素、第七像素、第十像素以及第十二像素的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管,像素结构包括以下至少一种结构:第三像素、第五像素以及第八像素的电极与薄膜晶体管的源级之间的连接线与其他像素的电极与薄膜晶体管的源级之间的连接线中较长的连接线的长度相等,第三像素、第五像素以及第八像素的电极与位于其下方的栅极线部分交叠,第四像素、第六像素以及第七像素的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离,其中,目标像素为电极与栅极线不存在交叠的像素。

30.由于像素结构中包括以上至少一种结构,所以可以通过连接线的长度、电极与栅极线部分交叠和/或电极与栅极线之间的距离来减小甚至消除不同像素的电极之间电容差异,从而减小甚至消除不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,改善因电压差所产生的竖纹,从而改善甚至解决摇头纹的问题。当然,实施本发明的任一产品或方法并不一定需要同时达到以上所述的所有优点。

附图说明

31.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的实施例。

32.图1为本发明实施例的目前z像素结构的一种示意图;

33.图2为图1所示的z像素结构的显示画面的一种示意图;

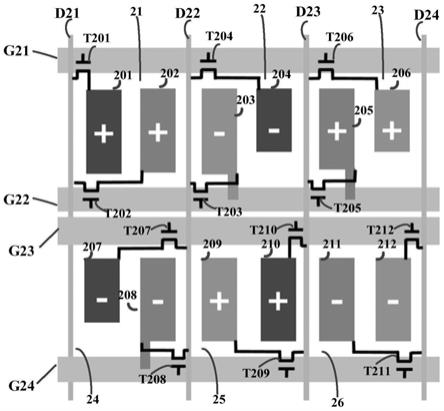

34.图3为本发明实施例所提供的第一种双栅驱动的像素结构的结构示意图;

35.图4为图1所示的z像素结构的显示画面的另一种示意图;

36.图5为本发明实施例所提供的第二种双栅驱动的像素结构的结构示意图;

37.图6为本发明实施例所提供的双栅驱动的像素结构的显示画面的一种示意图;

38.图7为本发明实施例所提供的像素结构与目前z像素结构的一种对比图。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完

整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员基于本发明所获得的所有其他实施例,都属于本发明保护的范围。

40.目前显示面板的z像素结构包括多个像素单元,每个像素单元如图1所示,包括四条栅极线g11

‑

栅极线g14、四条数据线d11

‑

数据线d14以及六个像素区,即像素区11、像素区12、像素区13、像素区14、像素区15以及像素区16。

41.栅极线g11、栅极线g12、栅极线g13以及栅极线g14平行设置,其中,栅极线g11与栅极线g12之间的距离和栅极线g13与栅极线g14之间的距离相等,栅极线g12与栅极线g13相邻设置,数据线d11、数据线d12、数据线d13以及数据线d14依次垂直于栅极线设置,且相邻数据线之间的距离相等,这样,栅极线和数据线共同限定出排列为两行的六个像素区。

42.每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管,两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线每个像素区中的两个像素平行于栅极线设置,具体来说:

43.在像素区11中,像素101的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t101和薄膜晶体管t102,薄膜晶体管t101设置于栅极线g11上,薄膜晶体管t102设置于栅极线g12上。像素101与像素102平行于栅极线设置,像素101与像素102与位于上方的栅极线g11的距离相等,与下方栅极线g12的距离也相等,像素101的电极与薄膜晶体管t101的源级相连,薄膜晶体管t101的栅极与栅极线g11相连,薄膜晶体管t101的漏极与数据线d11相连。

44.像素102的电极与薄膜晶体管t102的源级相连,薄膜晶体管t102栅极与栅极线g12相连,薄膜晶体管t102的漏极与数据线d11相连。像素101的电极与薄膜晶体管t101的源级的连接线比像素102的电极与薄膜晶体管t102的源级的连接线短,即像素101的电极与薄膜晶体管t101为短桥连接,像素102的电极与薄膜晶体管t102为长桥连接。

45.在像素区12中,像素103的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t103和薄膜晶体管t104,薄膜晶体管t103设置于栅极线g12上,薄膜晶体管t104设置于栅极线g11上。像素103与像素104平行于栅极线设置,像素103与像素104与位于上方的栅极线g11的距离相等,与下方栅极线g12的距离也相等,像素103的电极与薄膜晶体管t103的源级相连,薄膜晶体管t103的栅极与栅极线g12相连,薄膜晶体管t103的漏极与数据线d12相连。

46.像素104的电极与薄膜晶体管t104的源级相连,薄膜晶体管t104的栅极与栅极线g11相连,薄膜晶体管t104的漏极与数据线d12相连,像素103的电极与薄膜晶体管t103的源级的连接线比像素104的电极与薄膜晶体管t104的源级的连接线短,即像素103的电极与薄膜晶体管t103为短桥连接,像素104的电极与薄膜晶体管t104为长桥连接。

47.在像素区13中,像素105的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t105和薄膜晶体管t106,薄膜晶体管t105设置于栅极线g12上,薄膜晶体管t106设置于栅极线g11上。像素105与像素106平行于栅极线设置,像素105与像素106与位于上方的栅极线g11的距离相等,与下方栅极线g12的距离也相等,像素105的电极与薄膜晶体管t105的源级相连,薄膜晶体管t105的栅极与栅极线g12相连,薄膜晶体管t105的漏极

与数据线d13相连。

48.像素106的电极与薄膜晶体管t106的源级相连,薄膜晶体管t106的栅极与栅极线g11相连,薄膜晶体管t106的漏极与数据线d13相连,像素105的电极与薄膜晶体管t105的源级的连接线比像素106的电极与薄膜晶体管t106的源级的连接线短,即像素105的电极与薄膜晶体管t105为短桥连接,像素106的电极与薄膜晶体管t106为长桥连接。

49.在像素区14中,像素108的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t107和薄膜晶体管t108,薄膜晶体管t107设置于栅极线g13上,薄膜晶体管t108设置于栅极线g14上。像素107与像素108平行于栅极线设置,像素107与像素108与位于上方的栅极线g13的距离相等,与下方栅极线g14的距离也相等,像素107的电极与薄膜晶体管t107的源级相连,薄膜晶体管t107的栅极与栅极线g13相连,薄膜晶体管t107的漏极与数据线d12相连。

50.像素108的电极与薄膜晶体管t108的源级相连,薄膜晶体管t108的栅极与栅极线g14相连,薄膜晶体管t108的漏极与数据线d12相连,像素107的电极与薄膜晶体管t107的源级的连接线比像素108的电极与薄膜晶体管t108的源级的连接线长,即像素108的电极与薄膜晶体管t108为短桥连接,像素107的电极与薄膜晶体管t107为长桥连接。

51.在像素区15中,像素110的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t109和薄膜晶体管t110,薄膜晶体管t110设置于栅极线g13上,薄膜晶体管t109设置于栅极线g14上。像素109与像素110平行于栅极线设置,像素109与像素110与位于上方的栅极线g13的距离相等,与下方栅极线g14的距离也相等,像素109的电极与薄膜晶体管t109的源级相连,薄膜晶体管t109的栅极与栅极线g14相连,薄膜晶体管t109的漏极与数据线d13相连。

52.像素110的电极与薄膜晶体管t110的源级相连,薄膜晶体管t110的栅极与栅极线g13相连,薄膜晶体管t110的漏极与数据线d13相连,像素109的电极与薄膜晶体管t109的源级的连接线比像素110的电极与薄膜晶体管t110的源级的连接线长,即像素110的电极与薄膜晶体管t110为短桥连接,像素109的电极与薄膜晶体管t109为长桥连接。

53.在像素区16中,像素112的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t111和薄膜晶体管t112,薄膜晶体管t112设置于栅极线g13上,薄膜晶体管t111设置于栅极线g14上。像素111与像素112平行于栅极线设置,像素111与像素112与位于上方的栅极线g13的距离相等,与下方栅极线g14的距离也相等,像素111的电极与薄膜晶体管t111的源级相连,薄膜晶体管t111的栅极与栅极线g14相连,薄膜晶体管t111的漏极与数据线d14相连。

54.像素112的电极与薄膜晶体管t112的源级相连,薄膜晶体管t112的栅极与栅极线g13相连,薄膜晶体管t112的漏极与数据线d14相连,像素111的电极与薄膜晶体管t111的源级的连接线比像素112的电极与薄膜晶体管t112的源级的连接线长,即像素112的电极与薄膜晶体管t112为短桥连接,像素111的电极与薄膜晶体管t111为长桥连接。

55.以上述像素区11为例,z像素结构中产生侧向电容差异的原因共有三个,具体如下:

56.原因一、由于像素102的电极与薄膜晶体管t102的源级的连接线比像素101的电极与薄膜晶体管t101的连接线长,导致像素102的电极与栅极线的源级之间的侧向电容c

gs长

大

于像素101的电极与栅极线的源级之间的侧向电容c

gs

短,从而导致像素间的

△

vp差异。

57.原因二、由于像素101的电极连接于奇数行的栅极线g11上,而连接在奇数行的像素不仅受到本行栅极线关断的影响,还会受到下一行栅极线关断的影响,即像素101不仅受到栅极线g11关断的影响,还会受到下一行栅极线g12的影响。而像素102连接于偶数行的栅极线g12上,连接在偶数行的像素只受到本行栅极线关断的影响,即像素102只受到栅极线g12关断的影响,因此,像素101对应的侧向电容包括受到栅极线g11关断的影响所产生的电容c

gp自

和受到栅极线g12关断影响所产生的电容c

gp他

,像素102对应的侧向电容仅包括受到栅极线g12关断的影响所产生的电容c

gp自

,从而导致像素间的

△

vp’差异。

58.原因三、由于像素101的电极上方的栅极线g11和下方的栅极线g12均设置有薄膜晶体管,因此,像素101的电极上方的栅极线g11和下方的栅极线g12的挖槽多,像素101的电极与栅极线之间的电容c

gp

小,即c

gp自

和c

gp他

均较小。而像素102的电极上方的栅极线g11和下方的栅极线g12未设置薄膜晶体管,像素102的电极上方的栅极线g11和下方的栅极线g12挖槽少,像素102的电极与栅极线之间的c

gp

大,即c

gp自

较大,从而导致像素间的

△

vp’差异。

59.同样的,在像素区像素区12、像素区13、像素区14、像素区15以及像素区16中的像素也存在上述三个原因导致的侧向电容差异,由于侧向电容差异的存在,导致不同的像素之间产生电压差异。

60.针对上述z像素结构的像素单元,根据实验可以计算得到像素101对应的

△

vp+

△

vp’之和为0.3v;像素102对应的为0.3v;像素103对应的

△

vp+

△

vp’之和为0.2v,与像素101和像素102相差8个灰阶;像素104对应

△

vp+

△

vp’之和为0.4v,与像素101和像素102相差8个灰阶。

61.可以看出,像素101和像素102对应的侧向电容相等,即“c

gs短”+“c

gp自

小”+“c

gp他

小”等效于“c

gs长”+“c

gp自

大”。由于其余像素的连接关系分别像素101、像素102、像素103、像素104中的一个相同,所以其余像素对应的侧向电容为像素101、像素102、像素103、像素104对应的侧向电容一个相同。也就是说,像素单元包括的12个像素根据对应的侧向电容的差异可以划分为三类,第一类像素包括像素101、像素102、像素109、像素110、像素111以及像素112,第二类像素包括像素104、像素106以及像素107,第三类像素包括像素103、像素105以及像素108。其中,三类像素包括的像素对应的侧向电容导致的电压差异分别为0.3v、0.4v以及0.2v。

62.在这种情况下,假设显示面板的公共电压vcom的大小以上述第一类像素即像素101、像素102、像素109、像素110、像素111以及像素112作为基准,由于上述第二类像素对应的电压差异大于第一类像素对应的电压差异,上述第三类像素对应的电压差异小于第一类像素对应的电压差异,那么,其会导致显示画面的效果如图2所示。正帧时,像素101、像素102正极性显示正常,像素103负极性偏暗,像素104负极性偏亮,像素105正极性偏亮,像素106正极性偏暗,像素107负极性偏亮,像素108负极性偏暗,像素109正极性正常,像素110正极性正常,像素111负极性正常,像素112负极性正常。

63.负帧时,像素101、像素102负极性显示正常,像素103正极性偏亮,像素104正极性偏暗,像素105负极性偏暗,像素106负极性偏亮,像素107正极性偏暗,像素108正极性偏亮,像素109负极性正常,像素110负极性正常,像素111正极性正常,像素112正极性正常。以此类推,正帧时产生暗亮交替竖纹,负帧时产生亮暗交替竖纹,该竖纹正负帧可抵消,但是用

户摆头观看时会产生摇头纹。

64.为了能够解决摇头纹的问题,本发明实施例提供了一种双栅驱动的像素结构及显示面板,下面对本发明实施例所提供的第一种双栅驱动的像素结构进行介绍。

65.如图3所示,一种双栅驱动的像素结构,所述像素结构包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:

66.所述四条栅极线g21

‑

g24平行设置,所述四条数据线d21

‑

d24垂直于所述栅极线设置,限定出排列为两行的所述六个像素区21

‑

26,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管;

67.所述两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素201至第六像素206,第二行包括第七像素207至第十二像素212,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线;

68.所述第一像素201、第四像素202、第六像素206、第七像素207、第十像素210以及第十二像素212的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管;

69.所述像素结构包括以下至少一种结构:所述第三像素203、所述第五像素205以及所述第八像素208的电极与薄膜晶体管的源级之间的连接线与其他像素的电极与薄膜晶体管的源级之间的连接线中较长的连接线的长度相等;

70.所述第三像素203、所述第五像素205以及所述第八像素208的电极与位于其下方的栅极线部分交叠;

71.所述第四像素204、所述第六像素206以及所述第七像素207的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离。

72.其中,所述目标像素为电极与栅极线不存在交叠的像素。

73.可见,本发明实施例提供的像素结构中,包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:四条栅极线平行设置,四条数据线垂直于所述栅极线设置,限定出排列为两行的六个像素区,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管,两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素至第六像素,第二行包括第七像素至第十二像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线,第一像素、第四像素、第六像素、第七像素、第十像素以及第十二像素的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管,像素结构包括以下至少一种结构:第三像素、第五像素以及第八像素的电极与薄膜晶体管的源级之间的连接线与其他像素的电极与薄膜晶体管的源级之间的连接线中较长的连接线的长度相等,第三像素、第五像素以及第八像素的电极与位于其下方的栅极线部分交叠,第四像素、第六像素以及第七像素的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离,其中,目标像素为电极与栅极线不存在交叠的像素。由于像素结构中包括以上至少一种结构,所以可以通过连接线的长度、电极与栅极线部分交叠和/或电极与栅极线之间的距离来减小甚至消除不同像素的电极之间电容差异,从而减小甚至消除不同像素的电极之间的电压

差,进而使显示面板中不同像素之间的电容差异得到平均,改善因电压差所产生的竖纹,从而改善甚至解决摇头纹的问题。

74.本发明实施提供的第一种双栅驱动的像素结构包括多个像素单元,每个像素单元包括栅极线g21

‑

栅极线g24、数据线d21

‑

数据线d24、像素区21、像素区22、像素区23、像素区24、像素区25以及像素区26。

75.四条栅极线平行设置,其中,栅极线g21与栅极线g22之间的距离与栅极线g23与栅极线g24之间的距离相等,栅极线g22与栅极线g23相邻设置,数据线d21、数据线d22、数据线d23以及数据线d24垂直于栅极线依次设置,且相邻数据线之间的距离相等,这样,限定出排列为两行的六个像素区。

76.第一行像素区包括像素区21、像素区22以及像素区23,第二行像素区包括像素区24、像素区25以及像素区26。像素区21与像素区24构成的第一列像素区,像素区22与像素区25构成第二列像素区,像素区23与像素区26构成第三列像素区。

77.每个像素区包括两个平行于栅极线设置的像素,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管。该两个薄膜晶体管的漏极连接于同一条数据线,垂直的两个像素区连接于不同的数据线,即垂直的两个像素区对应的薄膜晶体管连接于不同的数据线。即第一像素201、第四像素204、第六像素206、第七像素207、第十像素210以及第十二像素212的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管。其中,奇数行栅极线即为栅极线g21和栅极线g23,偶数行栅极线即为栅极线g22和栅极线g24。

78.在像素区21中,像素201的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t201和薄膜晶体管t202,薄膜晶体管t201设置于栅极线g21上,薄膜晶体管t202设置于栅极线g22上。第一像素201与第二像素202平行于栅极线设置,第一像素201的电极与薄膜晶体管t201的源级相连,薄膜晶体管t201的栅极与栅极线g21相连,薄膜晶体管t201的漏极与数据线d21相连,第二像素202的电极与薄膜晶体管t202的源级相连,薄膜晶体管t202的栅极与栅极线g22相连,薄膜晶体管t202的漏极与数据线d21相连。

79.在像素区22中,像素203的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t203和薄膜晶体管t204,薄膜晶体管t204设置于栅极线g21上,薄膜晶体管t203设置于栅极线g22上。第三像素203与第四像素204平行于栅极线设置,第三像素203的电极与薄膜晶体管t203的源级相连,薄膜晶体管t203的栅极与栅极线g22相连,薄膜晶体管t203的漏极与数据线d22相连,第四像素204的电极与薄膜晶体管t204的源级相连,薄膜晶体管t204的栅极与栅极线g21相连,薄膜晶体管t204的漏极与数据线d22相连。

80.在像素区23中,像素205的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t205和薄膜晶体管t206,薄膜晶体管t206设置于栅极线g21上,薄膜晶体管t205设置于栅极线g22上。第五像素205与第六像素206平行于栅极线设置,第五像素205的电极与薄膜晶体管t205的源级相连,薄膜晶体管t205的栅极与栅极线g22相连,漏极与数据线d23相连,第六像素206的电极与薄膜晶体管t206的源级相连,薄膜晶体管t206的栅极与栅极线g21相连,薄膜晶体管t206的漏极与数据线d23相连。

81.在像素区24中,像素208的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t207和薄膜晶体管t208,薄膜晶体管t207设置于栅极线g23上,薄膜晶

体管t208设置于栅极线g24上。第七像素207与第八像素208平行于栅极线设置,第七像素207的电极与薄膜晶体管t207的源级相连,薄膜晶体管t207的栅极与栅极线g23相连,薄膜晶体管t207的漏极与数据线d22相连,第八像素208的电极与薄膜晶体管t208的源级相连,薄膜晶体管t208的栅极与栅极线g24相连,薄膜晶体管t208的漏极与数据线d22相连。

82.在像素区25中,像素210的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t209和薄膜晶体管t210,薄膜晶体管t210设置于栅极线g23上,薄膜晶体管t209设置于栅极线g24上。第九像素209与第十像素210平行于栅极线设置,第九像素209的电极与薄膜晶体管t209的源级相连,薄膜晶体管t209的栅极与栅极线g24相连,漏极与数据线d23相连,第十像素210的电极与薄膜晶体管t210的源级相连,薄膜晶体管t210的栅极与栅极线g23相连,薄膜晶体管t210的栅极漏极与数据线d23相连。

83.在像素区26中,像素212的上下两条栅极线上设置有上下位置对应的两个薄膜晶体管,即薄膜晶体管t211和薄膜晶体管t212,薄膜晶体管t212设置于栅极线g23上,薄膜晶体管t211设置于栅极线g24上。第十一像素211与第十二像素212平行于栅极线设置,第十一像素211的电极与薄膜晶体管t211的源级相连,薄膜晶体管t211的栅极与栅极线g24相连,漏极与数据线d24相连,第十二像素212的电极与薄膜晶体管t212的源级相连,薄膜晶体管t212的栅极与栅极线g23相连,薄膜晶体管t212的漏极与数据线d24相连。

84.其中,第一像素201、第十像素210以及第十二像素212的电极与薄膜晶体管的源级之间的连接线长度相等,该长度可以为第一长度。第二像素202、第四像素204、第六像素206、第七像素207、第九像素209以及第十一像素211的电极与薄膜晶体管的源级之间的连接线长度相等,该长度可以为第二长度,第二长度大于第一长度。

85.即第一像素201、第十像素210以及第十二像素212的电极与薄膜晶体管的源级之间为短桥连接,第二像素202、第四像素204、第六像素206、第七像素207、第九像素209以及第十一像素211的电极与薄膜晶体管的源级之间为长桥连接。

86.这样,根据上述描述可知,第一类像素包括第一像素201、第二像素202、第九像素209、第十像素210、第十一像素211以及第十二像素212,其对应的侧向电容导致的电压差异是等效的,因此,可以以该第一类像素为基准设置像素结构以减小甚至消除各像素间的电压差异。

87.具体来说,针对第三像素203、第四像素204、第五像素205、第六像素206、第七像素207以及第八像素208,可以采用以下至少一种结构:

88.第一种结构中,根据上述产生侧向电容的原因一,可以设置第三像素203、第五像素205、第八像素208的电极与薄膜晶体管源级之间的连接线与其他像素的电极与薄膜晶体管的源级之间的连接线中较长的连接线的长度相等,即设置为上述第二长度的连接线。这样,可以使得第三像素203、第五像素205、第八像素208的电极与薄膜晶体管之间为长桥连接,即这些电极与栅极线的源级之间的侧向电容为c

gs长

,从而降低像素间的

△

vp差异。

89.第二种结构中,根据上述产生侧向电容的原因二,可以设置第三像素203、第五像素205以及第八像素208的电极与位于其下方的栅极线部分交叠,也就是第三像素203以及第五像素205的电极与位于下方的栅极线g22部分交叠,第八像素208的电极与位于其下方的栅极线g24部分交叠。这样,交叠部分的产生的电容可以作为c

gp

增大补偿,从而降低像素间的

△

vp’差异。

90.第三种结构中,根据上述产生侧向电容的原因三,可以设置第四像素204、第六像素206以及第七像素207的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离,其中,目标像素为电极与栅极线不存在交叠的像素,目标像素可以为第一像素201、第二像素202、第九像素209、第十像素210、第十一像素211以及第十二像素212。这样,第四像素204、第六像素206以及第七像素207的电极与位于其下方的栅极线之间的距离大于目标像素的电极与位于其下方的栅极线之间的距离的部分可以作为c

gp

减小补偿,从而降低像素间的

△

vp’差异。

91.图3中同时示出了上述三种结构,仅仅作为一种可行的示例,并不代表本发明实施例所提供的像素结构必须同时包括上述三种结构,不能作为对本发明实施例所提供的像素结构的限定。

92.由于本发明实施例所提供的第一种像素结构的像素单元包括以上至少一种结构,所以可以通过连接线的长度、电极与栅极线部分交叠和/或电极与栅极线之间的距离来减小甚至消除不同像素的电极之间电容差异,从而减小甚至消除不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,改善因电压差所产生的竖纹,从而改善甚至解决摇头纹的问题。

93.作为本发明实施例的一种实施方式,上述第三像素的电极、第五像素的电极以及第八像素的电极与位于其下方的栅极线交叠部分的电容为第一预设电容。

94.其中,第一预设电容为第二像素的电极与栅极线之间的电容与第一目标电容的差值,第一目标电容为未与栅极线交叠状态下的第三像素的电极与栅极线之间的电容。

95.上述第三像素的电极、第五像素的电极以及第八像素的电极与位于其下方的栅极线交叠部分的具体大小可以根据交叠部分所产生的电容来确定。如果第三像素的电极与栅极线不存在交叠,那么第三像素与第二像素之间由于电极与栅极线之间的电容产生的差异即为需要补偿的电容差异,即第一预设电容。所以可以设置第三像素的电极、第五像素的电极以及第八像素的电极与位于其下方的栅极线交叠部分的电容为第一预设电容。

96.例如,第一目标电容为未与栅极线交叠状态下的第三像素的电极与栅极线之间的电容,即为上述z像素结构中的像素103与栅极线g12之间的侧向电容c

gp自

,其值较小,第二像素的电极与栅极线之间的电容为c

gp自

,其值较大,那么,第一预设电容可以为第二像素的电极与栅极线之间的电容为c

gp自

与像素103与栅极线g12之间的侧向电容c

gp自

之间的差值。

97.可见,在本实施例中,第三像素的电极、第五像素的电极以及第八像素的电极与位于其下方的栅极线交叠部分的电容为第一预设电容,第一预设电容为第二像素的电极与栅极线之间的电容与第一目标电容的差值,第一目标电容为未与栅极线交叠状态下的第三像素的电极与栅极线之间的电容。即通过电极与栅极线部分交叠来补偿不同像素的c

gp

之间的差异,从而减小不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,进一步改善因电压差所产生的竖纹,从而进一步改善摇头纹的问题。

98.作为本发明实施例的一种实施方式,上述第四像素的电极、第六像素的电极以及第七像素的电极与位于其下方的栅极线之间的距离使得第四像素的电极、第六像素的电极以及第七像素的电极与栅极线之间的电容为第二预设电容。

99.其中,第二预设电容为第二目标电容与第二像素的电极与栅极线之间的电容的差值,第二目标电容为与栅极线之间的距离与第二像素的电极与栅极线之间的距离相同的状

态下的第四像素的电极与栅极线之间的电容。

100.上述第四像素的电极、第六像素的电极以及第七像素的电极与位于其下方的栅极线之间的距离的具体值可以根据该距离所产生的电容来确定。如果第四像素的电极、第六像素的电极以及第七像素的电极与位于其下方的栅极线之间的距离与其他像素与位于其下方的栅极线之间的距离相等,而第四像素、第六像素以及第七像素的上下没有设置薄膜晶体管,并且其连接于设置在奇数行的栅极线,则会导致电容c

gp自大

和c

gp他

均较大,会与第四像素的电极与栅极线之间的电容产生电容差异,即第二目标电容。

101.所以为了消除该电容差异,可以设置第四像素的电极、第六像素的电极以及第七像素的电极与位于其下方的栅极线之间的距离使得第四像素的电极、第六像素的电极以及第七像素的电极与栅极线之间的电容为第二预设电容。

102.例如,第二目标电容与栅极线之间的距离与所述第二像素的电极与栅极线之间的距离相同的状态下的第四像素的电极与栅极线之间的电容,即为上述z像素结构中像素104的电极与栅极线g11和栅极线g12之间的电容c

gp自

和c

gp他

。第二像素的电极与栅极线之间的电容为c

gp自

,那么,第二预设电容可以为像素104的电极与栅极线g11和栅极线g12之间的电容c

gp自

和c

gp他

之和,与第二像素的电极与栅极线之间的电容为c

gp自

之间的差值。

103.可见,本实施例中,第四像素的电极、第六像素的电极以及第七像素的电极与位于其下方的栅极线之间的距离使得第四像素的电极、第六像素的电极以及第七像素的电极与栅极线之间的电容为第二预设电容,第二预设电容为第二目标电容与第二像素的电极与栅极线之间的电容的差值,第二目标电容为与栅极线之间的距离与第二像素的电极与栅极线之间的距离相同的状态下的第四像素的电极与栅极线之间的电容。即通过电极与栅极线之间的距离来补偿不同像素之间的c

gp

电容差异,从而进一步减小不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,进一步改善因电压差所产生的竖纹,从而进一步改善摇头纹的问题。

104.作为本发明实施例的一种实施方式,上述第一像素至第十二像素的电极与其上方的栅极线之间的距离可以均相同。这样,可以使各个像素之间的c

gp

电容差异仅受到与其下方栅极线之间的距离的影响,方便准确设置上述第二种和/或第三种结构,进一步保证改善摇头纹的问题的效果。

105.仍然以上述图1所示的目前的z像素结构为例进行说明,假设显示面板的公共电压vcom的大小以上述第二类像素即像素104、像素106以及像素107作为基准,由于上述第二类像素对应的电压差异大于第一类像素对应的电压差异,上述第三类像素对应的电压差异小于第一类像素对应的电压差异,那么,其会导致显示画面的效果如图4所示。正帧时,像素101正极性偏亮,像素102正极性偏亮,像素103负极性暗,像素104负极性正常,像素105正极性亮,像素106正极性正常,像素107负极性正常,像素108负极性暗,像素109正极性偏亮,像素110正极性偏亮,像素111负极性偏暗,像素112负极性偏暗。

106.负帧时,像素101负极性偏暗,像素102负极性偏暗,像素103正极性亮,像素104正极性正常,像素105负极性暗,像素106负极性正常,像素107正极性正常,像素108正极性亮,像素109负极性偏暗,像素110负极性偏暗,像素111正极性偏亮,像素112正极性偏亮。以此类推,正帧时产生亮暗交替竖纹,负帧时产生暗亮交替竖纹,该竖纹正负帧可抵消,但是用户摆头观看时会产生摇头纹。

107.针对上述情况,基于与上述第一种双栅驱动的像素结构同样的发明构思,从上述导致摇头纹的三个原因出发,本发明实施例还提供了另一种双栅驱动的像素结构进行介绍。下面对本发明实施例所提供的第二种双栅驱动的像素结构进行介绍。

108.如图5所示,一种双栅驱动的像素结构,所述像素结构包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:

109.所述四条栅极线g31

‑

g34平行设置,所述四条数据线d31

‑

d34垂直于所述栅极线设置,限定出排列为两行的所述六个像素区31

‑

36,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管;

110.所述两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素301至第六像素306,第二行包括第七像素307至第十二像素312,每个像素区包括的两个像素的像素电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线;

111.所述第一像素301、第四像素304、第六像素306、第七像素307、第十像素310以及第十二像素312的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管;

112.所述像素结构包括结构:所述第一像素301至所述第十二像素312的电极与薄膜晶体管的源级之间的连接线的长度均相等;和/或,

113.所述第一像素301、所述第二像素302、所述第三像素303、所述第五像素305、所述第八像素308、所述第九像素309、所述第十像素310、所述第十一像素311以及所述第十二像素312的电极与其连接的薄膜晶体管所在的栅极线部分交叠。

114.可见,本发明实施例提供的像素结构中,包括多个像素单元,每个像素单元包括四条栅极线、四条数据线和六个像素区,其中:四条栅极线平行设置,四条数据线垂直于栅极线设置,限定出排列为两行的六个像素区,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管,两个薄膜晶体管的漏极连接于同一条数据线,每个像素区包括两个平行于栅极线设置的像素,第一行包括第一像素至第六像素,第二行包括第七像素至第十二像素,每个像素区包括的两个像素的电极分别连接一个薄膜晶体管的源级,垂直的两个像素区连接于不同的数据线,第一像素、第四像素、第六像素、第七像素、第十像素以及第十二像素的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管,像素结构包括结构:第一像素至第十二像素的电极与薄膜晶体管的源级之间的连接线的长度均相等;和/或,第一像素、第二像素、第三像素、第五像素、第八像素、第九像素、第十像素、第十一像素以及第十二像素的电极与其连接的薄膜晶体管所在的栅极线部分交叠。由于像素结构中包括以上至少一种结构,所以可以通过连接线的长度和/或电极与栅极线部分交叠减小甚至消除不同像素的电极之间电容差异,从而减小甚至消除不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,改善因电压差所产生的竖纹,从而改善甚至解决摇头纹的问题。

115.本发明实施例所提供的第二种双栅驱动的像素结构包括多个像素单元,每个像素单元,包括栅极线g31

‑

栅极线g34、数据线d31

‑

数据线d34以及六个像素区,即像素区31、像素区32、像素区33、像素区34、像素区35以及像素区36。

116.四条栅极线平行设置,其中,栅极线g31与栅极线g32之间的距离与栅极线g33与栅

极线g34之间的距离相等,栅极线g32与栅极线g33相邻设置,数据线d31、数据线d32、数据线d33以及数据线d34垂直于栅极线依次设置,且相邻数据线之间的距离相等,这样,限定出排列为两行的六个像素区。

117.第一行像素区包括像素区31、像素区32以及像素区33,第二行像素区包括像素区34、像素区35以及像素区36。像素区31与像素区34构成第一列像素区,像素区32与像素区35构成第二列像素区,像素区33与像素区36构成第三列像素区。

118.每个像素区包括两个平行于栅极线设置的像素,每个像素区对应的两条栅极线上设置有上下位置对应的两个薄膜晶体管。该两个薄膜晶体管的漏极连接于同一条数据线,垂直的两个像素区连接于不同的数据线,即垂直的两个像素区对应的薄膜晶体管连接于不同的数据线。即第一像素301、第四像素304、第六像素306、第七像素307、第十像素310以及第十二像素312的电极连接于设置在奇数行栅极线上的薄膜晶体管,其余像素的电极连接于设置在偶数行栅极线上的薄膜晶体管。其中,奇数行栅极线即为栅极线g31和栅极线g33,偶数行栅极线即为栅极线g32和栅极线g34。

119.像素区31、像素区32、像素区33、像素区34、像素区35以及像素区36,其中像素的设置以及与薄膜晶体管连接方式分别与上述第一种像素结构中的像素区21、像素区22、像素区23、像素区24、像素区25以及像素区26类似,在此不再赘述。下面主要描述与上述第一种像素结构的不同之处。

120.第二种双栅驱动的像素结构中,第二像素302、第四像素304、第六像素306、第七像素707、第九像素209以及第十一像素211的电极与薄膜晶体管的源级之间的连接线长度相等,均为长桥连接。

121.这样,根据上述描述可知,第二类像素包括第四像素304、第六像素306以及第七像素307,其对应的侧向电容导致的电压差异是等效的,因此,可以以该第二类像素为基准设置像素结构以减小甚至消除各像素间的电压差异。

122.具体来说,针对第一像素301、第二像素302、第三像素303、第五像素305、第八像素308、第九像素309、第十像素310、第十一像素311以及第十二像素312,可以采用以下至少一种结构:

123.第一种结构中,根据上述产生侧向电容的原因一,可以设置第一像素301至第十二像素312的电极与薄膜晶体管的源级之间的连接线的长度均相等,即均为长桥连接,即这些电极与栅极线的源级之间的侧向电容为c

gs长

,从而降低像素间的

△

vp差异。

124.第二种结构中,根据上述产生侧向电容的原因二和原因三,可以设置第一像素301、第二像素302、第三像素303、第五像素305、第八像素308、第九像素309、第十像素310、第十一像素311以及第十二像素312的电极与其连接的薄膜晶体管所在的栅极线部分交叠,这样,交叠部分的产生的电容可以作为c

gp

增大补偿,从而降低像素间的

△

vp’差异。

125.图5中同时示出了上述两种结构,仅仅作为一种可行的示例,并不代表本发明实施例所提供的像素结构必须同时包括上述两种结构,不能作为对本发明实施例所提供的像素结构的限定。

126.由于本发明实施例所提供的第二种像素结构的像素单元包括以上至少一种结构,所以可以通过连接线的长度和/或电极与栅极线部分交叠减小甚至消除不同像素的电极之间电容差异,从而减小甚至消除不同像素的电极之间的电压差,进而使显示面板中不同像

素之间的电容差异得到平均,改善因电压差所产生的竖纹,从而改善甚至解决摇头纹的问题。

127.作为本发明实施例的一种实施方式,上述第一像素、第二像素、第三像素、第五像素、第八像素、第九像素、第十像素、第十一像素以及第十二像素的电极与其连接的薄膜晶体管所在的栅极线交叠部分的电容为第三预设电容。

128.其中,第三预设电容为第四像素的电极与栅极线之间的电容与第三目标电容的差值,第三目标电容为未与栅极线交叠状态下的第一像素的电极与栅极线之间的电容。

129.例如,第三目标电容为未与栅极线交叠状态下的第一像素的电极与栅极线之间的电容,即为上述z像素结构中像素101电极与栅极线g11和栅极线g12之间的电容c

gp自

和c

gp他

,二者均较小。第四像素的电极与栅极线之间的电容为c

gp自

和c

gp他

,二者均较大。那么,第三预设电容可以为第四像素的电极与栅极线之间的电容为c

gp自

和c

gp他

之和,与像素101电极与栅极线g11和栅极线g12之间的电容c

gp自

和c

gp他

之和的差值。

130.可见,在本实施例中,第一像素、第二像素、第三像素、第五像素、第八像素、第九像素、第十像素、第十一像素以及第十二像素的电极与其连接的薄膜晶体管所在的栅极线交叠部分的电容为第三预设电容,第三预设电容为第四像素的电极与栅极线之间的电容与第三目标电容的差值,第三目标电容为未与栅极线交叠状态下的第一像素的电极与栅极线之间的电容。即通过电极与栅极线部分交叠来补偿不同像素的c

gp

之间的差异,从而减小不同像素的电极之间的电压差,进而使显示面板中不同像素之间的电容差异得到平均,进一步改善因电压差所产生的竖纹,从而进一步改善摇头纹的问题。

131.作为本发明实施例的一种实施方式,上述第一像素至所述第十二像素的未与栅极线交叠一侧的电极与其临近的栅极线之间的距离可以均相同。这样,可以使各个像素之间的c

gp

电容差异仅受到与交叠的栅极线之间的距离的影响,方便准确设置上述第二种结构,进一步保证改善摇头纹的问题的效果。

132.采用上述第一种双栅驱动的像素结构以及上述第二种双栅驱动的像素结构的显示面板所显示画面的效果如图6所示,正帧和负帧时,各个像素的侧向电容差异较小甚至不存在差异,电压差异较小甚至不存在差异,所以不同像素之间的电容差异得到平均,减轻甚至消除了因电压差异所产生的竖纹,从而减轻甚至解决了摇头纹的问题。

133.图7为目前的z像素结构与本发明实施例所提供的像素结构的一种对比示意图,其中,目前的z像素结构710中,像素的电极711与栅极线712上的薄膜晶体管713之间为短桥连接714;像素的电极711与栅极线712不存在交叠部分。本发明实施例所提供的像素结构720中,像素的电极721与栅极线722上的薄膜晶体管723之间为长桥连接724;像素的电极721与栅极线722存在交叠部分725。本发明实施例所提供的像素结构730中,像素的电极731与栅极线732之间的距离小于目前的z像素结构710中像素的电极711与栅极线712之间的距离。

134.需要说明的是,图7仅仅是为了说明本发明实施例所提供的像素结构与目前的z像素结构可以存在的不同之处,并不代表本发明实施例所提供的像素结构中的每个像素都具有图7所示的结构,具体像素单元中哪些像素具有何种结构参见上述实施例中的详细说明。

135.相应于上述第一种双栅驱动的像素结构,本发明实施例提供了第一种双栅驱动的显示面板,所述显示面板包括上述任一实施例所述的第一种双栅驱动的像素结构。

136.相应于上述第二种双栅驱动的像素结构,本发明实施例提供了第二种双栅驱动的

显示面板,所述显示面板包括上述任一实施例所述的第二种双栅驱动的像素结构。

137.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

138.本说明书中的各个实施例均采用相关的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。

139.以上所述仅为本发明的较佳实施例,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1