一种非晶材料片上波导的高稳定性耦合封装方法

1.本发明涉及光子集成器件耦合封装的技术领域,更具体地,涉及一种非晶材料片上波导的高稳定性耦合封装方法。

背景技术:

2.近年来,敏感功能材料的研制开发所呈现的主要趋势之一是从单晶材料向多晶材料和非晶材料的方向过度发展。非晶材料的组成原子、分子的空间排列不呈周期性和平移对称性,无规则排列。无机非晶材料与单晶材料相比,在加工和集成过程中有明显优势,并且可以在不受晶格匹配约束的聚合物衬底上直接生长,目前用来制备光子器件的无机非晶材料包括非晶硅(a-si)、氮化硅(si3n4)、氧化物(如tio2)、玻璃等,将光子器件小型化集成在特殊的衬底材料(如一些有机衬底)上可形成光子芯片。

3.当前,伴随着芯片相关产业发展的迫切需要,为解决芯片产业发展面临的各方面“卡脖子”问题,迎接芯片产业发展的机遇,加强芯片在基础方面的建设至关重要,然而,芯片涉及到的基础问题较多,有材料、工艺、设备,涉及比较长的产业链。芯片要从实验室走出去,走进千家万户的生活中,开发一种稳定的芯片耦合封装技术显得尤为重要。

4.由于芯片是微型化的器件,其中的光波导的几何尺寸也是非常小的。因此,光纤纤芯与芯片波导尺寸的差距会引起较为严重的模场不匹配,给耦合带来较大的插损。现有技术中公开了一种硅纳米光波导与光纤的耦合封装方法,利用倒锥型模斑转换器实现硅纳米光波导中的小尺寸模斑向光纤的大尺寸模斑转换,并利用v型光纤定位槽的自对准特性实现硅纳米光波导与光纤的对准耦合与简便封装,实现了波导与光纤的精确中心对准与高效光耦合,光纤的固定封装工艺简便,但该方案仅考虑了波导与光纤的对准,对波导而言,在对其耦合封装时,输出端与输入端的耦合均应考虑,而每一个端的耦合都涉及到模场大小不匹配的问题,可能产生耦合插损,而且稳定性差,插损随环境变化的波动性较大,这不利于波导芯片成品的应用,另外,通常芯片的商业化需采用1550nm的通信窗口,在1550nm的通信线路上,很多器件采用单模光纤作为输入、输出,为了满足产品的普遍适配性,若耦合时通常选用多模光纤,可能涉及多模光纤到单模光纤的转换,这时,耦合稳定性因光纤转换可能遭受到极大的不利影响。

技术实现要素:

5.为解决当前非晶材料片上波导在耦合封装过程中面临的耦合插损高及稳定性差的问题,本发明提出一种非晶材料片上波导的高稳定性耦合封装方法,实现了高效率、低损耗的耦合封装,提高了耦合封装的稳定性。

6.为了达到上述技术效果,本发明的技术方案如下:

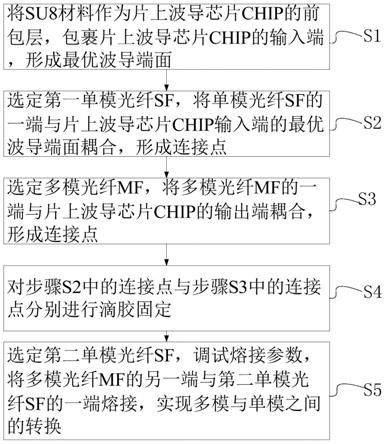

7.一种非晶材料片上波导的高稳定性耦合封装方法,包括以下步骤:

8.s1.将su8材料作为片上波导芯片chip的前包层,包裹片上波导芯片chip的输入端,形成最优波导端面;

9.s2.选定第一单模光纤sf,将单模光纤sf的一端与片上波导芯片chip输入端的最优波导端面耦合,形成连接点;

10.s3.选定多模光纤mf,将多模光纤mf的一端与片上波导芯片chip的输出端耦合,形成连接点;

11.s4.对步骤s2中的连接点与步骤s3中的连接点分别进行滴胶固定;

12.s5.选定第二单模光纤sf,调试熔接参数,将多模光纤mf的另一端与第二单模光纤sf的一端熔接,实现多模与单模之间的转换。

13.在本技术方案中,考虑单模光纤的模场尺寸与片上波导芯片chip的模场尺寸之间的差距较大,为降低耦合插损,通过波导端面改造片上波导芯片chip的波导结构来改变光波传播的模场,以实现不同直径模场的匹配,然后滴胶固定,提升抗扰动的稳定性,并且在片上波导芯片chip的输出端采用多模光纤进行接收,可以实现较高的耦合稳定性,为提高耦合封装方法的适配性与可用性,以降低单模光纤与多模光纤熔接插损为出发点,对光纤熔接参数调试设置,将多模光纤再与单模光纤进行熔接,实现多模与单模之间的转换,在确保插损小、普适性的前提下为提高光子集成器件耦合封装稳定性提供了解决思路。

14.优选地,所述的片上波导芯片chip是以sio2为衬底,尾端呈锥形的硫系波导,尾端与衬底边缘的距离至少为100um,为模场放大提供足够的距离。

15.优选地,步骤s1中所述的最优波导端面通过fdtd仿真软件的模拟计算和对实际成品的对比测试得出,引入片上波导耦合封装系统,所述片上波导耦合封装系统包括依次相连的激光器、功率衰减器、偏振控制器、片上波导芯片chip,所述激光器作为输出光源,功率衰减器用于防止光功率过载,同时调节光功率的大小,偏振控制器控制片上波导芯片chip内的偏振态,确保光功率损耗最低。

16.优选地,步骤s2所述将单模光纤sf的一端与片上波导芯片chip输入端的最优波导端面耦合的过程为:

17.s21.在减震台的耦合平台上,将单模光纤sf的中心与片上波导芯片chip的中心对准;

18.s22.打开激光器通光,并使用功率衰减器调节光功率;

19.s23.明确片上波导芯片chip耦合封装后的最终输出端,在最终输出端接入光功率计;

20.s24.调节耦合平台的位置调节旋钮,观察光功率计显示的光功率变化,确定最佳耦合位置并进行耦合。

21.优选地,步骤s3所述将多模光纤mf的一端与片上波导芯片chip的输出端耦合的过程为:

22.s31.在减震台的耦合平台上,将多模光纤mf的中心与片上波导芯片chip的中心对准;

23.s32.打开激光器通光,并使用功率衰减器调节光功率;

24.s33.预先明确片上波导芯片chip耦合封装后的输出端,在输出端接入光功率计;

25.s34.调节耦合平台的位置调节旋钮,观察光功率计显示的光功率变化,确定最佳耦合位置并进行耦合。

26.在此,相比于输入端,输出端是小模场与大模场进行匹配,所以光功率的损耗会较

小,可以直接用多模光纤与波导进行耦合,但由于波导尺寸较小,光纤纤芯与波导稍微有些许偏离则会给耦合带来巨大的插损,在减震台的耦合平台上进行耦合,有利于保证耦合效果。

27.优选地,对步骤s2中的连接点与步骤s3中的连接点分别进行滴胶固定时,胶水选用紫外固化胶noa61,热膨胀系数小,可以显著提高封装的稳定性,确保固化胶的热膨胀不会给耦合光纤的纤芯带来大的偏移,提升其抗扰动的稳定性。

28.优选地,对步骤s2中的连接点进行滴胶固定或对步骤s3中的连接点进行滴胶固定的过程为:

29.s41.利用点胶机将胶水点至连接点,然后利用365nm的紫外固化灯5mw固化30秒,熄灭紫外固化灯,等待5分钟,直至光功率计显示的光功率稳定,执行步骤s42;

30.s42.利用点胶机将胶水点至连接点,然后利用365nm的紫外固化灯1mw固化120秒,熄灭紫外固化灯,等待光功率计显示的光功率稳定,执行步骤s43;

31.s43.利用365nm的紫外固化灯1mw固化120秒;

32.s44.将步骤s41~s43执行3~5次,直至胶水完全固化。

33.优选地,步骤s5所述的将多模光纤mf的另一端与第二单模光纤sf的一端熔接的过程为:

34.s51.将多模光纤mf和第二单模光纤sf均剥去保护套和涂覆层;

35.s52.调节设置多模光纤mf待熔接端与第二单模光纤sf待熔接端之间的距离;调节设置熔接机的熔接参数;

36.s53.将多模光纤mf与第二单模光纤sf按设置的距离放入熔接机各自对应的刻槽固定;

37.s54.在多模光纤mf的端面与第二单模光纤sf的端面均平整且对齐时,进行放电清灰操作;

38.s55.放电清灰完成后,开始熔接。

39.优选地,步骤s52中,调节设置的多模光纤mf待熔接端与第二单模光纤sf待熔接端之间的距离为22um;

40.调节设置的熔接机的熔接参数为:放电强度为20,放电时间为200-240ms,切割角度门限为20.0deg,清洁放电强度20,清洁放电时间200-240ms,预熔时间为160ms,熔接机推进类型两侧光纤,z轴推进量15um,左侧光纤mfr为4.65um,右侧光纤mfr4.6um,纤芯门限值0.20um。

41.优选地,步骤s5之后还包括对耦合封装后的片上波导芯片chip进行热稳定性测试,在热稳定性测试中,逐渐升高或降低温度,观察耦合封装后的光功率损耗变化。

42.与现有技术相比,本发明技术方案的有益效果是:

43.本发明提出一种非晶材料片上波导的高稳定性耦合封装方法,通过波导端面改造片上波导芯片chip的波导结构来改变光波传播的模场,以实现不同直径模场的匹配,然后滴胶固定,提升耦合封装成品抗扰动的稳定性,并且在片上波导芯片chip的输出端采用多模光纤进行接收,可以实现较高的耦合稳定性。另外,为提高耦合封装方法的适配性与可用性,以降低单模光纤与多模光纤熔接插损为出发点,对光纤熔接参数调试设置,将多模光纤再与单模光纤进行熔接,实现多模与单模之间的转换,在确保插损小、普适性的前提下为提

高光子集成器件耦合封装稳定性提供了解决思路。

附图说明

44.图1表示本发明实施例1中提出的非晶材料片上波导的高稳定性耦合封装方法的流程示意图;

45.图2表示本发明实施例1中提出的非晶材料片上波导的高稳定性耦合封装过程模拟系统结构示意图;

46.图3表示本发明实施例3中提出的在使用传统耦合封装技术下,耦合封装后的片上波导芯片chip进行热稳定性测试时,光功率损耗随温度变化的曲线图;

47.图4表示本发明实施例3中提出的使用本发明所提出的方法,耦合封装后的片上波导芯片chip进行热稳定性测试时,光功率损耗随温度变化的曲线图。

具体实施方式

48.附图仅用于示例性说明,不能理解为对本专利的限制;

49.为了更好地说明本实施例,附图某些部位会有省略、放大或缩小,并不代表实际尺寸;

50.对于本领域技术人员来说,附图中某些公知内容说明可能省略是可以理解的。

51.附图中描述位置关系的仅用于示例性说明,不能理解为对本专利的限制;

52.下面结合附图和实施例对本发明的技术方案做进一步的说明。

53.实施例1

54.对片上波导芯片chip而言,在对其耦合封装时,输出端的耦合与输入端的耦合均应考虑,而每一个端的耦合都涉及到模场大小不匹配的问题,可能产生耦合插损,而且稳定性差,插损随环境变化的波动性较大,这不利于波导芯片成品的应用,另外,很多器件采用单模光纤作为输入输出,为了满足产品的普遍适配性,最终输出端应为单模光纤,对耦合时通常选用多模光纤而言,可能涉及多模光纤到单模光纤的转换,这时,耦合稳定性因光纤转换可能遭受到极大的不利影响。

55.为解决以上问题,在本实施例中提出了一种非晶材料片上波导的高稳定性耦合封装方法,考虑单模光纤的模场尺寸与片上波导芯片chip的模场尺寸之间的差距较大的问题,为降低耦合插损,通过波导端面改造,改善片上波导芯片chip的波导结构,来改变光波传播的模场,以实现不同直径模场的匹配,然后滴胶固定,提升耦合封装成品抗扰动的稳定性,并且在片上波导芯片chip的输出端采用多模光纤进行接收,可以实现较高的耦合稳定性,为提高耦合封装方法的适配性与可用性,以降低单模光纤与多模光纤熔接插损为出发点,对光纤熔接参数调试设置,将多模光纤再与单模光纤进行熔接,实现多模与单模之间的转换,整体上,该方法的流程图如图1所示,参见图1,包括以下步骤:

56.s1.将su8材料作为片上波导芯片chip的前包层,包裹片上波导芯片chip的输入端,形成最优波导端面;

57.在本实施例中,片上波导芯片chip采用的是geasse,以su8材料作为片上波导芯片chip的前包层,是为步骤s2中选用第一单模光纤sf与片上波导芯片chip相耦合做准备,由于单模光纤的模场与波导模场的尺寸相差较大,通过这种端面改造设计,以进行模场匹配,

形成的最优波导端面截面为2.4*2.4um2的矩形,长度大于(200+尖端长度)um。

58.s2.选定第一单模光纤sf,将单模光纤sf的一端与片上波导芯片chip输入端的最优波导端面耦合,形成连接点;

59.s3.选定多模光纤mf,将多模光纤mf的一端与片上波导芯片chip的输出端耦合,形成连接点;

60.s4.对步骤s2中的连接点与步骤s3中的连接点分别进行滴胶固定;

61.s5.选定第二单模光纤sf,调试熔接参数,将多模光纤mf的另一端与第二单模光纤sf的一端熔接,实现多模与单模之间的转换。

62.在本实施例中,最优波导端面通过fdtd仿真软件的模拟计算和对实际成品的对比测试得出,引入片上波导耦合封装系统,参见图2,非晶材料片上波导的高稳定性耦合封装过程的模拟系统结构包括依次相连的激光器laser、功率衰减器voa、偏振控制器pc、片上波导芯片chip,其中,激光器laser作为输出光源,功率衰减器voa用于防止光功率过载,同时调节光功率的大小,偏振控制器pc控制片上波导芯片chip内的偏振态,确保光功率损耗最低,fuse代表熔接示意。

63.进一步结合图2,图2中的(a)表示将单模光纤sf的一端与片上波导芯片chip输入端的最优波导端面(已由su8材料作为前包层改造)耦合的过程,参见图2,所述的片上波导芯片chip是以sio2为衬底,尾端呈锥形的硫系波导,尾端与衬底边缘的距离至少为100um,从而为模场放大提供足够距离,在本实施例中,尾端与衬底边缘的距离设置100um。

64.虽然已进行了波导端面的改造,但对于整个耦合,稍有偏离也会造成巨大的插损,因此,为保证耦合过程的严谨性,本实施例中采用的耦合过程具体为:

65.s21.在减震台的耦合平台上,将单模光纤sf的中心与片上波导芯片chip的中心对准;

66.s22.打开激光器laser通光,并使用功率衰减器voa调节光功率;

67.s23.明确片上波导芯片chip耦合封装后的最终输出端,在最终输出端接入光功率计;此步骤是为了通过光功率计显示光功率的变化,然后便于步骤s23进行位置调节,以选择最佳耦合位置。

68.s24.调节耦合平台的位置调节旋钮,观察光功率计显示的光功率变化,确定最佳耦合位置并进行耦合。这里涉及到将人工观察光功率变化的波动小、稳定时对应耦合平台的旋钮位置,将光功率稳定、且在最大值时的耦合位置作为最佳耦合位置,这时耦合效率最高。

69.片上波导芯片chip的输出端是小模场与大模场进行匹配,所以光功率的损耗会较小,可以直接用多模光纤与波导进行耦合,但由于波导尺寸较小,光纤纤芯与波导稍微有些许偏离则会给耦合带来巨大的插损,在减震台的耦合平台上进行耦合,有利于保证耦合效果,同样的,在本实施例中,结合图2,图2中的(b)表示将多模光纤mf的一端与片上波导芯片chip的输出端耦合的过程,过程为:

70.s31.在减震台的耦合平台上,将多模光纤mf的中心与片上波导芯片chip的中心对准;

71.s32.打开激光器通光,并使用功率衰减器调节光功率;

72.s33.预先明确片上波导芯片chip耦合封装后的输出端,在输出端接入光功率计;

73.s34.调节耦合平台的位置调节旋钮,观察光功率计显示的光功率变化,确定最佳耦合位置并进行耦合。

74.在本实施例中,片上波导芯片chip的输入端与输出端均初步耦合之后,形成各自的连接点,对于步骤s2中的连接点与步骤s3中的连接点分别进行滴胶固定时,胶水选用紫外固化胶noa61,热膨胀系数小,可以显著提高封装的稳定性,确保固化胶的热膨胀不会给耦合光纤的纤芯带来大的偏移,提升其抗扰动的稳定性。

75.对步骤s2中的连接点进行滴胶固定或对步骤s3中的连接点进行滴胶固定的过程为:

76.s41.利用点胶机将胶水点至连接点,然后利用365nm的紫外固化灯5mw固化30秒,熄灭紫外固化灯,等待5分钟,直至光功率计显示的光功率稳定,执行步骤s42;

77.此步骤中,在具体操作时,点胶水的大小大概是一个芝麻大小,点到芯片与光纤的连接点上,光功率稳定是指光功率计显示的光功率在较小范围内波动,

±

0.02dbm即算稳定,光功率计精度比较高,所以轻微的扰动也会带来一定影响,不会完全稳稳地定在某个确切的值。

78.s42.利用点胶机将胶水点至连接点,然后利用365nm的紫外固化灯1mw固化120秒,熄灭紫外固化灯,等待光功率计显示的光功率稳定,执行步骤s43;

79.此步骤中,在具体操作时,点胶水的大小比步骤s41中大一些,大概是一个绿豆大小,再一次点到芯片与光纤的连接点上。

80.s43.利用365nm的紫外固化灯1mw固化120秒;

81.s44.将步骤s41~s43执行3~5次,直至胶水完全固化。

82.实施例2

83.在本实施例中,在实施例1中片上波导芯片chip的输入端与输出端均已进行耦合并且滴胶固定的前提下,鉴于在1550nm通信波长系统中的大多数器件都是单模输入输出的,所以为保证这一耦合封装方法的适配性和可用性,将输出的多模光纤与单模光纤进行熔接,以实现多模转单模。

84.具体的涉及到步骤s5,步骤s5中将多模光纤mf的另一端与第二单模光纤sf的一端熔接的过程为:

85.s51.将多模光纤mf和第二单模光纤sf均剥去保护套和涂覆层;

86.s52.调节设置多模光纤mf待熔接端与第二单模光纤sf待熔接端之间的距离;调节设置熔接机的熔接参数;

87.s53.将多模光纤mf与第二单模光纤sf按设置的距离放入熔接机各自对应的刻槽固定;

88.s54.在多模光纤mf的端面与第二单模光纤sf的端面均平整且对齐时,进行放电清灰操作;

89.s55.放电清灰完成后,开始熔接。

90.步骤s52中,调节设置的多模光纤mf待熔接端与第二单模光纤sf待熔接端之间的距离为22um;

91.调节设置的熔接机的熔接参数为:放电强度为20,放电时间为200-240ms,切割角度门限为20.0deg,清洁放电强度20,清洁放电时间200-240ms,预熔时间为160ms,熔接机推

进类型两侧光纤,z轴推进量15um,左侧光纤mfr为4.65um,右侧光纤mfr4.6um,纤芯门限值0.20um。

92.实施例3

93.在本实施例中,步骤s5之后还包括对耦合封装后的片上波导芯片chip进行热稳定性测试,在热稳定性测试中,逐渐升高或降低温度,观察耦合封装后的光功率损耗变化,本实施例中的热稳定性测试采用的是使用本发明所提出的方法与使用传统耦合封装技术进行对比的方式,图3表示在使用传统耦合封装技术下,耦合封装后的片上波导芯片chip进行热稳定性测试时,光功率损耗随温度变化的曲线图;图4表示使用本发明所提出的方法下,耦合封装后的片上波导芯片chip进行热稳定性测试时,光功率损耗随温度变化的曲线图,在图3和图4中,横坐标均表示温度变化,纵坐标均表示光功率损耗。

94.如图3所示,在使用传统耦合封装技术时,对两天中加热(day1-heat up/day2-heat up)和冷却(day1-cooling/day2-cooling)下光功率损耗随温度的变化进行考量,为区分曲线情况,图3中“一”所指的曲线表示day1-heat up对应的曲线,

“◇”

所在的曲线表示day2-heat up对应的曲线,纯粹的

“※”

趋势曲边表示day1-cooling对应的曲线,连线型

“※”

曲线表示day2-cooling对应的曲线;由图3可得,无论在第一天还是第二天,随着加热或者冷却,使用传统耦合封装技术下耦合封装后的片上波导芯片chip的光功率损耗会有一个上升,然后骤然降低,损耗从最高点至最低点的波动范围较大,很不稳定。为提高说服力,图4对应的是三天的加热(day1-heat up/day2-heat up/day3-heat up)和冷却(day1-cooling/day2-cooling/day3-cooling)下光功率损耗随温度的变化进行考量,在运用本发明所提方法时,可以发现,无论是加热或冷却,而且几天数据统计下,片上波导芯片chip的光功率损耗没有大的波动,最高点与最低点之间的差距稳定,无论温度如何变化,所有温度对应单一曲线中,光功率损耗基本稳定在2dbm,因此,也可以得出本发明所提出的耦合封装方法稳定性较高。

95.显然,本发明的上述实施例仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1