一种基于二氧化硅光波导的三维边缘耦合器

1.本发明属于集成光电子学技术领域,具体涉及一种基于二氧化硅光波导的三维边缘耦合器。该三维边缘耦合器用于集成光子芯片与光纤的耦合连接,实现单模光纤与二氧化硅波导间的光信号耦合。该器件在光通信、高性能计算机、光学传感等领域具有重要的应用价值和发展前景。

背景技术:

2.光子芯片可应用于通信网络、数据中心及光计算等领域。在光子学中,功能集成可通过将不同功能元件制作在同一衬底,实现多个单一器件组合所具备的功能,例如将光学组件(波导、光学开关、边缘耦合器、偏振片等)与电学组件(场效应晶体管等)集成,实现光电收发器等功能。光集成芯片的重要指标之一就是光损耗,解决集成光子芯片波导与光纤之间耦合损耗问题,降低由于模场失配导致的光泄露,提高光纤与波导耦合效率,是实现高密度高性能光集成的关键技术。

3.边缘耦合器通常用于光纤与光子芯片上光波导的连接耦合。波导器件与光纤结构尺寸相差较大,模场大小及分布不同,所引起的耦合损耗成为光网络损耗的主要因素。该边缘耦合器包括一段小尺寸芯层波导,其波导截面面积小于光纤模场大小,这会导致光纤与边缘耦合器二氧化硅光波导芯层之间的耦合能量损失,耦合效率降低导致的损耗增大。

4.边缘耦合器需改进波导材料、结构及制造方法等在内的相关内容,通过优化光纤与波导模场匹配,减少模式失配导致的光损耗,同时增大对准容差,降低成本和工艺难度。

5.在过去几十年的研究中,基于二氧化硅材料的集成光学器件取得了巨大进步。二氧化硅材料具有低损耗、高工艺容差、cmos工艺兼容及同单模光纤模场匹配好等优点,在光通信、光互连和集成光学中得到了广泛的应用。

技术实现要素:

6.本发明的目的是提供一种耦合效率高、结构紧凑利于集成、易于封装、层间对准容差大、耦合效率随波长变化不敏感的基于二氧化硅光波导的三维边缘耦合器。

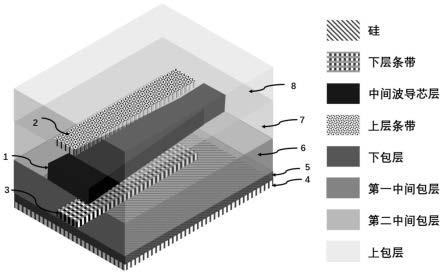

7.本发明所述的一种基于二氧化硅光波导的三维边缘耦合器,其特征在于:如图1和图2(a)所示,从下至上依次由基底层(4)、下包层(5)、下层条带(3)、第一中间包层(6)、中间波导芯层(1)、第二中间包层(7)、上层条带(2)和上包层(8)组成,下层条带(3)位于下包层(5)之上且被包覆在第一中间包层(6)之中,中间波导芯层(1)位于第一中间包层(6)之上且被包覆在第二中间包层(7)之中,上层条带(2)位于第二中间包层(7)之上且被包覆在上包层(8)之中;下层条带(3)与上层条带(2)的结构与尺寸完全相同,在与光传输方向垂直的截面上,下层条带(3)、上层条带(2)与中间波导芯层(1)垂直对准,中心位置偏移量为-3μm~3μm;下包层(5)、第一中间包层(6)、第二中间包层(7)、上包层(8)的材料均为低折射率的二氧化硅,其折射率为1.445;下层条带(3)、中间波导芯层(1)、上层条带(2)的材料均为高折射率的二氧化硅,折射率均为1.481;基底层(4)为硅,折射率为3.455。

8.如图2(b)和图2(c)所示,中间波导芯层(1)由锥形耦合波导core1和输出波导core2构成;core1为宽度线性变窄的锥形结构波导,输入端宽度w1=8μm,输出端宽度w2=3.5μm,厚度h1=3.5μm,长度l1=95μm;core2为矩形结构直波导,输入端和输出端宽度相同为w2=3.5μm,厚度h1=3.5μm,长度l2=20μm;下层条带(3)和上层条带(2)为结构尺寸相同的矩形结构直波导,两者相对于中间波导芯层(1)对称设置,下层条带(3)位于中间波导芯层(1)的正下方,上层条带(2)位于中间波导芯层(1)的正上方;下层条带(3)和上层条带(2)输入端和输出端宽度相同为w3=3.5μm,厚度h2=1.5μm,长度l3=97μm;下层条带(3)与中间波导芯层(1)之间、上层条带(2)与中间波导芯层(1)之间的二氧化硅中间层的厚度gap=0.8μm。

9.该三维边缘耦合器的工作原理如下:

10.1、波导器件与光纤的耦合效率是指光纤中信号光通过光纤波导耦合器耦合进入波导中的能量占光纤中信号光能量的比例。光纤与二氧化硅光波导的耦合损耗包括波导-光纤因结构、尺寸不同导致的模式失配损耗,以及光泄露产生的泄露光损耗。当光纤中传输的信号光自中心波导芯层(1)输入,进入宽度线性变窄的耦合波导core1,根据光模式耦合原理,二氧化硅光波导宽度变窄会导致其所支持光模场尺寸随之下降,即光模场随耦合波导core1的宽度变窄而被逐渐压缩,从高斯分布的圆锥形光纤模场逐渐过渡到到厄米-高斯分布的椭圆形波导模场,并自输出波导core2输出,该渐变波导结构可有效降低模式失配损耗。

11.2、当上层条带(2)和下层条带(3)折射率相同或折射率差较小时,如上层条带(2)和下层条带(3)与中心波导芯层(1)沿光传输方向平行排列时,中心波导芯层(1)泄露的光信号会耦合至上层条带(2)和下层条带(3),经一段距离传输后,光场能量可由上层条带(2)和下层条带(3)耦合回中心波导芯层(1)中,从而抑制中心波导芯层(1)由于光泄露导致的损耗,满足高耦合效率的要求。

12.本发明所述的一种制备方法,包括:形成中间波导芯层;形成位于该中间波导芯层上方和下方的条带边缘耦合器(即上层条带(2)和下层条带(3));形成中间包层、下包层和上包层。

13.与现有器件相比,本发明的有益效果是:相比于传统的锥型模斑转换器,本发明所述三维耦合器上、下两个条带可阻止垂直于光传播方向上的光泄露,并且尺寸较小,利于集成与封装。在实现光纤-波导耦合的不同结构中,该结构耦合效率高、层间对准容差大,且波长不敏感,符合本发明技术要求,具有广泛的应用前景。

附图说明

14.图1是本发明所述的基于二氧化硅光波导的三维边缘耦合器结构示意图;

15.图2是本发明所述的基于二氧化硅光波导的三维边缘耦合器沿光传输方向的前视图(a)、俯视图(b)和左视图(c);

16.图3(a)是通过时域有限差分法(finite-difference time-domain,fdtd)计算信号光波长为1550nm时,上(下)层条带中心与中心波导芯层(1)中心的垂直距离z(z=(h1+h2)/2+gap)与耦合效率的关系曲线;图3(b)是通过时域有限差分法计算,信号光波长为1550nm时,上(下)层条带中心与中心波导芯层(1)中心的垂直位置偏移量y(即层间对准失调)与耦合效率的关系曲线;

17.图4是本发明所述的基于二氧化硅光波导的三维边缘耦合器的耦合效率随着信号光波长变化曲线;

18.图5是信号光从中间波导芯层(1)输入端输入时,该三维边缘耦合器的光场分布图(沿光传输方向xz平面);

19.图6是本发明所述的基于二氧化硅光波导的三维边缘耦合器制备工艺流程:步骤1为作为基底层的硅衬底的准备,步骤2为沉积低折射率sio2下包层,步骤3沉积第一高折射率sio2芯层,步骤4为离子刻蚀第一高折射率sio2芯层形成下层条带,步骤5为沉积低折射率sio2第一中间包层,步骤6为沉积第二高折射率sio2芯层,步骤7为离子刻蚀第二层高折射率sio2芯层形成中间波导芯层,步骤8为沉积低折射率sio2第二中间包层,步骤9为沉积第三高折射率sio2芯层,步骤10为离子刻蚀第三高折射率sio2芯层形成上层条带,步骤11为沉积折低射率sio2上包层。

具体实施方式

20.下面通过具体的实施方式结合附图对本发明做进一步详细说明。

21.实施例1

22.1、确定中心波导芯层(1)的输入端宽度w1、输出端宽度w2和厚度h1。单模光纤纤芯直径范围为8.3μm~10μm,通过时域有限差分法计算时,本实施例选用纤芯直径为8.3μm的单模光纤,波导尺寸为3.5μm

×

3.5μm,所以中心波导芯层(1)的输入端宽度选定为w1=8μm,输出端宽度选定为w2=3.5μm,厚度h1=3.5μm。

23.2、确定中心波导芯层(1)的锥形耦合波导core1和输出波导core2长度。考虑到器件尺寸过大不利于集成和封装,根据有限时域差分法(finite-difference time-domain,fdtd)计算,锥形耦合波导core1长度l1=95μm,输出波导core2长度选定为l2=20μm。

24.3、确定下层条带(3)和上层条带(2)的宽度w3、长度l3、厚度h2。通过有限时域差分法确定,直波导可将泄露的信号光耦合进中间波导芯层,所以下层条带(3)和上层条带(2)选用具有相同结构尺寸的矩形直波导,宽度w3与中间波导芯层core2输出端宽度相同,w3=3.5μm,长度为l3=97μm。条带高度过大会导致部分结构与光纤芯无重叠,增大损耗;条带高度过小,则泄露光无法完全耦合至条带内,同样会增大损耗,因此条带厚度选为h2=1.5μm,以满足结构紧凑利于集成、易于封装的要求。

25.4、最后确定下层条带与中间波导芯层、上层条带与中间波导芯层之间的二氧化硅中间层厚度gap。由于gap过大或过小均会降低条带层的抑制光泄露功能。图3(a)显示时域有限差分法计算得到的信号光波长为1550nm时,上(下)层条带中心距芯层波导中心xy平面的距离z(如图2(a))与耦合效率间关系。由图可知,上(下)层条带中心距芯层波导中心xy平面的距离z为3.3μm,即下层条带与中间波导芯层、上层条带与中间波导芯层间的低折射率二氧化硅中间层厚度gap=0.8μm时,耦合效率最大为95.53%;上(下)层条带中心距芯层波导中心xy平面的距离z在2.9μm~3.7μm范围内,即下层条带与中间波导芯层、上层条带与中间波导芯层之间低折射率二氧化硅中间层厚度gap在0.4μm~1.2μm范围内时,耦合效率大于93.54%,耦合器对二氧化硅中间层厚度gap变化敏感度较低。

26.5、确定该器件的层间对准容差。理想状态下,在信号光波长为1550nm时,所述三维边缘耦合器耦合效率可达95.53%,针对三维多层结构存在层间对准问题,有必要增大层间

对准容差,降低工艺难度。图3(b)所示为通过时域有限差分法计算信号光波长为1550nm时,上(下)层条带中心位置距芯层波导中心xz平面的距离y(如图2(a),即层间对准误差)与耦合效率的关系曲线,由图可知:上(下)层条带中心位置距芯层波导中心xz平面的距离y为0时,耦合效率最大,为95.53%;当上(下)层条带中心位置距芯层波导中心xz平面的距离y在-3μm~3μm范围内时,耦合效率大于92.47%;当y在-3μm~3μm范围内变化时,耦合效率仅降低约3%,所述,三维边缘耦合器对于垂直对准精度要求低,有效降低了工艺难度。

27.6、图4显示了光纤与二氧化硅光波导三维边缘耦合器耦合效率随着信号光波长变化,结果表明,在1500nm~1620nm波长范围内,所述三维边缘耦合器的耦合效率大于94.98%,耦合效率变化范围94.98%~95.75%;在信号光波长为1550nm时,耦合效率为95.53%,可满足三维边缘耦合器波长不敏感要求。

28.7、图5为信号光从中间波导芯层输入端输入时,所述三维边缘耦合器光模场分布。由图可见,由光纤泄露的部分信号光耦合进入上、下条带后,又通过上、下条带与芯层波导构成的耦合结构,耦合进入中间芯层波导,上、下条带内无光能量残留,芯层波导传输过程中无明显光能量泄露,证明所述三维边缘耦合器有效降低了光模场失配导致的耦合损耗。

29.实施例2

30.下面结合图6详细说明本发明的具体制备方式,具体步骤如下:

31.1、硅衬底准备:选用硅片作为基底层(4),折射率为3.455,清洗硅衬底上的杂质、油污等有机物质,然后烘干。

32.2、沉积低折射率sio2下包层(5):采用等离子体增强化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)方法在清洗干净的硅基底层表面沉积sio2层,通过控制反应气体流量和射频功率,使sio2折射率为1.445(不掺锗的sio2),然后采用化学机械抛光(cmp)的方法控制sio2层的厚度和表面平整度,通过使低折射率sio2下包层厚度为10μm,得到下包层(5)。

33.3、沉积第一高折射率sio2芯层:采用pecvd法沉积第一高折射率sio2芯层,通过掺杂锗(ge)元素调节折射率,使其折射率为1.481,通过控制沉积速率生长高折射率sio2芯层,通过控制沉积速率使高折射率sio2薄膜厚度为1.5μm。

34.4、离子刻蚀第一高折射率sio2芯层形成下层条带(3):在生成的第一高折射率sio2芯层上旋涂光刻胶,利用紫外光刻将下层条带的波导图形转移至光刻胶,显影后icp刻蚀去除多余光刻胶,获得下层条带(3)。

35.5、沉积低折射率sio2第一中间包层(6):采用pecvd法在下层条带(3)表面沉积低折射率sio2层作为第一中间包层,第一中间包层完全覆盖下层条带(3);再采用化学机械抛光的方法控制低折射率sio2层厚度,使下层条带(3)上方sio2层的厚度为0.8μm,即本发明所述的第一中间包层(6)。

36.6、沉积第二高折射率sio2芯层:采用pecvd法沉积掺ge的sio2,通过控制沉积速率使掺杂ge的高折射率sio2薄膜厚度为3.5μm,折射率为1.481;

37.7、离子刻蚀第二层高折射率sio2芯层形成中间波导芯层(1):在生成的第二高折射率sio2芯层上旋涂光刻胶,紫外光刻中使中间波导芯层与下层条带垂直对准,将中间波导芯层的波导图形转移至光刻胶,显影后icp刻蚀去除多余去除光刻胶,从而获得本发明中的中间波导芯层(1)。

38.8、沉积低折射率sio2第二中间包层(7):采用pecvd法在中间波导芯层(1)上沉积低折射率sio2层,折射率为1.445;该低折射率sio2层覆盖中间波导芯层的同时,也将中间波导芯层周围的区域填满;再采用化学机械抛光方法控制低折射率sio2层的厚度和平整度,使中间波导芯层上方低折射率sio2层厚度为0.8μm,得到本发明所述的sio2第二中间包层(7)。

39.9、沉积第三高折射率sio2芯层:采用pecvd法沉积掺杂ge的高折射率sio2,通过控制沉积速率使掺ge的sio2薄膜厚度为1.5μm,折射率为1.481;

40.10、离子刻蚀第三高折射率sio2芯层形成上层条带(2):在生成的第三高折射率sio2芯层上旋涂光刻胶,紫外光刻中使上层条带与中间波导芯层垂直对齐,将中间波导芯层的波导图形转移至光刻胶,显影后icp刻蚀去除多余sio2芯层,去除光刻胶,从而得到本发明所述的上层条带(2)。

41.11、沉积sio2上包层(8):在上层条带(2)上沉积sio2层;该sio2层覆盖上层条带的同时,也将上层条带周围的区域填满;再采用化学机械抛光的方法,对其上表面进行研磨,使其厚度保持在10μm以上,形成sio2上包层(8),折射率为1.445,最终得到本发明所述的基于二氧化硅光波导的三维边缘耦合器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1