一种集成芯片上制备电极的方法与流程

1.本发明涉及集成芯片技术领域,更具体地说,它涉及一种在集成芯片上制备电极的方法。

背景技术:

2.由于电光调控具有极高的响应速度与极强的可控性,被广泛应用于光场调控中。在器件附近集成电极,电极上加一定电压,产生的电场可以改变器件的折射率,从而改变器件中传输光的特性(如振幅、相位、偏振信息等)。而通过改变加载的电压大小可以调谐器件中的光学性能。

3.因此,如何在光学器件上制备集成高质量的电极至关重要。目前较为广泛的是利用lift-off工艺(剥离工艺)在器件附近制备金属电极。其中,双层剥离工艺比较成熟,应用较为广泛,并且应用效果较好。市场上应用的双层剥离工艺主要是剥离两层不同的光刻胶材料:首先在需要制备电极的基片上旋涂两层不同种类的光刻胶,对于紫外双层胶体系,下面一层光刻胶选用不含光敏的胶体能直接在显影液中进行腐蚀,通过腐蚀时间控制腐蚀宽度;上面一层光刻胶选用光敏正胶或负胶,可以通过紫外曝光形成一定的图案掩膜。这样两层光刻胶结构通过紫外曝光,然后显影腐蚀就得到了预期图案的底切形态(在有光刻胶留下的区域,上层光刻胶宽度大,下层宽度小,可参考本发明技术附图7)。在光刻胶显影后,再在整个片子上方镀上预期作为电极的金属。最后再利用显影液腐蚀去除掉之前剩下的底层光刻胶。这样镀在光刻胶上方的金属就被剥离掉了,直接镀在基片上需要的金属电极就被保留下来了。

4.但是上述的剥离双层光刻胶制备金属电极的工艺还是存在较多方面的问题。在最后一步镀金属的过程中,不可避免的会有温度变化,而之前作为剥离层留下来的没有腐蚀掉的光刻胶也会受到温度影响。一旦超过光刻胶的玻璃态转化温度,光刻胶就会发生软化,使得图案变形,还有些胶在一定高温度下会加剧交联化,导致后续很难去除;另外镀膜时受热可能导致光刻胶变形、光刻胶与衬底以及薄膜的热膨胀系数不同,会导致薄膜层褶皱,边缘翘起等现象。以上问题都是由于光刻胶的热稳定性较差导致的,而镀膜过程必然会引入温度变化,而要解决这些问题,必然会增加工艺的复杂程度,增加时间成本,人工成本。

5.另外,在刚开始时,利用紫外曝光的方法在光刻胶上形成所需图案,虽然比较成熟,但依赖于掩模的图案,而制备高精度的特定图形掩模比较昂贵;另外,电子束刻写产生图形的方法虽然不依赖于成形的掩模,但是花费昂贵,速度较慢。因此两者都存在一定的缺陷。

6.因此亟需一种新的技术方案来解决上述技术问题。

技术实现要素:

7.针对现有技术存在的不足,本发明的目的在于提供一种在集成芯片上制备电极的方法。

8.本发明的上述技术目的是通过以下技术方案得以实现的:一种在集成芯片上制备电极的方法,其特征在于,包括如下步骤:

9.s1、利用紫外光刻技术、电子束刻蚀技术或激光加工技术等方法得到片上微纳结构,在片上微纳结构上镀第一薄膜层;

10.s2、在第一薄膜层的表面镀上第二薄膜层;

11.s3、在第二薄膜层的表面镀上第三薄膜层;

12.s4、利用飞秒激光烧蚀去除特定区域的第三薄膜层,去除的区域是最后需要设置金属电极的区域,得到掩膜;

13.s5、利用离子刻蚀方法或湿法刻蚀方法去除第二薄膜层相应区域,将掩膜图案转移到第二薄膜层,即上方有第三薄膜层存在的区域被保护,上方第三薄膜层被激光烧蚀去除区域的第二薄膜层被刻蚀去除;

14.s6、根据第二薄膜层的掩膜图案,利用湿法腐蚀或气体腐蚀方法,去除第一薄膜层的相应区域,并适当地比第二薄膜层所保护区域范围去除更大的范围,以形成底切形态;

15.s7、在整个样品表面镀金属层;

16.s8、利用湿法腐蚀或者气体腐蚀的方法腐蚀去除剩余的第一薄膜层。

17.通过采用上述技术方案,利用飞秒激光直写去除最顶层的cr膜或者光刻胶来获得掩膜图案,可以得到任何形状的二维掩膜图形,无需特意地制备一个可能只用一次的掩模。在不同的基片上只要镀上一层cr膜或者旋涂上一层光刻胶就可以随意得到不同的掩膜图案。并且对于不同精度的掩膜图案要求,成本基本一样。

18.本发明进一步设置为:在步骤s1中,所述第一薄膜层为si薄膜,其厚度为600nm-1um。

19.本发明进一步设置为:在步骤s2中,所述第二薄膜层为sio2薄膜,其厚度为200-400nm。

20.本发明进一步设置为:在步骤s3中,所述第三薄膜层为cr膜或光刻胶,其厚度为30-100nm。

21.本发明进一步设置为:镀膜方法为磁控溅射法。

22.本发明进一步设置为:镀膜方法为使用等离子体增强的化学气相沉积法(pecvd)。

23.本发明进一步设置为:如果薄膜层为cr薄膜,镀膜方法为磁控溅射法;如果薄膜层为光刻胶,则采用旋涂法。

24.本发明进一步设置为:在步骤s4中,利用飞秒激光将第三薄膜层的特定区域去除,形成需要的掩膜图案,去除的区域为需要制备金属电极的区域,选用波长为1030nm、重复频率为200khz的飞秒激光经聚焦后对第三薄膜层进行扫描,扫描速度为100mm/s,焦点扫描区域的第三薄膜层被直接烧蚀去除。

25.本发明具有以下有益效果:

26.1、利用飞秒激光直写去除最顶层的cr膜或者光刻胶来获得掩膜图案,可以得到任何形状的二维掩膜图形,无需特意地制备一个可能只用一次的掩模。在不同的基片上只要镀上一层cr膜或者旋涂上一层光刻胶就可以随意得到不同的掩膜图案。并且对于不同精度的掩膜图案要求,成本基本一样。

27.2、本发明中两个剥离层选用的分别是sio2薄膜和si薄膜,然后利用离子刻蚀方法

根据掩膜图案去除掉sio2薄膜,利用湿法腐蚀或者气体腐蚀的方法去除掉si薄膜,而本发明技术选取的sio2材料和si材料作为固体材料,在镀金属时所需的温度范围内具有很好的热稳定性,不存在现有技术方案因为温度变化导致的一系列问题。

附图说明

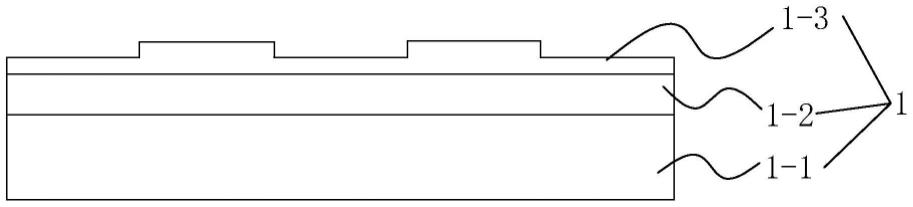

28.图1为片上微纳结构的结构示意图;

29.图2为片上微纳结构镀上第一薄膜层的结构示意图;

30.图3为片上微纳结构镀上第二薄膜层的结构示意图;

31.图4为片上微纳结构镀上第三薄膜层的结构示意图;

32.图5为通过飞秒激光烧蚀掉第三薄膜层特定区域后产品的结构示意图;

33.图6为刻蚀掉特定区域的第二薄膜层后的产品结构示意图;

34.图7为去除特定区域的第一薄膜层后的产品结构示意图;

35.图8为在最顶层镀上金属层后的产品结构示意图;

36.图9为去除剩下区域的第一薄膜层,使剥离掉上方剩余的第二薄膜层和金属层后的产品结构示意图。

37.附图说明:1、片上微纳结构;1-1、第一衬底;1-2、第二衬底;1-3、微纳结构;2、第一薄膜层;3、第二薄膜层;4、第三薄膜层;5、金属层。

具体实施方式

38.以下结合附图对本发明作进一步详细说明。

39.其中相同的零部件用相同的附图标记表示。需要说明的是,下面描述中使用的词语“前”、“后”、“左”、“右”、“上”和“下”指的是附图中的方向,词语“底面”和“顶面”、“内”和“外”分别指的是朝向或远离特定部件几何中心的方向。

40.具体实施例1:

41.一种在集成芯片上制备电极的方法,包括如下步骤:

42.(1)、先利用紫外光刻技术、电子束刻蚀技术或激光加工技术等任何可以实现微纳结构加工的方法得到如附图1所示的片上微纳结构1,其包括第一衬底1-1、第二衬底1-2与位于第二衬底表面的微纳结构1-3,微纳结构1-3可为马赫曾德干涉仪(mzi)结构。在片上微纳结构1上镀上第一薄膜层2,第一薄膜层为si薄膜,如附图2所示。镀膜方法包括化学气相沉积法(cvd)或磁控溅射法等。利用磁控溅射法在该结构上方镀1μm左右厚度的si薄膜,选用氩气作为溅射气体,通入流量为40sccm(40立方厘米/分钟),溅射气压0.5pa,射频溅射功率200w,衬底温度800℃,溅射时间为1h。

43.(2)、完成步骤(1)后在最上方镀上第二薄膜3,第二薄膜3为sio2薄膜,如附图3所示。使用等离子体增强的化学气相沉积法(pecvd):使用sih4和n2o作为反应生成sio2的原料气体,其流量配比为60:20,射频功率为200w,压强为28pa,沉积温度为300℃,沉积时间是1h。最后得到220nm厚度的sio2薄膜。

44.(3)、在完成(2)所述的步骤,即镀完sio2薄膜后,如附图4所示,利用磁控溅射技术镀50nm的第三薄膜4,第三薄膜为cr薄膜。氩气作为溅射气体,通入流量选择为25sccm(25立方厘米/分钟),溅射气压0.12pa,射频溅射功率150w,衬底温度100℃,溅射时间为5min。

45.(4)、利用飞秒激光将cr薄膜的特定区域去除,形成需要的掩膜图案,去除的区域为需要制备金属电极的区域,如附图5所示。选用波长为1030nm、重复频率为200khz的飞秒激光经聚焦后对cr膜进行扫描,扫描速度为100mm/s。

46.(5)、如附图6所示,使用反应离子刻蚀方法(rie)将cr膜上形成的掩膜图案转移到下一层sio2薄膜上。chf3作为反应气体,通入流量为40sccm(40立方厘米/分钟),反应气体压力为5pa,射频功率是300w,反应时间为1min。

47.(6)、将sio2薄膜层刻蚀之后的图案转移到下方的si薄膜层,也就是将si薄膜层需要集成金属电极的相应区域去除掉,并且相比于sio2层,腐蚀更深的宽度(横向拓宽深度)以形成底切结构,避免下一步蒸镀金属时金属颗粒附着到si层侧壁上影响si薄膜最终的去除。如附图7所示。使用湿法腐蚀法来去除掉si薄膜层相应区域。利用了质量分数为25%的tmah溶液在80摄氏度的水浴条件下对si进行腐蚀。先将样品浸没在腐蚀液中3分钟,以去除全部厚度的si薄膜,然后继续腐蚀7分钟,使得si薄膜腐蚀区域往里再腐蚀大约2.6um,与上方刻蚀之后的sio2薄膜层形成底切结构,腐蚀时间为10分钟。

48.(7)、最上方再镀上需要的金属层5,这里选用au(金)作为电极材料,如附图8所示,利用电子束蒸发镀膜的方式在最上方镀500nm厚的au薄膜。基片温度设为22℃,蒸距60cm,电子枪电压10kv,电子枪电流1a,蒸发速率为1nm/s,蒸发时间8分钟左右。

49.(8)、最后一步是剥离掉不需要电极的相应区域的au薄膜,如附图9所示。利用和步骤(7)一样的方法去除掉余下的si薄膜层即可。这里将整个结构浸没在tmah溶液中,腐蚀1小时左右,确保si薄膜腐蚀干净。这样最终就得到了集成有au电极的片上mzi结构。

50.具体实施例二:

51.一种在集成芯片上制备电极的方法,包括如下步骤:

52.(1)、已有片上微纳结构1,在片上微纳结构1上镀厚度为800nm的第一薄膜2,第一薄膜为sio2薄膜,使用等离子体增强的化学气相沉积法(pecvd)。

53.(2)、完成步骤(1)后在最上方利用磁控溅射法镀厚度为200nm的第二薄膜3,第二薄膜为si薄膜。

54.(3)、利用磁控溅射法镀厚度为50nm的第三薄膜4,第三薄膜为cr薄膜。

55.(4)、利用飞秒激光将cr薄膜的特定区域去除,形成需要的掩膜图案,去除的区域为需要制备金属电极的区域。

56.(5)、使用湿法腐蚀方法将cr膜上形成的掩膜图案转移到下一层si薄膜上。利用了质量分数为25%的tmah溶液在80摄氏度的水浴条件下对si进行腐蚀。

57.(6)、将si薄膜层刻蚀之后的图案转移到下方的sio2薄膜层,使用湿法腐蚀法来去除掉sio2薄膜层相应区域。利用了质量分数为20%的naoh溶液在80摄氏度的水浴条件下对sio2进行腐蚀。

58.(7)、最上方再镀上需要的金属层5,这里选用au(金)作为电极材料,利用电子束蒸发镀膜的方式在最上方镀500nm厚的au薄膜。

59.(8)、最后一步是剥离掉不需要电极的相应区域的au薄膜,利用和步骤(7)一样的方法去除掉余下的sio2薄膜层即可。这里将整个结构浸没在naoh溶液中,确保sio2薄膜腐蚀干净。这样最终就得到了集成有au电极的片上mzi结构。

60.具体实施例三:

61.一种在集成芯片上制备电极的方法,包括如下步骤:

62.(1)、已有片上微纳结构1,在片上微纳结构上利用磁控溅射法镀厚度为800nm的第一薄膜2,第一薄膜2为cr薄膜。

63.(2)、完成步骤(1)后在最上方利用化学气相沉积法(pecvd)镀厚度为300nm的第二薄膜3,第二薄膜3为sio2薄膜。

64.(3)、利用磁控溅射法镀厚度为50nm的第三薄膜4,第三薄膜4为cr薄膜。

65.(4)、利用飞秒激光将cr薄膜的特定区域去除,形成需要的掩膜图案,去除的区域为需要制备金属电极的区域。

66.(5)、使用反应离子刻蚀方法(rie)将cr膜上形成的掩膜图案转移到下一层sio2薄膜上。

67.(6)、通过湿法腐蚀法将sio2薄膜层刻蚀之后的图案转移到下方的cr薄膜层,利用cr腐蚀液(主要成分是硝酸铈铵和硝酸)来去除掉cr薄膜层相应区域。

68.(7)、最上方再镀上需要的金属层5,这里选用au(金)作为电极材料,利用电子束蒸发镀膜的方式在最上方镀500nm厚的au薄膜。

69.(8)、最后一步是剥离掉不需要电极的相应区域的au薄膜,利用和步骤(7)一样的方法去除掉余下的cr薄膜层即可。将整个结构浸没在cr腐蚀液中,确保cr薄膜腐蚀干净,这样最终就得到了集成有au电极的片上mzi结构。

70.具体实施例仅仅是对本发明的解释,其并不是对本发明的限制,本领域技术人员在阅读完本说明书后可以根据需要对本实施例做出没有创造性贡献的修改,但只要在本发明的权利要求范围内都受到专利法的保护。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1