一种半导体器件及其制作方法与流程

1.本发明涉及半导体器件领域,特别涉及一种半导体器件的制作方法以及制得的半导体器件。

背景技术:

2.随着时间的推移,硅电子集成电路的性能越来越接近技术的物理极限,改进的步伐已经放缓。在数据处理和通信领域,数据中心和高性能计算机的不断增长的带宽需求必须不断提高自己的能力和表现。该增强数据处理性能应该伴随着功耗的减少以及较低的制造成本。硅光子集成电路可能是实现该需求最有前途的技术。

3.在硅光子集成电路中,光波导是实现不同光子芯片信息交互的核心器件。在同一硅光子集成电路中,为实现不同的功能,会布设多种类型的光波导器件,不同类型的光波导具有不同的刻蚀深度,部分类型的波导例如脊形光波导本身具有两个不同的刻蚀深度。现有技术中采用多步刻蚀波导材料层的方式满足不同硅刻蚀深度的需求,在该工艺中,刻蚀步骤多,工艺复杂,并且在后续步骤刻蚀的过程中,前面步骤已经形成的光波导器件的部分表面会再次受到等离子体的轰击,导致光波导器件的侧壁或表面存在较大的刻蚀损伤,具有增大光损耗的风险,不利于器件的稳定性。

技术实现要素:

4.为了克服现有技术的不足,本发明的目的在于提供一种半导体器件的制作方法,其可以实现光波导工艺的简化,提交光波导器件工艺的一致性,在防止所述光波导表面或侧壁受损,从而解决光损耗大的问题。

5.本发明的目的采用以下技术方案实现:根据本发明的一方面,提供一种半导体器件的制作方法,所述方法包括:提供一半导体衬底,所述半导体衬底包括一支撑衬底、设置在所述支撑衬底上表面的埋氧层以及设置在所述埋氧层上表面的光波导材料层;在所述光波导材料层上表面沉积一硬掩模层,所述硬掩模层具有一预定的厚度;通过三次及以上的光刻刻蚀步骤,在所述硬掩模层上刻蚀出与目标光波导形貌一致的硬掩模图案,其中,所述硬掩模图案具有预设的三个及以上的不同刻蚀深度;利用所述硬掩模图案为刻蚀掩模,通过一步刻蚀工艺刻蚀所述光波导材料层,形成多个光波导,所述多个光波导中具有预设的三个及以上的不同刻蚀深度。

6.可选的,所述光波导材料层是硅层或者氮化硅层。

7.可选的,所述硬掩模层是依次层叠的氧化硅层和氮化硅层。

8.进一步的,所述通过三次及以上的光刻刻蚀步骤,在所述硬掩模层上刻蚀出与目标光波导形貌一致的硬掩模图案包括:在所述硬掩模层上形成第一光刻胶,通过光刻工艺在硬掩模层第一区域对应的位置定义出所述光波导中具有第一刻蚀深度部分的图形,刻蚀所述硬掩模层的第一区域至第

四刻蚀深度,在所述第一区域形成与所述光波导中具有第一刻蚀深度部分的形貌一致的第一硬掩模图案,去除所述第一光刻胶;在所述硬掩模层上形成第二光刻胶,通过光刻工艺,在硬掩模层第二区域对应的位置定义出所述光波导中具有第二刻蚀深度部分的图形,刻蚀所述硬掩模层的第二区域至第五刻蚀深度,在所述第二区域形成与所述光波导中具有第二刻蚀深度部分的形貌一致的第二硬掩模图案,去除所述第二光刻胶;在所述硬掩模层上形成第三光刻胶,通过光刻工艺在硬掩模层第三区域对应的位置定义出所述光波导中具有第三刻蚀深度部分的图形,刻蚀所述硬掩模层的第三区域至第六刻蚀深度,在所述第三区域形成与所述光波导中具有第三刻蚀深度部分的形貌一致的第三硬掩模图案,去除所述第三光刻胶。

9.进一步的,所述第一刻蚀深度、所述第二刻蚀深度、所述第三刻蚀深度三者互不相等。例如,设所述第一刻蚀深度为h1,设所述第二刻蚀深度为h2,设所述第三刻蚀深度为h3,其中,h1、h3、h2互不相等。

10.可选的,所述第二区域、所述第一区域、所述第三区域相互具有重叠的部分。

11.可选的,所述第二区域与所述第一区域、所述第三区域具有重叠的部分,所述第一区域和所述第三区域不重叠。

12.进一步的,所述多个光波导至少包括一个及以上的光栅、一个及以上的条形光波导、一个及以上的脊形光波导。

13.进一步的,所述在所述硬掩模层上形成第一光刻胶的步骤包括:在所述硬掩模层的表面形成第一抗反射涂层,在所述第一抗反射涂层的表面形成所述第一光刻胶,所述第一抗反射涂层是底部抗反射涂层或介质抗反射涂层;进一步的,所述在所述硬掩模层上形成第二光刻胶的步骤包括:在所述硬掩模层的表面形成第二抗反射涂层,在所述第二抗反射涂层的表面形成所述第二光刻胶,所述第二抗反射涂层是底部抗反射涂层或介质抗反射涂层;进一步的,所述在所述硬掩模层上形成第三光刻胶的步骤包括:在所述硬掩模层的表面形成第三抗反射涂层,在所述第三抗反射涂层的表面形成所述第三光刻胶,所述第三抗反射涂层是底部抗反射涂层或介质抗反射涂层。

14.可选的,所述一步刻蚀工艺是等离子体刻蚀工艺。

15.根据本发明的另一方面,提供一种半导体器件,所述半导体器件包括:半导体衬底,所述半导体衬底包括一支撑衬底、所述支撑衬底上表面的埋氧层以及设置在所述埋氧层上表面的多个光波导,所述多个光波导由同一光波导材料层通过一步刻蚀工艺刻蚀形成,所述多个光波导具有三个不同的刻蚀深度。

16.可选的,所述多个光波导至少包括一个及以上的光栅、一个及以上的条形光波导、一个及以上的脊形光波导。

17.可选的,所述半导体器件是采用上述制作方法制得的。

18.本发明实施例提供的半导体器件的制作方法,通过多次刻蚀硬掩模形成与多种波导形貌一致的硬掩模图案,再利用一步刻蚀工艺刻蚀波导材料层形成波导,简化了刻蚀工艺,同时避免部分波导受到多次等离子体刻蚀气体的轰击而造成额外的刻蚀损伤,降低了光波导器件的传输损耗。

附图说明

19.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的实施方式。

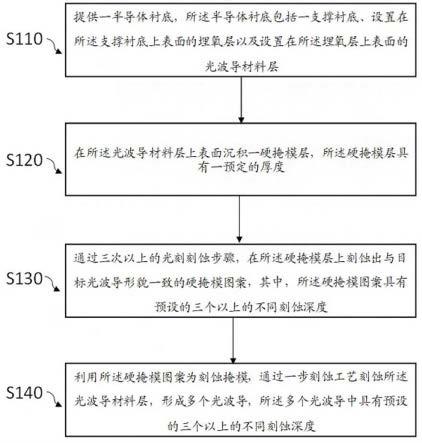

20.图1是根据本发明实施例的半导体器件的制作方法的流程图。

21.图2a-图2k是根据本发明实施例提供的半导体器件的制作方法的制作工序示意图。

22.图3是根据本发明实施例提供的半导体器件的剖面示意图。

具体实施方式

23.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

24.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。本文中芯片的含义可以包括裸芯片。在涉及方法步骤时,本文图示的先后顺序代表了一种示例性的方案,但不表示对先后顺序的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

25.针对现有的采用多步刻蚀波导材料层以得到不同光波导刻蚀深度的工艺,刻蚀步骤多,工艺复杂,并且对部分光波导器件的部分表面造成较大的刻蚀损伤,存在较大光损耗的风险等技术问题,本发明实施例提出了一种半导体器件的制作方法,通过多步刻蚀硬掩模形成与待形成的光波导形貌一致的硬掩模图案,再通过一次等离子体刻蚀工艺形成光子集成芯片上的全部光波导,并保证了光波导性能的一致性,大大减小刻蚀损耗,保持了器件的稳定性。

26.为使本发明的目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

27.图1是根据本发明实施例的半导体器件的制作方法的流程图。所述半导体器件的制作方法包括:s110,提供一半导体衬底,所述半导体衬底包括一支撑衬底、设置在所述支撑衬底上表面的埋氧层以及设置在所述埋氧层上表面的光波导材料层;s120,在所述光波导材料层上表面沉积一硬掩模层,所述硬掩模层具有一预定的厚度;s130,通过三次及以上的光刻刻蚀步骤,在所述硬掩模层上刻蚀出与目标光波导形貌一致的硬掩模图案,其中,所述硬掩模图案具有预设的三个及以上的不同刻蚀深度;s140,利用所述硬掩模图案为刻蚀掩模,通过一步刻蚀工艺刻蚀所述光波导材料层,形成多个光波导,所述多个光波导中具有预设的三个及以上的不同刻蚀深度。

28.图2a-图2k是根据本发明一实施例提供的半导体器件的制作方法的制作工序示意图。以下将结合图2a-图2k对本发明实施例进行详细说明。

29.在本发明实施例中,示例性地,请参阅图2a的示意,提供半导体衬底100,所述半导体衬底100包括支撑衬底101、设置在所述支撑衬底101上表面的埋氧层102、设置在埋氧层102上表面的光波导材料层103。可选的,所述光波导材料层103可以是硅层、sin层,所述支撑衬底101可以是任意合适的支撑材料,例如硅材料、陶瓷材料、石英等。

30.参阅图2b的示意,在所述半导体衬底100的所述光波导材料层103上形成硬掩模层200,所述硬掩模层200具有预设的厚度,用于后续刻蚀形成具有三个及以上刻蚀深度的图案。优选地,所述硬掩模层200包括依次层叠的氧化硅层104、氮化硅层105,所述氧化硅层104设置在所述光波导材料层103的上表面,所述氮化硅层设置在所述氧化硅层104的上表面。可选地,采用pecvd法、热氧化法形成所述氧化硅层104,采用化学沉积的方法形成所述氮化硅层105。

31.参阅图2c的示意,在所述硬掩模层200的上表面形成第一光刻胶层106,通过对所述第一光刻胶层106进行曝光、显影,在所述氮化硅层105的第一区域对应的表面上形成与具有第一刻蚀深度(设为h1)的光波导形貌一致的第一光刻胶图案。作为示例的,在所述氮化硅层105的第一区域对应的表面上形成与光栅的栅线形貌一致的第一光刻胶图案。

32.参阅图2d的示意,利用所述第一光刻胶图案采用等离子体刻蚀方法执行第一刻蚀步骤,刻蚀所述硬掩模层200的第一区域至第四深度(设为h4),形成与具有第一刻蚀深度h1的光波导形貌一致的第一硬掩模图案,作为可选的示例,所述第一硬掩模图案与光栅的栅线形貌一致,所述第四深度h4等于氮化硅层105的厚度,所述第一刻蚀步骤停止于所述氧化硅层104的上表面。执行所述第一刻蚀步骤之后,去除剩余的所述第一光刻胶。

33.参阅图2e的示意,在具有所述第一硬掩模图案的所述硬掩模层200上形成第二光刻胶层107,通过对所述第二光刻胶层107进行曝光、显影,在所述氮化硅层105的第二区域对应的表面上形成与具有第二刻蚀深度(设为h2)的光波导形貌一致的第二光刻胶图案。其中,所述第二区域与所述第一区域具有重叠的部分。作为示例的,在所述氮化硅层105的第二区域对应的表面上形成与条形光波导形貌一致的第二光刻胶图案。

34.参阅图2f的示意,利用所述第二光刻胶图案,采用等离子体刻蚀方法执行第二刻蚀步骤,刻蚀所述硬掩模层200的第二区域至第五深度(设为h5),形成与具有第二刻蚀深度h2的光波导形貌一致的第二硬掩模图案,作为可选的示例,所述第二硬掩模图案与条形光波导形貌一致,所述第五深度h5等于氧化硅层104与氮化硅层105的厚度之和,所述第二刻蚀步骤停止于所述光波导材料层103的上表面。执行所述第二刻蚀步骤之后,去除剩余的所述第二光刻胶。由于第二区域与第一区域具有重叠的部分,因此,得到的第一硬掩模图案与第一硬掩模图案也具有重叠的部分。作为示例的,所述第一区域的硬掩模图案是组合了第一硬掩模图案和第二硬掩模图案的集合,即所述第一区域的硬掩模图案的外部轮廓与条形光波导一致,中间还具有光栅的栅线图形。其他区域也可以根据需要调制成具有所述第一硬掩模图案与所述第二硬掩模图案的组合,并且,第一硬掩模图案与第二硬掩模图案可以是其他任意合适的光波导器件的形貌。

35.参阅图2g的示意,在具有所述第一硬掩模图案及所述第二硬掩模图案的所述硬掩模层200上依次形成底部抗反射涂层108、第三光刻胶层109,通过对所述第三光刻胶层109

进行曝光、显影,在所述氮化硅层105的第三区域对应的上方形成与具有第三刻蚀深度(设为h3)的光波导形貌一致的第三光刻胶图案。作为可选的示例,所述第三区域与所述第二区域具有重叠的部分,另外,根据需要,所述第三区域也可以与所述第一区域具有重叠的部分,或者所述第三区域与所述第一区域、所述第二区域都具有重叠的部分。

36.参阅图2h的示意,利用所述第三光刻胶图案,执行第三刻蚀步骤,刻蚀所述底部抗反射涂层108直至暴露出硬掩模层200的上表面。继续参阅图2i,利用第三光刻胶图案与上述刻蚀出的底部抗反射涂层的图案,采用等离子刻蚀方法执行第四刻蚀步骤,刻蚀硬掩模层200的第三区域至第六刻蚀深度(设为h6),形成与具有第三刻蚀深度h3的光波导形貌一致的第三硬掩模图案,作为可选的示例,所述第三硬掩模图案与脊形光波导中的凸起的脊部形貌一致。所述第六深度大于氮化硅层105的厚度,但是小于氧化硅层104与氮化硅层105的厚度之和,所述第三刻蚀步骤停止于所述氧化硅层104中间的预设位置。执行所述第四刻蚀步骤之后,去除剩余的所述第三光刻胶和所述底部抗反射涂层,并采用湿法清洗步骤把残留在表面的杂质去除,得到如图2j示意的具有所述第一硬掩模图案、第二硬掩模图案、第三硬掩模图案的硬掩模图案层,该硬掩模图案层具有三个不同的刻蚀深度。

37.由于待刻蚀基体表面的光学反射效应,反射光线和入射光线相干涉,在光刻胶内部形成驻波效应(standing wave effect)和多重曝光,导致图案的关键尺寸无法控制,图案侧壁出现波浪似的锯齿状缺失,大大增加了控制刻蚀精确性的难度。在形成第三光刻胶109之前,在具有所述第一硬掩模图案及所述第二硬掩模图案的所述硬掩模层200的表面先形成底部抗反射涂层,底部抗反射涂层能有效消除反射形成干涉驻波,增加曝光能量范围和焦距,降低基体几何结构差异对关键尺寸均匀度的影响。可选择的,所述底部抗反射涂层还可以用介质抗反射涂层代替。可选择的,可以在具有所述第一硬掩模图案及所述第二硬掩模图案的所述硬掩模层200的表面直接形成第三光刻胶层109而不形成底部抗反射涂层。根据刻蚀图案的需要,也可以在形成第一光刻胶层106、形成第二光刻胶层107之前先形成底部抗反射涂层。

38.参阅图2k的示意,利用上述步骤得到的硬掩模图案层,采用等离子体刻蚀工艺,对所述光波导材料层103执行第五刻蚀步骤,该第五刻蚀步骤通过一次刻蚀工艺,对所述半导体衬底100上的光波导材料层103进行全刻蚀,得到分布于所述半导体衬底100上的多个光波导,所述多个光波导具有三个以上的刻蚀深度。具体作为示例的,参阅图3的示意,展示了三种不同形貌的光波导,分别是光栅201、条形光波导202、脊形光波导203,其中,所述光栅201的栅线201-1具有第一刻蚀深度h1,所述条形光波导202具有第二刻蚀深度h2,所述脊形光波导203的脊部具有第三刻蚀深度h3,其中,h1、h2、h3互不相等。另外,所述光栅201、所述脊形光波导203的外侧面的刻蚀深度与所述条形光波导202的深度相同,因此,在刻蚀硬掩模图案层的过程中,所述第二区域与所述第一区域、所述第三区域具有重叠的部分,也就是所述光栅201的外侧壁、所述脊形光波导203的外侧壁的硬掩模图案与所述条形光波导的硬掩模图案在同一步刻蚀工艺完成。

39.作为示意的,上述半导体器件制备方法中示意的仅仅是三种不同形貌的光波导,具有三个不同的刻蚀深度。本发明的方法不局限于以上的示例,可以是具有多于三种形貌的光波导,也可以具有多于三个的不同刻蚀深度。所述半导体器件也不局限于光波导,也可以是其他需要刻蚀的、同层形成并具有不同刻蚀深度需求的半导体器件。硬掩模层的刻蚀

顺序也不局限于上述的示例,可以根据需求调制刻蚀顺序。

40.再次结合图3对本发明的半导体器件做进一步的详细说明。图3是本发明实施例的半导体器件的局部剖视图,所述半导体器件包括:一半导体衬底,所述半导体衬底包括一支撑衬底101、设置在所述支撑衬底101上表面的埋氧层102以及设置在所述埋氧层上表面的多个光波导,所述多个光波导由同一光波导材料层通过一步刻蚀工艺刻蚀形成,所述多个光波导分别为光栅、条形光波导、脊形光波导,该些光波导结构具有三个不同的刻蚀深度,分别设为h1、h2、h3,其中,所述光栅201的栅线201-1的刻蚀深度的h1,所述条形光波导202、所述光栅201的外侧壁、所述脊形光波导的外侧壁的刻蚀深度是h2,所述脊形光波导203的脊部203-1的刻蚀深度是h3。可选的,所述多个光波导还可以是其他类型的光波导,也可以是多于三种类型的光波导,和/或多于三种的刻蚀深度,可以根据实际需求进行选择。

41.本发明实施例提供的半导体器件的制作方法,通过多次刻蚀硬掩模形成与多种波导形貌一致的硬掩模图案,再利用一次刻蚀工艺刻蚀波导材料层形成波导,简化了刻蚀工艺,同时避免部分波导多次受到等离子体刻蚀气体的轰击而造成额外的刻蚀损伤,降低了光波导器件的传输损耗,提高了器件的稳定性。此外,在形成光刻胶之前,在硬掩模层的表面先形成底部抗反射涂层,底部抗反射涂层能有效消除反射形成干涉驻波,增加曝光能量范围和焦距,降低基体几何结构差异对关键尺寸均匀度的影响,进一步提高了器件的稳定性能。

42.上文仅为本发明的较佳实施例而已,并非用来限定本发明实施的范围,凡依本发明权利要求范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的权利要求范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1