阵列基板及显示面板的制作方法

1.本发明涉及显示技术领域,具体涉及一种阵列基板及一种显示面板。

背景技术:

2.信号在传输过程中受各种因素影响会出现不同程度的延迟,影响信号的传输均一性,引起显示面板出现显示质量问题。如在显示面板的扇出区内,由于多条信号线的长度并不相同,因此,各信号线的阻值会存在一定差异,导致各信号线传输的信号具有不同的延迟,从而使得传输至显示面板面内的信号存在差异,致使显示面板出现暗带不良问题,影响显示面板的显示质量。

技术实现要素:

3.本发明实施例提供一种阵列基板及一种显示面板,可以改善暗带不良问题。

4.本发明实施例提供一种阵列基板,所述阵列基板具有显示区、扇出区和位于所述显示区与所述扇出区之间的连接区。所述阵列基板包括多条扇出线、多条信号线、多条连接线以及多条耦合线。

5.所述多条扇出线位于所述扇出区内,且所述多条扇出线的电阻不同;所述多条信号线位于所述显示区内;所述多条连接线位于所述连接区内,所述多条连接线电性连接于所述多条扇出线和所述多条信号线之间;所述多条耦合线位于所述连接区内,所述多条耦合线与所述多条连接线异层。

6.其中,在俯视视角下,所述多条连接线和所述多条耦合线部分重叠,且所述连接线和所述耦合线的重叠面积与所述连接线电性连接的所述扇出线的电阻负相关。

7.可选地,在本发明的一些实施例中,所述阵列基板还包括多条扫描线及多个选通驱动电路。所述多条扫描线与所述多条耦合线平行;多个所述选通驱动电路与所述多条扫描线和所述多条耦合线电性连接。

8.可选地,在本发明的一些实施例中,所述多条耦合线与所述多条扫描线同层。

9.可选地,在本发明的一些实施例中,所述多条扇出线包括第一扇出线和第二扇出线,所述第一扇出线的电阻大于所述第二扇出线的电阻。多条信号线包括第一信号线和第二信号线。所述多条连接线包括第一连接线和第二连接线,所述第一连接线电性连接于所述第一信号线和所述第一扇出线之间,所述第二连接线电性连接于所述第二信号线和所述第二扇出线之间。

10.其中,至少一所述耦合线包括电性连接的第一走线部和耦合部,所述第一走线部的宽度小于所述耦合部的宽度;在俯视视角下,所述第一连接线与所述第一走线部部分重叠,所述第二连接线与所述耦合部部分重叠。

11.可选地,在本发明的一些实施例中,所述第二连接线包括电性连接的第二走线部和连接部,所述连接部的宽度大于所述第一走线部、所述第二走线部的宽度。其中,在俯视视角下,所述连接部与所述耦合部至少部分重叠。

12.可选地,在本发明的一些实施例中,所述第二连接线的长度大于所述第一连接线的长度。

13.可选地,在本发明的一些实施例中,所述多条扇出线还包括多条第三扇出线,所述多条第三扇出线的电阻自所述第二扇出线靠近所述第一扇出线的方向上逐渐增大。多条信号线还包括多条第三信号线。所述多条连接线还包括位于所述第一连接线和所述第二连接线之间的多条第三连接线,所述多条第三连接线电性连接于所述多条第三信号线和所述多条第三扇出线之间。

14.其中,在俯视视角下,所述耦合部的宽度自所述第二连接线靠近所述第一连接线的方向上逐渐减小,所述多条第三连接线与所述耦合部的重叠面积自所述第二连接线靠近所述第一连接线的方向上逐渐减小。

15.可选地,在本发明的一些实施例中,所述多条扇出线包括第一扇出线、第二扇出线和多条第三扇出线,所述第一扇出线的电阻大于所述第二扇出线的电阻,所述多条第三扇出线的电阻自所述第二扇出线靠近所述第一扇出线的方向上逐渐增大。多条信号线包括第一信号线、第二信号线和多条第三信号线。所述多条连接线包括第一连接线、第二连接线和多条第三连接线,所述第一连接线电性连接于所述第一信号线和所述第一扇出线之间,所述第二连接线电性连接于所述第二信号线和所述第二扇出线之间,所述多条第三连接线电性连接于所述多条第三信号线和所述多条第三扇出线之间。

16.其中,所述第二连接线的长度大于所述第一连接线的长度,所述多条第三连接线的长度自所述第二连接线靠近所述第一连接线的方向上逐渐减小。

17.本发明还提供一种显示面板,包括任一上述的阵列基板、彩膜基板及框胶。所述彩膜基板与所述阵列基板相对设置。所述框胶位于所述阵列基板和所述彩膜基板之间,且所述框胶位于所述扇出区远离所述连接区的一侧。

18.本发明还提供一种显示面板,包括任一上述的阵列基板及发光器件层,所述发光器件层位于所述阵列基板上,所述发光器件层包括多个发光器件,所述多个发光器件与所述多条信号线电性连接。

19.本发明还提供一种显示装置,包括任一上述的显示面板。

20.本发明提供一种阵列基板、一种显示面板及一种显示装置,通过在扇出区和显示区之间设置连接区,并在连接区内设置多条连接线及多条耦合线,使连接线与耦合线的重叠面积与连接线电性连接的扇出线的电阻负相关,以补偿因位于扇出区内的多条扇出线所具有的电阻差异而导致的信号延迟及损耗差异,使得位于显示区内的多条信号线所传输的信号具有相近的损耗和延迟,显示面板及显示装置均包括阵列基板,从而可以改善显示暗带问题。

附图说明

21.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

22.图1是现有技术中阵列基板的结构示意图及信号变化波形图;

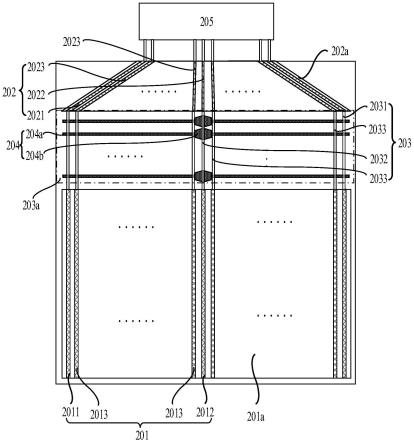

23.图2a~图2d是本发明实施例提供的阵列基板的结构示意图;

24.图3a~图3b是本发明实施例提供的显示面板的结构示意图;

25.图4a~图4b是仿真结果对比图。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。在本发明中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

27.具体地,如图1是现有技术中显示面板的结构示意图及信号变化波形图。以信号线传输的信号为数据信号为例,数据信号由电路板101经覆晶薄膜102、位于扇出区10a内扇出走线传输至位于显示区10b内的数据线,位于显示区10b内的各子像素与数据线电性连接,以根据数据信号进行显示。数据信号在由电路板101传输至子像素的过程中,会受各种因素影响(如空间限制、制程工艺能力等),致使各数据线内传输的数据信号会出现延迟现象,从而影响子像素的充电效果,严重的会引起垂直暗带问题。

28.如由于受显示面板本身的边框尺寸和覆晶薄膜规格因素的影响,扇出区10a会被设计出梯形,相应地,位于扇出区10a内的扇出走线就会出现长度差异,进而导致位于扇出区10a内的扇出走线出现阻值差异,继而导致经由扇出线进行传输的数据信号出现不同的延迟效果,故而引起暗带不良的问题,影响显示面板的显示品质。具体的,位于扇出区10a中部的扇出线l2长度小于位于扇出区10a两侧的扇出线l1的长度。因此,位于扇出区10a两侧的扇出线l1的电阻r1大于位于扇出区10a中部的扇出线的电阻r2,经位于扇出区10a两侧的扇出线l1传输的数据信号data1相较于经位于扇出区10a中部的扇出线l2传输的数据信号data2会具有延迟及损耗差异,从而使传输至对应子像素的像素电压pixel1和pixel2出现差异。此外,在覆晶薄膜102及数据线的制备过程中,受工艺条件及工艺能力的限制,还会出现电阻电容差异不良或缺陷,从而引起暗带问题。特别的,在高频、高分辨率显示面板中尤其明显。其中,gate表示扫描信号。

29.为此,本技术提供一种阵列基板、显示面板及显示装置,以改善显示暗带问题。具体的,图2a~图2d是本发明实施例提供的阵列基板的结构示意图。

30.阵列基板具有显示区201a、扇出区202a和位于所述显示区201a与所述扇出区202a之间的连接区203a。所述阵列基板包括多条信号线201、多条扇出线202、多条连接线203以及多条耦合线204。

31.所述多条扇出线202位于所述扇出区202a内,且所述多条扇出线202的电阻不同。可选地,所述多条扇出线202的长度不同,使得所述多条扇出线202的电阻不同。可选地,所述多条扇出线202中的部分扇出线可能存在换线(即由具有不同电阻率的走线电性连接形成)等,从而使得所述多条扇出线202的电阻不同。可选地,所述多条扇出线202受工艺制程等影响,使得所述多条扇出线202的横截面不同,从而使得所述多条扇出线202的电阻不同。

32.所述多条信号线201位于所述显示区201a内。可选地,所述多条信号线201包括数据线,所述数据线用于输出数据信号。可选地,所述多条信号线201还可以包括扫描线,多条扫描线用于传输多个扫描信号。

33.所述多条连接线203位于所述连接区203a内,所述多条连接线203电性连接于所述多条扇出线202和所述多条信号线201之间。

34.所述多条耦合线204位于所述连接区203a内,所述多条耦合线204与所述多条连接线203异层。可以理解的,为避免所述多条耦合线204和所述多条连接线203之间出现短路,所述多条耦合线204所在的膜层和所述多条连接线203所在的膜层之间还具有绝缘层。

35.在俯视视角下,所述多条连接线203和所述多条耦合线204部分重叠,且所述连接线203与所述耦合线204的重叠面积与所述连接线203电性连接的所述扇出线202的电阻呈负相关。即所述扇出线202的电阻越大,所述连接线203与所述耦合线204的重叠面积越小,从而使得所述连接线203与所述耦合线204形成的耦合电容越小;所述扇出线202的电阻越小,所述连接线203与所述耦合线204的重叠面积越大,从而使得所述连接线203与所述耦合线204形成的耦合电容越大。

36.相应地,若所述扇出线202包括的第一扇出线2021的电阻大于所述扇出线202包括的第二扇出线2022的电阻,所述连接线203包括第一连接线2031和第二连接线2032,所述信号线201包括第一信号线2011和第二信号线2012,所述第一连接线2031电性连接于所述第一信号线2011和所述第一扇出线2021之间,所述第二连接线2032电性连接于所述第二信号线2012和所述第二扇出线2022之间。那么,与所述第一扇出线2021、所述第一信号线2011及所述第一连接线2031对应的总电容小于与所述第二扇出线2022、所述第二信号线2012及所述第二连接线2032对应的总电容,从而改善所述第一扇出线2021与所述第二扇出线2022之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。

37.通过使所述多条连接线203和所述多条耦合线204部分重叠,以使所述多条连接线203和所述多条耦合线204之间对应具有多个耦合电容。通过使所述连接线203与所述耦合线204的重叠面积与所述连接线203电性连接的所述扇出线202的电阻呈负相关,以控制与具有不同电阻的扇出线202相接的连接线203所对应的耦合电容也不同,从而使相接的所述扇出线202、所述连接线203和所述信号线201上的总电容所导致的信号延迟和损耗差异与所述扇出线202所具有的电阻差异所导致的信号延迟差异相抵消,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟,从而改善显示暗带问题。

38.可选地,在俯视视角下,所述多条连接线203和所述多条耦合线204部分重叠,且所述连接线203与所述耦合线204的重叠面积与所述连接线203电性连接的所述扇出线202的长度呈负相关,以补偿因所述多条扇出线202的长度差异所造成的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。

39.可选地,所述阵列基板还包括多个子像素,多个所述子像素位于所述显示区201a内,多个所述子像素与所述多条信号线201电性连接。如所述多条信号线201包括所述多条数据线时,所述多条数据线与多个所述子像素电性连接,以使多个所述子像素根据多个所

述数据线传输的数据信号进行显示。所述多条信号线201包括所述多条扫描线时,所述多条扫描线与多个所述子像素电性连接,以实现多个所述子像素的显示时刻等控制。

40.可选地,所述阵列基板还包括多个选通驱动电路,所述多条扫描线与多个所述子像素电性连接,且所述多条扫描线与所述多条耦合线204平行;多个所述选通驱动电路与所述多条扫描线和所述多条耦合线204电性连接。所述多个选通驱动电路用于生成扫描信号,所述多条耦合线204与所述扫描线均用于传输扫描信号。

41.可选地,所述耦合线204可与所述阵列基板中的信号走线复用。如在一些阵列基板中,为保证扫描信号的均一性,阵列基板在所述连接区203a内设有虚拟扫描线,所述虚拟扫描线可复用为所述耦合线204,所述虚拟扫描线可用于传输扫描信号。

42.可选地,所述多条耦合线204与所述多条扫描线同层,以节省制程工序。

43.可选地,可通过改变所述连接线203和/或所述耦合线204的形状、长度、宽度、尺寸等参数,以对应补偿所述扇出线202之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟,从而改善显示暗带问题。

44.具体的,请继续参阅图2a~图2c,仍以所述多条信号线201包括第一信号线2011和第二信号线2012;所述多条扇出线202包括第一扇出线2021和第二扇出线2022,所述多条连接线203包括第一连接线2031和第二连接线2032为例进行说明。

45.所述第一扇出线2021的电阻大于所述第二扇出线2022的电阻。可选地,所述第一扇出线2021的长度大于所述第二扇出线2022的长度,使得所述第一扇出线2021的电阻大于所述第二扇出线2022的电阻。

46.所述第一连接线2031电性连接于所述第一信号线2011和所述第一扇出线2021之间,所述第二连接线2032电性连接于所述第二信号线2012和所述第二扇出线2022之间。

47.可选地,至少一所述耦合线204包括电性连接的第一走线部204a和耦合部204b,所述第一走线部204a的宽度小于所述耦合部204b的宽度。在俯视视角下,所述第一连接线2031与所述第一走线部204a部分重叠,所述第二连接线2032与所述耦合部204b部分重叠,如图2a所示,从而使所述第一连接线2031与所述耦合线204的重叠面积小于所述第二连接线2032与所述耦合线204的重叠面积,继而使所述第一连接线2031与所述耦合线204形成的耦合电容小于所述第二连接线2032与所述耦合线204的形成的耦合电容,进而对应补偿所述第一扇出线2021和所述第二扇出线2022之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。其中,所述第一走线部204a的宽度和所述耦合部204b的宽度均指所述耦合线204在垂直于其延伸方向上的尺寸。

48.可以理解的,根据所述多条扇出线202之间的电阻差异,可选择所述多条耦合线204中的部分所述耦合线204设置所述耦合部204b,而未设置所述耦合部204b的耦合线204可仅包括所述第一走线部204a。

49.可选地,所述第二连接线2032包括电性连接的第二走线部2032a和连接部2032b,所述连接部2032b的宽度大于所述第一走线部204a、所述第二走线部2032a的宽度。其中,在俯视视角下,所述连接部2032b与所述耦合部204b至少部分重叠,如图2b所示,以增大所述第二连接线2032与所述耦合线204的重叠面积,从而增大所述第二连接线2032与所述耦合

线204的形成的耦合电容,继而对应补偿所述第一扇出线2021和所述第二扇出线2022之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。其中,所述连接部2032b的宽度和所述第二走线部2032a的宽度均指所述连接线203在垂直于其延伸方向上的尺寸。

50.可选地,除通过增加所述第二连接线2032的宽度之外,还可通过增加所述第二连接线2032的长度,以增大所述第二连接线2032的电阻,从而增大所述第二连接线2032与所述耦合线204的形成的耦合电容,继而对应补偿所述第一扇出线2021和所述第二扇出线2022之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。可选地,所述第二连接线2032的长度大于所述第一连接线2031的长度,如图2c所示。可选地,所述第二连接线2032的走线形状可呈蛇形走线形式。

51.可选地,请继续参阅图2a~图2c,所述多条扇出线202还包括多条第三扇出线2023,所述多条第三扇出线2023的电阻自所述第二扇出线2022靠近所述第一扇出线2021的方向上逐渐增大。可选地,所述多条第三扇出线2023的长度自所述第二扇出线2022靠近所述第一扇出线2021的方向上逐渐增大,使得所述多条第三扇出线2023的电阻自所述第二扇出线2022靠近所述第一扇出线2021的方向上逐渐增大。

52.多条信号线201还包括多条第三信号线2013。所述多条连接线203还包括位于所述第一连接线2031和所述第二连接线2032之间的多条第三连接线2033,所述多条第三连接线2033电性连接于所述多条第三信号线2013和所述多条第三扇出线2023之间。

53.可选地,在俯视视角下,所述耦合部204b的宽度自所述第二连接线2032靠近所述第一连接线2031的方向上逐渐减小,所述多条第三连接线2033与所述耦合部204b的重叠面积自所述第二连接线2032靠近所述第一连接线2031的方向上逐渐减小,以在自所述第二连接线2032靠近所述第一连接线2031的方向上,使所述多条第三连接线2033与所述耦合线204之间形成的耦合电容对应所述多条第三扇出线2023的电阻减小,从而对应补偿所述第一扇出线2021、所述第二扇出线2022和所述第三扇出线2023之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。

54.可选地,至少一所述耦合线204包括一所述耦合部204b,所述耦合部204b的宽度自所述第二连接线2032靠近所述第一连接线2031的方向上逐渐减小,以使所述多条第三连接线2033和所述第二连接线2032均与所述耦合部204b重叠。

55.可选地,至少一所述耦合线204包括多个耦合部204b,在自所述第二连接线2032靠近所述第一连接线2031的方向上,多个耦合部204b的面积逐渐减小。可选地,多个耦合部204b包括多个第一耦合部和第二耦合部,每一所述第一耦合部的宽度和/或长度均小于所述第二耦合部的宽度和/或长度,多个所述第一耦合部分的宽度和/或长度自所述第二连接线2032靠近所述第一连接线2031的方向上逐渐减小。其中,在府视视角下,第二连接线2032与所述第二耦合部重叠,所述多条第三连接线2033与所述多个第一耦合部重叠,且在自所述第二连接线2032靠近所述第一连接线2031的方向上,所述第三连接线2033与所述第一耦合部的重叠面积逐渐减小,从而使所述多条第三连接线2033与所述耦合线204之间形成的耦合电容对应所述多条第三扇出线2023的电阻减小,从而对应补偿所述第一扇出线2021、

所述第二扇出线2022和所述第三扇出线2023之间的电阻差异而导致的信号延迟及损耗差异,使得位于所述显示区201a内的所述多条信号线201所传输的信号具有相近的损耗和延迟。

56.请继续参阅图2d,可通过单独改变所述连接线203的长度的形式改善所述多条扇出线202之间的电阻差异。具体的,所述多条扇出线202包括第一扇出线2021、第二扇出线2022和多条第三扇出线2023,所述第一扇出线2021的电阻大于所述第二扇出线2022的电阻,所述多条第三扇出线2023的电阻自所述第二扇出线2022靠近所述第一扇出线2021的方向上逐渐增大。

57.所述多条信号线201包括第一信号线2011、第二信号线2012和多条第三信号线2013。所述多条连接线203包括第一连接线2031、第二连接线2032和多条第三连接线2033,所述第一连接线203电性连接于所述第一信号线2011和所述第一扇出线2021之间,所述第二连接线2032电性连接于所述第二信号线和2012所述第二扇出线2022之间,所述多条第三连接线2033电性连接于所述多条第三信号线2013和所述多条第三扇出线2023之间。

58.其中,所述第二连接线2032的长度大于所述第一连接线2031的长度,所述多条第三连接线2033的长度自所述第二连接线2032靠近所述第一连接线2031的方向上逐渐减小,以使所述多条连接线203之间的电阻差异对应所述多条扇出线202之间的电阻差异实现互补,从而改善显示暗带问题。可选地,所述第二连接线2032的走线形状可呈蛇形走线形式。

59.可选地,在一些实施例中,所述耦合线204的延伸方向可与所述连接线203的延伸方向相同。

60.可以理解的,本领域技术人员可根据实际需求对所述第一扇出线2021、所述第二扇出线2022和所述第三扇出线2023的排布形式进行变更,即所述第一扇出线2021、所述第二扇出线2022和所述第三扇出线2023的排布形式不限于图2a~图2d所示的形式。

61.可以理解的,图2a~图2d均以所述多条扇出线202的长度不同导致的电阻差异为例进行说明,对于换线、所述扇出线202的电阻率差异或受工艺制程等影响致使的所述多条扇出线202的电阻差异导致的暗带问题,本领域技术人员仍可沿用本技术中的所述连接线203和所述耦合线204的设计。

62.可以理解的,所述耦合部204b、所述连接线203、所述耦合线204的长度、延伸方向、形状、宽度等均可根据实际需求进行设置。所述信号线201在所述显示区201a内的延伸方向、形状等也均可根据实际需求进行设置。

63.可选地,所述扇出线202与覆晶薄膜205电性连接。

64.图3a~图3b是本发明实施例提供的显示面板的结构示意图;本发明还提供一种显示面板,所述显示面板包括任一上述的阵列基板300。可选地,所述显示面板包括自发光显示面板,被动式发光显示面板。自发光显示面板包括有机发光二极管、次毫米发光二极管、微型发光二极管等发光器件。被动式发光显示面板包括液晶显示面板、量子点显示面板等。

65.可选地,请继续参阅图3a,所述显示面板还包括:彩膜基板311及框胶312。

66.所述彩膜基板311与所述阵列基板300相对设置。可选地,所述彩膜基板311包括黑色矩阵、彩色滤光片等。

67.所述框胶312位于所述阵列基板300和所述彩膜基板311之间,且所述框胶312位于所述扇出区202a远离所述连接区203a的一侧。

68.由于所述框胶312距所述连接区203a的距离大于所述框胶312距所述扇出区202a的距离,且所述扇出区202a又靠近边缘切割区域。因此,相较于在所述扇出区202a内设置所述耦合线204的设计,在所述连接区203a内设置所述耦合线204可以降低所述耦合线204被水氧侵蚀的风险,可以降低因水氧侵蚀,致使所述耦合线204被腐蚀,影响所述扇出线202电阻差异而导致的信号延迟和损耗差异的补偿效果的优势。

69.此外,由于所述框胶312内还包括用于导电的导电粒子,因此,若将所述耦合线204设置在所述扇出区202a内,则所述耦合线204会经所述框胶312内的导电粒子与所述扇出线202或其他信号产生短路或静电问题,影响显示面板的功能。

70.可选地,所述显示面板还包括位于所述阵列基板300和所述彩膜基板311之间的液晶分子313、配向膜等未示出部分。

71.请继续参阅图3b,所述显示面板还包括:发光器件层321,所述发光器件层321位于所述阵列基板300上,所述发光器件层321包括多个发光器件,所述多个发光器件与所述多条信号线电性连接。

72.可选地,所述阵列基板300包括多个像素驱动电路pe,多个所述像素驱动电路pe与所述多条信号线和所述多个发光器件电性连接,多个所述像素驱动电路pe用于驱动多个所述发光器件发光。

73.可选地,所述像素驱动电路pe包括至少一晶体管,所述信号线与所述晶体管的源极和漏极中的一个电性连接,所述晶体管用于根据所述信号线传输的信号驱动对应的所述发光器件发光。

74.可选地,所述发光器件包括有机发光二极管、次毫米发光二极管、微型发光二极管等。

75.可选地,所述发光器件包括第一电极322、第二电极323及位于所述第一电极322和所述第二电极323之间的发光层324,所述发光层324位于像素定义层325中的像素定义区内。可选地,所述第一电极322与对应的所述像素驱动电路pe所包括的晶体管电性连接,所述第一电极322位于所述第二电极323靠近所述阵列基板300的一侧。

76.如图4a~图4b是仿真结果对比图。其中,以所述信号线201为传输数据信号的数据线为例,图4a是未对所述多条扇出线202之间具有的电阻差异进行补偿所得到的数据信号的变化示意图,图4b是对所述多条扇出线202之间具有的电阻差异采用图2a~图2d所示的方案进行补偿后,所得到的数据信号的变化示意图。

77.将位于所述显示区201a内的所述数据线沿其延伸方向,按与所述扇出区202a的距离的远近划分为远端、中间和近端。在补偿前,由于所述多条扇出线202具有电阻差异,且同一数据信号在同根数据线的不同位置处的损耗表现不同。因此,经具有不同电阻差异的所述扇出线202传输的数据信号被传输至位于所述显示区201a内的所述数据线时,所述数据信号所表现出的信号量并不相同。具体的,如图4a所示,经具有最小电阻的所述扇出线202传输的数据信号被传输至位于所述显示区201a内所述数据线时,所述数据信号所表现出的信号量(如图4a中的l11所示),与经具有最大电阻的所述扇出线202传输的数据信号被传输至位于所述显示区201a内所述数据线时,所述数据信号所表现出的信号量(如图4a中的l12所示)并不相同。无论是在所述数据线的远端、近端还是中间,因所述扇出线202所具有的电阻差异而导致的所述数据信号表现出的信号量差异均存在。而在采用本技术后,无论是在

所述数据线的远端、近端还是中间,因所述扇出线202所具有的电阻差异而导致的所述数据信号表现出的信号量差异均得到改善。具体的,如图4b所示,经具有最小电阻的所述扇出线202传输的数据信号被传输至位于所述显示区201a内所述数据线时,所述数据信号所表现出的信号量(如图4b中的l21所示),与经具有最大电阻的所述扇出线202传输的数据信号被传输至位于所述显示区201a内所述数据线时,所述数据信号所表现出的信号量(如图4b中的l22所示)相同,l21和l22几乎重合,表明因所述扇出线202所具有的电阻差异而导致的所述数据信号表现出的信号量差异均得到改善,故可以改善显示暗带问题。

78.本发明还提供一种显示装置,所述显示装置包括任一上述的驱动电路或任一上述的显示面板。

79.可以理解地,所述显示装置包括可移动显示装置(如笔记本电脑、手机等)、固定终端(如台式电脑、电视等)、测量装置(如运动手环、测温仪等)等。

80.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1