用于将在衬底上制造的设计图案的倍缩掩模增强技术的方法与流程

背景技术:

1、亚微米制造使用光刻技术在衬底上建立材料层,以产生晶体管、二极管、发光二极管(leds)、电容器、电阻器、电感器、传感器、线缆、光缆、微机电系统(mems)以及共同产生提供某种功能的装置的其他元件。衬底光刻是一种印刷工艺,其中掩模(有时称为倍缩掩模)用于将图案转印到衬底以产生装置。在装置(诸如集成电路或平板显示器)的生产或制造中,可使用衬底光刻来制造装置。当待产生的装置是集成电路时,衬底通常是硅晶圆。在产生集成电路的过程中,光刻是半导体光刻,对于大批量生产来说,所述半导体光刻通常是衬底光刻。其他衬底可包括平板显示器、液晶面板显示器、用于平板显示器的掩模、纳米印刷母版或其他衬底,甚至是其他掩模。

2、在半导体光刻中,该掩模或多个掩模可含有电路图案,所述电路图案对应于集成电路的多个图案化工艺中的单个层或一个层的一部分。所述图案可成像到衬底上的某个区域上,所述区域已涂布有称为光致抗蚀剂或抗蚀剂的辐射敏感材料层。一旦图案化层被转印,所述层便可经历各种其他工艺,诸如蚀刻、离子植入(掺杂)、金属化、氧化和抛光。这些工艺用于完成衬底中的单个层。如果需要若干层,则将针对各新层重复整个工艺或其变型。最终,可为集成电路的多个装置的组合将呈现在衬底上。然后可通过切粒或锯切将这些装置彼此分开,然后可安装到单个封装中。

3、光学光刻可以是193nm光(在具有或不具有浸没的情况下)、或极紫外光(euv)或x射线光刻、或任何其他频率的光或其任何组合。

4、使用193nm光波的光学光刻与折射光学器件以及透射光掩模或倍缩掩模一起起作用。掩模选择性地阻挡、部分地阻挡光波或将光波传输到衬底上,所述衬底通常在光刻工艺期间涂布有抗蚀剂以部分地曝光或以曝光衬底的不同部分或衬底上的一些材料。掩模通常是目标衬底尺寸的4倍放大倍率。

5、极紫外光光刻(euv)使用大约13.5nm波长的光和反射光学器件。一些实现方式使用在一个维度具有8倍放大倍率且在另一维度具有4倍放大倍率的变形掩模。

6、一般来讲,更小波长的光能够分辨更精细的几何结构、几何结构之间的更精细空间以及衬底上更高频率(密度)的特征。另外一般来讲,更难以可靠地产生和控制更小波长的光。在经济方面,最佳使用能够分辨装置所需的特征大小、空间和频率的最大波长的光。因此,感兴趣的是利用任何给定波长的光增强衬底上可实现的分辨率。

7、对于特定分辨率的任何光刻,额外技术(诸如离轴照明、相移掩模和多重图案化)扩展分辨率能力。当使用多重图案化时,单个衬底层被曝光多次,每次都使用不同掩模,其称为掩模层。

8、存在许多带电粒子束技术。三种常见类型的带电粒子束光刻是可变形状束(vsb)、字符投影(cp)和多束投影。用于前缘掩模产生的最常用系统是vsb。vsb和cp是成形束带电粒子束光刻的子类别,其中电子束(ebeam)由一系列孔口整形并被引导以对抗蚀剂涂布的表面曝光。出于本公开的目的,射域(shot)是某一表面区域在一段时间内的曝光。所述区域可包含多个不连续的更小区域。射域可由多个其他射域构成,所述多个其他射域可以重叠或可以不重叠并且可以同时曝光或可以不同时曝光。射域可包含指定剂量,或者剂量可以是未指定的。射域可使用整形束、未整形束或整形束与未整形束的组合。多束使用多个带电粒子束,而vsb和cp机器通常具有单个束。

9、对于具有最小特征的掩模层,掩模由电子束光刻产生。在电子束光刻中,电子对涂布掩模表面的光致抗蚀剂的区域或射域进行曝光,所述区域然后被处理以在掩模中产生所要开口。射域中递送的能量称为剂量,按照惯例,在剂量设置为0.0且标称剂量设置为1.0时可能不具有能量。当剂量超过某个阈值时将记录图案,按照惯例,所述阈值通常接近0.5。除其他之外,临界尺寸(cd)变化与抗蚀剂阈值处的剂量曲线的斜率成反比。该反比关系称为边缘斜率或剂量余裕。

10、难以印刷大小类似于或小于用于光刻的光的波长的特征。业界已应用各种技术来解决在衬底上可靠地印刷所要图案的难点。计算光刻领域已出现使用计算增强衬底光刻,衬底光刻在半导体光刻中也称为晶圆光刻。倍缩掩模增强技术(ret)包括计算方法和系统以设计目标倍缩掩模形状,利用所述目标倍缩掩模形状,跨制造变化更精确地且更可靠地将所要图案投影在衬底上。ret通常使用计算来增强掩模上的图像,以更准确地且更可靠地并且对制造变化具有适应力地印刷所要衬底图案。ret中的两种常见技术是光学近接修正(opc)和反向光刻技术(ilt)。该两种技术调整定义掩模的参数,直到衬底上的所要图案在一组或一系列条件下处于可接受公差内为止。常规的opc是基于规则的,即,掩模特征被评估且调整以符合例如与掩模特征的最小宽度、面积和间距以及其他参数有关的一组掩模规则。opc操纵掩模几何结构且调整目标边缘附近的晶圆图案。

11、opc可向掩模图案添加亚分辨率光刻特征,以减少原始物理设计图案(即,设计)与衬底上的最终转印电路图案之间的差异。亚分辨率光刻特征与物理设计中的原始图案并且与彼此相互作用,并且补偿近接效应以改善最终转印电路图案。opc和ilt两者中用以改善图案转印的一个特征是亚分辨率辅助特征(sraf)。通常情况下,sraf的表面制造工艺所需的精度小于意欲印刷在衬底上的图案(通常称为主要特征)所需的精度。当光学光刻的极限正在向亚波长范围远处扩展时,opc特征必定会变得越来越复杂,以便补偿甚至更微妙的相互作用和效应。当成像系统更加靠近其极限时,产生具有足够精细opc特征的倍缩掩模的能力变得至关重要。尽管向掩模图案添加opc特征是有利的,但这也明显增加了掩模图案中的总特征计数。

12、添加opc特征是一项非常繁重的任务,需要很多的计算时间,并且导致更昂贵的倍缩掩模。opc图案不但复杂,而且由于与最小线和空间尺寸相比,光学近接效应是长距离的,因此给定位置中的正确opc图案在很大程度上取决于附近的其他几何结构。即使目标可能是在晶圆上产生完全相同的形状也是如此。这些轻微但至关重要的变化是重要的并且阻止其他人能够形成倍缩掩模图案。常规的做法是,根据主要特征(即,反映opc装饰之前的设计的特征;以及opc特征,其中opc特征可包括sraf)来论述待写入倍缩掩模上的opc装饰图案。为了量化细微变化的含义,邻域之间的opc装饰的典型细微变化可能是主要特征大小的5%至80%。需注意,为清楚起见,opc设计中的变化是所引用的内容。制造变化(诸如圆角)也将呈现在实际的表面图案中。当这些opc变化在晶圆上产生基本上相同的图案时,这意味着晶圆上的几何结构想要在指定误差范围内是相同的,这取决于该几何结构被设计用于执行的功能(例如,晶体管或线缆)的细节。然而,典型的规格是在主要特征范围的2%至50%内。还有许多制造因素会引起变化,但具有该总体误差的opc组件通常在所列范围内。

13、opc形状(诸如亚分辨率辅助特征)受各种设计规则(诸如基于可使用光学光刻转印至晶圆的最小特征的大小的规则)影响。其他设计规则可来自掩模制造工艺,或者如果字符投影带电粒子束写入系统用于在倍缩掩模上形成图案,则其他设计规则可来自模板制造工艺。还需要注意,掩模上sraf特征的准确度要求可低于掩模上主要特征的准确度要求。随着工艺节点继续收缩,光掩模上的最小sraf的大小也收缩。例如,在20nm逻辑工艺节点处,在掩模上需要40nm至60nm sraf以获得最高精度层。

14、ilt通常涉及迭代优化算法。ilt能够将掩模传输作为像素进行操纵,并且ilt通常模拟整个晶圆图案(即,称为密集模拟的工艺),而不是像通常在opc中做的那样仅调整目标边缘附近的形状。ilt的迭代优化算法通常由以下组成:(1)评估提出的解以分配试图被最小化的成本;(2)如果成本低于成本标准,则停止;(3)计算所提出的解的各元素的梯度,这将导致成本降低;(4)根据所计算的梯度调整所提出的解;(5)返回到(1)。成本通常用正值定义,其中零是如在此假设的最佳可能分数。然而,可使用替代的成本定义。

15、一般来讲,ret意欲在标称(预期)制造条件下以及在围绕标称制造条件的预期制造变化内提高所有所要特征的可印刷性。由于制造工艺不完美,因此设计需要适应某些预期制造变化。更大的工艺窗口意味着对制造变化的更强适应性,特别是通过散焦和剂量变化引起的图案偏差在可接受公差内。为尽可能多的特征提供足够的工艺窗口是ret的目的。在制造之后如指定般起作用的芯片的百分比通常称为良率。许多因素影响良率。本领域技术人员通常认为改善工艺窗口与提高良率相关。

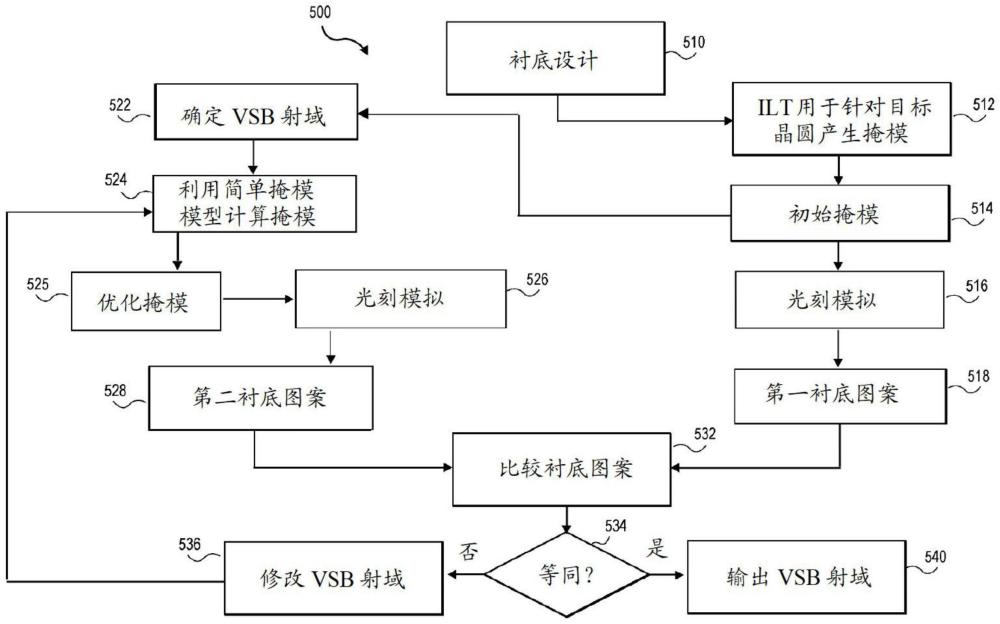

技术实现思路

1、在一些实施方案中,一种用于与可变形状束(vsb)光刻一起使用的倍缩掩模增强技术(ret)的方法包括:输入待在衬底上形成的所要图案;根据所述衬底的所述所要图案确定初始掩模图案;使用vsb曝光系统针对晶圆质量优化所述初始掩模图案,由此产生优化掩模图案;以及输出所述优化掩模图案。

2、在一些实施方案中,一种用于使用可变形状束(vsb)光刻分割表面上的待曝光图案的方法包括:输入初始图案;用二维网格覆盖所述初始图案,其中一组初始vsb射域由所述初始图案与所述网格上的位置的联合形成;合并该组初始vsb射域中的两个或更多个相邻射域以在一组修改后的vsb射域中产生更大射域;以及输出该组修改后的vsb射域。

- 还没有人留言评论。精彩留言会获得点赞!