阵列基板及显示面板的制作方法

本发明涉及显示面板,更具体而言,涉及到一种阵列基板及显示面板。

背景技术:

1、在相关技术中,双栅极线(dual gate)驱动电路结构可以将显示面板中的数据线的数量减少一半,栅极线的数量增加一倍,即,将与数据线连接的源极驱动集成电路数量减半,将与栅极线连接的栅极驱动集成电路的数量加倍。由于栅极驱动集成电路的单价比源极驱动集成电路的单价便宜,降低了显示面板的成本。

2、但是,由于像素电极和栅极线之间绝缘交叠,像素电极和栅极线之间存在寄生电容,像素电极会收到栅极(gate)电压的拉动。而双栅极线驱动电路结构导致各个数据线两侧的像素电压受到不同大小的栅极(gate)电压的拉动,各个像素电极会收到栅极(gate)电压的拉动不一致,导致各个像素电压不一致,显示面板会出现摇头纹(vertical line)的现象,影响了显示面板的显示效果。

技术实现思路

1、本发明实施方式提供一种阵列基板及显示面板。

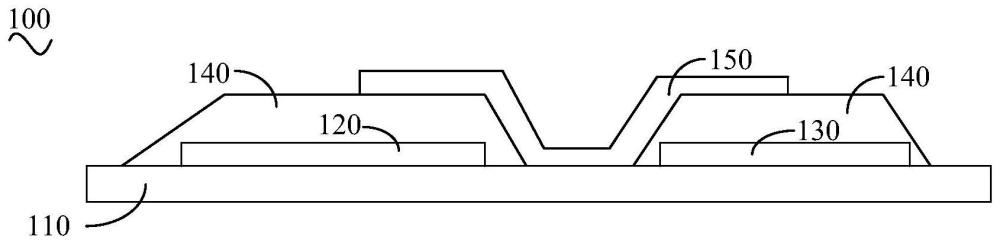

2、本发明实施方式提供的阵列基板形成在基底上。所述阵列基板包括栅极层、像素电极层、复合绝缘层以及隔离金属层。其中,所述栅极层设置在所述基底上,形成有多个栅极。所述像素电极层设置在所述基底上,形成有多个像素电极。所述复合绝缘层设置在所述栅极层和所述像素电极层的上,所述复合绝缘层在相邻的所述栅极和所述像素电极之间形成有空心槽。所述隔离金属层覆盖所述复合绝缘层和所述空心槽,以屏蔽相邻的所述栅极和所述像素电极之间形成的寄生电容。

3、隔离金属层设置在相邻的栅极和像素电极之间,栅极通过复合绝缘层与隔离金属层绝缘隔离,而隔离金属层再通过复合绝缘层和像素电极绝缘隔离。如此,隔离金属层可以屏蔽栅极、像素电极和绝缘金属层形成的寄生电容。

4、在双栅极线(dual gate)驱动电路结构中,像素电极和栅极之间的寄生电容被屏蔽。当栅极(gate)电压跳变时,各个像素电极的电压受到的拉动降低,避免了显示面板的摇头纹(vertical line)现象。

5、在某些实施方式中,所述隔离金属层形成有多个公共电极。

6、隔离金属层复用作为公共电极层,在提高阵列基板制程效率的同时,也屏蔽了栅极和像素电极之间的寄生电容。

7、在某些实施方式中,沿所述栅极与对应的所述像素电极的中心连线方向上,所述公共电极在所述基底上的正投影与对应的所述栅极在所述基底上的正投影交叠的长度大于1.6μm。

8、沿栅极与对应的像素电极的中心连线方向上,公共电极层在基底上的正投影与栅极层在基底上的正投影交叠的长度可以设置为大于1.6μm,公共电极作为隔离金属的时候能够有效地屏蔽栅极。

9、当公共电极层在基底上的正投影与栅极层在基底上的正投影交叠的长度小于1.6μm的时候,栅极的屏蔽效果变差。

10、进一步地,公共电极层在基底上的正投影与栅极层在基底上的正投影交叠的长度可以设置为大于2.1μm,能够更加有效地屏蔽栅极,将栅极和像素电极之间的寄生电容减小至接近于零。

11、在某些实施方式中,沿所述栅极与对应的所述像素电极的中心连线方向上,所述公共电极在所述基底上的正投影与对应的所述像素电极在所述基底上的正投影交叠的长度大于1.6μm。

12、沿栅极与对应的像素电极的中心连线方向上,公共电极层在基底上的正投影与像素电极层在基底上的正投影交叠的长度可以设置为大于1.6μm,公共电极作为隔离金属的时候能够有效地屏蔽像素电极。

13、当公共电极层在基底上的正投影与像素电极层在基底上的正投影交叠的长度小于1.6μm的时候,像素电极的屏蔽效果变差。

14、进一步地,公共电极层在基底上的正投影与像素电极层在基底上的正投影交叠的长度可以设置为大于2.1μm,能够更加有效地屏蔽像素极,将栅极和像素电极之间的寄生电容减小至接近于零。

15、本发明实施方式提供一种显示面板,所述显示面板上述任意一项实施方式的阵列基板。

16、在某些实施方式中,所述显示面板还包括彩膜基板,所述基底上形成有多个凸起部,所述彩膜基板包括多个支撑柱状隔垫物,所述彩膜基板通过所述支撑柱状隔垫物承靠在对应的所述凸起部设置在所述阵列基板上。

17、彩膜基板通过支撑柱状隔垫物承靠在对应的凸起部设置在阵列基板上,防止彩膜基板和阵列基板在受到外力作用时发生位移或形变,避免了显示面板的液晶单元间隙(cell gap)均匀性不良而导致显示面板在视觉上呈现颜色不均匀的现象。

18、在某些实施方式中,所述阵列基板包括源漏极层,形成多个源极和多个漏极,所述凸起部包括所述栅极、所述源极和/或漏极。

19、栅极、源极和漏极都可以复用作为凸起部,在提高阵列基板制程效率的同时,也避免了彩膜基板和阵列基板在受到外力作用时发生位移或形变。

20、在某些实施方式中,所述支撑柱状隔垫物在所述基底的正投影落入所述凸起部在所述基底的正投影内。

21、支撑柱状隔垫物在基底的正投影落入凸起部在基底的正投影内,防止支撑柱状隔垫物滑落出去,确保彩膜基板和阵列基板的位置固定。

22、在某些实施方式中,所述支撑柱状隔垫物在所述基底的正投影边缘与所述凸起部在所述基底的正投影边缘的距离大于3μm。

23、支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离可以设置为大于3μm,可以有效地防止支撑柱状隔垫物滑落出去,确保彩膜基板和阵列基板的位置相对一致。

24、当支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离小于3μm的时候,凸起部的承接效果变差,不能很好地防止支撑柱状隔垫物滑落出去。

25、进一步地,当支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离可以设置为大于4μm,可以更加有效地防止支撑柱状隔垫物滑落出去,确保彩膜基板和阵列基板的位置固定不变。

26、在某些实施方式中,所述支撑柱状隔垫物在所述基底的正投影边缘与所述凸起部在所述基底的正投影边缘的距离小于8μm。

27、支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离可以设置为小于8μm。确保阵列基板和彩膜基板之间的液晶层的透光间隙足够大,进而保障显示面板的透光率足够高,满足显示面板的使用需求。

28、进一步地,支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离可以设置为小于7μm,阵列基板和彩膜基板之间的液晶层的透光间隙足够大,显示面板可以显示更加清晰的画面。

29、当支撑柱状隔垫物在基底的正投影边缘与凸起部在基底的正投影边缘的距离大于8μm的时候,阵列基板和彩膜基板之间的液晶层的透光间隙比较小,显示面板的透光率偏低,显示面板显示的画质差。

30、本发明实施方式一种阵列基板及显示面板。阵列基板形成在基底上。阵列基板包括栅极层、像素电极层、复合绝缘层以及隔离金属层。其中,栅极层设置在基底上,形成有多个栅极。像素电极层设置在基底上,形成有多个像素电极。复合绝缘层设置在栅极层和像素电极层的上方,复合绝缘层在相邻的栅极和像素电极之间形成有空心槽。隔离金属层覆盖复合绝缘层和空心槽,以屏蔽相邻的栅极和像素电极之间形成的寄生电容。

31、隔离金属层设置在相邻的栅极和像素电极之间,栅极通过复合绝缘层与隔离金属层绝缘隔离,而隔离金属层再通过复合绝缘层和像素电极绝缘隔离。如此,隔离金属层可以屏蔽栅极、像素电极和绝缘金属层形成的寄生电容。

32、在双栅极线(dual gate)驱动电路结构中,像素电极和栅极之间的寄生电容被屏蔽。当栅极(gate)电压跳变时,相同颜色的像素电压基本一致,避免了显示面板的摇头纹(vertical line)现象。

33、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!