半导体封装材料和半导体器件的制作方法

1.本发明涉及一种半导体封装材料和半导体器件,并且更具体地,涉及一种用于制造半导体器件的半导体封装材料和半导体器件。

背景技术:

2.通过回流工艺使半导体封装的焊球熔化,然后通过焊接将半导体封装安装在印刷布线板上。无铅焊料用作焊球的材料。这导致回流工艺的温度达到260℃或更高的高温。因此,需要在从常温到约260℃的高温的广泛范围内减小半导体封装的翘曲。

3.通过使用具有根据半导体封装的结构而调整的物理特性的半导体封装材料,可以在一定程度上控制半导体封装的翘曲行为。例如,通过根据半导体封装的结构(在其自身大小和其芯片的大小的方面上)来调整半导体封装材料的成形收缩因子,可以在一定程度上控制半导体封装的翘曲行为。

4.如今,半导体封装的大小和厚度已通过各种封装方法而减小。可以举出诸如晶片级封装(wlp)和薄倒装芯片

‑

芯片大小封装(fc

‑

csp)之类的两种类型的封装作为这样的半导体封装的典型形式。

5.专利文献1公开了用于扇出晶片级封装(fo

‑

wlp)的减小翘曲材料。减小翘曲材料由可固化树脂组合物制成,该可固化树脂组合物包括可以通过活性能量射线和热而固化的成分。当减小翘曲材料通过活性能量射线和热而固化成固化产品的平膜时,固化产品的25℃下的线性膨胀系数d(ppm/℃)、25℃下的弹性模量β(gpa)、以及厚度γ(μm)满足以下关系式:2000≤d

×

β

×

γ≤10000。

6.然而,专利文献1的减小翘曲材料仅可以用于fo

‑

wlp。因此,专利文献1的减小翘曲材料难以减小上述fc

‑

csp的翘曲。特别在fc

‑

csp中,半导体封装中的半导体芯片的体积占有率显著高于已知的fc

‑

csp。因此,在半导体封装的翘曲行为与半导体封装材料的成形收缩因子之间建立相关性变得越来越不可能。

7.引用列表

8.专利文献

9.专利文献1:jp 2018

‑

170500 a

技术实现要素:

10.本公开的目的在于提供一种有助于减小半导体器件的翘曲的半导体封装材料和半导体器件。

11.根据本公开的一方面的半导体封装材料用于制造半导体器件。该半导体器件包括半导体芯片和封装部分。封装部分由半导体封装材料的固化产品制成。封装部分封装半导体芯片。半导体封装材料的由下式(1)给出的应力指数(si)等于或大于8500:

12.13.在式(1)中,e’(t)表示储能模量,cte(t)表示热膨胀系数,并且mold temp.表示成形温度。

14.如果用vc表示半导体芯片的体积并用va表示半导体芯片和封装部分的总体积,则体积vc和总体积va满足下式(2):

[0015][0016]

根据本公开的另一方面的半导体器件包括半导体芯片和封装该半导体芯片的封装部分。封装部分由半导体封装材料的固化产品制成。

附图说明

[0017]

图1是根据本公开的示例性实施例的半导体器件(被实现为fc

‑

csp的第一半导体器件)的示意性横截面图;

[0018]

图2是根据本公开的示例性实施例的半导体器件(被实现为wlp的第二半导体器件)的示意性横截面图;

[0019]

图3是根据本公开的示例性实施例的基板组件的示意性平面图;以及

[0020]

图4是通过将基板组件切割成多片而获得的半导体器件的示意性横截面图。

具体实施方式

[0021]

(1)概述

[0022]

根据本实施例的半导体封装材料用于制造半导体器件1。半导体器件1包括半导体芯片2和封装部分3(例如,参见图1)。封装部分3由半导体封装材料的固化产品制成。封装部分3封装半导体芯片2。

[0023]

由下式(1)给出的半导体封装材料的应力指数(si)等于或大于8500:

[0024][0025]

式(1)中,e’(t)表示储能模量,cte(t)表示热膨胀系数,mold temp.表示成形温度。

[0026]

另外,如果用vc表示半导体芯片2的体积并用va表示半导体芯片2和封装部分3的总体积,则vc和va满足下式(2):

[0027][0028]

在根据本实施例的半导体封装材料中,由于应力指数(si)等于或大于8500,因此封装部分3可以获得显著的收缩力。这允许根据该实施例的半导体封装材料减少半导体器件的翘曲。

[0029]

(2)细节

[0030]

首先将描述半导体器件1(半导体封装),然后将描述半导体封装材料。

[0031]

(2.1)半导体器件

[0032]

(2.1.1)第一实施例

[0033]

图1示出了根据本实施例的半导体器件1(在下文中,被称为“第一半导体器件

11”)。第一半导体器件11包括半导体芯片2、封装部分3和基板5。第一半导体器件11被实现为倒装芯片

‑

芯片大小封装(fc

‑

csp)。

[0034]

半导体芯片2是大致长方体形状的倒装芯片。也就是说,半导体芯片2是已从晶片上切下的作为功能单元的裸半导体芯片。半导体芯片2包括以矩阵布置并用作连接端子的焊料凸块4。

[0035]

半导体芯片2的尺寸不限于特定尺寸。具体地,半导体芯片2的长度可以落在例如从5mm到30mm的范围内。半导体芯片2的宽度可以落在例如从5mm到30mm的范围内。半导体芯片2(不包括焊料凸块4)的厚度(dt)可以落在例如从50μm到500μm的范围内。

[0036]

封装部分3封装半导体芯片2。封装部分3与基板5接合。封装部分3由半导体封装材料的固化产品制成。封装部分3的外形为大致长方体形状。

[0037]

封装部分3的外部尺寸不限于特定外部尺寸。具体地,封装部分3的长度可以落在例如6mm至35mm的范围内。封装部分3的宽度可以落在例如从6mm到35mm的范围内。封装部分3的厚度(mt)可以落入例如从0.15mm到0.5mm的范围内。

[0038]

基板5也被称为封装基板或中介层。尽管基板5不限于特定基板,但是可以给出ets(嵌入式迹线基板)作为基板5的示例。ets是具有内置导体布线的基板。ets也可以是无芯基板。无芯基板是仅由堆积层制成的基板。基板5的厚度(st)没有特别限定,但是例如可以落在例如从0.1mm到0.3mm的范围内。

[0039]

半导体芯片2是倒装安装(和接合)(面朝下安装)到基板5的芯片。具体地,半导体芯片2的焊料凸块4接合到基板5的连接盘(land)。用作连接端子的焊球7以矩阵布置在基板5的未安装半导体芯片2的表面上。

[0040]

半导体芯片2的体积占有率被定义为半导体芯片2相对于半导体芯片2和封装部分3的总体积的体积百分比。具体地,如果用vc表示半导体芯片2的体积并用va表示半导体芯片2和封装部分3的总体积,则用vc/va表示半导体芯片2的体积占有率。本实施例中,vc和va满足下式(2):

[0041][0042]

也就是说,在本实施例中,半导体芯片2的体积占有率以体积计相对于半导体芯片2和封装部分3的总体积为30%或更多。当制造满足这样的条件的半导体器件1时,有利地使用了根据本实施例的半导体封装材料。

[0043]

半导体芯片2的体积占有率的下限值以体积计优选地为35%或更多,更优选地为40%或更多,进一步优选地为45%或更多。可以看出,随着半导体芯片2的体积占有率的下限值增大,封装部分3的体积占有率相应地减小。这有利于减小第一半导体器件11的尺寸和厚度。

[0044]

另一方面,半导体芯片2的体积占有率的上限值以体积计优选地为70%或更小,更优选地为65%或更小,进一步优选地为60%或更小。可以看出,随着半导体芯片2的体积占有率的上限值减小,封装部分3的体积占有率相应地增大。这允许产生更大的收缩力,从而有利于减小第一半导体器件11的翘曲。

[0045]

(2.1.2)第二实施例

[0046]

图2示出了根据第二实施例的半导体器件1(在下文中,被称为“第二半导体器件

12”)。第二半导体器件12包括半导体芯片2、封装部分3和再布线层6。第二半导体器件12被实现为晶片级封装(wlp)。再布线层6是通过使用晶片工艺从半导体芯片2的端子延伸布线而形成的。因此,第二半导体器件12不包括基板5。此外,半导体芯片2也不包括焊料凸块4。由于第二半导体器件12在其他方面具有与上述第一实施例相同的配置,因此在此将省略对其的描述。

[0047]

(2.1.3)第三实施例

[0048]

图3示出了根据第三实施例的基板组件100。图4示出了根据本实施例的半导体器件1(在下文中,被称为“第三半导体器件13”)。当基板组件100被切割成多片时,获得了多个第三半导体器件13。也就是说,第三半导体器件13是通过所谓的map(成形阵列工艺)而形成的。在map工艺中,基板组件100是通过将多个半导体芯片2安装在单个基板5的一个表面上使得每个产品区域包括半导体芯片2中的一个半导体芯片2,并通过用半导体芯片封装材料共同封装这些半导体芯片2而获得的。然后,通过将基板组件100切削(切割)成与产品区域相同数量的片来获得第三半导体器件13。在以下说明中,将不再重复描述与上述第一实施例具有相同配置的构成要素,而仅描述与第一实施例的不同。

[0049]

基板组件100包括多个半导体芯片2、封装部分3和基板5。

[0050]

基板5的外部尺寸不限于特定尺寸。基板5的长度(fs2)可以落在例如从100mm到300mm的范围内。基板5的宽度(fs1)可以落在例如从30mm到80mm的范围内。

[0051]

每个半导体芯片2的尺寸与针对第一实施例描述的尺寸相同。多个半导体芯片2以矩阵状布置在单个基板5的一个表面上,并且通过管芯附接膜8与其接合。管芯附接膜8的厚度没有特别限定,但是可以落在例如从10μm到30μm的范围内。

[0052]

封装部分3封装多个半导体芯片2。封装部分3与基板5接合。封装部分3由半导体封装材料的固化产品制成。封装部分3的外形为大致长方体形状。

[0053]

封装部分3的外部尺寸不限于特定外部尺寸。具体地,封装部分3的长度(ma2)可以落在例如从90mm到290mm的范围内。封装部分3的宽度(ma1)可以落在例如从25mm到75mm的范围内。

[0054]

在基板组件100中,多个半导体芯片2的体积占有率被定义为多个半导体芯片2相对于多个半导体芯片2和封装部分3的总体积的体积百分比。在本实施例中,多个半导体芯片2的体积占有率相对于多个半导体芯片2和封装部分3的总体积以体积计为30%或更大。注意,基板组件100中的多个半导体芯片2的体积占有率低于第三半导体器件13中的单个半导体芯片2的体积占有率。这是因为基板组件100具有用于切削的划线(切削余量)。

[0055]

多个半导体芯片2的体积占有率的下限值以体积计优选地为32%或更大,更优选地为35%或更大,进一步优选地为38%或更大。可以看出,随着多个半导体芯片2的体积占有率的下限值增大,封装部分3的体积占有率相应地减小。这有利于减小基板组件100的大小和厚度。这也有利于减小第三半导体器件13的大小和厚度。

[0056]

另一方面,多个半导体芯片2的体积占有率的上限值以体积计优选地为70%或更小,更优选地为65%或更小,进一步优选地为60%或更小。可以看出,随着多个半导体芯片2的体积占有率的上限值减小,封装部分3的体积占有率相应地增大。这允许产生更大的收缩力,从而有利于减小基板组件100的翘曲。这也有助于减小第三半导体器件13的翘曲。

[0057]

在基板组件100中,当每对相邻的半导体芯片2被切削且被切割成多片时,获得了

多个第三半导体器件13。第三半导体器件13的半导体芯片2的体积占有率与针对第一实施例描述的体积占有率相同。

[0058]

(2.2)半导体封装材料

[0059]

根据本实施例的半导体封装材料用于制造半导体器件1。半导体器件1的实施例包括第一半导体器件11、第二半导体器件12、第三半导体器件13和基板组件100。半导体封装材料用于形成封装部分3。

[0060]

半导体封装材料的应力指数(si)可以通过下式(1)获得:

[0061][0062]

式(1)中,e’(t)表示储能模量,cte(t)表示热膨胀系数,并且mold temp.表示成形温度。

[0063]

式(1)中的储能模量e’(t)是温度的函数,并且可以通过动态机械分析(dma)进行测量。在这种情况下,储能模量(e’(t))的单位是gpa。同时,式(1)中的热膨胀系数(cte(t))是温度的函数,并且可以通过热机械分析(tma)进行测量。在这种情况下,热膨胀系数(cte(t))的单位是ppm/℃。成形温度可以但不必是例如175℃。注意,应力指数(si)是评估指标,并且不具有特定单位。

[0064]

如上所述,应力指数(si)是通过在35℃到成形温度的范围内对温度的函数进行积分而获得的值,该函数是作为储能模量(e

′

(t))和热膨胀系数(cte(t))的乘积而获得的。因此,在应力指数(si)中考虑了半导体封装材料的玻璃化转变温度(tg)的影响。为此,应力指数(si)允许更准确地评估半导体器件1的封装部分3的收缩力。

[0065]

应力指数(si)是有效地用于评估其中半导体芯片2具有高体积占有率的类型的半导体器件1的翘曲行为的指标。具体地,应力指数(si)对于评估半导体芯片2的体积占有率以体积计为30%或更大的半导体器件1的翘曲行为特别有效。另外,应力指数(si)尤其可有效地用于评估第一半导体器件11的翘曲行为。

[0066]

具体地,半导体封装材料的由式(1)给出的应力指数(si)等于或大于8500。这允许封装部分3获取显著的收缩力,从而减小半导体器件1的翘曲。特别地,在第一半导体器件11中,由于半导体芯片2与基板5之间的热膨胀系数的不匹配,很可能会引起所谓的“凸翘曲”(也被称为“cry翘曲”)。尽管如此,如果应力指数(si)等于或大于8500,则即使封装部分3的体积占有率很小,封装部分3也可以获得显著的收缩力。这可以减少第一半导体器件11的凸翘曲。

[0067]

应力指数(si)可以通过式(1)在分析上获得,但是也可以在数值上获得。为了在数值上获得应力指数(si),对于储能模量(e

′

(t))和热膨胀系数(cte(t))中的每一个,在从35℃到成形温度的恒定步长(例如,5℃的步长)下获得测量值。接下来,将相同温度下的储能模量(e’(t))和热膨胀系数(cte(t))的相应测量值相乘以获得乘积。最后,将乘积一起积分以获得应力指数(si)。

[0068]

为了在数值上获得应力指数(si),优选地在从35℃到成形温度(175℃)的5℃的步长下获得测量值。在这种情况下,应力指数(si)的下限值优选地为8500或更大,更优选地为8600或更大,进一步优选地为8700或更大。同时,应力指数(si)的上限值优选地为17000或更小,更优选地为16000或更小,进一步优选地为15000或更小。

[0069]

半导体封装材料可以包含热固性树脂。热固性树脂不限于特定热固性树脂,但是可以包括环氧树脂基固化剂和酚醛树脂基固化剂。环氧树脂不限于特定环氧树脂,但是可以举出联苯型环氧树脂和三酚甲烷型环氧树脂作为环氧树脂的示例。

[0070]

半导体封装材料还可以包含固化促进剂以加速热固性树脂的固化。尽管固化促进剂不限于特定固化促进剂,但是可以给出三苯基膦作为固化促进剂的示例。

[0071]

半导体封装材料可以包含无机填料,用于调节其储能模量、热膨胀系数和机械强度。如果半导体封装材料包含无机填料,则无机填料的含量以质量计相对于半导体封装材料的总质量优选地落在从55%到85%的范围内。这进一步减小了半导体器件1的翘曲。

[0072]

无机填料的含量的下限值以质量计更优选地为57%或更大,进一步优选地为60%或更大。同时,无机填料的含量的上限值以质量计更优选地为83%或更小,进一步优选地为80%或更小。

[0073]

无机填料可以包括氢氧化镁和/或氢氧化铝。如果半导体封装材料包含氢氧化镁和/或氢氧化铝,则氢氧化镁和/或氢氧化铝的含量以质量计相对于半导体封装材料的总质量优选地为10%或更大。这进一步减小了半导体器件1的翘曲。

[0074]

氢氧化镁和/或氢氧化铝的含量的下限值以质量计更优选地为11%或更大,进一步优选地为12%或更大。同时,氢氧化镁和/或氢氧化铝的含量的上限值以质量计优选地为80%或更小,更优选地为75%或更小,进一步优选地为70%或更小。

[0075]

如果半导体封装材料包含无机填料,则半导体封装材料还可以包含硅烷偶联剂以提高热固性树脂与无机填料之间的粘合性。尽管硅烷偶联剂不限于特定硅烷偶联剂,但是可以给出3

‑

环氧丙氧基丙基三甲氧基硅烷作为硅烷偶联剂的示例。

[0076]

半导体封装材料还可以包含离子清除剂以去除腐蚀性离子。离子清除剂也被称为无机离子交换剂。

[0077]

半导体封装材料还可以包含颜料以对封装部分3进行着色。尽管颜料不限于特定颜料,但是可以给出炭黑作为颜料的示例。

[0078]

半导体封装材料的固化产品在260℃下的弯曲模量优选地落在从0.1gpa到0.9gpa的范围内。这进一步减小了半导体器件1的翘曲。特别地,当通过map工艺制造半导体器件1时,可以减小基板组件100在切割之前的翘曲。减小基板组件100的翘曲允许基板组件100上的各种后续工艺顺利进行。

[0079]

半导体封装材料的固化产品的成形收缩因子优选地落在从0.35%到1.3%的范围内。这进一步减小了半导体器件1的翘曲。

[0080]

成形收缩因子的下限值更优选地为0.38%或更大,进一步优选地为0.40%或更大。同时,成形收缩因子的上限值更优选地为1.28%或更小,进一步优选地为1.26%或更小。

[0081]

(3)变型例

[0082]

在上述实施例中,fc

‑

csp被例示为第一半导体器件11且wlp被例示为第二半导体器件12。然而,半导体器件1不限于这些类型。其他类型的半导体器件的示例包括诸如sip(系统级封装)的模块型半导体器件和组合使用布线连接和倒装芯片接合的混合型半导体器件。

[0083]

在上述实施例中,通过map工艺制造第三半导体器件13。然而,也可以通过map工艺

制造第一半导体器件11和第二半导体器件12。

[0084]

(总结)

[0085]

从实施例的前述描述中可以看出,本发明具有以下方面。在以下描述中,将附图标记插入括号中只是为了阐明本公开的以下方面与上述示例性实施例之间的构成要素的对应关系。

[0086]

根据第一方面的半导体封装材料用于制造半导体器件(1)。半导体器件(1)包括半导体芯片(2)和封装部分(3)。封装部分(3)由半导体封装材料的固化产品制成。封装部分(3)封装半导体芯片(2)。由下式(1)给出的半导体封装材料的应力指数(si)等于或大于8500:

[0087][0088]

式(1)中,e’(t)表示储能模量,cte(t)表示热膨胀系数,并且mold temp.表示成形温度。

[0089]

如果用vc表示半导体芯片(2)的体积并用va表示半导体芯片(2)和封装部分(3)的总体积,则体积vc和总体积va满足下式(2):

[0090][0091]

该方面允许减小半导体器件(1)的翘曲。

[0092]

在可以与第一方面结合实现的根据第二方面的半导体封装材料中,半导体封装材料的固化产品在260℃下的弯曲模量在从0.1gpa到0.9gpa的范围内。

[0093]

该方面允许进一步减小半导体器件(1)的翘曲。特别地,当通过map工艺制造半导体器件(1)时,可以减小基板组件(100)在切割之前的翘曲。

[0094]

在可以与第一方面或第二方面结合实现的根据第三方面的半导体封装材料中,半导体封装材料的固化产品的成形收缩因子落在从0.35%到1.3%的范围内。

[0095]

该方面允许进一步减小半导体器件(1)的翘曲。

[0096]

可以与第一方面至第三方面中的任一方面结合实现的根据第四方面的半导体封装材料包含无机填料。无机填料的含量以质量计相对于半导体封装材料的总质量落在从55%到85%的范围内。

[0097]

该方面允许进一步减小半导体器件(1)的翘曲。

[0098]

在可以与第四方面结合实现的第五方面的半导体封装材料中,无机填料包括氢氧化镁和/或氢氧化铝。氢氧化镁和/或氢氧化铝的含量以质量计相对于半导体封装材料的总质量为10%或更大。

[0099]

该方面允许进一步减小半导体器件(1)的翘曲。

[0100]

根据第六方面的半导体器件(1)包括半导体芯片(2)和封装半导体芯片(2)的封装部分(3)。封装部分(3)由根据第一方面至第五方面中的任一方面的半导体封装材料的固化产品制成。

[0101]

该方面允许减小半导体器件(1)的翘曲。

[0102]

示例

[0103]

将通过示例的方式详细地描述本公开。注意,本公开不限于以下示例。

[0104]

1.半导体封装材料

[0105]

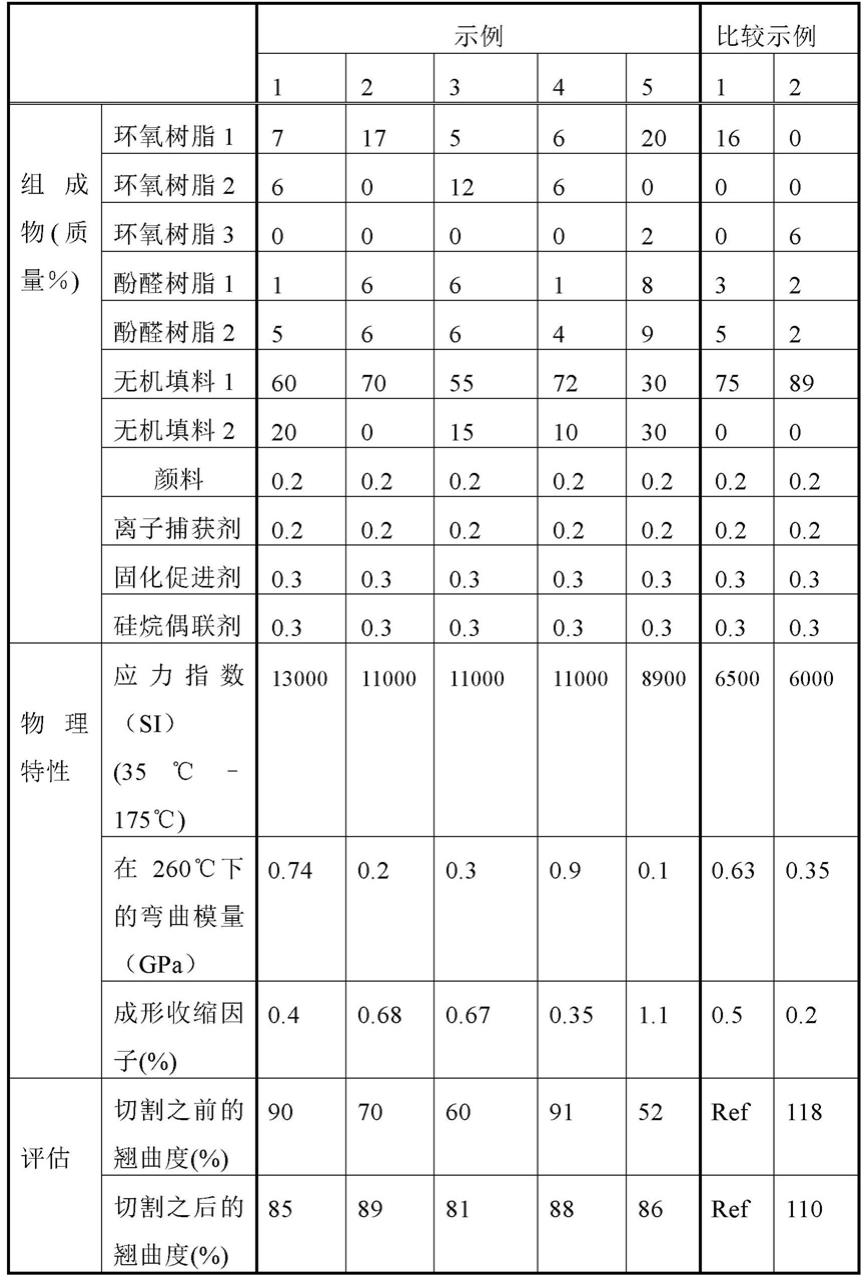

通过将表1的“组成物”栏中所示的成分混合来获得半导体封装材料。注意,表1中所示的成分的细节如下:

[0106]

环氧树脂1:联苯型环氧树脂,nc

‑

3000,nippon kayaku co.,ltd.制造,环氧当量为265

‑

285g/eq;

[0107]

环氧树脂2:三酚甲烷型环氧树脂,eppn

‑

501hy,nippon kayaku co.,ltd.制造,环氧当量为163

‑

175g/eq;

[0108]

环氧树脂3:联苯型环氧树脂,yx4000,三菱化学公司制造,环氧当量为180

‑

192g/eq;

[0109]

酚醛树脂1:mehc

‑

7851,meiwa plastic industries,ltd.制造,oh当量为201

‑

220g/eq;

[0110]

酚醛树脂2:mehc

‑

7800

‑

m,meiwa plastic industries,ltd.制造,oh当量为167

‑

180g/eq;

[0111]

无机填料1:二氧化硅,fb

‑

5sdc,denka company limited.制造,平均粒径(d50)为4.1μm;

[0112]

无机填料2:氢氧化镁,kisuma 8sn,kyowa chemical industry co.,ltd.制造,平均粒径为1.48μm;

[0113]

颜料:炭黑,ma600,三菱化学公司制造,粒径为20nm(算术平均直径);

[0114]

离子捕获剂:ixe

‑

700f(镁,铝基),toagosei co.,ltd.制造;

[0115]

固化促进剂:三苯基膦,hokuko tpp,hokko chemical industry co.,ltd.制造;以及

[0116]

硅烷偶联剂:3

‑

缩水甘油丙氧基三甲氧基硅烷,kbm

‑

403,shin

‑

etsu chemical co.,ltd制造。

[0117]

2.物理特性

[0118]

(1)应力指数

[0119]

(dma)

[0120]

由半导体封装材料形成的试验片(具有5mm

×

50mm

×

1mm的尺寸)从25℃到280℃以5℃/min的速率升高其温度,并且使用热机械分析仪(日立高科技公司制造的“dma7100”)以10hz的频率测量试验片的储能模量e’(t)(单位:gpa)。储能模量(e’(t))的测量值是从25℃起在5℃的步长下获得的。

[0121]

(tma)

[0122]

由半导体封装材料形成的试验片(具有φ5mm

×

1mm的尺寸)从25℃到280℃以5℃/min的速率升高其温度,并且使用热机械分析仪(日立高科技公司制造的“tma7100”)在

‑

1g的荷重下测量试验片的热膨胀系数(cte(t))(单位:ppm/℃)。热膨胀系数(cte(t))的测量值是从25℃起在5℃的步长下获得的。

[0123]

(计算)

[0124]

在计算应力指数(si)时,使用了在从35℃到175℃(成形温度)的范围内的相应温度下测量的存储模量e

′

(t)(gpa)和热膨胀系数(cte(t))(ppm/℃)的值。将在相同温度下测量的储能模量(e’(t))和热膨胀系数(cte(t))的各个值相乘在一起以获得乘积。应力指数

(si)是通过将这些乘积一起积分而获得的。如前所述,应力指数(si)是评估指标,并且不具有特定单位。

[0125]

(2)弯曲模量

[0126]

使用autograph万能试验机(shimadzu corporation制造的“ag

‑

is”)在260℃下测量由半导体封装材料形成的试验片(具有80mm

×

10mm

×

4mm的尺寸)的弯曲模量。弯曲模量是在包括支点间距离为64mm、试验速率为2mm/min的条件下测量的。

[0127]

(3)成形收缩因子

[0128]

使用半导体封装材料通过转印成形形成试验片。成形工艺在包括管芯直径为80mm、管芯温度为175℃、注入压力为6.9mpa、以及成形时间为150秒的条件下进行的。测量了由此形成的试验片的直径,并且基于试验片相对于管芯直径的尺寸来计算成形收缩率。

[0129]

3.评估

[0130]

(1)基板组件

[0131]

制造了如图3中所示的基板组件100。具体地,基板组件100是通过将多个(4

×

16个)半导体芯片2安装在单个基板5的一个表面上使得每个产品区域包括半导体芯片2中的一个半导体芯片,并通过用半导体芯片封装材料共同封装这些半导体芯片2而获得的。通过使用成形机(towa corporation制造的“fft”)来执行共同封装。其他细节如下:

[0132]

‑

基板:ets,无芯,三层(残铜率分别为55%、70%和60%);

[0133]

‑

基板的长度(fs2):220.0mm;

[0134]

‑

基板的宽度(fs1):60.0mm;

[0135]

‑

基板的厚度(st):110μm;

[0136]

‑

半导体芯片的长度:12.4mm;

[0137]

‑

半导体芯片的宽度:10.9mm;

[0138]

‑

半导体芯片的厚度(dt):150μm;

[0139]

‑

多个半导体芯片的体积占有率:以体积计42.0%;

[0140]

‑

管芯附接膜的厚度:15μm;

[0141]

‑

封装部分的长度(ma2):213.6mm;

[0142]

‑

封装部分的宽度(ma1):53.6mm;

[0143]

‑

封装部分的厚度(mt):270μm;以及

[0144]

‑

基板组件的厚度(pt):380μm。

[0145]

(2)切割之前的翘曲

[0146]

基板组件100在175℃下进行二次固化6小时。另外,基板组件100在回流炉中加热,从而使基板组件100在从160℃到200℃的范围的温度下保持加热1分30秒,并且在260℃的最高温下加热10秒。然后,将基板组件100放置在平坦的表面上以用尺子测量其四个角处的相应上升高度,并且计算了如此测量的四个角处的上升高度的平均值并将其视为切割之前的翘曲。注意,在表1中,示例1

‑

5和比较示例2中的每个示例中的切割之前的翘曲度指示对于假设比较示例1的切割之前的翘曲度为100%(ref)的相对值。

[0147]

(3)切割之后的翘曲

[0148]

通过将基板组件100切割成多片而获得64个如图4中所示的第三半导体器件13。通过使用3d加热表面轮廓测量系统(akrometric llc制造的“thermomoire ps200”)测量从25

℃到260℃的温度范围内的第三半导体器件13的共面性值,并且计算了这些共面性值的平均值并将其视为切割之后的翘曲度。注意,在表1中,示例1

‑

5和比较示例2中的每个示例中的切割之前的翘曲度指示对于假设比较示例1的切割之前的翘曲度为100%(ref)的相对值。第三半导体器件13的其他细节如下:

[0149]

‑

半导体芯片的体积占有率:以体积计51.9%;

[0150]

‑

第三半导体器件的长度:12.8mm;

[0151]

‑

第三半导体器件的宽度:11.3mm;以及

[0152]

‑

第三半导体器件的厚度(pt):270μm。

[0153]

[表1]

[0154][0155]

如从表1中可以看出的,与比较示例1、2中的应力指数(si)值相比,示例1

‑

5中的每个示例的应力指数(si)等于或大于8500。这表明在示例1

‑

5中减小了切割前后的翘曲。注意,切割之前的翘曲和切割之后的翘曲均为凸翘曲。

[0156]

附图标记列表

[0157]

1 半导体器件

[0158]

2 半导体芯片

[0159]

3 封装部分。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1