半导体封装制造工艺用胶带及其制造方法与流程

1.本发明涉及半导体封装制造工艺用胶带,更详细地,涉及如下的半导体封装制造工艺用胶带:当进行半导体封装的电磁干扰(emi,electro magnetic interference)屏蔽层形成工艺时,有效地保护半导体封装的下表面及形成于半导体封装的下表面的多个突出电极。

背景技术:

2.作为在半导体封装中执行与外部的端子接触的方式,在以往,广泛使用引脚网格阵列(pga,pin grid array)方式或引脚框架(lead frame)方式,但近来广泛使用球状网格阵列(bga,ball grid array)方式。

3.bga方式通过利用在半导体封装的底面突出形成的多个突出电极,即,焊球(solder ball)来实现与外部的端子接触,相比于以往的pga方式或引脚框架方式,可传递更多的信号。

4.bga方式因这种特性,用作新一代高速存储器的主要封装类型,将限定于移动电话或数码相机等便携式信息通信设备的芯片级封装(csp,chip scale package)的使用领域扩张至个人计算机(pc)或工作台等的计算机领域。

5.另外,在如移动电话的移动领域中,为了增强终端的便携性,减少终端的大小的必要性增加,由此,为了减少终端的大小,减少在终端中所占比重相对大的印制电路板(pcb,printed circuit board)的大小的必要性增加。

6.但是,若减少pcb的大小,则包括在pcb的半导体器件之间的间隔变窄,由此,不可避免地发生半导体器件相互之间的电磁波干扰引起的误差。为了抑制这种器件之间的电磁波干扰,研发及引入覆盖器件屏蔽用帽(cap)的方法或通过电磁干扰溅射技术在器件的外表面形成屏蔽用金属涂敷的技术。其中,通过溅射的屏蔽用金属涂敷技术是指通过溅射工艺,向除半导体器件的联接端子之外的剩余外表面形成用于屏蔽电磁波的金属薄膜。

7.与此相关地,作为与进行用于bga类型半导体封装的电磁波屏蔽的溅射工艺时不影响联接端子的方法相关的现有技术,公开了韩国授权专利公报第10-1501735号(专利文献1)及韩国授权专利公报第10-1662068号(专利文献2)。

8.专利文献1涉及半导体封装的电磁干扰屏蔽处理工艺,其特征在于,包括:胶带附着步骤,在框架的下表面附着胶带的边缘,在框架的内周形成胶带;胶带切割步骤,在上述胶带以规定间隔形成孔;半导体封装粘结设置步骤,将半导体封装的下表面边缘配置于胶带的上表面来将上述半导体封装以规定间隔粘结设置于胶带的上表面,使得形成于半导体封装的下表面的凸点插入于胶带的孔中;以及涂敷步骤,在上述胶带的上部进行涂敷作业来对粘结于胶带的上表面的半导体封装及胶带的上表面进行涂敷处理,由此,除半导体封装的下表面之外的5面进行涂敷。

9.但是,在专利文献1中公开的技术,在胶带中以规定间隔形成孔的胶带切割步骤中具有发生过多费用的风险,在半导体封装粘结设置步骤中,当未将半导体封装准确地配置

于胶带的孔时,在通过电磁干扰溅射进行屏蔽用金属涂敷时,具有薄膜不良沉积的问题。

10.现有技术文献

11.专利文献1:韩国授权专利公报第10-1501735号(2015年03月05日授权)

12.专利文献2:韩国授权专利公报第10-1662068号(2016年09月27日授权)

技术实现要素:

13.技术问题

14.为解决前述的问题,本发明的目的在于,提供一种半导体封装制造工艺用胶带,其中,粘结特性、保持特性、分离特性及应力特性优秀,当进行配置有多个突出电极的半导体封装的电磁干扰屏蔽层形成工艺时,有效地保护半导体封装的下表面及形成于半导体封装的下表面的多个突出电极。

15.并且,本发明的目的在于,提供一种半导体封装制造工艺用胶带,其中,第一基膜包含塑料材料或金属材料,由此,当进行电磁干扰屏蔽层形成工艺时,与形成有多个突出电极的半导体封装下表面的拓扑对应,有效保持应力均衡,并容易确保半导体封装制造工艺用胶带所需的应力特性。

16.并且,本发明的目的在于,提供一种半导体封装制造工艺用胶带,其中,第一粘结层包含丙烯酸类共聚物来在高温下具有优秀的耐热性,由此减少脱气现象,适当支撑金属材料的第二基膜的形态变形,以防止第二基膜撕裂,并且,即使第二基膜被撕裂,很好地包围第二基膜来有效地保护多个突出电极,且第一粘结层具有强于第二粘结层的粘合力,在电磁干扰屏蔽层形成工艺结束后,当从半导体封装分离胶带时,在第二粘结层中分离。

17.并且,本发明的目的在于,提供一种半导体封装制造工艺用胶带,其中,第二基膜包含金属材料,由此,防止可在第一粘结层中产生的气泡传递至第二粘结层,由于充足的保持特性,当在半导体封装的下表面附着时,以与半导体封装下表面的拓扑对应的方式改变形态后,可保持工艺之间的变形的形态。

18.并且,本发明的目的在于,提供一种半导体封装制造工艺用胶带,其中,第二粘结层包含具有螺旋网状结构的硅,由此,在半导体封装的下表面与突出电极相接触的区域,向半导体封装与胶带之间赋予充足的粘结特性,即使产生孔隙,也可防止真空状态的制造工艺之间的孔隙过度膨胀。

19.技术方案

20.本发明实施例的半导体封装制造工艺用胶带附着于形成有多个突出电极的半导体封装的下表面,上述半导体封装制造工艺用胶带包括:第一基膜;第一粘结层,层叠于上述第一基膜的上部,并包含丙烯酸类共聚物;第二基膜,层叠于上述第一粘结层的上部,并包含金属材料,以与上述半导体封装下表面的拓扑对应的方式改变形态后,保持工艺之间的变形的形态;以及第二粘结层,层叠于上述第二基膜的上部,包含具有螺旋网状结构的硅。

21.在此情况下,优选地,上述第一基膜包含塑料材料或金属材料。

22.此时,优选地,上述第一基膜以聚对苯二甲酸乙二醇酯(polyethylene terephthalate)、聚酰亚胺(polyimide)或聚烯烃(polyolefin)中的一种的单层或层叠两种以上的多层结构形成,具有10μm至150μm范围的厚度。

23.并且,优选地,上述第一基膜包含至少99重量百分比以上的铝(al)来具有4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度、6.4%至19.2%范围的伸长率及20μm至80μm范围的厚度,或者包含至少99重量百分比以上的铜(cu)来具有8kgf/mm2至31.2kgf/mm2范围的拉伸强度、3.2%至14.4%范围的伸长率及20μm至80μm范围的厚度。

24.另外,优选地,上述第一粘结层包含丙烯酸丁酯(butyl acrylate)-甲基丙烯酸丁酯(butyl methacrylate)-甲基丙烯酸(methacrylic acid)-甲基丙烯酸甲酯(methyl methacrylate)-苯乙烯(styrene)共聚物以及丙烯酸(acrylic acid)-丙烯酸2-乙基己酯(2-ethylhexyl acrylate)-甲基丙烯酸2-乙基己酯(2-ethylhexyl methacrylate)-甲基丙烯酸缩水甘油酯(glycidyl methacrylate)共聚物中的一种以上。

25.在此情况下,优选地,上述第一粘结层通过将25重量份至30重量份的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物、70重量份至75重量份的乙酸乙酯的第一粘合组合物及25重量份至30重量份的丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物、50重量份至55重量份的甲苯、15重量份至20重量份的乙酸乙酯的第二粘合组合物中的一种以上与环氧固化剂相混合并涂敷在上述第一基膜后,进行干燥及固化来形成。

26.在此情况下,优选地,上述第一粘结层通过将80重量份至120重量份的上述第一粘合组合物及0.5重量份至1.5重量份的上述环氧固化剂相混合并涂敷在上述第一基膜后,进行干燥及固化来形成。

27.并且,优选地,上述第一粘结层通过将40重量份至60重量份的上述第一粘合组合物、40重量份至60重量份的上述第二粘合组合物及0.5重量份至1.5重量份的上述环氧固化剂相混合并涂敷在上述第一基膜后,进行干燥及固化来形成。

28.另外,优选地,上述第一粘结层具有100μm至700μm范围的厚度及至少500gf/25mm以上的粘合力,上述第二粘结层具有10μm至50μm范围的厚度及50gf/25mm至500gf/25mm范围的粘合力。

29.在此情况下,优选地,在上述第一粘结层中,厚度随着上述突出电极的尺寸增加而在所设置的厚度范围内减少,厚度随着上述突出电极之间的间隔增加而在所设置的厚度范围内增加,在上述第二粘结层中,厚度随着上述突出电极的尺寸增加而在所设置的厚度范围内增加,厚度随着上述突出电极之间的间隔增加而在所设置的厚度范围内减少。

30.另外,优选地,上述第二基膜具有1μm至10μm范围的厚度。

31.另外,优选地,上述第二基膜包含至少99重量百分比以上的铝来具有4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度、6.4%至19.2%范围的伸长率及10μm至35μm范围的厚度,或者包含至少99重量百分比以上的铜来具有8kgf/mm2至31.2kgf/mm2范围的拉伸强度、3.2%至14.4%范围的伸长率及10μm至35μm范围的厚度。

32.另外,优选地,上述第二粘结层包含三甲基化二氧化硅(trimethylated silica)-二甲基硅氧烷(dimethyl siloxane)共聚物。

33.另外,本发明实施例的半导体封装制造工艺用胶带的制造方法包括:第一胶带准备步骤,制造第一胶带及第二胶带,上述第一胶带依次层叠有包含塑料材料或金属材料的第一基膜、包含丙烯酸类共聚物的第一粘结层及包含氟的第一离型膜,上述第二胶带依次层叠有包含金属材料的第二基膜、包含具有螺旋网状结构的硅的第二粘结层及包含氟的第

二离型膜;以及第一胶带贴合步骤,从上述第一胶带去除上述第一离型膜,通过使上述第一粘结层与上述第二基膜面接触来使上述第一胶带与上述第二胶带贴合。

34.另外,本发明另一实施例的半导体封装制造工艺用胶带的制造方法包括:第二胶带准备步骤,制造第一胶带、第三胶带及第四胶带,上述第一胶带依次层叠有包含塑料材料或金属材料的第一基膜、包含丙烯酸类共聚物的第一粘结层及包含氟的第一离型膜,上述第三胶带通过金属沉积方式在第三离型膜形成上述第二基膜,上述第四胶带依次层叠有包含具有螺旋网状结构的硅的第二粘结层及包含氟的第二离型膜;以及第二胶带贴合步骤,从上述第一胶带去除上述第一离型膜,通过使上述第一粘结层与上述第三胶带的上述第二基膜面接触来使上述第一胶带与上述第三胶带贴合,从上述第三胶带去除上述第三离型膜,通过使第二基膜与上述第四胶带的上述第二粘结层面接触来使上述第三胶带与上述第四胶带贴合。

35.发明的效果

36.如上所述,在本发明的半导体封装制造工艺用胶带中,粘结特性、保持特性、分离特性及应力特性优秀,当进行配置有多个突出电极的半导体封装的电磁干扰屏蔽层形成工艺时,有效地保护半导体封装的下表面及形成于半导体封装的下表面的多个突出电极。

37.并且,在本发明的半导体封装制造工艺用胶带中,第一基膜包含塑料材料或金属材料,由此,当进行电磁干扰屏蔽层形成工艺时,与形成有多个突出电极的半导体封装下表面的拓扑对应,有效保持应力均衡,并容易确保半导体封装制造工艺用胶带所需的应力特性。

38.并且,在本发明的半导体封装制造工艺用胶带中,第一粘结层包含丙烯酸类共聚物来在高温下具有优秀的耐热性,由此减少脱气现象,适当支撑金属材料的第二基膜的形态变形,以防止第二基膜撕裂,并且,即使第二基膜被撕裂,很好地包围第二基膜来有效地保护多个突出电极,且第一粘结层具有强于第二粘结层的粘合力,在电磁干扰屏蔽层形成工艺结束后,当从半导体封装分离胶带时,在第二粘结层中分离。

39.并且,在本发明的半导体封装制造工艺用胶带中,第二基膜包含金属材料,由此,防止可在第一粘结层中产生的气泡传递至第二粘结层,由于充足的保持特性,当在半导体封装的下表面附着时,以与半导体封装下表面的拓扑对应的方式改变形态后,可保持工艺之间的变形的形态。

40.并且,在本发明的半导体封装制造工艺用胶带中,第二粘结层包含具有螺旋网状结构的硅,由此,在半导体封装的下表面与突出电极相接触的区域,向半导体封装与胶带之间赋予充足的粘结特性,即使产生孔隙,也可防止真空状态的制造工艺之间的孔隙过度膨胀。

附图说明

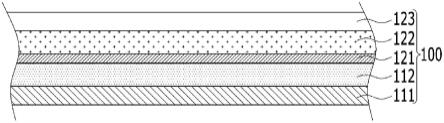

41.图1为示出本发明实施例的半导体封装制造工艺用胶带的截面形状的图。

42.图2为示出从图1中所示的半导体封装制造工艺用胶带去除第二离型膜后粘结于半导体封装的下表面的截面形状的图。

43.图3为用于说明本发明实施例的半导体封装制造工艺用胶带的制造方法的流程图。

44.图4为用于说明本发明第一实施例的半导体封装制造工艺用胶带的制造方法的图。

45.图5为用于说明本发明第二实施例的半导体封装制造工艺用胶带的制造方法的图。

46.(附图标记的说明)

47.10:半导体封装

48.11:突出电极

49.100:半导体封装制造工艺用胶带

50.110:第一胶带

51.111:第一基膜

52.112:第一粘结层

53.113:第一离型膜

54.120:第二胶带

55.121:第二基膜

56.122:第二粘结层

57.123:第二离型膜

58.130:第三胶带

59.131:第三离型膜

60.140:第四胶带

具体实施方式

61.在本发明中,为了与现有技术的差别及明确性以及便于掌握技术,附图可由夸张的表达示出。并且,后述的术语为考虑本发明中的功能而定义的术语,可根据使用人员、操作人员的意图或惯例不同,因此,需根据本说明书全文的技术内容定义这些术语。另外,实施例仅为在本发明的发明要求范围中提出的结构要素的例示性事项,并不限定本发明的权利范围,应根据本发明的说明书全文的技术思想解释权利范围。

62.图1为示出本发明实施例的半导体封装制造工艺用胶带的截面形状的图,图2为示出从图1中所示的半导体封装制造工艺用胶带去除第二离型膜后粘结于半导体封装的下表面的截面形状的图,图3为用于说明本发明实施例的半导体封装制造工艺用胶带的制造方法的流程图,图4为用于说明本发明第一实施例的半导体封装制造工艺用胶带的制造方法的图,图5为用于说明本发明第二实施例的半导体封装制造工艺用胶带的制造方法的图。

63.在详述本发明的实施例之前,通常,在进行电磁干扰屏蔽层形成工艺时使用的半导体封装制造工艺用胶带具有确保粘结特性(adhesion characteristic)、保持特性(retention characteristic)、分离特性(remove characteristic)及应力特性(stress characteristic)的必要性。

64.首先,根据粘结特性方面,胶带的基膜及粘结层需与突出电极的尺寸(例如,直径或高度)无关地与突出电极及包括突出电极的半导体封装下表面的拓扑(topology)对应来粘结及紧贴,从而防止在半导体封装的下表面与突出电极相接触的区域产生孔隙(air gap)。同时,胶带需在用于形成电磁干扰屏蔽层的工艺环境,例如,高温及高真空环境中,很

好地粘附而不推动突出电极。即,胶带需在电磁干扰屏蔽层形成工艺环境中也持续保持粘结能力及紧贴能力。

65.之后,根据保持特性方面,胶带应保持粘结能力及密封能力,由此,在电磁干扰屏蔽层形成工艺条件下,在没有自改性、变形、变色及脱气(outgassing)的情况下,保持原型,并且,防止工艺之间的气体及颗粒渗透至胶带与半导体封装粘结面之间。同时,当进行电磁干扰屏蔽层形成工艺时,当在半导体封装的下表面与突出电极相接触的区域中产生孔隙时,胶带应防止工艺之间(尤其,高真空环境的工艺时)孔隙过于膨胀。

66.接着,根据分离特性方面,当完成电磁干扰屏蔽层形成工艺后在常温及大气压状态下从半导体封装分离时,胶带以小的力也容易分离,并且,在半导体封装的下表面及突出电极的表面并不残留粘结物质。尤其,胶带需具备可通过从胶带自动分离半导体封装(或芯片)的自动化设备容易分离半导体封装(或芯片)的粘合力,不能通过在自动化设备中使用的真空吸盘(vacuum chuck)或升降销(lift pin)产生孔或被撕裂。通常,从胶带自动分离半导体封装(或半导体芯片)的自动化设备的最大容许张力约为500gf/25mm,因此,在分离特性方面,优选地,胶带具有小于其的粘合力。

67.并且,根据应力特性方面,当进行电磁干扰屏蔽层形成工艺时,在胶带上放置及粘结多个半导体封装,即,多个半导体芯片,因此,胶带需确保适当水平的拉伸应力及压缩应力,以将相邻的半导体芯片之间的间隔保持恒定的状态下进行电磁干扰屏蔽层形成工艺。即,胶带稳定地保持拉伸状态,并且,与包括突出电极的半导体封装下表面的拓扑对应来保持应力平衡(stress balance)。

68.参照图1及图2,本发明实施例的半导体封装制造工艺用胶带100涉及附着在形成有多个突出电极11的半导体封装10下表面的半导体封装制造工艺用胶带100。

69.如前所述,本发明实施例的半导体封装制造工艺用胶带100为了确保进行电磁干扰屏蔽层形成工艺时所需的粘结特性、保持特性、分离特性及应力特性而创造。

70.首先,本发明实施例的半导体封装制造工艺用胶带100包括第一基膜111、第一粘结层112、第二基膜121以及第二粘结层122。

71.在此情况下,本发明实施例的半导体封装制造工艺用胶带100还可包括第二离型膜123,对于上述第二离型膜123,在本发明实施例的半导体封装制造工艺用胶带的制造方法中进行更加详细地说明。

72.上述第一基膜111包含塑料材料或金属材料。

73.在此情况下,塑料材料的上述第一基膜111以对聚对苯二甲酸乙二醇酯、聚酰亚胺或聚烯烃中的一种的单层或层叠两种以上的多层结构形成。

74.此时,上述第一基膜111可具有10μm至150μm范围的厚度。在上述第一基膜111中,在其厚度小于10μm的情况下,使用人员可能很难处理本发明实施例的半导体封装制造工艺用胶带100,在其厚度大于150μm的情况下,难以与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来保持应力平衡。

75.另外,优选地,金属材料的上述第一基膜111包含至少99重量百分比以上的铝来具有4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度、6.4%至19.2%范围的伸长率及20μm至80μm范围的厚度,或者包含至少99重量百分比以上的铜来具有8kgf/mm2至31.2kgf/mm2范围的拉伸强度、3.2%至14.4%范围的伸长率及20μm至80μm范围的厚度。

76.在此情况下,为了在包含99重量百分比以上的铝或99重量百分比以上的铜的同时满足前述的拉伸强度范围及伸长率范围,上述第一基膜111可包含1重量百分比以下的添加物。添加物可包含选自硅(si)、铁(fe)、锰(mn)、镁(mg)、锌(zn)及钛(ti)组成的组中的一种或两种以上。

77.另外,上述第一基膜111在包含99重量百分比以上的铝的同时满足4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度的原因在于,在拉伸强度小于4.8kgf/mm2的情况下,可能出现上述半导体封装100的制造工艺之间无法没有拉长且稳定地保持拉紧状态的现象,在拉伸强度大于14.4kgf/mm2的情况下,难以与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来保持应力平衡。

78.并且,上述第一基膜111在包含99重量百分比以上的铝的同时满足6.4%至19.2%范围的伸长率的原因在于,在伸长率小于6.4%的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第一基膜111的形态,在伸长率大于19.2%的情况下,难以持续保持工艺之间的上述第一基膜111变形的形态。

79.另外,上述第一基膜111在包含99重量百分比以上的铜的同时满足8kgf/mm2至31.2kgf/mm2范围的拉伸强度的原因在于,在拉伸强度小于8kgf/mm2的情况下,可能出现上述半导体封装100的制造工艺之间无法没有拉长且稳定地保持拉紧状态的现象,在拉伸强度大于31.2kgf/mm2的情况下,难以与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来保持应力平衡。

80.并且,上述第一基膜111在包含99重量百分比以上的铜的同时满足3.2%至14.4%范围的伸长率的原因在于,在伸长率小于3.2%的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第一基膜111的形态,在伸长率大于14.4%的情况下,难以持续保持工艺之间的上述第一基膜111变形的形态。

81.另外,金属材料的上述第一基膜111可具有10μm至150μm范围的厚度。在上述第一基膜111中,在其厚度小于20μm的情况下,使用人员非常难以处理本发明实施例的半导体封装制造工艺用胶带100,在其厚度大于80μm的情况下,难以与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来保持应力平衡。

82.上述第一基膜111由如上所述的材料及结构形成,由此,当进行电磁干扰屏蔽层形成工艺时,与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来有效保持应力平衡,容易确保半导体封装制造工艺用胶带所需的应力特性。即,上述第一基膜111由如上所述的材料及结构形成,由此具有如下的特性:可稳定地保持上述半导体封装100的制造工艺之间无法没有拉长且稳定地保持拉紧状态,并且,可与形成有上述突出电极11的上述半导体封装10下表面的拓扑对应来保持应力平衡,在高温及高真空环境下,改性及变形发生得小。同时,上述第一基膜111通过包含塑料材料或金属材料来防止存在于外部的气泡(气体、颗粒)传递至上述第一粘结层112。

83.上述第一粘结层112层叠于上述第一基膜111的上部,包含丙烯酸类共聚物。

84.优选地,上述第一粘结层112具有比上述第二粘结层122更厚的厚度,并具有比上述第二粘结层122的粘合力更强的粘合力。更详细地,上述第一粘结层112可具有100μm至700μm范围的厚度及至少500gf/25mm以上的粘合力。即,上述第一粘结层112可具有100μm至700μm范围的厚度及至少500gf/25mm以上的粘合力,例如,可具有500gf/25mm至2500gf/

25mm范围的粘合力,从而在内部浸渍上述突出电极11。

85.其中,在上述第一粘结层112中,在其厚度小于100μm的情况下,可能降低向上述半导体封装制造工艺用胶带100浸渍上述突出电极11来提供对于工艺之间的上述突出电极11的缓冲感的能力,在其厚度大于700μm的情况下,可降低上述半导体封装10的下表面与上述半导体封装制造工艺用胶带100之间的粘结能力、密封能力及保持特性。

86.并且,在上述第一粘结层112中,在其粘合力小于500gf/25mm情况下,当从上述半导体封装10去除上述半导体封装制造工艺用胶带100时,可产生在上述第一粘结层112中发生剥离的不良,在其粘合力大于2500gf/25mm的情况下,上述第一粘结层112的粘合力具有与其厚度成正比的特性,因此,难以实现上述半导体封装制造工艺用胶带100所需的上述第一粘结层112的厚度。

87.在材料方面,优选地,上述第一粘结层112包含丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物及丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物中的至少一种以上。此时,在两种丙烯酸类共聚物中,可改变各单体的结合顺序,结合方式可具有交替共聚物(alternating copolymer)、块状共聚物(block copolymer)、无规则共聚物(random copolymer)、全同共聚物(isotactic copolymer)、间规共聚物(syndiotactic copolymer)、无规共聚物(atactic copolymer)等,并不限定于特定结合方式。

88.另外,优选地,上述第一粘结层112通过将25重量份至30重量份的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物、70重量份至75重量份的乙酸乙酯的第一粘合组合物及25重量份至30重量份的丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物、50重量份至55重量份的甲苯、15重量份至20重量份的乙酸乙酯的第二粘合组合物中的一种以上与环氧固化剂相混合并涂敷在上述第一基膜111后,进行干燥及固化来形成。

89.在此情况下,在上述第一粘结层112中,若作为上述第一粘合组合物的粘结主剂的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物小于25重量份,则具有如下的问题:降低粘合力及耐热性,并且,变得过于软,使得所执行的缓冲作用不足,从而使上述第二基膜121被撕裂,若作为上述第一粘合组合物的粘结主剂的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物大于30重量份,则具有如下的问题:变得过于硬,使得缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态,变形之后,因膨胀难以独自保持变形的形态。

90.并且,在上述第一粘结层112中,若作为上述第一粘合组合物的溶剂的乙酸乙酯小于70重量份,则具有如下的问题:上述第一粘合组合物的粘度过于高,难以与上述第二粘合组合物及上述环氧固化剂相混合,并且,在涂敷过程中,使上述第一粘结层112的表面变得粗糙,并且,在干燥及固化过程中发生较多的脱气现象,从而降低上述第一粘结层112的特性,若作为上述第一粘合组合物的溶剂的乙酸乙酯大于75重量份,则具有如下的问题:上述第一粘合组合物的粘度过于低,因此,在涂敷过程中,上述第一粘结层112难以形成充足的厚度,从而降低上述第一粘结层112的缓冲特性。

91.并且,在上述第一粘结层112中,若作为上述第二粘合组合物的粘结主剂的丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物小于25重量

份,则具有如下的问题:降低粘合力及耐热性,并且,变得过于软,使得所执行的缓冲作用不足,从而使上述第二基膜121被撕裂,若作为上述第二粘合组合物的粘结主剂的丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物大于30重量份,则具有如下的问题:变得过硬,使得缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态,变形之后,因膨胀难以独自保持变形的形态。

92.并且,在上述第一粘结层112中,若作为上述第二粘合组合物的溶剂的甲苯与乙酸乙酯之和小于65重量份,则具有如下的问题:上述第二粘合组合物的粘度过于高,难以与上述第一粘合组合物及上述环氧固化剂相混合,并且,在涂敷过程中,使上述第一粘结层112的表面变得粗糙,并且,在干燥及固化的过程中发生较多的脱气现象,从而降低上述第一粘结层112的特性,若作为上述第二粘合组合物的溶剂的甲苯与乙酸乙酯之和大于75重量份,则具有如下的问题:上述第二粘合组合物的粘度过于低,因此,在涂敷过程中,上述第一粘结层112难以形成充足的厚度,从而降低上述第一粘结层112的缓冲特性。

93.另外,优选地,在上述第一粘结层112中,上述第一粘结层112通过将80重量份至120重量份的上述第一粘合组合物及0.5重量份至1.5重量份的上述环氧固化剂相混合并涂敷在上述第一基膜111后,进行干燥及固化来形成。

94.在此情况下,在上述第一粘结层112中,若上述第一粘合组合物小于80重量份,则具有如下的问题:降低粘合力及耐热性,并且,变得过于硬,使得所执行的缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态,若上述第一粘合组合物大于120重量份,则具有如下的问题:变得过于软,使得所执行的缓冲作用不足,从而使上述第二基膜121被撕裂。

95.并且,在上述第一粘结层112中,若上述环氧固化剂小于0.5重量份,则具有如下的问题:未进行充足的固化而变得过于软,使得所执行的缓冲作用不足,从而使上述第二基膜121被撕裂,若上述环氧固化剂大于1.5重量份,则具有如下的问题:变得过于硬,使得所执行的缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态。

96.另外,优选地,上述第一粘结层112通过将40重量份至60重量份的上述第一粘合组合物、40重量份至60重量份的上述第二粘合组合物及0.5重量份至1.5重量份的上述环氧固化剂相混合并涂敷在上述第一基膜111后,进行干燥及固化来形成。

97.在此情况下,在上述第一粘结层112中,若上述第一粘合组合物小于40重量份,则具有如下的问题:降低粘合力及耐热性,并且,变得过于硬,使得所执行的缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态,若上述第一粘合组合物大于60重量份,则具有如下的问题:变得过于软,使得所执行的缓冲作用不足,从而使上述第二基膜121被撕裂。

98.并且,在上述第一粘结层112中,若上述环氧固化剂小于0.5重量份,则具有如下的问题:未进行充足的固化而变得过于软,使得所执行的缓冲作用不足,由此使上述第二基膜121被撕裂,若上述环氧固化剂大于1.5重量份,则具有如下的问题:变得过于硬,使得所执行的缓冲作用不足,由此,难以与上述半导体封装10下表面的拓扑对应来改变形态。

99.在上述第一粘结层112中,关于保持特性,因材料特性而在高温具有优秀的耐热性,减少脱气现象,适当支撑金属材料的上述第二基膜121的形态变形,由此,防止上述第二基膜121被撕裂,并且,即使上述第二基膜121被撕裂,也很好地包裹其来有效地保护上述突

出电极11。

100.并且,在上述第一粘结层112中,关于分离特性,具有比上述第二粘结层122更强的粘合力,因此,完成电磁干扰屏蔽层形成工艺后,当从上述半导体封装10分离上述半导体封装制造工艺用胶带100时,在上述第二粘结层122中进行分离。

101.另外,优选地,上述第一粘结层112具有100μm至700μm范围的厚度,厚度随着上述突出电极11的尺寸的增加而在所设置的厚度范围内减少,并且,厚度随着上述突出电极11之间的间隔的增加而在所设置的厚度范围内增加。

102.上述第一粘结层112的厚度随着上述突出电极11的尺寸的增加而在所设置的厚度范围内减少的原因在于,在相同环境中,上述第二粘结层122的厚度增加,因此,使上述半导体封装制造工艺用胶带100的整个厚度保持得恒定,并且,将上述半导体封装10的制造工艺中所需的上述半导体封装制造工艺用胶带100的粘结特性、分离特性、保持特性及应力特性保持得恒定。

103.并且,上述第一粘结层112的厚度随着上述突出电极11之间的间隔增加而在所设置的厚度范围内增加的原因在于,在相同环境中,上述第二粘结层122的厚度减少,因此,使上述半导体封装制造工艺用胶带100的整个厚度保持得恒定,并且,将上述半导体封装10的制造工艺所需的上述半导体封装制造工艺用胶带100的粘结特性、分离特性、保持特性及应力特性保持得恒定。尤其,在上述突出电极11之间的间隔增加的情况下,与上述第二粘结层122粘结的上述半导体封装10的下表面的面积增加,在进行电磁干扰屏蔽层形成工艺后,不易去除上述半导体封装制造工艺用胶带100,或者在上述半导体封装10的下表面残留粘结物质的可能性大,因此,减少上述第二粘结层122的厚度,并降低与上述半导体封装10的下表面的粘合力。

104.上述第二基膜121层叠于上述第一粘结层112的上部,以与上述半导体封装10下表面的拓扑对应的方式改变形态后,以保持工艺之间的变形的形态的方式包含金属材料。

105.作为一实施例,优选地,上述第二基膜121具有1μm至10μm范围的厚度。这是因为,在上述第二基膜210的厚度小于1μm的情况下,使用人员非常难以处理上述半导体封装制造工艺用胶带100,并且,难以保持变形的形态,在上述第二基膜121的厚度大于10μm的情况下,难以与形成有上述突出电极11的半导体封装10下表面的拓扑对应来改变形态,并难以保持应力平衡。与后述的其他实施例不同地,这种范围的厚度在上述突出电极11的大小大的情况下有利。

106.例如,上述第二基膜121通过金属沉积方式将铝或铜沉积在离型膜,并以金属沉积的转印膜形态制造后,可贴合于上述第一粘结层112。对此,在关于本发明第二实施例的半导体封装制造工艺用胶带100的制造方法s100的说明部分进行更加详细的说明。

107.另外,作为另一实施例,优选地,上述第二基膜121包含至少99重量百分比以上的铝来具有4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度(tensile strength)、6.4%至19.2%范围的伸长率(elongation)及10μm至35μm范围的厚度,或者包含至少99重量百分比以上的铜来具有8kgf/mm2至31.2kgf/mm2范围的拉伸强度、3.2%至14.4%范围的伸长率及10μm至35μm范围的厚度。

108.更详细地,针对上述第二基膜121,当进行上述半导体封装10的制造工艺时,以与形成有上述突出电极11的半导体封装10下表面的拓扑对应的方式改变形态后,可单独保持

变形的形态,能够以在高温及高真空环境中不发生改性及变形的方式包含99重量百分比以上的铝或99重量百分比以上的铜。

109.在此情况下,为了在包含99重量百分比以上的铝或99重量百分比以上的铜的同时满足前述的拉伸强度范围及伸长率范围,上述第二基膜121可包含1重量百分比以下的添加物。添加物可包含选自由硅、铁、锰、镁、锌及钛组成的组中的一种或两种以上。

110.另外,上述第二基膜121在包含99重量百分比以上的铝的同时满足4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度的原因在于,在拉伸强度小于4.8kgf/mm2的情况下,因进行上述半导体封装制造工艺用胶带100的制造工艺及电磁干扰屏蔽层形成工艺时施加的外力,可发生上述第二基膜121断裂或撕裂的现象,在拉伸强度大于14.4kgf/mm2的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第二基膜121的形态。

111.并且,上述第二基膜121在包含99重量百分比以上的铝的同时满足6.4%至19.2%范围的伸长率的原因在于,在伸长率小于6.4%的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第二基膜121的形态,在伸长率大于19.2%的情况下,难以持续保持工艺之间的上述第二基膜121变形的形态。

112.另外,上述第二基膜121在包含99重量百分比以上的铜的同时满足8kgf/mm2至31.2kgf/mm2范围的拉伸强度的原因在于,在拉伸强度小于8kgf/mm2的情况下,因进行上述半导体封装制造工艺用胶带100的制造工艺及电磁干扰屏蔽层形成工艺时施加的外力,可发生上述第二基膜121断裂或撕裂的现象,在拉伸强度大于31.2kgf/mm2的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第二基膜121的形态。

113.并且,上述第二基膜121在包含99重量百分比以上的铜的同时满足3.2%至14.4%范围的伸长率的原因在于,在伸长率小于3.2%的情况下,难以与上述半导体封装10下表面的拓扑对应来改变上述第二基膜121的形态,在伸长率大于14.4%的情况下,难以持续保持工艺之间的上述第二基膜121变形的形态。

114.另外,上述第二基膜121可具有10μm至35μm范围的厚度。原因在于,在上述第二基膜210的厚度小于10μm的情况下,使用人员非常难以处理上述半导体封装制造工艺用胶带100,在上述第二基膜121的厚度大于35μm的情况下,难以与形成有上述突出电极11的半导体封装10下表面的拓扑对应来改变形态,并难以保持应力平衡。与前述的一实施例不同地,这种范围的厚度在上述突出电极11的大小小的情况下有利。

115.上述第二基膜121包含金属材料,由此,防止可在上述第一粘结层112产生的气泡(气体、颗粒)传递至上述第二粘结层122,由于充足的保持特性,当将上述半导体封装制造工艺用胶带100附着在上述半导体封装10的下表面时,以与上述半导体封装10下表面的拓扑对应来改变形态后,保持工艺之间的变形的形态。即,上述第二基膜121包含金属材料,由此,防止在上述第一粘结层112中产生的气体等传递至上述第二粘结层122,支撑上述第二粘结层122保持平坦,由此,在高温及高真空环境下,持续保持与配置有上述突出电极11的上述半导体封装10的下表面的粘结能力及紧贴能力。

116.上述第二粘结层122层叠于上述第二基膜121的上部,包含具有螺旋网状结构的硅。

117.优选地,上述第二粘结层122具有小于上述第一粘结层112的厚度,且具有弱于上述第一粘结层122的粘合力的粘合力。更详细地,上述第二粘结层122可具有10μm至50μm范

围的厚度及50gf/25mm至500gf/25mm范围的粘合力,以毫无缝隙地沿着形成有上述突出电极11的上述半导体封装10下表面的拓扑粘结。

118.其中,在上述第二粘结层122中,在其厚度小于10μm的情况下,无法确保所需的粘合力,在工艺过程中,与上述半导体封装10的下表面的粘结能力、密封能力及保持特性降低,由此,可发生剥离现象,在其厚度大于50μm的情况下,当附着于上述半导体封装10的下表面时,由于挤压压力,上述第二粘结层122朝向侧面挤出,发生不良,或者在完成工艺后,可发生难以从上述半导体封装10去除的问题。

119.并且,在上述第二粘结层122中,在其粘合力小于50gf/25mm的情况下,在电磁干扰屏蔽层形成工艺的高温及高真空工艺环境中,发生上述第二粘结层122从上述半导体封装10的下表面及上述突出电极11挤出而剥离的现象,或者可发生工艺之间的气体及颗粒渗透至上述第二粘结层122与上述半导体封装10的粘结面之间的现象,在其粘合力大于500gf/25mm的情况下,进行电磁干扰屏蔽层形成工艺后,在常温及大气压状态下,难以从上述半导体封装10去除,或者可发生在上述半导体封装10的下表面及上述突出电极11的表面残留粘结物质的问题。

120.材料方面,优选地,上述第二粘结层122包含三甲基化二氧化硅-二甲基硅氧烷共聚物。

121.上述第二粘结层122包含三甲基化二氧化硅-二甲基硅氧烷共聚物,由此,降低进行电磁干扰屏蔽层形成工艺时产生的热量引起的物性变形,并容易确保半导体封装制造工艺用胶带所需的粘结特性、保持特性、分离特性及应力特性。

122.进而,在上述第二粘结层122中,将硅氧烷键作为基本骨架,具有螺旋网状结构(spiral network structure)作为分子结构,因此,即使在上述半导体封装10的下表面及上述突出电极11与上述第二粘结层122之间产生孔隙,也可在高温及高真空环境下防止孔隙过于膨胀。

123.另外,优选地,上述第二粘结层122具有10μm至50μm范围的厚度,厚度随着上述突出电极11的尺寸的增加而在所设置的厚度范围内增加,厚度随着上述突出电极11之间的间隔增加而在所设置的厚度范围内减少。

124.上述第二粘结层122的厚度随着上述突出电极11的尺寸的增加而在所设置的厚度范围内增加的原因在于,随着上述突出电极11的尺寸的增加,发生上述第二粘结层122从上述突出电极11挤出而剥离的现象的可能性大,因此,用于提高上述第二粘结层122的粘合力。

125.并且,上述第二粘结层122的减少随着上述突出电极11之间的间隔的增加而在所设置的厚度范围内增加的原因在于,随着上述突出电极11之间的间隔的增加,与上述第二粘结层122粘结的半导体封装10的下表面的面积增加,由此,进行电磁干扰屏蔽层形成工艺后,不易去除上述第二粘结层122,或者,可发生在上述半导体封装10的下表面残留粘结物质的问题,因此,用于降低上述第二粘结层122的粘合力。

126.在上述第二粘结层122中,关于粘结特性,包含具有螺旋网状结构的硅,由此,在上述半导体封装10的下表面与上述突出电极11相接的区域赋予充足的粘结特性,关于分离特性,具有弱于上述第一粘结层112的粘合力,由此,进行电磁干扰屏蔽层形成工艺后,当从上述半导体封装10去除上述半导体封装制造工艺用胶带100时,从上述第二粘结层122分离,

而不是从上述第一粘结层112分离。

127.如上所述,本发明的半导体封装制造工艺用胶带100的粘结特性、保持特性、分离特性及应力特性优秀,当进行配置有多个上述突出电极11的上述半导体封装10的电磁干扰屏蔽层形成工艺时,在上述半导体封装的下表面10及上述半导体封装10的下表面有效保护多个上述突出电极11。

128.以下,参照图3至图5,对本发明实施例的半导体封装制造工艺用胶带100的制造方法s100进行说明。

129.分为第一实施例及第二实施例进行说明,首先,对于在本发明实施例的半导体封装制造工艺用胶带100中详述的结构,将省略部分重复的说明。

130.本发明实施例的半导体封装制造工艺用胶带100的制造方法s100包括胶带准备步骤s110以及胶带贴合步骤s120。

131.第一实施例

132.本发明第一实施例的半导体封装制造工艺用胶带100的制造方法s100包括第一胶带准备步骤s111及第一胶带贴合步骤s121。

133.上述第一胶带准备步骤s111为制造第一胶带110以及第二胶带120的步骤,上述第一胶带110依次层叠有包含塑料材料或金属材料的上述第一基膜111、包含丙烯酸类共聚物的上述第一粘结层112以及包含氟的第一离型膜113,上述第二胶带120依次层叠有包含金属材料的上述第二基膜121、包含具有螺旋网状结构的硅的第二粘结层122以及包含氟的第二离型膜123。

134.首先,制造上述第一胶带110的方法从制造商准备包含塑料材料或金属材料的上述第一基膜111的过程开始。如前所述,上述第一基膜111可包含至少99重量百分比以上的铝来具有4.8kgf/mm2至14.4kgf/mm2范围的拉伸强度、6.4%至19.2%范围的伸长率及20μm至80μm范围的厚度,或者可包含至少99重量百分比以上的铜来具有8kgf/mm2至31.2kgf/mm2范围的拉伸强度、3.2%至14.4%范围的伸长率及20μm至80μm范围的厚度。或者,上述第一基膜111以聚对苯二甲酸乙二醇酯、聚酰亚胺或聚烯烃中的一种的单层或层叠两种以上的多层结构形成,可具有10μm至150μm范围的厚度。

135.接着,制造商可将25重量份至30重量份的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物、70重量份至75重量份的乙酸乙酯的上述第一粘合组合物(80重量份至120重量份)及上述环氧固化剂(0.5重量份至1.5重量份)注入至混合容器中,通过搅拌作业混合,或者可将25重量份至30重量份的丙烯酸丁酯-甲基丙烯酸丁酯-甲基丙烯酸-甲基丙烯酸甲酯-苯乙烯共聚物、70重量份至75重量份的乙酸乙酯的上述第一粘合组合物(40重量份至60重量份)、25重量份至30重量份的丙烯酸-丙烯酸2-乙基己酯-甲基丙烯酸2-乙基己酯-甲基丙烯酸缩水甘油酯共聚物、50重量份至55重量份的甲苯、15重量份至20重量份的乙酸乙酯的上述第二粘合组合物(40重量份至60重量份)及上述环氧固化剂注入至混合容器,通过搅拌作业混合。此时,通过搅拌作业的混合工艺可在常温及正常湿度条件下执行。

136.此时,制造商使搅拌混合有上述第一粘合组合物及上述环氧固化剂的丙烯酸类组合物或搅拌混合有上述第一粘合组合物、上述第二粘合组合物及环氧固化剂的丙烯酸类组合物稳定化。丙烯酸类组合物的稳定化用于去除丙烯酸类组合物中的气泡,同时,诱导丙烯

酸类组合物的化学稳定性及均匀的交联反应。作为丙烯酸类组合物的稳定化的一方案,为了去除丙烯酸类组合物中的气泡,可进行超声波处理或真空吸入,去除气泡后,为了丙烯酸类组合物的稳定化,可使制造4小时至12小时的丙烯酸类组合物在热平衡状态下休止。优选地,为了确保化学稳定性且防止快速的交联反应,丙烯酸类组合物的稳定化在热平衡状态下进行。

137.接着,制造商通过如下的方式形成上述第一粘结层112:利用缺角轮涂布机(comma coater)、槽模涂布机(slot-die coater)、凹版涂布机(gravure coater)等向上述第一基膜111上涂布稳定化的丙烯酸类组合物后,进行干燥及固化。

138.此时,制造商利用缺角轮涂布机、槽模涂布机、凹版涂布机等,能够以与上述第一粘结层112的最终厚度相比更厚的方式将丙烯酸类组合物涂布在上述第一基膜111上。具体地,可控制缺角轮涂布机、槽模涂布机、凹版涂布机等以相比于上述第一粘结层112的目标厚度,厚2.5倍至3.5倍的方式涂布丙烯酸类组合物。例如,在上述第一粘结层112的目标厚度为100μm至700μm范围的情况下,可控制缺角轮涂布机以250μm至2450μm范围的涂布厚度涂布丙烯酸类组合物。向上述第一基膜111上涂布稳定化的丙烯酸类组合物的方法还可由旋涂法或喷射法等执行。

139.接着,制造商可通过干燥热处理及熟成固化过程最终形成上述第一粘结层112,在此过程中,上述第一粘结层112的厚度逐渐减少,从而达到目标厚度。

140.更具体地,制造商对上述第一粘结层112进行干燥热处理。干燥热处理用于去除丙烯酸类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,可在90℃至120℃范围的温度下进行15分钟至30分钟。

141.根据情况,干燥热处理可分离为第一次干燥热处理、第二次干燥热处理、第三次干燥热处理来执行。

142.此时,第一次干燥热处理用于去除丙烯酸类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,可在60℃至80℃范围的温度下进行3分钟至6分钟。

143.之后,与第一次干燥热处理相同地,第二次干燥热处理用于去除丙烯酸类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,在高于第一次干燥热处理的温度下,能够以与第一次干燥热处理相同的时间进行。例如,第二次干燥热处理可在90℃至120℃范围的温度下进行3分钟至6分钟。

144.接着,与第一次干燥热处理及第二次干燥热处理相同地,第三次干燥热处理用于去除丙烯酸类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,在高于第二次干燥热处理的温度下,能够以比第二次干燥热处理更长的时间进行。例如,第三次干燥热处理可在190℃至210℃范围的温度下进行9分钟至18分钟。

145.其中,在第一次干燥热处理至第三次干燥热处理过程中,在逐步升温的同时干燥上述第一粘结层112用于防止上述第一粘结层112从表面开始干燥及固化,由此,可容易去除上述第一粘结层112中的气泡。同时,进行第三次干燥热处理后,逐渐降低温度直到常温为止,从而可实现具有更稳定的状态及均匀的厚度的上述第一粘结层112。

146.之后,制造商在20℃至60℃的温度下,使上述第一粘结层112熟成12小时至48小时来进行稳定化及固化。即,通过将在干燥热处理过程中变热的上述第一基膜111及上述第一

粘结层112逐渐冷却至20℃至60℃为止的休止期稳定的完成上述第一粘结层112中的交联反应,并且,确保上述第一粘结层112所需的物性。

147.接着,制造商向上述第一粘结层112上附着含氟的上述第一离型膜113。上述第一离型膜113包含氟,以在保护包含丙烯酸类共聚物的上述第一粘结层112的同时容易从上述第一粘结层112分离,可具有3gf/25mm至8gf/25mm范围的粘合力。此时,在上述第一离型膜113中,在其粘合力小于3gf/25mm的情况下,可自然地从上述第一粘结层112脱离,在其粘合力大于8gf/25mm的情况下,在去除上述第一离型膜113的过程中,具有上述第一粘结层112可能受损的问题。

148.制造商可通过上述的工艺过程制造上述第一胶带110。

149.另外,制造上述第二胶带120的方法制造商准备上述第二基膜121的过程开始,上述第二基膜121包含至少99重量百分比以上的铝来具有6kgf/mm2至12kgf/mm2范围的拉伸强度来具有8%至16%范围的伸长率及10μm至35μm范围的厚度,或者包含至少99重量百分比以上的铜来具有10kgf/mm2至26kgf/mm2范围的拉伸强度、4%至12%范围的伸长率及10μm至35μm范围的厚度。

150.接着,制造商将三甲基化二氧化硅-二甲基硅氧烷共聚物、乙苯(ethylbenzene)溶剂及环氧固化剂注入至混合容器,并通过搅拌作业混合。此时,通过搅拌作业的混合工艺可在常温及正常条件下执行。

151.此时,制造商使搅拌、混合的硅类组合物稳定化。硅类组合物的稳定化用于去除硅类组合物中的气泡,并且,诱导硅类组合物的化学稳定性及均匀的交联反应。作为硅类组合物的稳定化的一方案,为了去除硅类组合物中的气泡,可进行超声波处理或真空吸入,在去除气泡后,为了硅类组合物的稳定化,可使制造4小时至12小时的硅类组合物在热平衡状态下休止。优选地,为了确保化学稳定性及防止快速的交联反应,硅类组合物的稳定化应在热平衡状态下进行。

152.之后,制造商通过如下的方式形成上述第二粘结层122:利用缺角轮涂布机、槽模涂布机、凹版涂布机等向上述第二基膜121上涂布稳定化的硅类组合物后,进行干燥及固化。

153.此时,制造商可利用缺角轮涂布机、槽模涂布机、凹版涂布机等,以比第二粘结层122的最终厚度更厚的方式将硅类组合物涂布在上述第二基膜121上。具体地,可控制缺角轮涂布机、槽模涂布机、凹版涂布机等以相比于上述第二粘结层122的目标厚度,厚2.5倍至3.5倍的方式涂布硅类组合物。例如,在上述第二粘结层122的目标厚度为10μm至50μm范围的情况下,可控制缺角轮涂布机以25μm至175μm范围的涂布厚度涂布硅类组合物。在上述第二基膜121上涂布稳定化的硅类组合物的方法还可由旋涂法或喷射法等执行。

154.接着,制造商可通过干燥热处理及熟成固化过程最终形成上述第二粘结层122,在此过程中,上述第二粘结层122的厚度逐渐减少,从而达到目标厚度。

155.更具体地,制造商对上述第二粘结层122进行干燥热处理。干燥热处理用于去除硅类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,可在160℃至180℃范围的温度下进行15分钟至30分钟。

156.根据情况,干燥热处理可分离为第一次干燥热处理、第二次干燥热处理、第三次干燥热处理来执行。

157.此时,第一次干燥热处理用于去除硅类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,可在60℃至80℃范围的温度下进行3分钟至6分钟。

158.之后,与第一次干燥热处理相同地,第二次干燥热处理用于去除硅类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,在高于第一次干燥热处理的温度下,能够以与第一次干燥热处理相同的时间进行。例如,第二次干燥热处理可在160℃至180℃范围的温度下进行3分钟至6分钟。

159.接着,与第一次干燥热处理及第二次干燥热处理相同地,第三次干燥热处理用于去除硅类组合物中的溶剂,并且,激活交联反应,可利用红外线灯或红外线/热风联合干燥等进行,在高于第二次干燥热处理的温度下,能够以比第二次干燥热处理更长的时间进行。例如,第三次干燥热处理可在190℃至210℃范围的温度下进行9分钟至18分钟。

160.其中,在第一次干燥热处理至第三次干燥热处理过程中,在逐步升温的同时干燥上述第二粘结层122用于防止上述第二粘结层122从表面开始干燥及固化,由此,可容易去除上述第二粘结层122中的气泡。同时,进行第三次干燥热处理后,逐渐降低温度直到常温为止,从而可实现具有更稳定的状态及均匀的厚度的上述第二粘结层122。

161.之后,制造商在20℃至30℃的温度下,使上述第二粘结层122熟成12小时至24小时来进行稳定化及固化。即,通过将在干燥热处理过程中变热的上述第二基膜121及上述第二粘结层122逐渐冷却至20℃至30℃为止的休止期稳定的完成上述第二粘结层122中的交联反应,并且,确保上述第二粘结层122所需的物性。

162.接着,制造商向上述第二粘结层122附着含氟的上述第二离型膜123。上述第二离型膜123包含氟,以在保护包含具有螺旋网状结构的硅的上述第二粘结层122的同时容易从上述第二粘结层122分离,可具有3gf/25mm至8gf/25mm范围的粘合力。此时,在上述第二离型膜123中,在其粘合力小于3gf/25mm的情况下,可自然地从上述第二粘结层122脱离,在其粘合力大于8gf/25mm的情况下,在去除上述第二离型膜123的过程中,具有上述第二粘结层122可能受损的问题。

163.制造商可通过上述的工艺过程制造上述第二胶带110。

164.上述第一胶带贴合步骤s121为如下的步骤:制造商从上述第一胶带110去除上述第一离型膜113,使上述第一粘结层112与上述第二基膜121面接触来使上述第一胶带110与上述第二胶带120贴合。

165.之后,使用人员通过如下的方式附着本发明实施例的半导体制造工艺用胶带100:在电磁干扰屏蔽层形成工艺之前,去除上述第二胶带120的上述第二离型膜123,使上述第二粘结层122与上述半导体封装10的下表面及上述突出电极11相接触。

166.第二实施例

167.本发明第二实施例的半导体封装制造工艺用胶带100的制造方法s100包括第二胶带准备步骤s112及第二胶带贴合步骤s122。

168.上述第二胶带准备步骤s112为制造第一胶带110、第三胶带130及第四胶带140的步骤,上述第一胶带110依次层叠有包含塑料材料或金属材料的上述第一基膜111、包含丙烯酸类共聚物的上述第一粘结层112及包含氟的第一离型膜113,上述第三胶带130通过金属沉积方式在第三离型膜131形成上述第二基膜121,上述第四胶带140依次层叠有包含具

有螺旋网状结构的硅的上述第二粘结层122及包含氟的上述第二离型膜123。

169.首先,制造上述第一胶带110的方法与第一实施例的内容相同,因此,将省略详细的说明。

170.另外,制造上述第三胶带130的方法通过如下的方式执行:通过金属沉积方式在上述第三离型膜131形成上述第二基膜121。更详细地,上述第二基膜121通过金属沉积方式将铝或铜沉积在上述第三离型膜131,由此,可制造为金属沉积的转印膜形态的上述第三胶带130。作为金属沉积方式,可使用溅射方式等,并不限定于此。

171.上述第三离型膜131可具有与上述第一离型膜113及上述第二离型膜123相同的特性。

172.在此情况下,优选地,上述第二基膜210沉积在上述第三离型膜131,以具有1μm至10μm范围的厚度。这种范围的厚度有利于上述突出电极11的大小相对大的情况。

173.另外,制造上述第四胶带140的方法通过如下的方式执行:将上述第二离型膜123用作基膜来形成上述第二粘结层122。对此,与在第一实施例中的在上述第二基膜121形成上述第二粘结层122的方法的内容相同,因此将省略详细的说明。

174.上述第二胶带贴合步骤s122为如下的步骤:制造商从上述第一胶带110去除上述第一离型膜113后,通过使上述第一粘结层112与上述第三胶带130的上述第二基膜121面接触来使上述第一胶带110与上述第三胶带130贴合,从上述第三胶带130去除上述第三离型膜131后,通过使上述第二基膜121与上述第四胶带140的上述第二粘结层122面接触来使上述第三胶带130与上述第四胶带140贴合。

175.之后,使用人员通过如下的方式附着本发明实施例的半导体制造工艺用胶带100:在电磁干扰屏蔽层形成工艺之前,去除上述第四胶带140的上述第二离型膜123,使上述第二粘结层122与上述半导体封装10的下表面及上述突出电极11相接触。

176.如上所述,在本发明实施例的半导体封装制造工艺用胶带100的制造方法s100中,通过个别制造工艺,制造上述第一胶带110至上述第四胶带120后贴合,来制造上述半导体制造工艺用胶带100最终产品,由此,在上述第一胶带110至上述第四胶带140的制造工艺中产生不良的情况下,可仅废弃产生不良的个别胶带,从而提高整体工艺收率。

177.如上所述,参照附图中的实施例说明了本发明,这仅为例示,应理解的是,可根据本技术领域的通常的知识进行各种变形及等同的其他实施例。因此,本发明的真正的技术保护范围遵循发明要求保护范围,应根据上述的具体实施方式定义。

178.产业上可利用性

179.本发明涉及半导体封装制造工艺用胶带,可利用于与半导体封装的电磁干扰屏蔽层形成工艺相关的产业领域。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1