一种基于多层结构设计的PVDF/PI复合电介质薄膜的储能性能优化方法

一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法

技术领域

1.本发明属于介质电容器领域,尤其涉及一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法。

背景技术:

2.基于聚偏氟乙烯(pvdf)以及聚酰亚胺(pi)电介质具有兼容性好、韧性好、成型简单、极化强度大、击穿强度较高等优点,在电介质储能领域具有广阔应用前景。由于pvdf作为一种铁电聚合物介质材料,拥有高的极化强度和介电常数,相应的介电损耗也比较高。因此,如何在提高以聚偏氟乙烯为基体的复合介质的储能密度的同时,降低其介电损耗,成为获得优异性能的复合材料的重点和难点。这项工作中,将聚偏氟乙烯作为多层结构的极化层,将聚酰亚胺作为多层结构的绝缘层,通过高温热压制备复合薄膜,基于界面极化,界面处的电场梯度和设计的缓冲层可有效阻止电荷注入和导电,以防止早期介质击穿,从而提高多层结构复合介质的极化性能。通过上述方式,结合有机电介质高介电常数和夹层结构高界面极化的特点,同时提高复合电介质击穿强度,获得一种具有高储能密度、高能量效率和高温稳定性的电能存储材料。最终,预计这项研究将推动高性能聚合物基多层复合电介质的发展,三层聚合物设计策略为获得同时具有优异η和高ud的电介质储能材料开辟了一条新途径。

技术实现要素:

3.本发明目的是为了解决介质储能密度较低、击穿强度较低的技术问题,通过非线性介电层提供高能量密度,而线性介电层提供高放电效率。特别是基于层状结构的界面极化效应可以有效地使电场分布均匀,因而大大提高了击穿强度和能量密度的原理,提供了一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法。

4.本发明的技术方案:一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法,其特征在于通过所述一种基于聚偏氟乙烯基体,以及一种聚酰亚胺基体,通过改变不同位置薄膜材料,设计不同的层状结构,经过高温热压法,制备成高储能密度多层电介质复合薄膜。

5.进一步的,所述一种pvdf/pi高储能密度介电复合多层薄膜的制备及储能性能优化方法,其特征在于所述顶层和底层的厚度为5μm~10μm ,所述中间层的厚度为5μm~10μm。

6.步骤一:取一定量的聚酰亚胺[pi],聚偏氟乙烯[pvdf],置于塑封袋中,在鼓风干燥箱中一定温度烘烤一段时间,目的是祛除粉末中吸收的空气中的水分,随后取两个相同烧杯分别称取等质量的聚偏氟乙烯粉末以及聚酰亚胺粉末,将其溶解在一定量的n-甲基吡咯烷酮溶液中,将其在适当温度下磁力搅拌至粉末分散均匀。设置搅拌温度,搅拌一段时间待溶质完

全溶解得到所需溶液a和b;步骤二:将步骤一中所得溶液a和b放入真空干燥箱中,设定好温度和时间抽取真空排除溶液内多余气泡,防止影响薄膜质量,静置若干小时,待溶液中气泡析出完全后取出胶体备用;步骤三:刮涂法制备有机复合介质湿膜,将洗净的玻璃板放置在自动涂膜机上,调平刮刀,确定刮刀的回转格数,通过调节自动涂膜机推进速率,以及推进位置,将刮涂法制备的湿膜置于鼓风干燥箱内适宜温度下烘干热处理若干小时;步骤四:采用热压和淬火工艺,对不同的多层结构复合介质薄膜进行热压,进行梯度升温热压处理:第一阶段热压温度一定,在适宜压力下保压;第二阶段进行卸压排气泡处理,最后通过水冷装置将复合薄膜的温度迅速降至室温,在一定压力下保压获得厚度适宜、均匀致密的多层结构复合介质。

[0007]

进一步的,步骤一所述将聚酰亚胺[pi],聚偏氟乙烯[pvdf]置于鼓风干燥箱中60 ℃温度下热处理6 h。之后,用数字天平依次称量五份1~2 g的聚偏氟乙烯粉末和聚酰亚胺粉末置于称量纸上,用移液管分别称取10~20 ml的n-甲基吡咯烷酮[nmp]溶液加入烧杯中,将干燥好的1~2 g聚酰亚胺[pi],1~2 g聚偏氟乙烯粉末分别依次加入nmp中并在室温下搅拌至完全溶解,常温搅拌12 h至溶液分散均匀。

[0008]

进一步的,步骤二所述将步骤一所得的有机介质溶液转入真空干燥箱中,抽真空静置3 h,待有机溶液的气泡析出后取出备用。

[0009]

进一步的,将事先准备好的干净玻璃板用酒精擦拭干净,确认表面光滑后放置在自动涂膜机上,设定涂膜机推刀前进速度为3~8 cm/s,推刀前进距离20~30 cm,取出刮刀放置在玻璃板上,调平刮刀,将刮刀螺旋刻度回转10~30格,将步骤二中准备好的有机溶液倾倒在玻璃板表面,适度倾斜玻璃板使有机溶液流动至刮刀处,然后进行涂膜处理。

[0010]

进一步的,将刮涂法制备的薄膜根据不同类别做好标记转移至鼓风干燥箱中,温度设定为60~120℃,时间设定为4~12 h。之后将玻璃板取出转移至真空干燥箱中,抽真空,温度设定为60~150 ℃,在真空干燥箱中热处理12 h后取出,在去离子水的作用下,使用刀片将薄膜揭下放在聚酯膜中备用。

[0011]

进一步的,步骤四所述采用热压工艺,将多层结构复合薄膜置于热压模板中,经过热压处理,进行梯度升温热压处理:第一阶段热压温度60~90

ꢀ°

c,在1~5 mpa下保压15~20 min;第二阶段进行卸压排气泡处理,第三阶段热压温度90~120

°

c,在15~20 mpa下保压15~20 min。

[0012]

进一步的,步骤四所述水冷装置将复合薄膜的温度迅速降至室温,在1~5 mpa下保压1~5 min获得致密的多层结构复合介质,厚度约为10~30 μm。

[0013]

本发明的有益效果:聚酰亚胺具有击穿强度高,介电损耗低,稳定性强的特点,而聚偏氟乙烯具有极化强度大、储能密度高的特点,将两种材料复合制备多层结构可以提高复合材料的击穿强度,提升多层结构聚合物的极化性能。通过引入线性聚合物聚酰亚胺,可以提高聚偏氟乙烯基

体的击穿强度,有效增强聚合物基复合介质的绝缘性能。电介质的击穿是一个时间依赖和路径依赖的过程,在整个多层复合材料中形成所谓的电树,层状结构的界面处电场畸变在调节击穿路径方面起着重要作用,通过夹层或层压结构,增强界面极化的同时,利用界面效应抑制电树的发展。在实验中,分别从提高极化和击穿方向,提高了聚偏氟乙烯的储能性能。

[0014]

本发明制备工艺及所需设备价格低廉,实验简易且容易实施。实验制备的分布均匀且致密的多层结构复合介质可以有效提升聚合物的储能性能,并维持了聚合物基体自身优异的机械性能。因此,本实验所制备的高储能密度复合介质可以应用在储能领域。

附图说明

[0015]

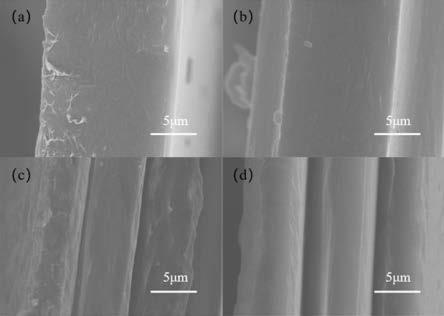

图1高储能密度介电复合介质薄膜sem扫描电镜图;图2高储能密度介电复合介质薄膜的xrd衍射谱图;图3高储能密度介电复合介质薄膜的傅里叶光谱图;图4高储能密度介电复合介质的击穿场强威布尔击穿分布;图5高储能密度介电复合介质介电性能;图6高储能密度介电复合介质储能性能。

具体实施方式

[0016]

下面结合实例对本发明的技术方案做进一步的说明,但不局限于此,凡是对本发明技术方案进行修改或者等同替换,而不脱离本发明技术方案的精神和范围,均应涵盖在本发明的保护范围中。

[0017]

实施例1一种pvdf/pi高储能密度介电复合多层薄膜的制备及储能性能优化方法,其特征在于所述聚偏氟乙烯基体以及聚酰亚胺基体,通过调整不同的多层结构,经高温热压,制备一种高储能密度的复合薄膜。

[0018]

一种pvdf/pi高储能密度介电复合多层薄膜的制备及储能性能优化方法步骤如下:步骤一:步骤一所述将聚酰亚胺[pi],聚偏氟乙烯[pvdf]置于鼓风干燥箱中60 ℃温度下热处理6 h。之后,用数字天平依次称量五份1~2 g的聚偏氟乙烯粉末和聚酰亚胺粉末置于称量纸上,用移液管分别称取10~20 ml的n-甲基吡咯烷酮溶液[nmp]加入烧杯中,将干燥好的1~2 g聚酰亚胺[pi],1~2 g聚偏氟乙烯粉末分别依次加入nmp中并在室温下搅拌至完全溶解,常温搅拌12 h至溶液分散均匀。

[0019]

步骤二:步骤二所述将步骤一所得的有机介质溶液转入真空干燥箱中,抽真空静置3 h,待有机溶液的气泡析出后取出备用;步骤三:将事先准备好的干净玻璃板用酒精擦拭干净,确认表面光滑后放置在自动涂膜机上,设定涂膜机推刀前进速度为3~8 cm/s,推刀前进距离20~30 cm,取出刮刀放置在玻璃

板上,调平刮刀,将刮刀螺旋刻度回转10~30格,将步骤二中准备好的有机溶液倾倒在玻璃板表面,适度倾斜玻璃板使有机溶液流动至刮刀处,然后进行涂膜处理。

[0020]

步骤四:将刮涂法制备的薄膜根据不同类别做好标记转移至鼓风干燥箱中,温度设定为60~120℃,时间设定为4~12 h。之后将玻璃板取出转移至真空干燥箱中,抽真空,温度设定为60~150 ℃,在真空干燥箱中热处理12 h后取出,在去离子水的作用下,使用刀片将薄膜揭下放在聚酯膜中备用。

[0021]

步骤五:采用热压工艺,将多层结构复合薄膜置于热压模板中,经过热压处理,进行梯度升温热压处理:第一阶段热压温度60~90

ꢀ°

c,在1~5 mpa下保压15~20 min;第二阶段进行卸压排气泡处理,第三阶段热压温度90~120

ꢀ°

c,在15~20 mpa下保压15~20 min。之后通过水冷装置将复合薄膜的温度迅速降至室温,在在1~5 mpa下保压1~5 min获得致密的多层结构复合介质,厚度约为10~30μm。

[0022]

实施例2一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法,其特征在于所述聚偏氟乙烯基体以及聚酰亚胺基体,通过调整不同的多层结构,经高温热压,制备一种高储能密度的复合薄膜。

[0023]

一种基于多层结构设计的pvdf/pi复合电介质薄膜的储能性能优化方法步骤如下:步骤一:将聚酰亚胺[pi],聚偏氟乙烯[pvdf]置于鼓风干燥箱中60 ℃温度下热处理6 h。之后,用数字天平依次称量五份1g的聚偏氟乙烯粉末和聚酰亚胺粉末置于称量纸中,用移液管分别称取10 ml的n-甲基吡咯烷酮[nmp]溶液加入烧杯中,将干燥好的1g聚酰亚胺[pi],1g聚偏氟乙烯粉末分别依次加入nmp中并在室温下搅拌至完全溶解,常温搅拌12 h至溶液分散均匀。

[0024]

步骤二:步骤二所述将步骤一所得的有机介质溶液转入真空干燥箱中,抽真空静置3 h,待有机溶液的气泡析出后取出备用;步骤三:将事先准备好的干净玻璃板用酒精擦拭干净,确认表面光滑后放置在自动涂膜机上,设定涂膜机推刀前进速度为4 cm/s,推刀前进距离20 cm,取出刮刀放置在玻璃板上,调平刮刀,将刮刀螺旋刻度回转25 格,将步骤二中准备好的前驱体溶液倾倒在玻璃板表面,适度倾斜玻璃板使有机溶液流动至刮刀处,然后进行涂膜处理。

[0025]

步骤四:将刮涂法制备的薄膜根据不同类别做好标记转移至鼓风干燥箱中,温度设定为80 ℃,时间设定为12 h。之后将玻璃板取出转移至真空干燥箱中,抽真空,温度设定为80 ℃,在真空干燥箱中热处理12 h后取出,在去离子水的作用下,使用刀片将薄膜揭下放在聚酯膜中备用。

[0026]

步骤五:

采用热压工艺,将多层结构复合薄膜置于热压模板中,经过热压处理,进行梯度升温热压处理:第一阶段热压温度80

°

c,在5 mpa下保压20 min;第二阶段进行卸压排气泡处理,第三阶段热压温度120

ꢀ°

c,在15 mpa下保压15 min。

[0027]

之后通过水冷装置将复合薄膜的温度迅速降至室温,在5 mpa下保压5 min获得致密的多层复合介质,厚度约为20μm。

[0028]

摘要附图1为高储能密度复合介质的断面扫描电镜图,根据sem图可以看出,多层结构复合介质单层薄膜厚度均匀,均在18μm左右,同时,层状结构明显,三层结构致密无空隙。 如图c和d,外层与中间层薄膜分别为pi/pvdf。此外,通过热压制备的多层介电膜具有清晰而均匀的界面区域,在pi和pvdf层之间没有明显的缺陷。基于先前的研究,高质量的界面有利于抑制电荷的传输,从而提高多层介电膜的绝缘性能。

[0029]

本实验中所得多层结构复合介质的xrd衍射谱图,结果如图2所示,观察xrd衍射谱图发现,夹层结构膜同时表现出pi和pvdf的特征峰,这也表明夹层膜的成功制备。此外,与未经处理的pvdf薄膜相比,热压制备的夹层结构薄膜的晶体形态发生了变化。由于热压的影响,夹层结构薄膜中的β相含量逐渐增加,而对于pvdf,17.9

°

、18.31

°

和20.20

°

的衍射峰可分别归属于非极性α相pvdf的(100)、(020)和(021)衍射面,18.50

°

和20.1

°

处的衍射峰。这些峰可分别指定为混合α相和低极性γ相pvdf的(020)和(110)衍射面。在20.9

°

附近2θ处的衍射峰可以被指定为极性β相pvdf的(110)衍射面,表明pvdf基体成功复合到多层薄膜中。

[0030]

图3傅里叶红外光谱图中发现多层结构复合薄膜1775 cm-1(c=o不对称拉伸)、1720 cm-1(c=o对称拉伸)、1366 cm-1(c=n拉伸)处出现新峰,表明pi基体成功复合进多层结构。

[0031]

图4为高储能密度复合介质介击穿强度威布尔分布图。从图中可以看到,在进行三层结构后,击穿强度提升夹层结构薄膜内部电场分布的畸变导致了绝缘的降低。与单层薄膜相比,由于pi和pvdf的介电常数不同,夹层薄膜中的内部电场会重新分布,从而提升薄膜绝缘能力,并且观察到形状因子显著提升,β=20.4,这说明多层结构复合电介质击穿稳定性提高。累积故障概率为63.2%时的特征击穿强度的范围为540~680 kv/mm。高的击穿场强说明薄膜的质量得到了优化,可以承受更高的电场强度。

[0032]

图5为高储能密度复合介质的介电性能图,从图中可以看出,可以发现,随着测试频率的升高,介电常数会有所下降并且损耗会有一定程度的增加。这是因为在高频下夹层结构膜的界面处的界面极化会增强,导致介电常数降低和损耗增加。此外,随着频率的增加,可以发现pi的介电常数稳定,而pvdf的介电系数呈下降趋势。对于线性pi,极化强度在频率范围内随电场线性变化,这使得介电常数在测试频率范围内稳定。然而,偶极极化主导了铁电聚合物的整体极化。与电子极化相比,实现偶极极化需要更长的时间。因此,偶极极化随着频率的增加而减弱,导致介电膜的介电常数减小。当频率增加时,结合线性pi和铁电pvdf的夹层结构膜的介电常数在101至10

6 hz的测试频率范围内略有下降,相较于纯pi介质,复合介质的介电常数有所提高,这可能是由于引入的有机聚合物pvdf本身具有较高的介电常数,以及界面极化的增强。在1 hz的频率下,高储能密度复合介质介电常数的范围4~8,介电损耗的范围在0.01~0.05。在1

×

10

7 hz的频率下,多层结构复合介质介电常数的范围5~7,介电损耗的范围在0.05~0.20。

[0033]

图6为高储能密度复合介质的储能性能图,可以发现,随着电场的增加,ud逐渐增加,而效率逐渐降低。由于良好的绝缘性能和改进的介电常数,将pvdf以及pi进行层状结构复合,其中pi/pvdf/pi多层结构在300 kv/mm的电场强度下放电能量密度范围为3.8~5.4 j/cm3,充放电效率的范围为85%~95%。在620 kv/mm的电场强度下放电能量密度范围为13.1~15.5 j/cm3,充放电效率的范围为55%~65%。结果表明,在620 kv/mm的电场强度下放电能量密度可达到14.6 j/cm3,充放电效率为62.2%。可以发现,铁电聚合物具有高ud但低η,而线性聚合物具有高η但低ud。本工作中制备的pi/pvdf/pi夹层膜显示出优异的放电能量密度和充放电效率,这结合了铁电聚合物和线性聚合物的特性,说明薄膜在具有优异的介电和耐击穿场强的基础上,拥有出色的储能性能。

[0034]

由图4、图5和图6可以看出本发明制备方法可使所制备的基于聚偏氟乙烯以及聚酰亚胺的多层复合介质具有较高介电常数和击穿强度。本发明通过将聚偏氟乙烯以及聚酰亚胺进行多层复合,提高了聚合物基复合介质的击穿性能,在相同的外加电场下,夹层结构薄膜的ud显著高于pi,并特别是,pi/pvdf/pi薄膜在620 kv/mm时表现出最高的ud为14.6 j/cm3,优异的η为62.2%。总之,所制备的夹层结构聚合物膜在提高介电薄膜电容器的介电和绝缘性能方面显示出巨大的应用前景。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1